Изобретение относится к радиотехнике и может быть использовано к системах встроенного контроля дискретно-коммутационных антенных решеток с pin-диодными фазовращателями.

Известно устройство для встроенного контроля дискретно-коммутационной антенной решетки с pin-диодными фазовращателями и со строчно-столбцовым фазированием (1), содержащее синхронизатор, соединенный с вычислителем фаз антенной решетки и блоком съема кода неисправного фазовращателя, q электронных ключей в каждой строке (q - число разрядов pin-диодного фазовращателя), управляемые синхронизатором и присоединенные к блоку сравнения кодов, вторые входы которого соединены с вычислителем кодов фаз антенной решетки. Это устройство имеет низкую помехозащищенность и малую надежность.

Перечисленные недостатки устранены в другом известном устройстге для встроенного контроля (2). которое является наиболее близким по технической сущности к

предлагаемому изобретению и выбрано в качестве прототипа.

Известное устройство для встроенного контроля дискретно-коммутационной антенной решетки с pin-диодными фазовращателями и строчно-столбцовым фазированием содержит синхронизатор, первый выход которого соединен со входом вычислителя кодов фаз антенной решетки, а второй выход подключен к первому входу блока сьема кода неисправного фазовращателя, электронные ключи в каждой строке, управляющие входы которых соединены со вторым N-разрядным (N - число строк антенной решетки) выходом синхронизатора, а выходы подключены к первому N-разряд- ному входу блока сравнения кодов, второй вход которого соединен с выходом вычислителя кодов фаз антенной решетки, а выход подключен ко второму входу блока сьема кода неисправного фазовращателя, выход которого является выходом устройства, логические элементы ИЛИ, подключенные выходами ко входу каждого электронного ключа, а каждый анод pin-диодов фазоврасл

С

i

00

сЈ

N

щателей одной строки соединен со входом логического элемента ИЛИ через дифференцирующие цепи.

Однако известное устройство не обеспечивает высокую достоверность контроля.

Целью изобретения является повышение достоверности контроля.

Положительный эффект предлагаемого устройства состоит в том, что в отличие от прототипа устройство реагирует на обрывы в цепях pin-диодов и распознает вид отказа pin-диода (короткое замыкание или обрыв).

Поставленная цель достигается тем, что в устройство для встроенного контроля дискретно-коммутационной антенной решетки с pin-диодными фазовращателями и со строчно-столбцовым фазированием, включающее синхронизатор, выход которого подключен к первому входу блока съема кода неисправного фазовращателя, выход которого является первым выходом устройства, N электронных ключей первой группы, вход каждого из которых подсоединен к выходу соответствующего логического элемента ИЛИ первой группы, а управляющие входы к первому N разрядному выходу синхронизатора, дополнительно введены MNQ электронных ключей второй группы, MNQ электронных ключей третьей группы, N электронных ключей четвертой группы, MNQ амплитудных селекторов, N логических элементов ИЛИ второй группы и логический элемент И, причем вход mnq-ro амплитудного селектора подключен к аноду pin-диода q-ro разряда фазовращателя, гл- го стобца и п-й строки (т 1 ... М; n 1....N; q 1....Q), первый выход - к входу mnq-ro электронного ключа второй группы, а второй выход - к входу mnq-ro электронного ключа третьей группы, выход которого подсоединен к mq-му входу n-го логического элемента ИЛИ второй группы, а mq-й вход n-го логического элемента ИЛИ первой группы подключен к выходу mnq-ro электронного ключа второй группы, выход каждого логического элемента ИЛИ второй группы через n-й электронный ключ четвертой группы подключен к первому входу логического элемента И, к второму входу которого подсоединены выходы электронных- ключей первой группы, я также второй вход блока съ ема кода неисправного фазовращателя, выход логического элемента И является вторым выходом устройства, управляющие входы каждого mnq-ro электронного ключа второй и третьей групп объединены и подключены к q-й п-разряд- ной линии m-й шины второго выхода синхронизатора вход которого является управляющим входом устройства, управляющий вход n-го электронного ключа четвертой группы подсоединен к управляющему входу n-го электронного ключа первой группы,

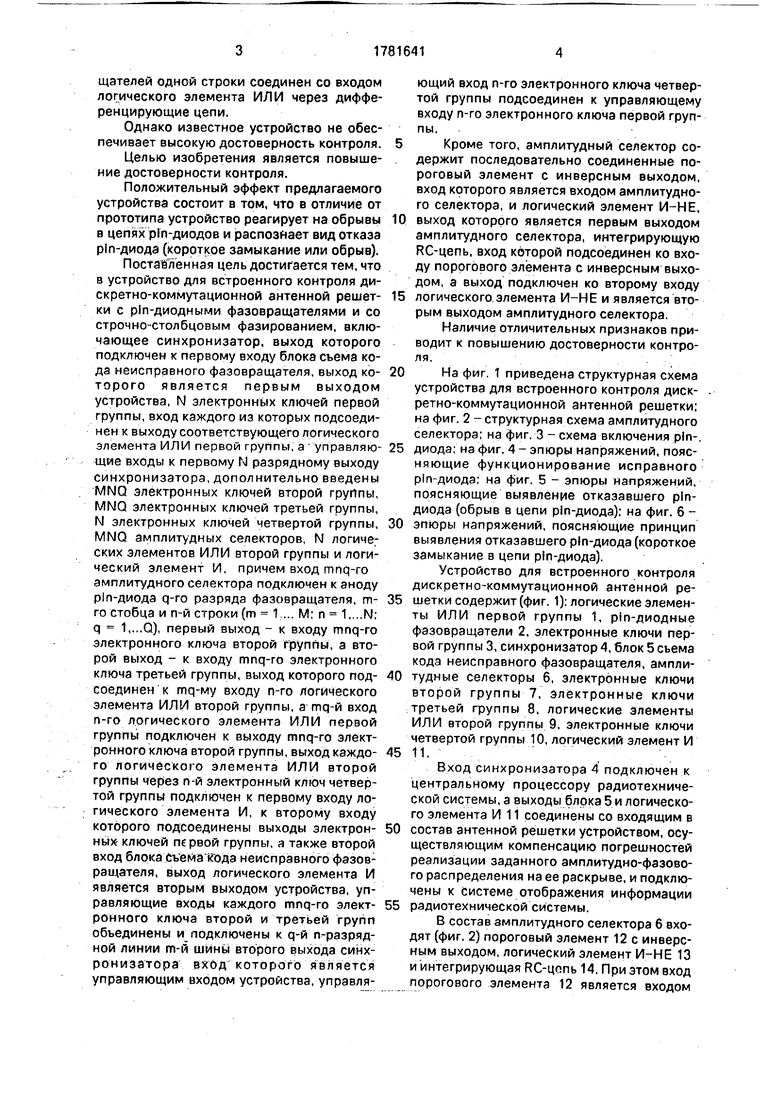

Кроме того, амплитудный селектор содержит последовательно соединенные пороговый элемент с инверсным выходом, вход которого является входом амплитудного селектора, и логический элемент И-НЕ,

0 выход которого является первым выходом амплитудного селектора, интегрирующую RC-цепь, вход которой подсоединен ко входу порогового элемента с инверсным выходом, а выход подключен ко второму входу

5 логического элемента И-НЕ и является вторым выходом амплитудного селектора.

Наличие отличительных признаков приводит к повышению достоверности контроля.

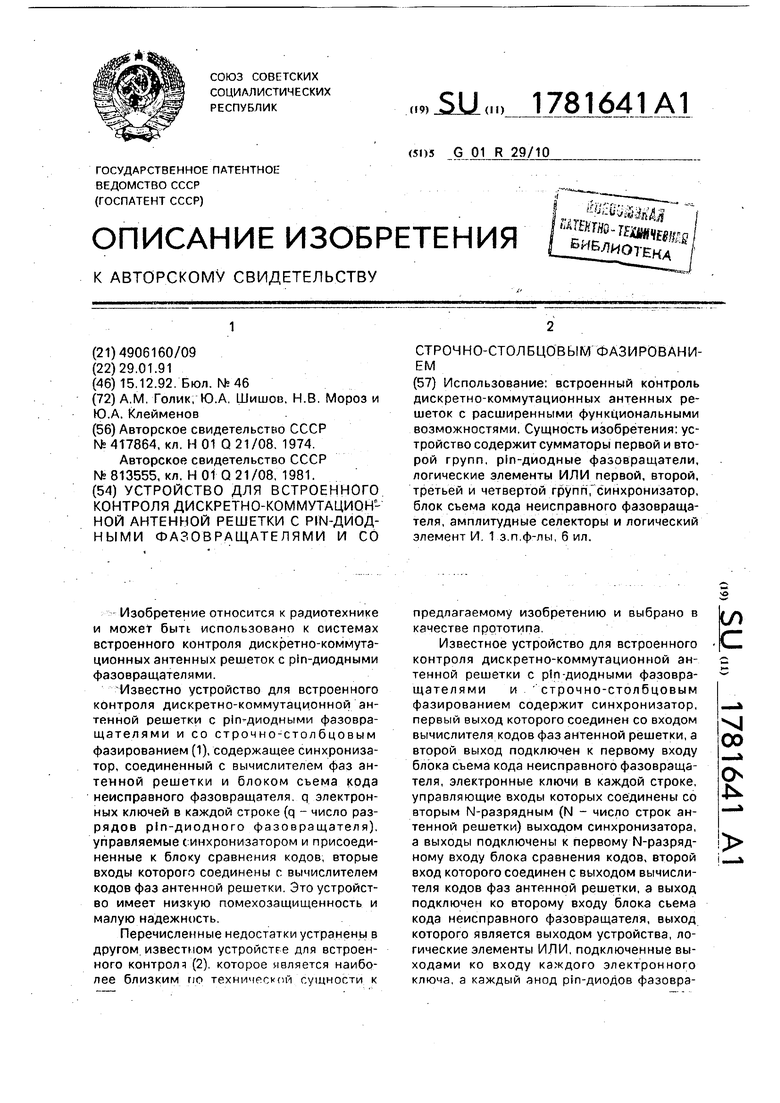

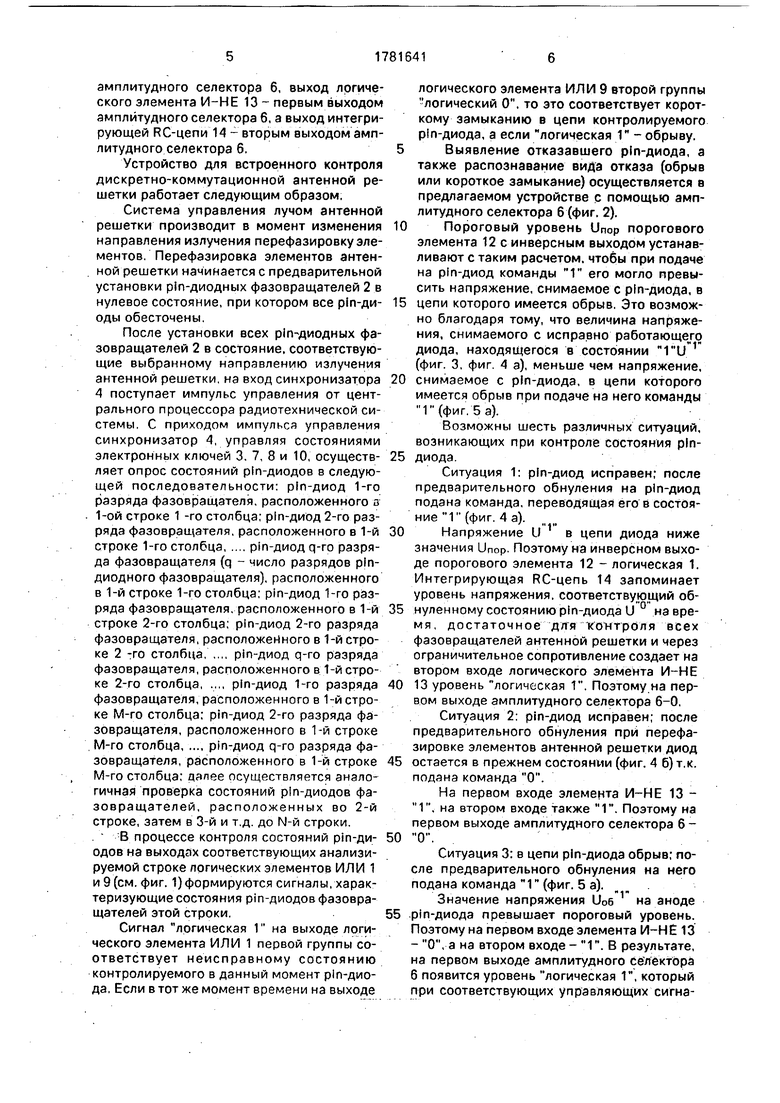

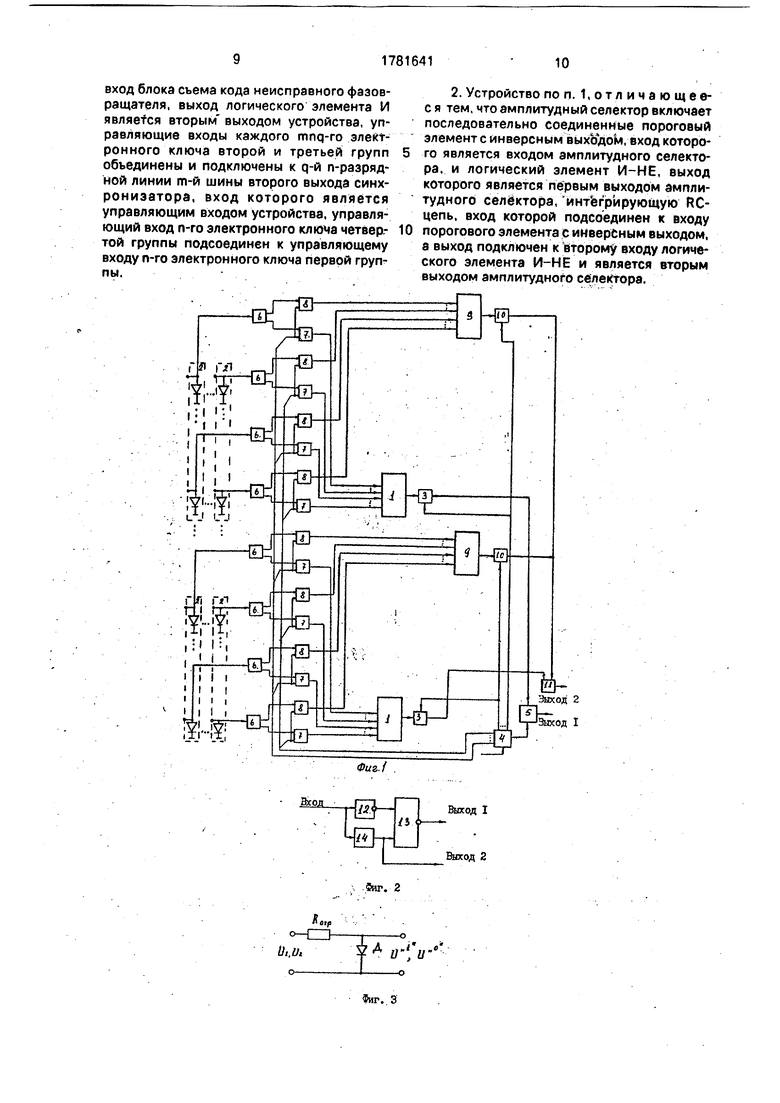

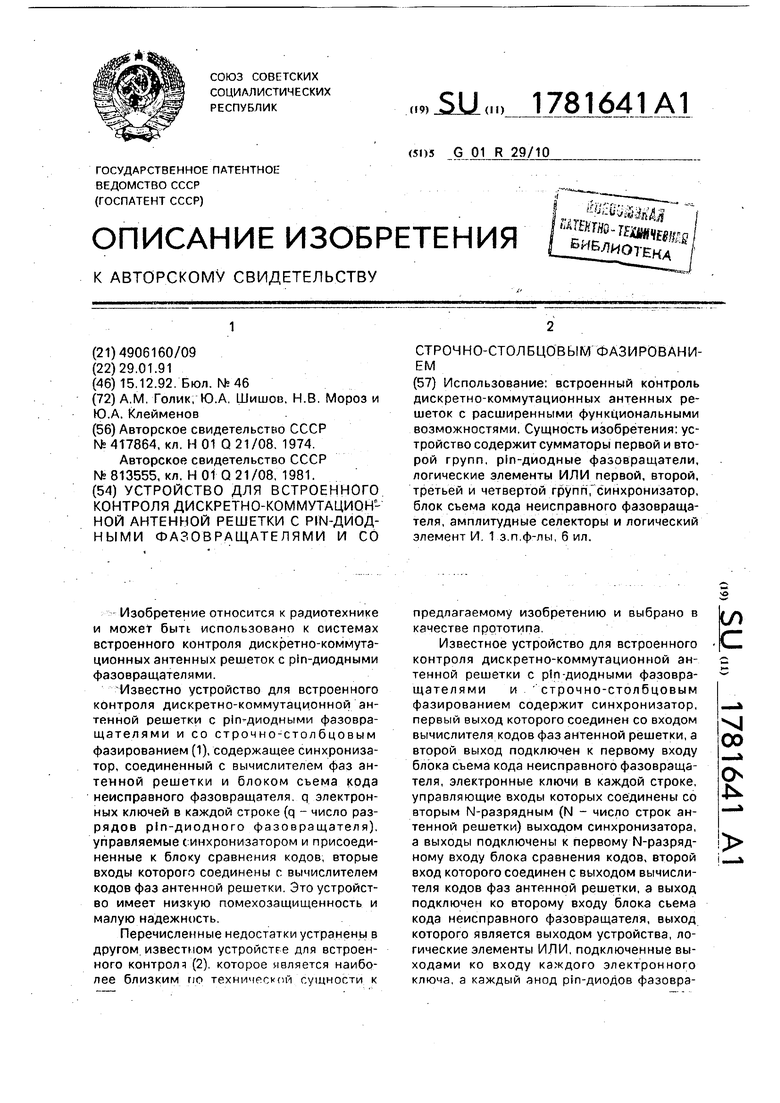

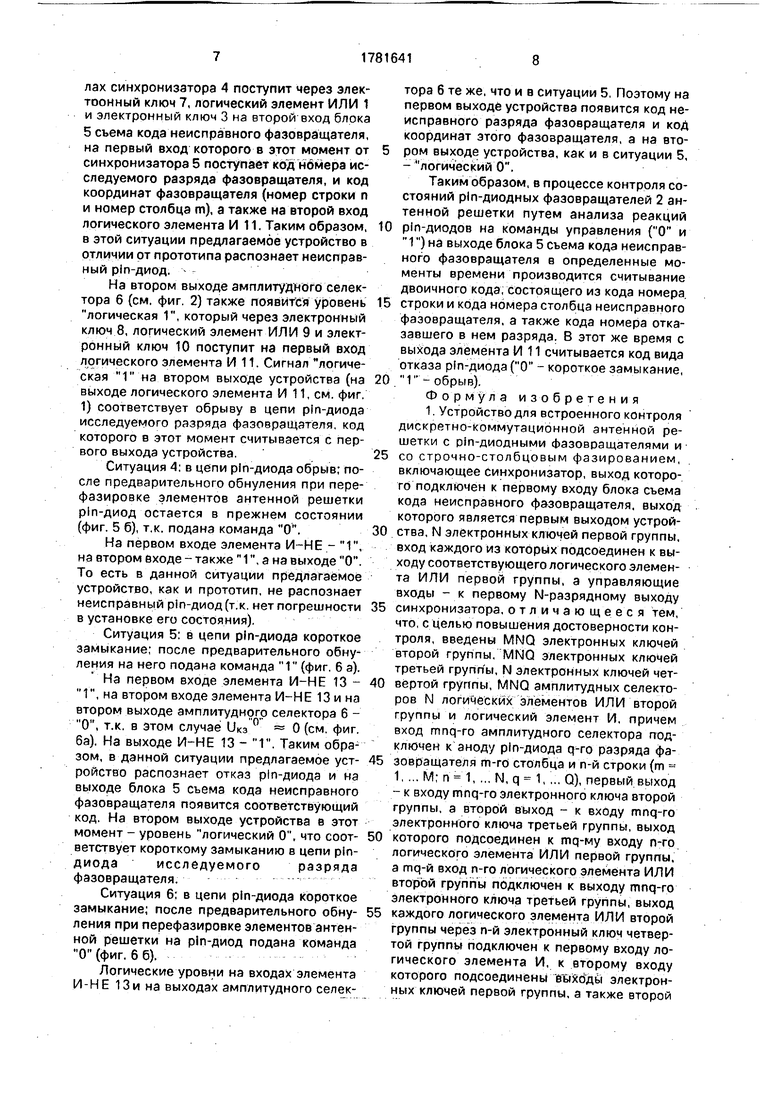

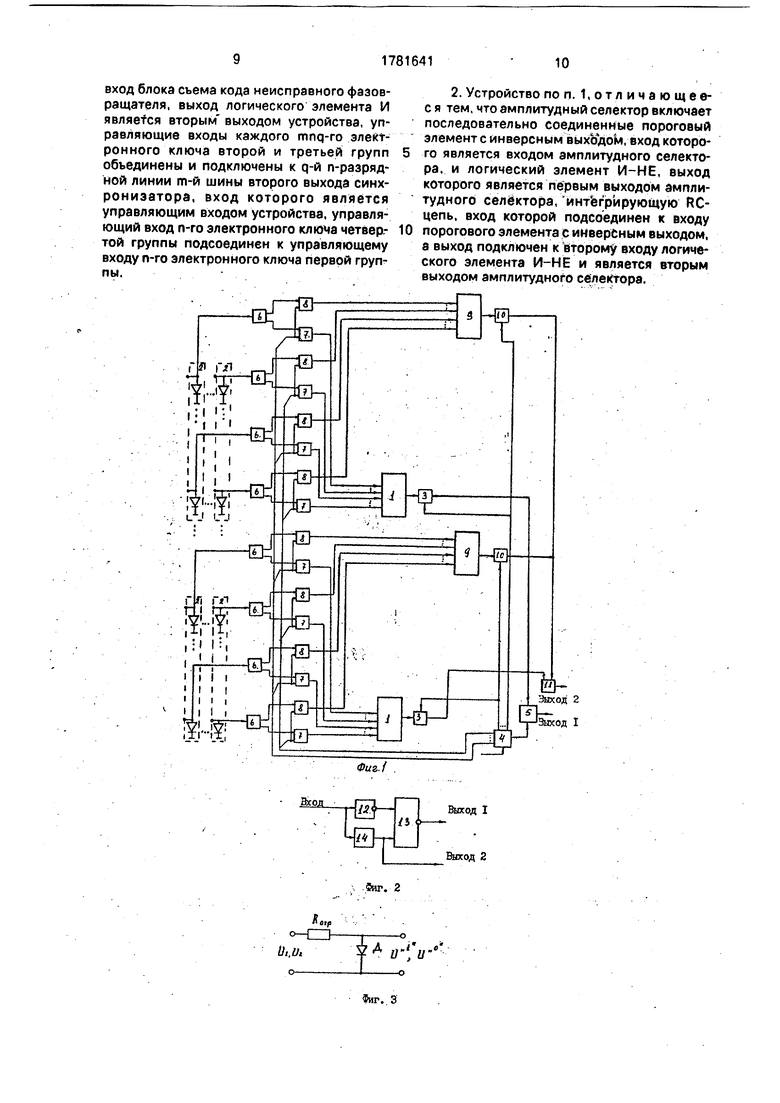

0 На фиг. 1 приведена структурная схема устройства для встроенного контроля дискретно-коммутационной антенной решетки; на фиг. 2 - структурная схема амплитудного селектора; на фиг. 3 - схема включения pin-.

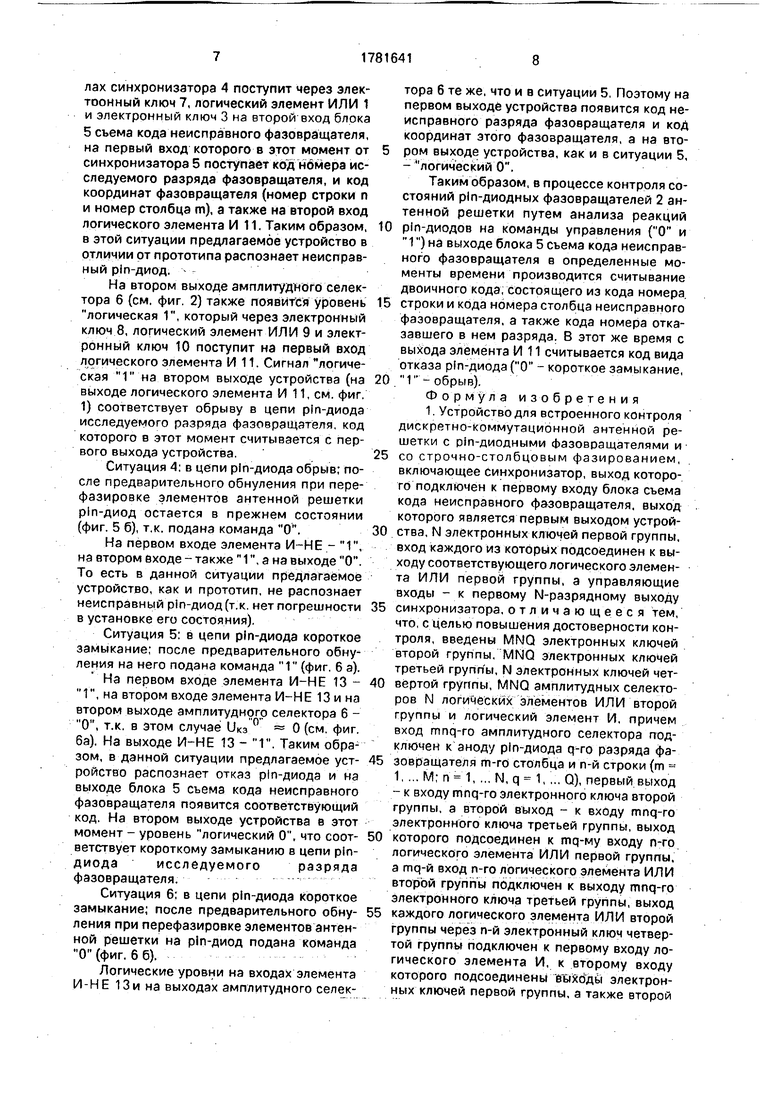

5 диода: на фиг. 4 - эпюры напряжений, поясняющие функционирование исправного pin-диода; на фиг. 5 - эпюры напряжений, поясняющие выявление отказавшего pin- диода (обрыв в цепи pin-диода); на фиг. 6 0 эпюры напряжений, поясняющие принцип выявления отказавшего pin-диода (короткое замыкание в цепи pin-диода).

Устройство для встроенного контроля дискретно-коммутационной антенной ре5 шетки содержит (фиг. 1): логические элементы ИЛИ первой группы 1, pin-диодные фазовращатели 2, электронные ключи первой группы 3, синхронизатор 4, блок 5 съема кода неисправного фазовращателя, ампли0 тудные селекторы б, электронные ключи второй группы 7, электронные ключи третьей группы 8, логические элементы ИЛИ второй группы 9, электронные ключи четвертой группы 10, логический элемент И

5 11.

Вход синхронизатора 4 подключен к центральному процессору радиотехнической системы, а выходы блока 5 и логического элемента И 11 соединены со входящим в

0 состав антенной решетки устройством, осуществляющим компенсацию погрешностей реализации заданного амплитудно-фазового распределения на ее раскрыве, и подключены к системе отображения информации

5 радиотехнической системы.

В состав амплитудного селектора 6 входят (фиг. 2) пороговый элемент 12 с инверсным выходом, логический элемент И-НЕ 13 и интегрирующая RC-цопь 14. При этом вход порогового элемента 12 является входом

амплитудного селектора 6, выход логического элемента И-НЕ 13 - первым выходом амплитудного селектора б, а выход интегрирующей RC-цепи 14 - вторым выходом амплитудного селектора 6,

Устройство для встроенного контроля дискретно-коммутационной антенной решетки работает следующим образом,

Система управления лучом антенной решетки производит в момент изменения направления излучения перефазировку элементов. Перефазировка элементов антенной решетки начинается с предварительной установки pin-диодных фазовращателей 2 в нулевое состояние, при котором все pin-ди- оды обесточены.

После установки всех pin-диодных фазовращателей 2 в состояние, соответствующие выбранному направлению излучения антенной решетки, на вход синхронизатора 4 поступает импульс управления от центрального процессора радиотехнической системы. С приходом импульса управления синхронизатор 4, управляя состояниями электронных ключей 3. 7, 8 и 10, осуществ- ляет опрос состояний pin-диодов в следующей последовательности: pin-диод 1-го разряда фазовращателя, расположенного з 1-ой строке 1 -го столбца; pin-диод 2-го разряда фазовраа ателя, расположенного в 1-й строке 1-го столбцаpin-диод q-ro разряда фазовращателя (q - число разрядов pin- диодного фазовращателя), расположенного в 1-й строке 1-го столбца: pin-диод 1-го разряда фазовращателя, расположенного в 1-й строке 2-го столбца; pin-диод 2-го разряда фазовращателя, расположенного в 1-й строке 2 -го столбца pin-диод q-ro разряда

фазовращателя, расположенного в 1-й строке 2-го столбца pin-диод 1-го разряда

фазовращателя, расположенного в 1-й строке М-го столбца; pin-диод 2-го разряда фазовращателя, расположенного в 1-й строке М-го столбцаpin-диод q-ro разряда фазовращателя, расположенного в 1-й строке М-го столбца; далее осуществляется аналогичная проверка состояний pin-диодов фазовращателей, расположенных во 2-й строке, затем в 3-й и т.д. до N-й строки.

В процессе контроля состояний pin-ди- одов на выходах соответствующих анализируемой строке логических элементов ИЛИ 1 и 9(см. фиг. формируются сигналы, характеризующие состояния pin-диодов фазовращателей этой строки,

Сигнал логическая 1 на выходе логического элемента ИЛИ 1 первой группы соответствует неисправному состоянию контролируемого в данный момент pin-диода, Если в тот же момент времени на выходе

логического элемента ИЛИ 9 второй группы логический 0. то это соответствует короткому замыканию в цепи контролируемого pin-диода, а если логическая 1 -обрыву.

Выявление отказавшего pin-диода, а также распознавание вида отказа (обрыв или короткое замыкание) осуществляется в предлагаемом устройстве с помощью амплитудного селектора 6 (фиг. 2).

Пороговый уровень Unop порогового элемента 12 с инверсным выходом устанавливают с таким расчетом, чтобы при подаче на pin-диод команды 1 его могло превысить напряжение, снимаемое с pin-диода, в цепи которого имеется обрыв. Это возможно благодаря тому, что величина напряжения, снимаемого с исправно работающе/о диода, находящегося в состоянии (фиг. 3, фиг. 4 а), меньше чем напряжение, снимаемое с pin-диода, в цепи которого имеется обрыв при подаче на него команды 1 (фиг. 5 а).

Возможны шесть различных ситуаций, возникающих при контроле состояния pin- диода.

Ситуация 1: pin-диод исправен; после предварительного обнуления на pin-диод подана команда, переводящая его в состояние 1 (фиг. 4 а).

Напряжение U в цепи диода ниже значения Unop. Поэтому на инверсном выходе порогового элемента 12 - логическая 1. Интегрирующая RC-цепь 14 запоминает уровень напряжения, соответствующий обнуленному состоянию pin-диода U ° на время, достаточное для контроля всех фазовращателей антенной решетки и через ограничительное сопротивление создает на втором входе логического элемента И-НЕ 13 уровень логическая 1. Поэтому на первом выходе амплитудного селектора 6-0,

Ситуация 2: pin-диод исправен; после предварительного обнуления при перефа- зировке элементов антенной решетки диод остается в прежнем состоянии (фиг. 4 б) т.к. подана команда О.

На первом входе элемента И-НЕ 13 - 1, на втором входе также 1. Поэтому на первом выходе амплитудного селектора 6 - О.

Ситуация 3: в цепи pin-диода обрыв; после предварительного обнуления на него подана команда 1 (фиг. 5 а).

Значение напряжения U06 1 на аноде pin-диода превышает пороговый уровень. Поэтому на первом входе элемента И-НЁ 13 - О, а на втором входе - 1. В результате, на первом выходе амплитудного селектора 6 появится уровень логическая 1, который при соответствующих управляющих сигналах синхронизатора 4 поступит через элек- тоонный ключ 7, логический элемент ИЛИ 1 и электронный ключ 3 на второй вход блока 5 съема кода неисправного фазовращателя, на первый вход которого в этот момент от синхронизатора 5 поступает код номера исследуемого разряда фазовращателя, и код координат фазовращателя (номер строки п и номер столбца т), а также на второй вход логического элемента И 11, Таким образом, в этой ситуации предлагаемое устройство в отличии от прототипа распознает неисправный pin-диод.

На втором выходе амплитудного селектора б (см. фиг 2) также появится уровень логическая 1, который через электронный ключ 8, логический элемент ИЛИ 9 и электронный ключ 10 поступит на первый вход логического элемента И 11. Сигнал логическая 1 на втором выходе устройства (на выходе логического элемента И 11, см. фиг. 1) соответствует обрыву в цепи pin-диода исследуемого разряда фазовращателя, код которого в этот момент считывается с первого выхода устройства.

Ситуация 4: в цепи pin-диода обрыв; после предварительного обнуления при пере- фазировке элементов антенной решетки pin-диод остается в прежнем состоянии (фиг. 5 б), т.к. подана команда О.

На первом входе элемента И-НЕ - 1, на втором входе - также 1, а на выходе О. То есть в данной ситуации предлагаемое устройство, как и прототип, не распознает неисправный pin-диод (т.к нет погрешности в установке его состояния).

Ситуация 5: в цепи pin-диода короткое замыкание; после предварительного обнуления на него подана команда 1 (фиг. 6 а).

На первом входе элемента И-НЕ 13 - 1, на втором входе элемента И-НЕ 13 и на втором выходе амплитудного селектора 6 - О, т.к. в этом случае 11кэ ° 0 (см фиг. ба). На выходе И-НЕ 13 - 1. Таким образом, в данной ситуации предлагаемое уст- ройство распознает отказ pin-диода и на выходе блока 5 съема кода неисправного фазовращателя появится соответствующий код. На втором выходе устройства в этот момент - уровень логический 0, что соот- ветствует короткому замыканию в цепи pin- диода исследуемого разряда фазовращателя.

Ситуация 6; в цепи pin-диода короткое замыкание; после предварительного обну- ления при перефазировке элементов антенной решетки на pin-диод подана команда О (фиг. 6 б).

Логические уровни на входах элемента И-НЕ 13и на выходах амплитудного селектора 6 те же, что и в ситуации 5, Поэтому на первом выходе устройства появится код неисправного разряда фазовращателя и код координат этого фазовращателя, а на втором выходе устройства, как и в ситуации 5,

- логический О.

Таким образом, в процессе контроля состояний pin-диодных фазовращателей 2 антенной решетки путем анализа реакций pin-диодов на команды управления (О и 1)на выходе блока 5 съема кода неисправного фазовращателя в определенные моменты времени производится считывание двоичного кода, состоящего из кода номера строки и кода номера столбца неисправного фазовращателя, а также кода номера отказавшего в нем разряда. В этот же время с выхода элемента И 11 считывается код вида отказа pin-диода (О - короткое замыкание, 1 - обрыв).

Формула изобретения 1 Устройство для встроенного контроля дискретно-коммутационной антенной решетки с pin-диодными фазовращателями и со строчно-столбцовым фазированием, включающее синхронизатор, выход которого подключен к первому входу блока съема кода неисправного фазовращателя, выход которого является первым выходом устройства, N электронных ключей первой группы, вход каждого из которых подсоединен к выходу соответствующего логического элемента ИЛИ первой группы, а управляющие входы - к первому N-разрядному выходу синхронизатора, отличающееся тем, что, с целью повышения достоверности контроля, введены MNQ электронных ключей второй группы, MNQ электронных ключей третьей группы, N электронных ключей четвертой группы, MNQ амплитудных селекторов N логических элементов ИЛИ второй группы и логический элемент И, причем вход mnq-ro амплитудного селектора подключен к аноду pin-диода q-ro разряда фазовращателя m-ro столбца и n-й строки (т - 1, . М; п 1, ... N, q 1,... Q), первый выход

-к входу mnq-ro электронного ключа второй группы, а второй выход - к входу mnq-ro электронного ключа третьей группы, выход которого подсоединен к mq-му входу л-го логического элемента ИЛИ первой группы, а mq-й вход п-го логического элемента ИЛИ второй группы подключен к выходу mnq-ro электронного ключа третьей группы, выход каждого логического элемента ИЛИ второй группы через n-й электронный ключ четвертой группы подключен к первому входу логического элемента И, к второму входу которого подсоединены выходы электронных ключей первой группы, а также второй

вход блока сьема кода неисправного фазовращателя, выход логического элемента И является вторым выходом устройства, управляющие входы каждого mnq-ro электронного ключа второй и третьей групп объединены и подключены к q-й п-разряд- ной линии m-й шины второго выхода синхронизатора, вход которого является управляющим входом устройства, управляющий вход п-го электронного ключа четвертой группы подсоединен к управляющему входу п-го электронного ключа первой группы.

0

2. Устройство по п. 1,отличающее- с я тем, что амплитудный селектор включает последовательно соединенные пороговый элемент с инверсным выходом, вход которого является входом амплитудного селектора, и логический элемент И-НЕ, выход которого является первым выходом амплитудного селектора, интегрирующую RC- цепь, вход которой подсоединен к входу порогового элемента с инверсным выходом, а выход подключен к второму входу логического элемента И-НЕ и является вторым выходом амплитудного селектора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для встроенного кон-ТРОля диСКРЕТНО-КОММуТАциОННОйАНТЕННОй РЕшЕТКи | 1979 |

|

SU813555A1 |

| Устройство для контроля работоспособности фазированной антенной решетки с фазовращателями на pIN-диодах | 1989 |

|

SU1659914A1 |

| Вычислительное устройство для управления лучом плоской антенной решетки | 1988 |

|

SU1580393A1 |

| ФАЗОВЫЙ ПАРАМЕТРИЧЕСКИЙ ГИДРОЛОКАТОР БОКОВОГО ОБЗОРА | 1992 |

|

RU2039366C1 |

| Устройство распределения и фазирования сверхвысокочастотного сигнала | 2018 |

|

RU2699041C1 |

| Устройство для управления лучом плоской антенной решетки | 1983 |

|

SU1167616A1 |

| СПОСОБ КОНТРОЛЯ ДИАГРАММНЫХ ПАРАМЕТРОВ ФАЗИРОВАННОЙ АНТЕННОЙ РЕШЕТКИ РАДИОПЕЛЕНГАТОРА | 1996 |

|

RU2117308C1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1982 |

|

SU1282190A1 |

| СПОСОБ ВСТРОЕННОГО КОНТРОЛЯ ХАРАКТЕРИСТИК ФАЗИРОВАННОЙ АНТЕННОЙ РЕШЕТКИ | 2006 |

|

RU2333502C2 |

| Вычислительное устройство для управления лучом плоской антенной решетки | 1981 |

|

SU1013967A1 |

Использование: встроенный контроль дискретно-коммутационных антенных решеток с расширенными функциональными возможностями. Сущность изобретения: устройство содержит сумматоры первой и второй групп, pin-диодные фазовращатели, логические элементы ИЛИ первой, второй, третьей и четвертой групп,синхронизатор, блок сьема кода неисправного фазовращателя, амплитудные селекторы и логический элемент И. 1 з,п.ф-лы, 6 ил.

.ВходГц

Lrn

и/

o-db Ut,U,

о

Выход I

Выход 2

y zrftf

Iп

V

Команда I

Untf

-.i

Т

а)

5иг. 4

Команда I Г

mi

„е /о

а)

Зиг. 5

тт Команда I

и

U пор f/tj

а)

Редактор А.Бер

5иг. 6

Составитель А.Голик Техред М.Моргентал

V

л«

Команда О

U

па ft

и

.о

б)

V . Комавда О

U ПО

„° U о

б)

U Команда О

it/™, г/«Г

б)

Корректор Л.Ливринц

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| ПРИБОР ДЛЯ ЗАПИСИ И ВОСПРОИЗВЕДЕНИЯ ЗВУКОВ | 1923 |

|

SU1974A1 |

| Устройство для встроенного кон-ТРОля диСКРЕТНО-КОММуТАциОННОйАНТЕННОй РЕшЕТКи | 1979 |

|

SU813555A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1992-12-15—Публикация

1991-01-29—Подача