вого счетчика является первым входом блока, выходы разрядов первого счетчика соединены с соответствующими входами дешифратора, первый которого соединен с первым входом первого элемента И, выход которого соединен со счетным входом первого счетчика, второй вход первого элемента И объединен с первым входом первого.элемента И-ИЛИ-НЕ и является вторым входом блока, второй вход первого элемента И-ИЛИ-НЕ является третьим входом блока, третий вход первого элемента И-ИЛИ-НЕ объединен с первым входом второго элемента И-ИЛИ-НЕ и подключен к нулевому входу триггера, единичный выход которого соединен с первым входом элемента ИЛИ, четвертым входом первого элемента И-ИЛИ-НЕ и вторым входом втрого элемента И-ИЛИ-НЕ, третий вход которого является четвертым входом блока, четвертый вход второго элемента И-ИЛИ-НЕ соединен с выходом старшего разряда второго счетчика, счетный вход которого соединен с выходом первого элемента И-ИЛИ-НЕ, выходы разрядов второго счетчика соединены с соответствующими входами первой группы входов преобразователя кодовj входы второй группы входов которого соединены с соответствующими выходами разрядов третьего счетчика, счетный вход которого соединен с выхрдом второго элемента И-ИЛИ-НЕ, выходы преобразователя кодов соединены с соответствующими информационными вхо,дами первого регистра и эдресными входами элемента памяти, вход записи-считывания которого соединен с выходом элемента ИЛИ, второй вход которого подключен к второму выходу дешифратора, информационные входы (Элемента памяти соединены с соответствующими выходами разрядов второго регистра, выходы элемента памяти соединены с соответствующими входами первой группы входов сумматора, входы второй группы входов которого, кроме первого входа, объединены и соединены с шиной нулевого логического сигнала, а рерый вход второй группы вхрдОв сумматора соединен с шиной единичного логического сигнала, информационные выходы сумматора соединены с соответствующими информационными входами второго регистра, вход тактовых импульсов которого объединен с первым входом второго элемента И и подключен к третьему вы(оду дешифратора, четвертый выход . которого соединен с входами начальной установки второго и третьего счетчиков, вход начальной установки второго регистра соединен с единичным выходом триггера, нулевой вход которого соединен с выходом старшего разряда третьего счетчика, единичный вход триггера объединен с входом тактовых импульсов первого регистра и подключен к выходу второго элемента И, второй вход которого подключен к выходу переноса сумматора, выходы первого регистра являются соответствующими выходами блока.

3. Коррелятор ПОП.1, о т л и чающийся тем, что блок управления содержит первый и второй счетчики, первый и второй сумматоры, первый, второй и третий инверторы, первый, второй, третий, четвертый и пятый элементы И, элемент И-НЕ, элемент ИЛИ, первый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, а также первую 14 вторую группы элементов ИСКЛЮЧАКМЦЕЕ ИЛИ, причем управляющие входы первого, второго, третьего и четвертого элементов И объединены и подключены к первому входу блока, первый вход первого элемента ИСКШЧ/УОЩЕЕ ИЛИ объединены с первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и является вторым входом блока, вторые входы первого и второго элементов ИСКЛШАЮЩЕЕ ИЛИ являются соответственно третьим и четвертым .входами блокаi выходы первого и второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с информационными входами первого и четвертого элементов И и входами первого, и второго инверторов соответственно, выходы которых соединены соответственно с информационными входами второго и третьего элементов И, выходы которых соединены соответственно с входами суммирования первого и второго счетчиков, входы начальной установки которых объединены и являются пятым входом блока, выходы разрядов первого, и второго счетчиков, кроме старшего разряда, соединены соответственно с соответствующими первыми входами элементов ИСКЛЮЧАЩЕЕ ИЛИ первой и второй групр, вторые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ первой и второй групп объединены в каждой из групп, а также объединены соответственно с входами пере

носа первого и второго сумматоров м подключены соответственно к выходам старшего разряда первого и второго . счетчиков, входы первой и второй групп информационных входов первого сумматор подключены соответственно к соответствующим: выходам элементов ИСКЛЮЧАЮЩЕЕ ИЛИ первой и второй групп, информационные выходы первого сумматора соединены с соответствующими информа ционными входами первой группы входов второго сумматора, информационные входы второй группы входов которого соединены с шиной управляющего кода, информационные выходы второго сумт матора соединены с соответствующими

входами элемента И-НЕ, выход которого соединен с информационным входом пятого элемента И, управляющий вход которого соединён с выходом третьего инвертора, вход которого объединен с выходом элемента ИЛИ и является первы выходом блока, первый и второй входы элемента ИЛИ соединены соответственно с выходами переноса первого и второго сумматоров, выход пятого .элемента И является вторым выходом блока, выходы первого и четвертого элементов И объединены соответственно с входами вычитания первого и второго счетчиков иявляются соответственно третьим и четвёртым выходами блока управления

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой коррелятор | 1989 |

|

SU1711181A1 |

| Устройство для определения взаимной корреляционной функции | 1990 |

|

SU1751779A1 |

| Цифровой коррелятор | 1985 |

|

SU1251107A1 |

| Устройство для определения взаимной корреляционной функции | 1986 |

|

SU1406602A1 |

| Коррелятор | 1983 |

|

SU1130874A1 |

| Цифровой коррелятор | 1983 |

|

SU1129621A1 |

| Корреляционный измеритель фазовых соотношений узкополосных случайных процессов | 1990 |

|

SU1714616A1 |

| Устройство для оценки амплитуды узкополосного случайного процесса | 1987 |

|

SU1499375A1 |

| Многоканальный цифровой коррелятор | 1984 |

|

SU1290352A1 |

| Устройство для определения заданной ординаты корреляционной функции | 1990 |

|

SU1777152A1 |

Изобретение предназначено для формирования оценок положения моды функции распределения плотности вероятности обобщенного коэффициента взаимной знаковой корреляции и может использо ваться в системах измерения и контроя, а также в составе специализированных вычислительных систем для обработки сигналов в реальном масштабе времени.10

Известен знаковый коррелятор, со- , держащий входной блок, выход которого через формирователь соединен с входами блока задержки и инвертора, выхоы которого соединены с входами эле-, j мента совпадения, выход которого соеДинен через блок усреднения с входом индикатора 1 .

Недостатками такого знакового коррелятора являются низкая точность 2о и ограниченные функциональные возможности.

Известен также коррелятор, содержащий генератор тактовых импульсов,; формирователь импульсов, блок форми 25 рования задержанного сигнала, первый и второй усилители-ограничители, переключатель, делитель частоты и per версивный счетчик, входы суммирования и вычитания которого соединены с ,Q выходами соответственно первого и вто рого элементов совпадения, а входы первого и второго усилителёй-ограничителей соединены соответственно с , , первым и вторым входами коррелятора z. 35

Недостатком известного коррелятора является относительно низкая точность измерения. Действительно, при измерении коэффициентов знаковой корреляции случайных сигналов,со значительной аддитивной шумовой составляющей коррелятор формирует оценки этих коэффициентов со значительной методической погрешностьюГЗ.

Цель изобретения - повышение точности определения оценок крэффициентов знаковой корреляции.

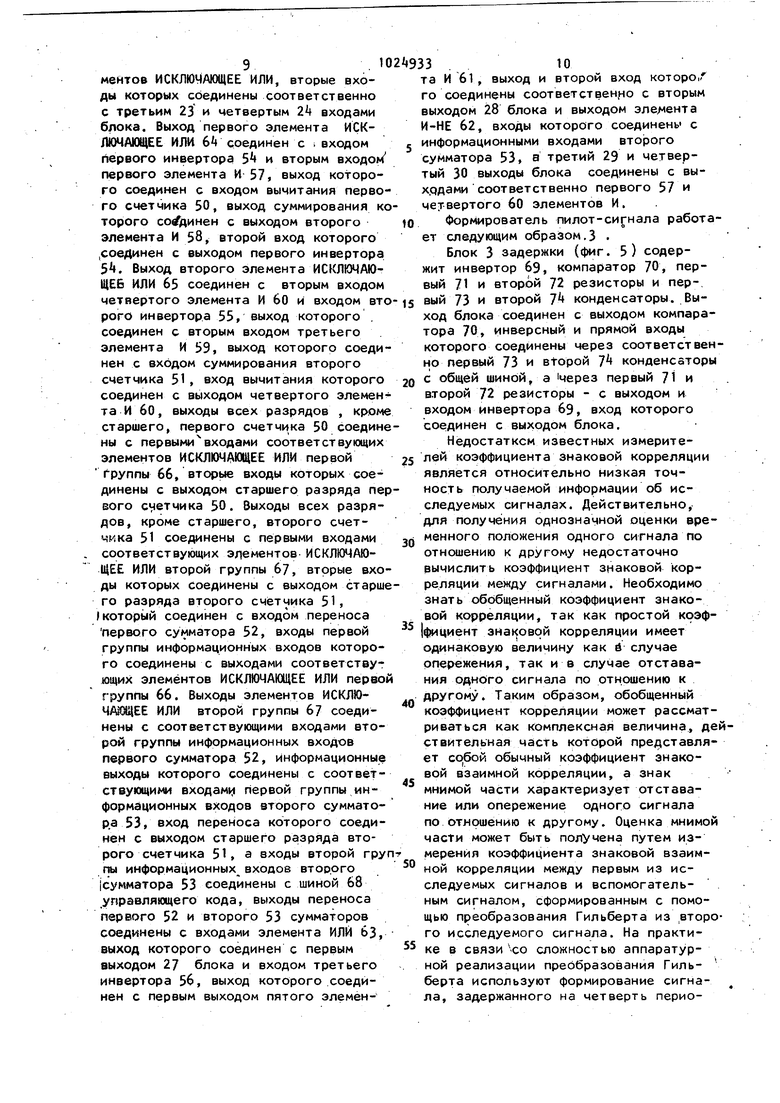

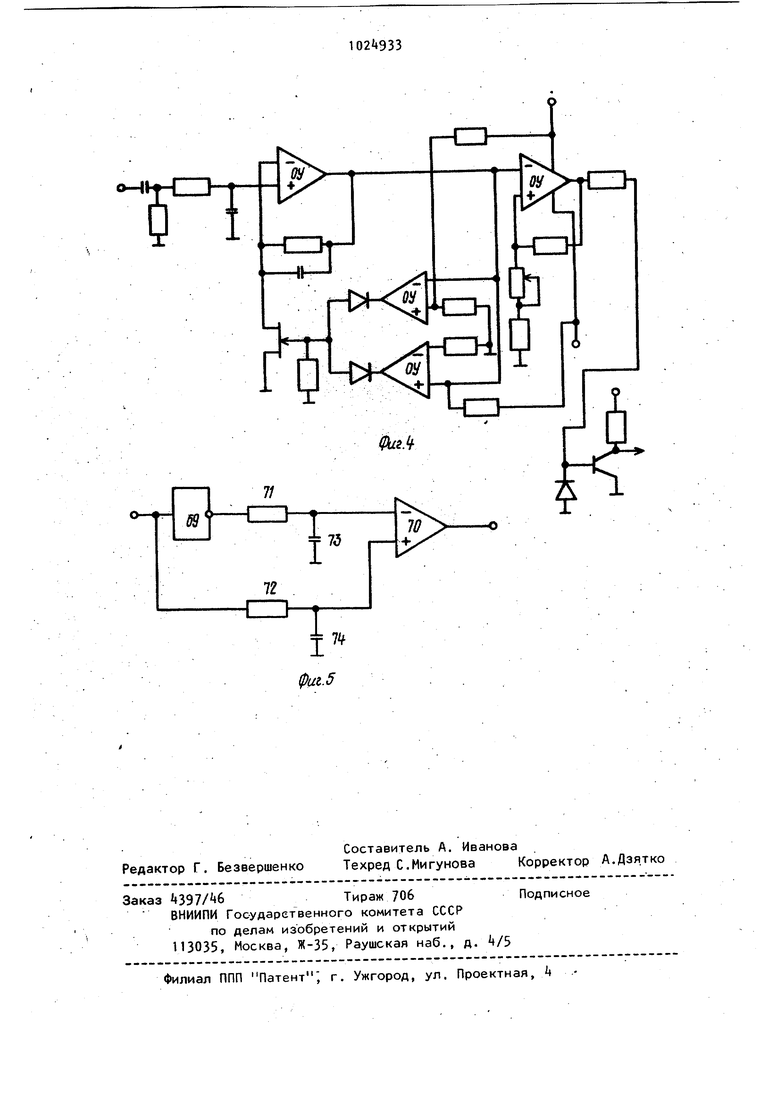

Поставленная цель достигается тем, что в знаковый коррелятор, содержащий первый и второй усилители-ограничители, входы которых соответст-венно являются Первым и вторым входами коррелятора, переключатель, генератор тактовых импульсов, блок задержки, делитель частоты и реверсивный счетчик, входы суммирования и вычитания которого срединены соответственно с выходами первого и второго элементов И, введены блок управления, блок измерения оценок коэффициентов корреляции, формирователь пил от-си гнал а, формирователь импульсов, элемент задержки и регистратор, причек выходы разрядов реверсивного счетчика соединены с управляющими входами делителя частоты, информационный входкоторого объединен с первым входом блока измерения оценок коэффициентов корреляции и подключен к выходу генератора тактовых импульсов, вых,оц делителя частоты соединен с пер вым входом блока управления, второй и третий входы которого объединены соответственно с первым и вторым входами переключапеля и подключены соответственно к выходам первого и второго усилителей-ограничителей, выход Btoporo усилителя-ограничителя соединен с входом блока задержки, выход которого соединен с четве тым входом блока управления, пятый вход которого объединен с первыми входами первого и второго элементов И, вторым входом блока измерения оц нок коэффициентов корреляции, входо элемента задержки и подключен к вых ду формирователя импульсов, первый и второй выходы блока управления соответственно соединены с вторыми входами первого и второго элементов И, а третий и четвертый выходы блока управления соответственно соединены с третьим и четвертым входами блока измерения оценок коэффициентов корреляции, выходная шина которого соединена с информационны входом регистратора, управляющий вход которого соединен с выходом эл мента задержки, вход формирователя импульсов соединен с выходом переключателя, третий вход которого с единен с выходом формирователя пилот-сигнала, вход которого является третьим входом коррелятора; Крйме того, блок измерения оценок коэффициентов корреляции содержит первый, второй и третий счет ки , дешифратор, преобразователь.кодов, первый и второй регистры, элемент памяти, первый и второй элементы И, первый и второй элементы И-ИЛИ-НЕ, триггер и элемент ИЛИ, причем вход начальной установки пер вого счетчика является первым входо блока , выходы разрядов первого счетчика соединены с соответствующи ми входами дешифратора, первый выхо которого соединен с первым входом п вого элемента И,выход которого соединен со счетным входом первого счетчика, второй выход первого элемента И объединен с первым входом первого элемента И-ИЛИ-НЕ и является вторым входом блока, второй первого элемента И-ИЛ является третьим входом блока, третий вход первого элемента И-ИЛИ-НЕ объединен с первым входом второго элемента И-ИЛИ-НЕ и подключен к нулевому выходу триггеpa, единичный выход которого соединен с первым входом элемента ИЛИ, четвертым входом первого элемента И-ИЛИ-НЕ и вторым входом второго элемента И-ИЛИ-НЕ, третий вход кото- , рого является четвертым входом блока, четвертый выход второго элемента И-ИЛИ-НЕ соединен с выходом старшего разряда второго счетчика, счетный вход которого соединен с выходом первого элемента И-ИЛИ-НЕ, выходы разрядов второго счетчика соединены с соответствующими входами I первой группы входов преобразователя,кодов, входы второй группы входов которого соединены с соответствующими выходами разрядов третьего счетчика, счетный вход которого соединен с выходом второго элемента И-ИЛИ-НЕ, выходы преобразователя кодов соединены с соответствующими информационными входами первого регистра и адресными входами элемента памяти, вход записи-считыйания которого соединен с выходом элемента ИЛИ, второй вход которого подключен к второму выходу дешифратора,, информационные входы элемента памяти соединены с соответствующими выходами разрядов второго регистра, выходы элемента памяти соединены с соответствующими входами первой группы входов сумматора, входы второй группы входов которого, кроме первого входа, объединены и соединены с шиной нулевого логического сигна ла, а первый вход второй группы входов сумматора соединен с шиной единичного логического сигнала, информационные выходы сумматора соединены с соответствующими информационными входами второго регистра, вход тактовых импульсов которого объединен с первым входом второго элемента И и подключен к третьелчу выходу дешифратора, четвертый выход 1 оторого соединен с входами-начальной установки второго и третьего счетчиков, вход начальной установки второго регистра соедине1Н с единичным -выходом триггера, нулевой вход которого соединен с выходом старшего разряда третьего счетчика, единичный вход триггера объединен с входом тактовых импульсов первого регистра и подключен к выходу второго элемента И, второй вход которого подключен к выходу переноса сумматора, выходы первого регистра являются соответствующими выходами блока. При этом блок управления содержит первый и второй счетчики, первый и второй сумматоры, первый, второй и третий инверторы, первый, второй, третий, четвертый и пятый элементы И, элемент И-НЕ, элемент ИЛИ, первый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, а также первую и вторую гру пы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, причем управляющие входы первого, второго, третьего и четвертого элементов И , объединены, и подключены к первому входу блока, первый вход первого эл мента ИСКЛЮЧАЮЩЕЕ ИЛИ объединен с первым входом второго элемента ИСКЛЮ ЧАЮЩЕЕ ИЛИ и Является вторым входом блока, вторые входы первого и второ,го элементов ИСКЛЮЧАЮЩЕЕ ИЛИ являются соответственно третьим и четверты входами блока, выходы первого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соеди ны соответственно с информационными входами первого и четвертого элементов И и входами первого и второго инверторов соответственно, выходы которых соединены соответственно с информационными входами второго и третьего элементов И, выходы которых соединены соответственно с входами суммирования первого и второго счетчиков, входы начальной уста новки которых объединены и являются пятым входом блока, выходы разря дов первого и второго счетчиков, кроме старшего разряда, соединены со ответствен но. с соответствующими nepвыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ первый и второй групп, вторые вх ды элементов ИСКЛЮЧАЮЩЕЕ ИЛИ первый и второй групп объединены в каждой из групп, а также объединены соответственно с входами переноса .первого и второго сумматоров и подключены соответственно к выходам старшего разряда первого и второго счетчиков, входы первой и второй групп информационных входов первого сумматора подключен соответственно к соо ветствующим выходам элементов ИСКЛ)Ч/МОЩЕЕ ИЛИ первой и втброй групп, информационные выходы первого сумматора соединены с соответствующими ин формационными входами первой группы входов второго сумматора, информационные входы второй группы входов которого соединены с шиной управляю/ щего кода, информационные выходы . второго сумматора соединены с соответствующими входами элемента И-НЕ, выход которого соединен с информационным входом пятого элемента И, управляющий вход которого соединен с выходом третьего инвертора, вход которого объединен с выходом элемента ИЛИ и является первым вуходом блока, первый и второй входы элемента, ИЛИ соединены соответствен/ но с выходами переноса первого и второго сумматоров, выход пятого элемента И является вторым выходом блока, выходы первого и четвертого элементов И объединены соответственно с входами вычитания первого и второго сумматоров и является соответственно третьим и четвертым выходами блока управления. На фиг. 1 представлена структурная схема предлагаемого коррелятора; на фиг, 2 - структурная схема блока измерения; на фиг. 3 - струк-. турная схема блока управления, на .фиг. - структурная схема формирователя пилот - сигналаJ на фиг. 5 структурная схема блока задержки. Коррелятор содержит (фиг. 1 ) генератор 1 тактовых импульсов, формирователь 2 импульсов, блок 3 задержки, первый k и второй 5 усилители-ограничители, переключатель 6, делитель 7 частоты и реверсивный счетчик 8. входы суммирования и вычитания которого соединены с выходами соответственно первого 9 и второго 10 элементов И, а входы первого и второго 5 усилителей-ограничителей соответственно с первым 11 и вторым 12 входами коррелятора. Коррелятор также содержит блок 13 управления, 14 измерения оценок коэффициентов корреляции, формирователь 15 пилотсигнала и элемент 1б задержки, выход и ВХОД которого соединены соответтвенно с управляющим входом регистратора 1 и выходом формирователя 2 импульсов, который соединен с первым входом 18 блока 1 измерения, выходная шина 19 которого соединена с информационным входомрегистратора 17. Второй вход 20 блока 1 измерения оценок коэффициентов корреляции соединен с выходом генератора 1 тактовых импульсов и входом делителя 7 частоты, выход которого соединен с первым входом 21 блока 13 управления,- второй 22, третий 23 и четвертый 2k входы которого соединены с выходами соответственно первого 4 и второго 5 усилителей-ограничителей и блока 3 за-: держки, ВХОД которого соединен с выхо дом второго усилителя-ограничителя 5 и первым неподвижным контактом/переключателя 6, второй и третий неподвижные контакты которого соединены с выходами соответственно первого усилителя-ограничителя 4 и формиро. вателя 15 пилот-сигнала, вход которого соединен с третьим входом 25 коррелятора. Подвижный контакт переключателя 6 соединен с входом формирователя 2 импульсов, выход которого соединен с пятым входом 26 блока 13 управления, первый 27 и второй 28 выходы которого соединены с первыми, входами соответственно первого 9 и второго 10 элементов И, вторые входы которых соединены с выходом формирователя 2 импульсов, выходы ревереивно го счетчика 8 соединены с управляющими входами делителя 7 частоты, а третий 29 и четвертой 30 выходы блока 13 управления соединены соответственно с третьим 31 и четвертым

32 входами блока Tt измерения оценок коэффициентов корреляции,

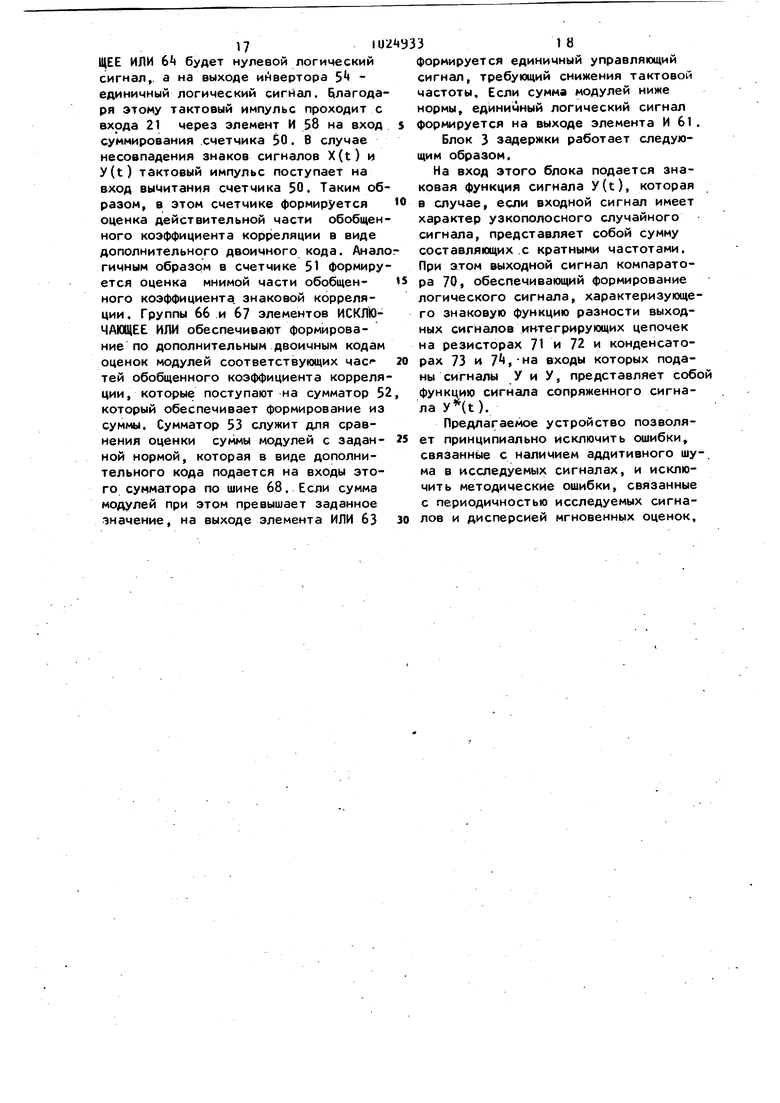

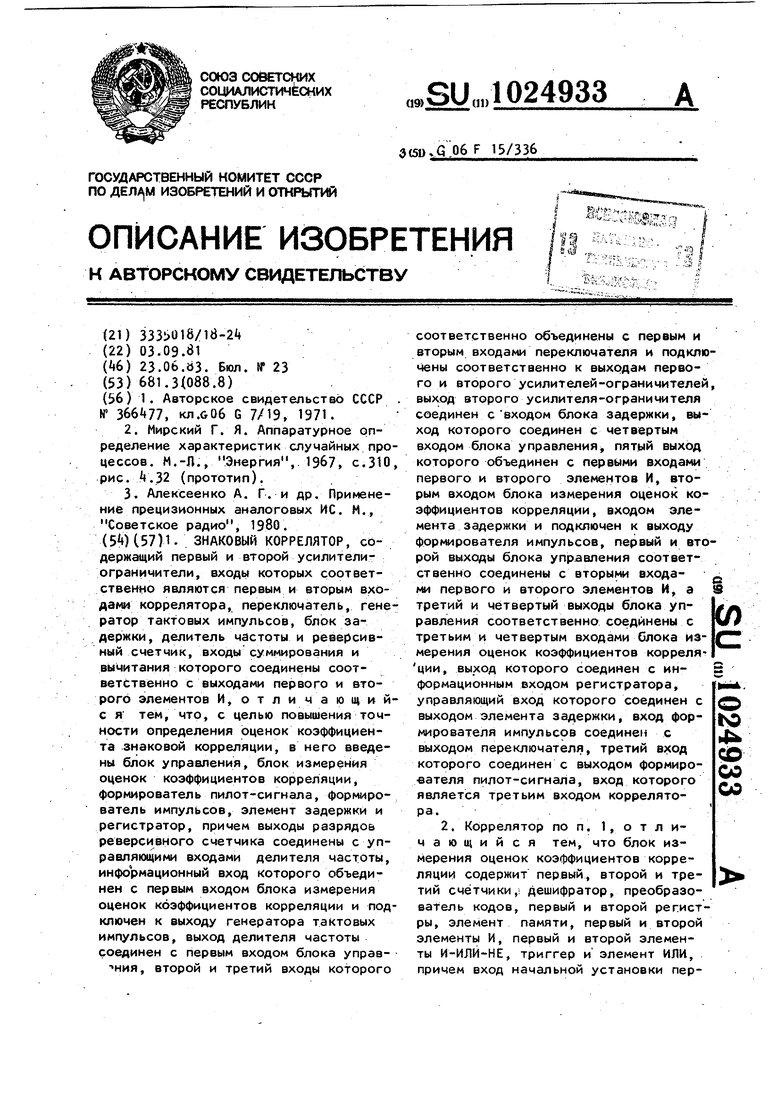

Блок1 измерения оценок коэффициIентов корреляции (фиг. 2) содержит первый 33, второй З и третий 35 счетчики, дешифратор 36, преобразователь 37 кодов, первый 38 и второй

39 регистры, сумматор 40, элемент 41 памяти, первый 42 и второй 43 элементы И, элемент ИЛИ 44 и триггер 45, единичный выход которого соединен с входом начальной установки первого регистра 38, первым входом элемента ИЛИ 44, а также первыми входами первого 46 и второго 47 элементов И-ИЛИ-НЕ. Первый вход 18 блока соединен с входом начальной установки первого счетчика 33, счетный вход и выходы которого соединены соответственно с выходом первого элемента И 42 и входами дешифраторами Зб, первый выход которого соединен с первым входом второго элемента И 43 и входом тактовых импульсов первого регистра 38, выходы которого соединены с информационными входами элемента 41 памяти, выход которого соединены с соответствуюш ми входами первой группы входов сумматора 40, вход первого разряда второй группы которого соединен с шиной 48 единичного лог гического сигнала, а все остальные входы второй группы входов сумматора 40 соединены с шиной 49 нулевого логического сигнала. Выходы сум10

выходами преобразователя 37 кодов, выход первой и второй группы входов которого соединены с соответствующими выходами второго 34 и третьего 35 счетчиков. Выход старшего разряда второго счетЧика 34 соединен с вторым входом второго элемента И-ИЛИ-НЕ 47, выход которого соединен с счетным входом третьего счетчика 35.

Нулевой выход триггера 45 соединен с (Третьими входами первого 46 и второго 47 элементов И-ИЛИ-НЕ, четвертые входы которых соединены соответственно с третьим 31 и четвертым 32 входами блока, выход первого элемента И-ИЛИ-НЕ 46 соединен со счетным входом второго счетчика 34, вход начальной установки которого соединен с входом начальной установки третьего счетчика Зб и третьим выходом дешифратора 36, четвертый выход которого соединен с вторым входом первого элемента И 42.

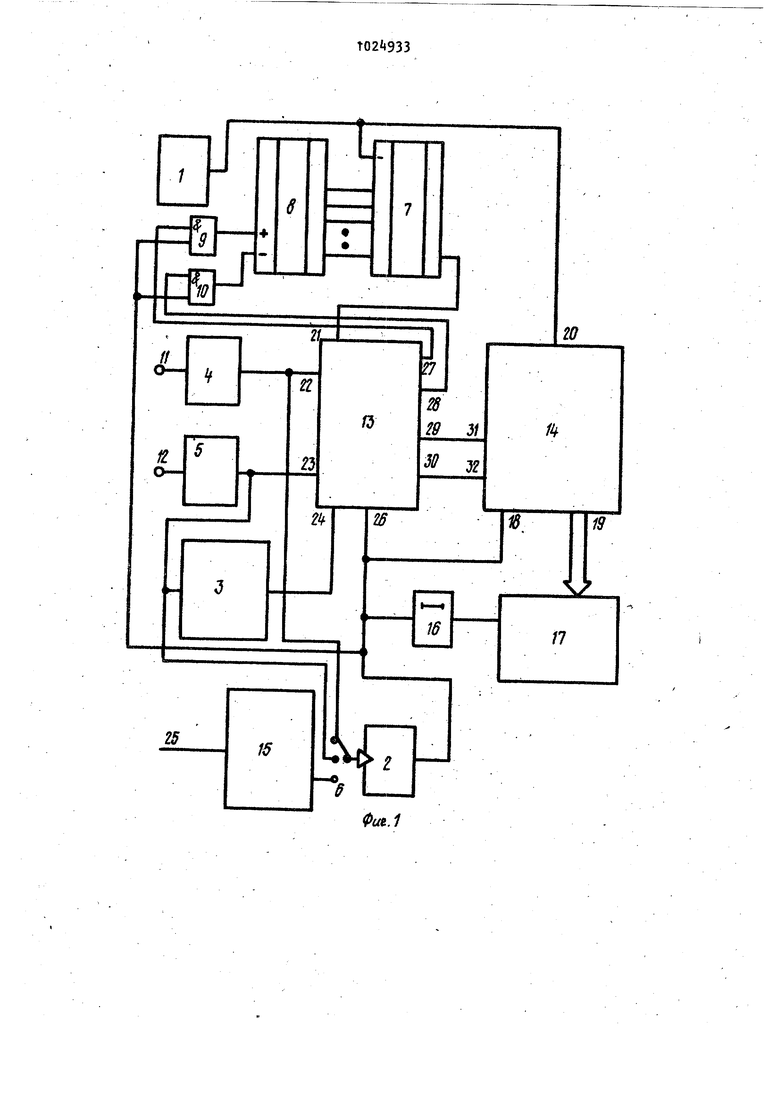

Блок 13 управления, (фиг. 3) содержит первый 50 и второй 51 счетчики, первый 52 и второй 53 сумматоры, первый 54, второй 55 и третий 6 инверторы, первый 57, второй 58, третий 59. четвертый 60 и пятый 61 элементы И, элемент И-НЕ б2, элемент

ИЛИ 63, первь1Й 64 и второй б5 элементы ИСКЛЮЧАЮЩЕЕ ИЛИ,а также первую 66 и вторую 67 группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, Первый вход 21 блока соединен с первыми входами первого 57, второго 58, третьего 59 и четвертого 60 элементов И. Второй вход 22 блока 13 соединен с первыми входами первого 64 и второго 65 эле38матора tO соединены с информационными входами первого регистра 38, а выход переноса сумматора lO соединен с вторым входом второго элемента ЦЗ, выход которого соединен с единичным входом триггера 5 и входом тактовых импульсов второго регистра 39, выходы которого соединены с соответствующими выходами выходной шины 19 блоКЗ 14 измерения, второй вход 20 которого соединен с вторым входом первого элемента И-ИЛИ-НЕ 6, а также соединен с первым входом первого элемента И 2, второй выход дешифратора Зб соединен с вторым входом элемента ИЛИ Ц, выход которого соединен с входом управления записью считыванием элемента 1 памяти, адресные входы которого соединены с информационными входами второго регистра 39 и 9. 1 ментов ИСКЛЮЧАЮЩЕЕ ИЛИ, вторые входы которых соединены соответственно с третьим 23 и четвертым 2k входами блока. Выход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ б соединен с . входом hepBoro инвертора 5 и вторым входом первого элемента И 57, выход которого соединен с входом вычитания перво го счетчика 50, выход суммирования к торого со/динен с выходом второго элемента И 58, второй вход которого .соединен с выходом первого инвертора Б. Выход второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ б5 соединен с вторым входом четвертого элемента И 60 и входом вт рого инвертора 55, выход которого соединен с вторым входом третьего элемента И 59, выход которого соеди нен с входом суммирования второго счетчика 51, вход вычитания которого соединен с выходом четвертого элемен та И 60, выходы всех разрядов , кроме старшего, первого счетчика 50 соедине ны с первыми входами соответствующих элементов ИСКЛЮЧАЮЩЕЕ ИЛИ первой (труппы 66, вторые входы которых соединены с выходом старшего разряда пе вого С1нетчика 50. Выходы всех разрядов, кроме старшего, второго счетчика 51 соединены с первыми входами соответствующих элементов ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы б7, вторые вхо ды которых соединены с выходом старш го разряда второго сч1етчика 51, I который соединен с входом переноса первого сумматора 52, входы первой группы информационных входов которого соединены с выходами соответствующих элементов ИСКЛЮЧАЮЩЕЕ ИЛИ перво группы 66. Выходы элементов ИСКЛЮЧ/ШДЕЕ ИЛИ второй группы 67 соединены с соответствующими входами второй группы информационных входов первого сумматора 52, информационные выходы которого соединены с соответствующими входам ; первой группы информационных входов второго сумматора 53, вход переноса которого соединен с выходом старшего разряда второго счетчика 51, а входы второй гру пы информационных входов второго сумматора 53 соединены с шиной 68 угфавляющего кода, выходы переноса первого 52 и второго 53 сумматоров соединены с входами элемента ИЛИ 63, выход которого соединен с первым выходом 27 блока и входом третьего инвертора 56, выход которого соединен с первым выходом пятого элемен3та И 61 , выход и второй вход которо, го соединены соответствен но с вторым выходом 28 блока и выходом эле 1ента И-НЕ 62, вхоДы которого соединены с информационными входами второго сумматора 53, а третий 29 и четвертый 30 выходы блока соединены с выхддами соответственно первого 57 и четвертого 60 элементов И. Формирователь пилот-сигнала работает следукмцим образом.3 . Блок 3 задержки (фиг. 5) содержит инвертор 69, компаратор 70, первый 71 и второй 72 резисторы и пер-. вый 73 и второй 7 конденсаторы ход блока соединен с выходом компарапрямой входы тора 70, инверсный и через соответственкоторого соединены но первый 73 и второй 7 конденсаторы с общей шиной, а через первый 71 и второй 72 резисторы - с выходом и входом инвертора 69, вход которого соединен с выходом блока. Недостатком известных измерителей коэффициента знаковой корреляции является относительно низкая точность получаемой информации об исследуемых сигналах. Действительно, для получения однозначной оценки временного положения одного сигнала по отношению к другому недостаточно вычислить коэффициент знаковой корреляции между сигналами. Необходимо знать обобщенный коэффициент знаковой корреляции, так как простой коэф| циент знаковой корреляции имеет одинаковую величину как 6 случае опережения, так ив случае отставания одного сигнала по отношению к другому. Таким образом, обобщенный коэффициент корреляции может рассматриваться как комплексная величина, действительная часть которой представляет собой обычный коэффициент знаковой взаимной корреляции, а знак мнимой части характеризует отставание или опережение одного сигнала по отношению к другому. Оценка мнимой части может быть получена путем измерения коэффициента знаковой взаимной корреляции между первым из исследуемых сигналов и вспомогательным сигналом, сформированным с помощью преобразования Гильберта из второго исследуемого сигнала. На практике в связи СО сложностью аппаратурной реализации преобразования Гильберта используют формирование сигнала, задержанного на четверть периода, что может служить аппроксимацией преобразования Гильберта (с то ностью до знака). Однако при измерении сигналов с высоким содержанием аддитивного щума получаемые оценки знакового коэффициента корреляции указываются заниженными, так как.в качестве нормы при этом либо используется оценка среднеквадратичных значений сигналов (а она сильно зависит от шума) , либо нормирование вообще не производится. Анализ соотношений между коэффициентами знаковой взаимной корреляции показы вает, что результат оценки знаковых коэффициентов взаимной корреляции не зависит от уровня шума, если прлучаемые оценки нормируют по сумме модулей действ ительной и мнимой частей обобщенного коэффициента знаковой взаимной корреляции. Другой особенностью измерения обобщенных коэффици ентов корреляции двух узкополосных случайных процессов является наличие сравнительно большой дисперсии оцет нок, что вызывает необходимость; формирования некоторой статистической рценки функции распределения плотности вероятности мгновенных значений обобщенного коэффициента корреляции. Обычно для этой цели используется формирование средних значений. Однако, в связи с тем, что по существу получаемые оценки распределяются к распределению Мизеса, оценка по среднему возможна только при условии формирования тригонометрических функций от мгновенных значений оцет нок с последующим усреднением и обратным переходом через обратные триг нометрические функции, что весьма затрудняет аппаратурную реализацию и снижает быстродействие .Наиболее эффективным в данном слу чае оказывается оценка в виде моды фун«ции распределения плотности веро ятности мгновенных оценок, так как в этом случае исключаются возможные значительные методические оценки, присущие оценкам по среднему, медиане и центру размаха. Таким образом, для получения адекватной оценки знакового коэффициента корреляции, хара теризующего исследуемые процессы, необходимо провести нормирование по сумме модулей и поиск моды функции распределения, что и обеспечивается в предлагаемом устройстве. 312 Коррелятор работает следующим образом. Входные исследуемые сигнала X(t) и y(t) подаются на входы 11 и 12 . устройства, откуда они поступают на усилители-ограничит ели i и 5, которые обеспечивают выделение знаковой функции входных сигналов, причем положительному значению входного сигнала на выходе соответствующего усилителяограничителя соответствует единичный логический сигнал, а отрицательному или нулевому значению входного сигнала соответствует нулевой логический сигнал на выходе соответствую щего усилителя-ограничителя. Таким образом, выходные сигналы усилителейограничителей i и 5 могут быть представлены как X sign X(t) и У sign Y(t). Сформированный сигнал У подается на вход блока 3 задержки, который на своем выходе обеспечивает формирование сигнала, сдвинутого по фазе на 90 , т.е. по существу сопряженного логического сигнала. Сопряженный логический сигнал У , так же как и сигналы У и X.подается навходы блока 13 управления. Кроме этого, на первый вход блока 13 управления подается тактовый сигнал, а на пятый вход этого блокя поступает сигнал готовности, который обеспечивает начало нового цикла работы. Этот сигнал готовности формируется б виде импульса относительно малой длительности формирователем 2 импульсов, на вход которого подается либо специальный пилот-сигналj поступающий с входа 25 через формирователь 15 пи л от-си гнал а-, либо один из аанализируемых сигналов X или У, причем выбор требуемого сИгнала может быть обеспечен с помощью переключателя 6. При выборе сигнала следует руководствоваться сообраГениями наименьшей зашумленности сигнала, используемого для формирования импульса готовности. Если , например, один из исследуемых сигналов представляет собой чистый гармонический сигнал, а второй - аддитивную смесь узкополосного случайного сигнала и случайного шума, в качестве сигнала, используемого для формирования импульса готовности, может быть использован первый из указанных исследуемых сигналов. Если оба входных сигнала X{t) и y(t) являются узкополосными случайными сигналами с значительной примесью аддитивного случайного широкополосного шума, в качестве такого опорного сигнала может использоваться специальный пилот-сигнал, подаваемый на вход 25. При этом, так как этот сигнал используется для формирования информации о среднем периоде исследуемого сигнала, пилот-сигнал в общей случае может бь1ть не коррелирован с исследуе-ю мыми сигналами, а его период может быть кратен целому числу среднего значения полупериодов сравниваемых сигналов. Формирователь 15 пилот-сигнала при этом может выполнять функции как собственно формирователя импульсов, так при необходимости и фильтра или буферного усилителя. Один из вариантов структурной схемы такого фор мирователя (фиг. k) обеспечивает, например, выделение импульсного пилот-сигнала из смеси сигнал-шум при уровне шумов, достигающем 701 от уррвня полезногосигнала. Импульс готовности при поступлении на все узлы обеспечивает начало нового цикла работь. Импульсы от генератора 1 тактовых импульсов проходят на делитель 7 частоты, на выходе которого формируются импульсы тактовой частоты, частота которых зависит как от периода исследуемых сигналов (периода пилот-сигнала), так и соотношения сигнал/шум исследуемых сигналов. Частота этих импульсов определяется кодом поступающим на управляющие входы делителя 7 частоты с выходов реверсивного счетчика 8, работа которого определяется импульсами, поступающими от элементов И 9 и 10. Причем код, с одержащийся в реверсивном счет чике 8, может измениться при поступлении импульса готовности с выхода фо мирователя 2 импульсов, если на одном из выходов 27 или 28 блока 13 уп .равления в данный момент присутствуе единичный логический сигнал. Таким о ,разом, блок 13 управления обеспечива ет формирование управляющих сигналов на выходах 27 и 28 -таким образом, чт

если формируемые коэффициенты корреляции не удовлетворяют заданной норме, в качестве которой используется сумма модулей знаковых коэффициентов корреляции, на соответствующем выходе появляется единичный логический сигнал, вызывающий соответствующее изменение частоты такто10

ности вероятности обобщённого коэффициента корреляции. Получаемая оценка с выхода 19 блока Т4 поступает на регистратор 17, обеспечивающий 55 индикацию или регистрацию получаемой оценки в требуемой форме по задержанному импульсу готовности, формируемому элементом 16 задержки. 31 вых импульвов. Например, если сумма модулей действительного и мнимого знаковых коэффициентов корреляции должна быть равна 100, а фактически она меньше, на выходе 28 в момент появления импульса готовности присутствует единичный логический сигнал, открывающий второй элемент И 10, в результате чего импульс тотовности проходит через этот элемент И на вход вычитания счетчика 8. Код, зафиксированный счетчиком 8, при этом уменьшается, что вызывает соответствующее увеличение частоты на выходе делителя 7 частоты, так как подобное изменение кода вызывает уменьшение коэффициента деления. Увеличение частоты тактовых импульсов приводит к тому, что за время между двумя импульсами готовности поступает большее число тактовых импульсов, что вызывает увеличение формируемых коэффициентов знаковой корреляции. Если требования выполнения условий нормирования не удовлетворены, процесс коррекции тактовой частоты повторяется. При превышении суммой модулей коэффициентов знаковой корреляции уелоВИЯ нормирования аналогичным образом происходит уменьшение тактовой частоты импульсов. Блок 13 управления, кроме формирования управляющих сигналов на выходах 27 и 28, обеспечивает одновременно и формирование на выходах 29 и 30 нормированных оценок действительного и мнимого коэффициентов знаковой корреляции в виде число-импульсных кодов, которые поступают на входы 31 и 32 блока 1 измерения корреляции оценок коэффициентов. Исходными данными при этом для блока 13 управления служат сигналы Х.У и У. Блок I измерения оценок коэффициентов корреляции обеспечивает формирование по оценкам мгновенных значений действительного и мнимого коэффициентов знаковой корреляции и формирование оценки положения центра функции распределения плотБлок измерения оценок коэффициентов корреляции работает следующим образом. Мгновенные оценки действительной и мнимой частей обобщенного коэффициента знаковой корреляции в виде ч ло-импульсных кодов поступают на входы 31 и 32 соответственно и проходят на счетные входы второго 3 и третьего 35 счетчиков. Таким обра зом, на выходах этих счетчиков форм руются коды, представляющие оценки соответствующих частей обобщенного коэффициента знаковой ции,.Эти коды проходят через преобразователь 37 кодов и формируют адрес элемента 41 памяти, по которо му в данном случае должна быть при бавлена единица, т.е. адрес определ ет номер канала, соответствующий .одной из абсцисс гистограммы, формируемой в элементе 41 памяти и представляющей оценку функции распр далейия плотности вероятности cS6ci6щенного коэффициента корреляции. Пр этом код, хранящийся в данном адресе элемента 41 памяти, поступа ет на сумматор 40, где к нему прибавляется единица, после чего он поступает на входы регистра 38, куда и записывается по импульсу с пер вого выхода дешифратора 36. Дешифратор 36 служит для формирования последовательности импульсов. Начало его работы связано с поступлением импульса на вход 18, после чего счетчик 33 начинает считать импульсы высокой тактовой частоты, поступающие с входа 20 через элемент И 42. Первым импульсом с первого выхода дешифратора 36 обес печивается запись нового кода суммы в регистр 38, а также oripoc триггера 45 через элемент И 45. Если по данному каналу сумма накопленных отсчетов достиглаграничного значения, что проявляется в наличии сигнала переноса на выходе сумм тора 40, импульс проходит на вход установки триггера 45 и устанавливает его в единичное состояние. При этом переключатся элементы И-ИЛИ-НЕ 46 и 47 и очищается регистр 38, а элемент 41 памяти переходит в режим записи. Импульсы высокой ч актовой частоты с входа 20 поступают на вход счетчика 34, а с его выхода - на вход счетчика 35. Коды (а выходах з этих сметчиков последовательно изменяются, что вызывает перебор всех адресов на выходе преобразователя 37 кодов адресном входе элемента 41 памяти, а так как оно находится в режиме записи и на его информационные входы с выхода регистра 38 поступает нулевой код, происходит очистка элемента 41 памяти. Однако еще до начала очистки импульсом, устанавливающим триггер 45 в единичное состояние, обеспечена запись в регистр 39 адреса, по которому достигнуто максимальное значение, т.е. оценка центра распределения функции распределения плотности вероятности. После очистки элемента 41 памяти импульсом с выхода переноса счетчика 34 триггер 45 устанавливается снова в нулевое состояние.;Если в данном цикле получение оценки максимума функции распределения плотности вероятности не зафиксировано, т.е. триггер 45 не перешел в единичное состояние, в регистре 39 продолжает храниться предьщущая оценка положения максимума (моды) функции распределения, а импульсом с второго выхода дешифратора 36 обеспечивается запись нового знамения суммы в соответствующий канал элемента 41 памяти. Третий импульс с третьего выхода де-( шифратора обеспечивает сброс счетчиков 34 и 35 в нулевое состояние, а сигналом с четвертого выхода дешифратора 36 запирается элемент И 42, чем блокируется дальнейшее изменение кода на выходе счетчика 33 .до поступления следующего . импульса на вход 18. Блок 13 управления работает следующим образом. Сигналы X, У и У поступают на входы 22-24, соответственно, а на вх,рд 21 поступает тактовый..сиг нал. На выходе первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 64 формируется функция несовпадения знаков сигналов X и У, а на выходе второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ б5 формируетс я функция несовпадения знаков сигналов X и У. Соответствующие им инверсные функции формируются на выходах инверторов 54 и 55. Если в данный момент времени сиг ч налы X(t) и y(t) имеют одмнаковые знаки, на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ б будет нулевой логический сигнал,, а на выходе ийвертора 5 единичный логический сигнал. Магодаря этому тактовый импульс проходит с входа 21 через элемент И 58 на вход суммирования .счетчика 50. В случае несовпадения знаков сигналов X(t) и y(t) тактовый импульс поступает на вход вычитания счетчика 50. Таким образом, в этом счетчике формируется оценка действительной части обобщенного коэффициента корреляции в виде дополнительного двоичного кода. Анало гичным образом в счетчике 51 формируется оценка мнимой части обобщенного коэффициента, знаковой корреляции. Группы 66 и 67 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ обеспечивают формирование по дополнительным двоичным кодам оценок модулей соответствующих час тей обобщенного коэффициента корреляции, которые поступают на сумматор 52 который обеспечивает формирование из суммы. Сумматор 53 служит для сравнения оценки суммы модулей с заданной нормой, которая в виде дополнительного кода подается на входы этого сумматора по шине 68. Если сумма модулей при этом превышает заданное значение, на выходе элемента ИЛИ 63 10 3 формируется единичный управляющий сигнал, требующий снижения тактовой частоты. Если сумма модулей ниже нормы, единичный логический сигнал формируется на выходе элемента И 61. Блок 3 задержки работает следующим образом. На вход этого блока подается знаковая функция сигнала y(t), которая в случае, если входной сигнал имеет характер узкополосного случайного сигнала, представляет собой сумму составляющих .с кратными частотами. При этом выходной сигнал компаратора 70) обеспечивающий формирование логического сигнала, характеризующего знаковую функцию разности выходных сигналов интегрирующих цепочек на резисторах 7 и 72 и конденсаторах 73 и 7,-на входы которых поданы сигналы У и У, представляет собой функцию сигнала сопряженного сигнала y(t). Предлагаемое устройство позволяет принципиально исключить ошибки связанные с наличием аддитивного шума в исследуемых сигналах, и исключить методические ошибки, связанные с периодичностью исследуемых сигналов и дисперсией мгновеннь1Х оценок.

«б

71

TV

ч

X

в

ч. ч.

ч.

4Й

«I

V

0

LTT «

45

j-ii

f «M itHZD

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР | |||

| Vf , кллОб G 7/19, 1971 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Я | |||

| Аппаратурное определение характеристик случайных процессов | |||

| М.-П., Энергия, | |||

| Запальная свеча для двигателей | 1924 |

|

SU1967A1 |

| Способ образования коричневых окрасок на волокне из кашу кубической и подобных производных кашевого ряда | 1922 |

|

SU32A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Г | |||

| и др | |||

| Применение прецизионных аналоговых ИС | |||

| М., Советское радио, 1980 | |||

Авторы

Даты

1983-06-23—Публикация

1981-09-03—Подача