1

(21)4716180/24 (22) 06.07.89 (46)07.07.91. Бюл. Ms 25

(71)Пермский политехнический институт

(72)Л. Ф. Викентьев, В. А. Гофман, О. Л. Лепихина и А. А. Клюкин (53)681.327.66(088.8)

(56) Букреев И. Н., Мансуров В. П., Горячев В. И. Микроэлектронные схемы цифровых устройств. - М.: Советское радио, 1975, с. 59, рис. 2.4,а.

Автоматное управление асинхронными процессами в ЭВМ и дискретных системах/ /Под ред. В. И, Варшавского. - М.: Наука, 1986, с. 98, рис. 4.9,6.

(54) АСИНХРОННЫЙ ТРИГГЕР (57) Изобретение относится к вычислительной технике, а точнее к устройствам памяти, и может быть применено в устройствах автоматики и связи. Целью изобретения является расширение области применения триггера за счет возможности управления его логической функцией. Цель достигается тем, что асинхронный триггер содержит инвертор 14 и с пятого по девятый элементы И-НЕ 9-13 с соответствующими связями. Входы элементов И-НЕ 11-13 и инвертора 14 являются информационными входами триггера. В зависимости от сигналов на них триггер выполняет функции RS-, R-, S-. IK-, Т-, VD- и D-триггеров. 1 ил., 1 табл

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофункциональный настраиваемый триггер | 1988 |

|

SU1642582A1 |

| Многофункциональный тактируемый триггер | 1985 |

|

SU1307540A1 |

| Апериодический многофункциональный триггер | 1990 |

|

SU1746515A1 |

| Многофункциональный тактируемый триггер с управлением по срезу тактового сигнала | 1986 |

|

SU1359885A1 |

| Апериодический многофункциональный триггер | 1990 |

|

SU1746516A1 |

| ДВУХТАКТНЫЙ САМОСИНХРОННЫЙ RS-ТРИГГЕР С ПРЕДУСТАНОВКОЙ И ВХОДОМ УПРАВЛЕНИЯ | 2008 |

|

RU2390093C1 |

| САМОСИНХРОННЫЙ ДИНАМИЧЕСКИЙ ДВУХТАКТНЫЙ D-ТРИГГЕР С ЕДИНИЧНЫМ СПЕЙСЕРОМ | 2018 |

|

RU2693319C1 |

| Устройство для измерения площади непрозрачных плоских фигур | 1989 |

|

SU1663431A1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ РТСМ | 2008 |

|

RU2390930C2 |

| Самосинхронный двухтактный триггер с парафазными входными и выходными сигналами с нулевым спейсером | 2024 |

|

RU2835382C1 |

Изобретение относится к вычислительной технике, а точнее к устройствам памяти, и может быть применено в устройствах автоматики и связи. Целью изобретения является расширение области применения триггера за счет возможности управления его логической функцией. Цель достигается тем, что асинхронный триггер содержит инвертор 14 и с пятого по девятый элементы И - НЕ 9 - 13 с соотвтствующими связями. Входы элементов И - НЕ 11 - 13 и инвертора 14 являются информационными входами триггера. В зависимости от сигналов на них триггер выполняет функции RS-,R-,S-,JK-,T-,VD-,и D-триггеров. 1 ил.

fe

Os

о

00 GO

Изобретение относится к вычислительной технике, а точнее к устройствам памяти, и может быть применено в устройствах автоматики и связи.

Целью изобретения является расширение области применения триггера за счет возможности управления его логической функцией.

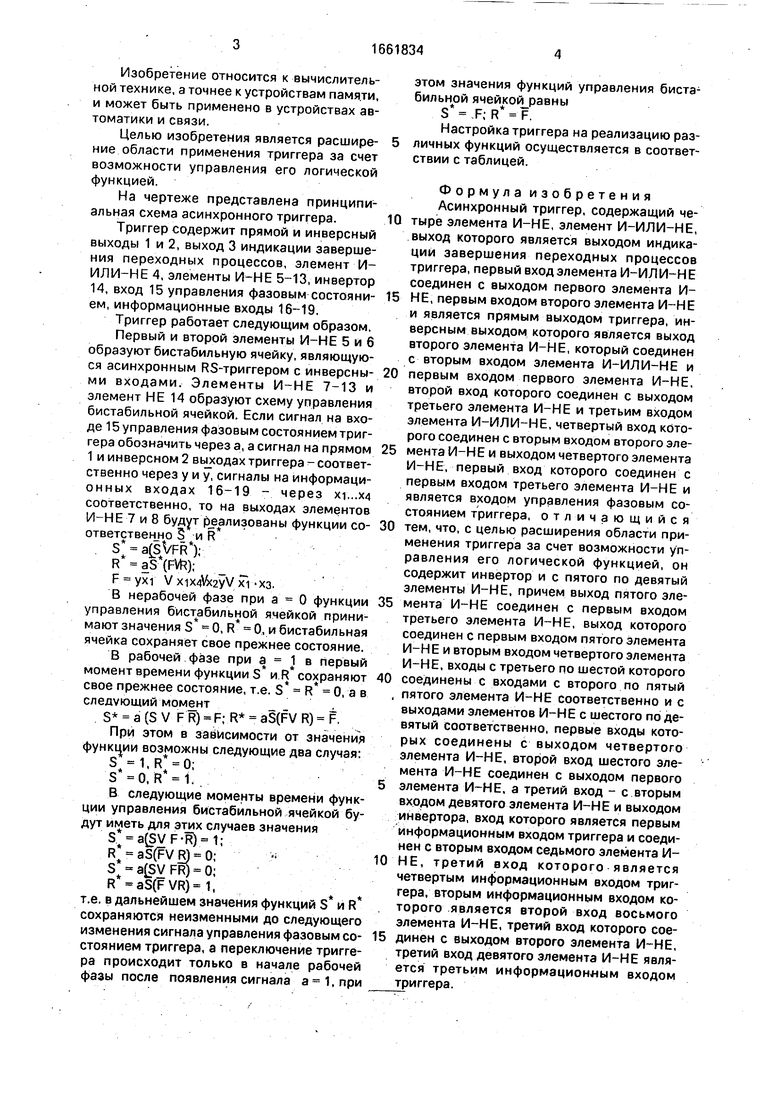

На чертеже представлена принципиальная схема асинхронного триггера.

Триггер содержит прямой и инверсный выходы 1 и 2, выход 3 индикации завершения переходных процессов, элемент И- ИЛИ-НЕ 4, элементы И-НЕ 5-13, инвертор 14, вход 15 управления фазовым состоянием, информационные входы 16-19.

Триггер работает следующим образом.

Первый и второй элементы И-НЕ 5 и 6 образуют бистабильную ячейку, являющуюся асинхронным RS-триггером с инверсными входами. Элементы И-НЕ 7-13 и элемент НЕ 14 образуют схему управления бистабильной ячейкой. Если сигнал на входе 15 управления фазовым состоянием триггера обозначить через а, а сигнал на прямом 1 и инверсном 2 выходах триггера - соответственно через у и у, сигналы на информаци- онных входах 16-19 - через xi,..x4 соответственно, то на выходах элементов И-НЕ 7 и 8 будут реализованы функции соответственно 3 и R

S aJsVFR);

R aS(FVR);

F yX1 V XI -X3.

В нерабочей фазе при а 0 функции управления бистабильной ячейкой принимают значения S 0, R 0, и бистабильная ячейка сохраняет свое прежнее состояние.

В рабочей фазе при а 1 в первый момент времени функции S nR сохраняют свое прежнее состояние, т.е. S R 0, а в следующий момент L

S a (S V F R) -F; R aS(FV R) F.

При этом в зависимости от значения функции возможны следующие два случая:

S 1,R 0;

S 0, R 1.

В следующие моменты времени функции управления бистабильной ячейкой будут иметь для этих случаев значения

S a(SVF-R) 1;

R aS(FV R) 0;

S - a(SV FR) 0;

R aS(FVR)1,

т.е. в дальнейшем значения функций S и R сохраняются неизменными до следующего изменения сигнала управления фазовым состоянием триггера, а переключение триггера происходит только в начале рабочей фазы после появления сигнала а-1,при

этом значения функций управления бистабильной ячейкой равны S R R F.

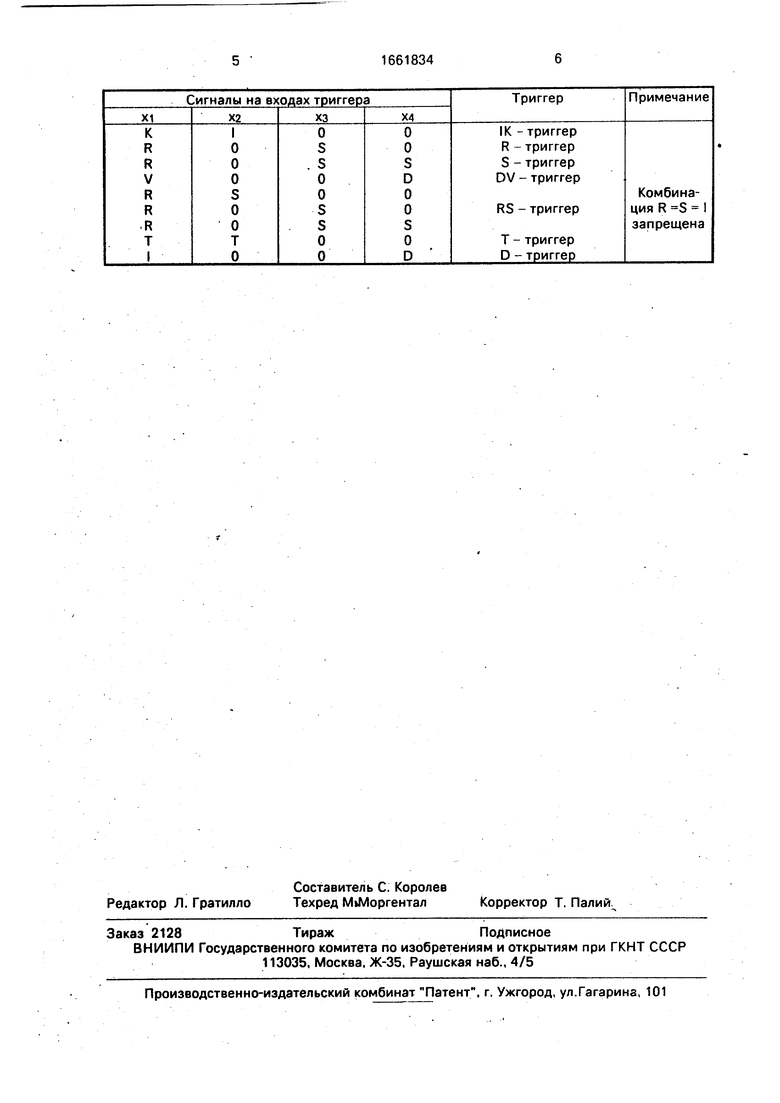

Настройка триггера на реализацию раз- личных функций осуществляется в соответствии с таблицей.

Формула изобретения Асинхронный триггер, содержащий че0 тыре элемента И-НЕ, элемент И-ИЛИ-НЕ, выход которого является выходом индикации завершения переходных процессов триггера, первый вход элемента И-ИЛИ-НЕ соединен с выходом первого элемента И5 НЕ, первым входом второго элемента И-НЕ и является прямым выходом триггера, инверсным выходом которого является выход второго элемента И-НЕ, который соединен с вторым входом элемента И-ИЛИ-НЕ и

0 первым входом первого элемента И-НЕ, второй вход которого соединен с выходом третьего элемента И-НЕ и третьим входом элемента И-ИЛИ-НЕ, четвертый вход которого соединен с вторым входом второго эле5 мента И-НЕ и выходом четвертого элемента И-НЕ, первый вход которого соединен с первым входом третьего элемента И-НЕ и является входом управления фазовым состоянием триггера, отличающийся

0 тем, что, с целью расширения области применения триггера за счет возможности управления его логической функцией, он содержит инвертор и с пятого по девятый элементы И-НЕ, причем выход пятого эле5 мента И-НЕ соединен с первым входом третьего элемента И-НЕ, выход которого соединен с первым входом пятого элемента И-НЕ и вторым входом четвертого элемента И-НЕ, входы с третьего по шестой которого

0 соединены с входами с второго по пятый . пятого элемента И-НЕ соответственно и с выходами элементов И-НЕ с шестого по девятый соответственно, первые входы которых соединены с выходом четвертого элемента И-НЕ, второй вход шестого элемента И-НЕ соединен с выходом первого 5 элемента И-НЕ, а третий вход - с вторым входом девятого элемента И-НЕ и выходом инвертора, вход которого является первым информационным входом триггера и соединен с вторым входом седьмого элемента И0 НЕ, третий вход которого является четвертым информационным входом триггера, вторым информационным входом которого является второй вход восьмого элемента И-НЕ, третий вход которого сое5 динен с выходом второго элемента И-НЕ, третий вход девятого элемента И-НЕ является третьим информационным входом триггера.

Авторы

Даты

1991-07-07—Публикация

1989-07-06—Подача