Изобретение относится к измерительной и информационной технике и может быть использовано в устройствах измерения частоты вращения.

Целью изобретения является повышение надежности и точности.

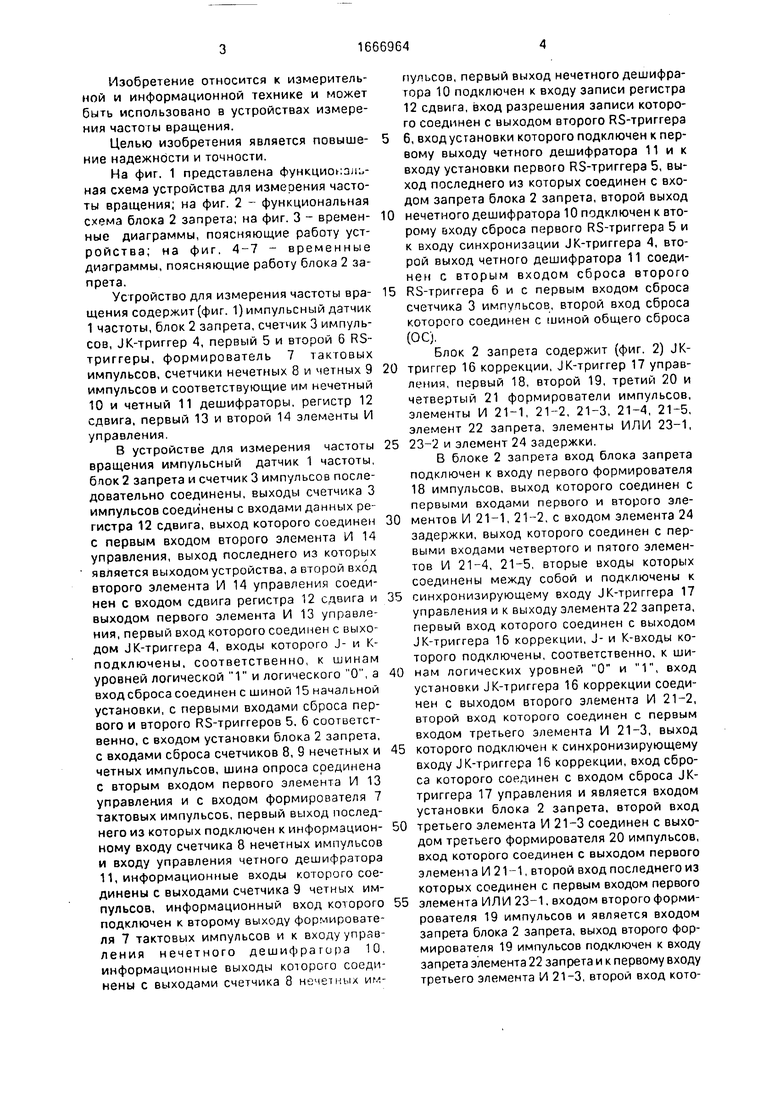

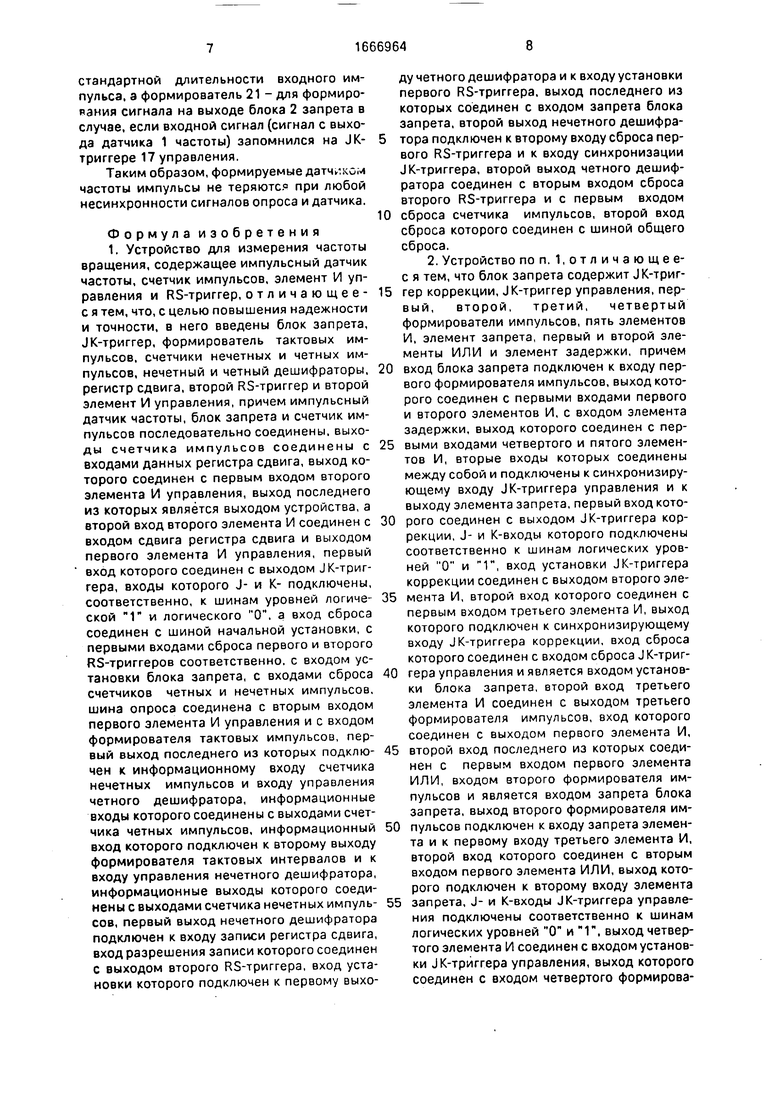

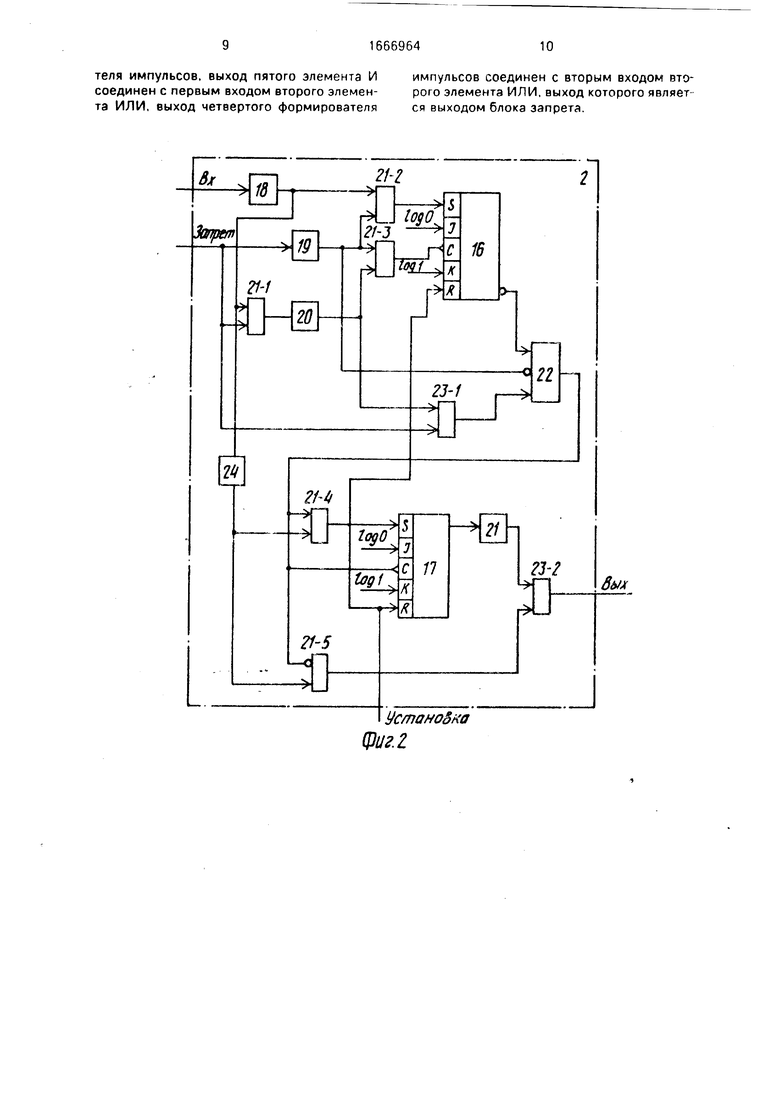

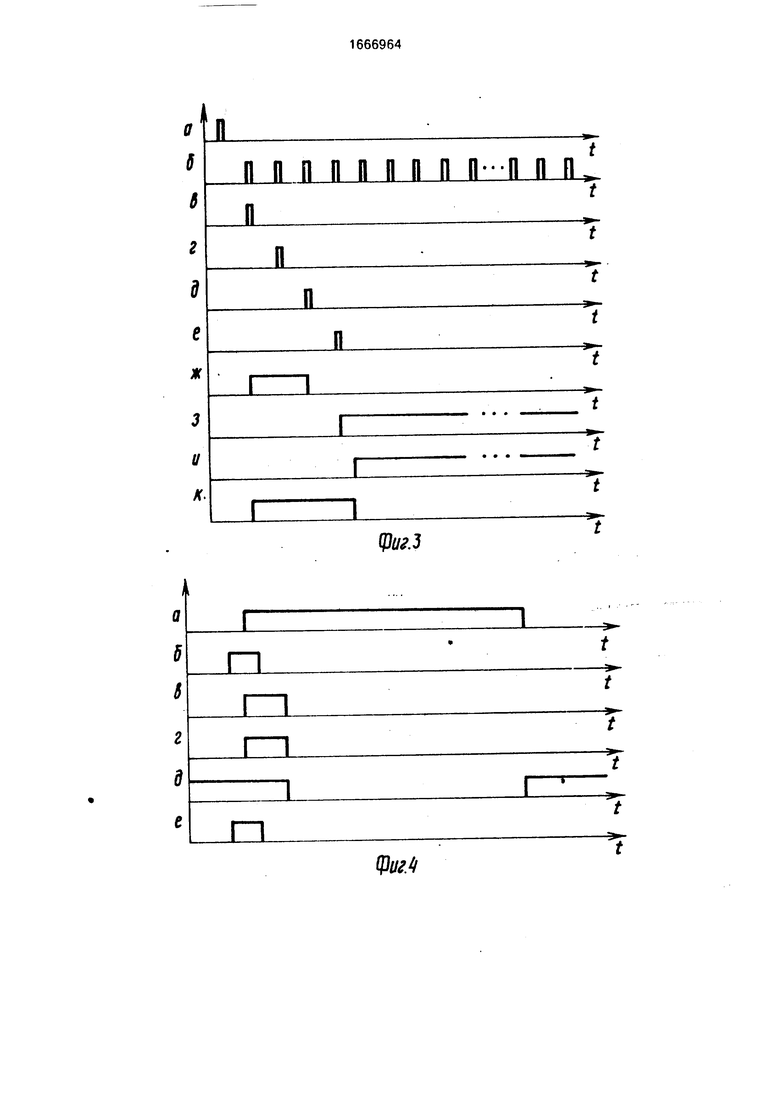

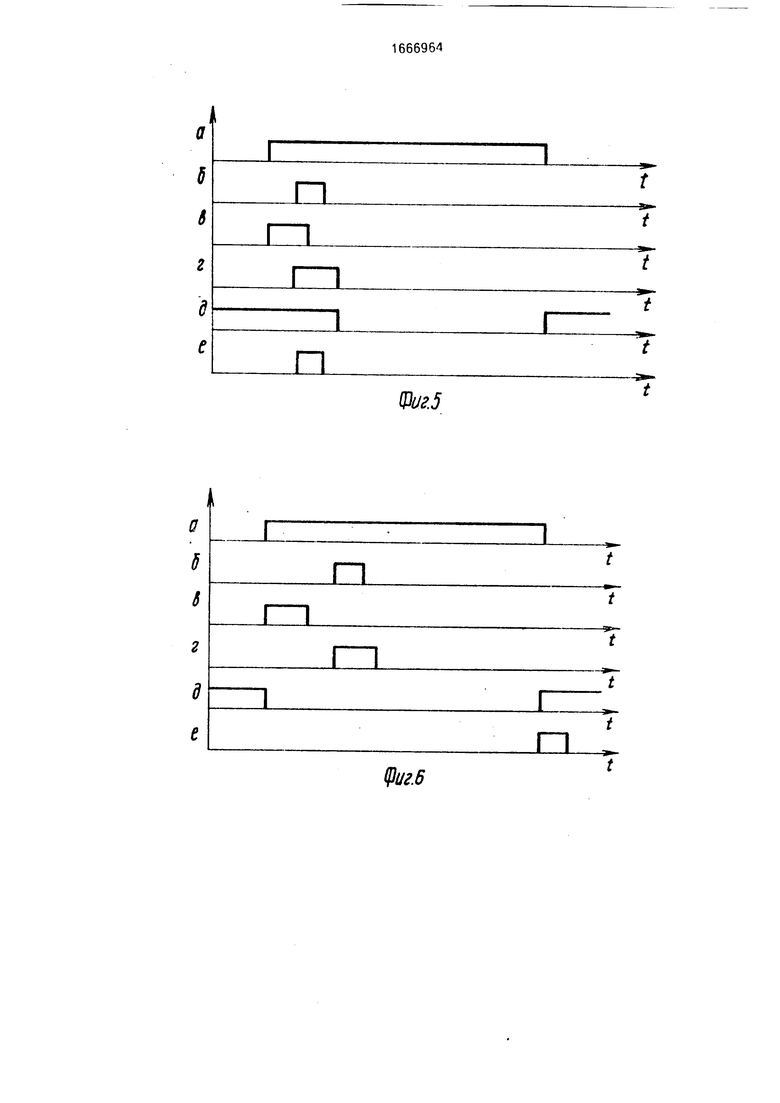

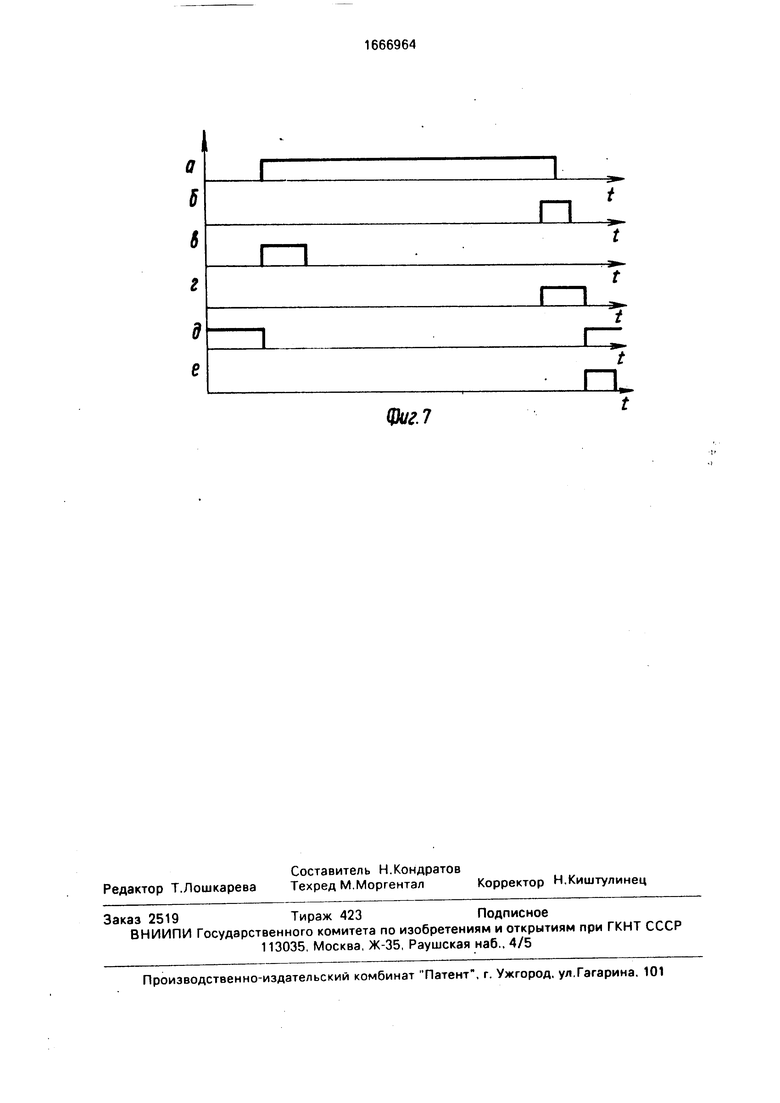

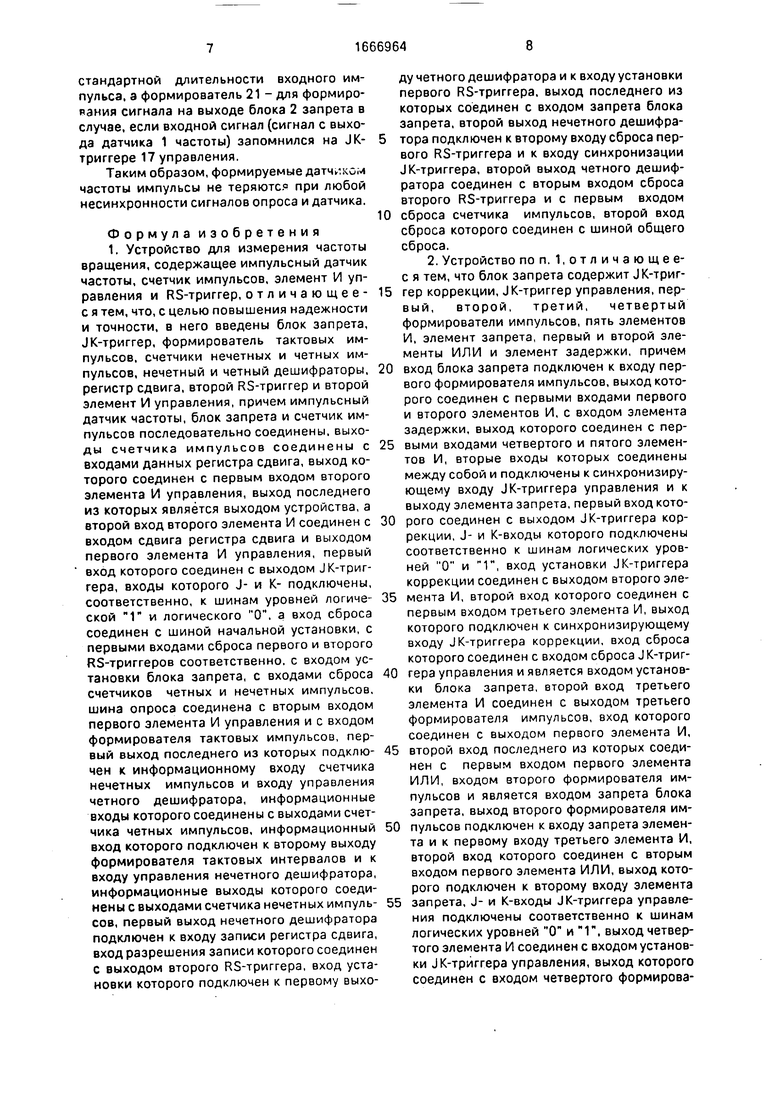

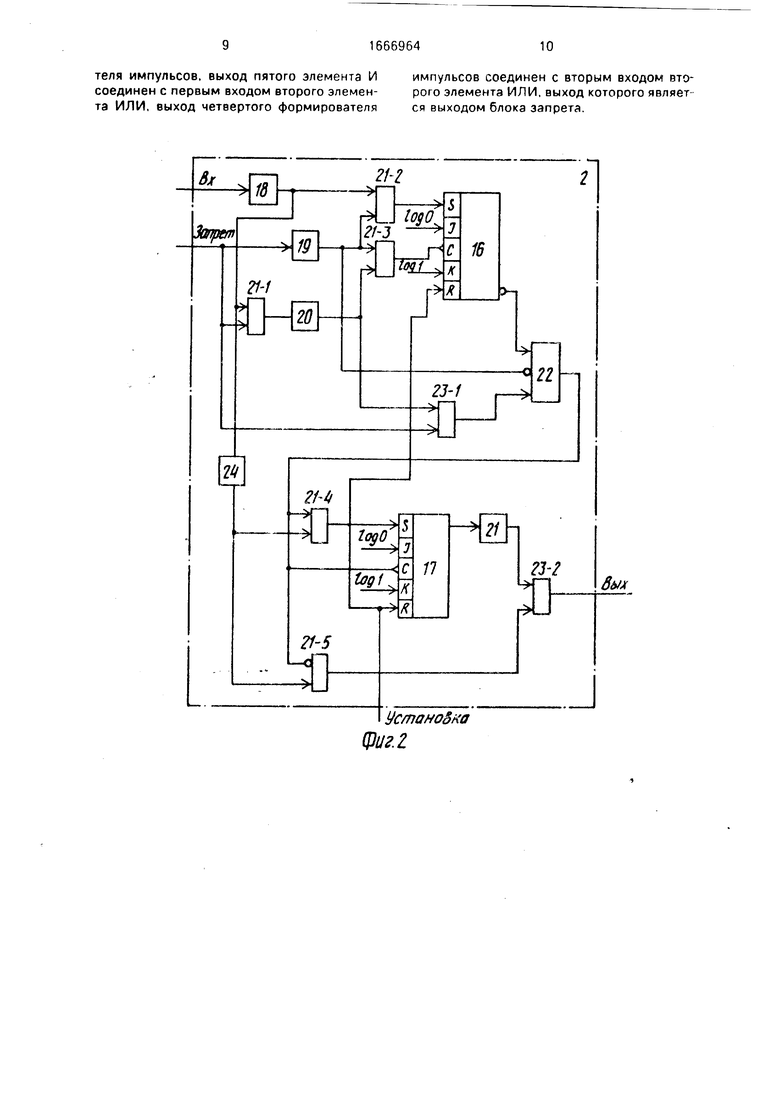

На фиг. 1 представлена функциональная схема устройства для измерения частоты вращения; на фиг. 2 - функциональная схема блока 2 запрета; на фиг. 3 - временные диаграммы, поясняющие работу устройства; на фиг. 4-7 - временные диаграммы, поясняющие работу блока 2 запрета.

Устройство для измерения частоты вращения содержит (фиг. 1) импульсный датчик 1 частоты, блок 2 запрета, счетчик 3 импульсов, JK-триггер 4, первый 5 и второй 6 RS- триггеры. формирователь 7 тактовых импульсов, счетчики нечетных 8 и четных 9 импульсов и соответствующие им нечетный 10 и четный 11 дешифраторы, регистр 12 сдвига, первый 13 и второй 14 элементы И управления.

В устройстве для измерения частоты вращения импульсный датчик 1 частоты, блок 2 запрета и счетчик 3 импульсов последовательно соединены, выходы счетчика 3 импульсов соединены с входами данных регистра 12 сдвига, выход которого соединен с первым входом второго элемента И 14 управления, выход последнего из которых является выходом устройства, а второй вход второго элемента И 14 управления соединен с входом сдвига регистра 12 сдвига и выходом первого элемента И 13 управления, первый вход которого соединен с выходом JK-триггера 4, входы которого J- и К- подключены, соответственно, к шинам уровней логической 1 и логического О, а вход сброса соединен с шиной 15 начальной установки, с первыми входами сброса первого и второго RS-триггеров 5, 6 соответственно, с входом установки блока 2 запрета, с входами сброса счетчиков 8, 9 нечетных и четных импульсов, шина опроса соединена с вторым входом первого элемента И 13 управления и с входом формирователя 7 тактовых импульсов, первый выход последнего из которых подключен к информационному входу счетчика 8 нечетных импульсов и входу управления четного дешифратора 11, информационные входы которого соединены с выходами счетчика 9 четных импульсов, информационный вход которого подключен к второму выходу формирователя 7 тактовых импульсов и к входу управления нечетного дешифратора 10, информационные выходы которого соединены с выходами счетчика 8 нечетных импульсов, первый выход нечетного дешифратора 10 подключен к входу записи регистра 12 сдвига, вход разрешения записи которого соединен с выходом второго RS-триггера

6, вход установки которого подключен к первому выходу четного дешифратора 11 и к входу установки первого RS-триггера 5, выход последнего из которых соединен с входом запрета блока 2 запрета, второй выход

0 нечетного дешифратора 10 подключен к второму входу сброса первого RS-триггера 5 и к входу синхронизации JK-триггера 4, второй выход четного дешифратора 11 соединен с вторым входом сброса второго

5 RS-триггера бис первым входом сброса счетчика 3 импупьсов, второй вход сброса которого соединен с шиной общего сброса (ОС),

Блок 2 запрета содержит (фиг. 2) JK0 триггер 16 коррекции, JK-триггер 17 управления, первый 18, второй 19, третий 20 и четвертый 21 формирователи импульсов, элементы И 21-1, 21-2, 21-3, 21-4, 21-5, элемент 22 запрета, элементы ИЛИ 23-1,

5 23-2 и элемент 24 задержки.

В блоке 2 запрета вход блока запрета подключен к входу первого формирователя 18 импульсов, выход которого соединен с первыми входами первого и второго эле0 ментов И 21-1, 21-2, с входом элемента 24 задержки, выход которого соединен с первыми входами четвертого и пятого элементов И 21-4, 21-5, вторые входы которых соединены между собой и подключены к

5 синхронизирующему входу JK-триггера 17 управления и к выходу элемента 22 запрета, первый вход которого соединен с выходом JK-триггера 16 коррекции, J- и К-входы которого подключены, соответственно, к ши0 нам логических уровней О и 1, вход установки JK-триггера 16 коррекции соединен с выходом второго элемента И 21-2, второй вход которого соединен с первым входом третьего элемента И 21-3, выход

5 которого подключен к синхронизирующему входу JK-триггера 16 коррекции, вход сброса которого соединен с входом сброса JK- триггера 17 управления и является входом установки блока 2 запрета, второй вход

0 третьего элемента И 21-3 соединен с выходом третьего формирователя 20 импульсов, вход которого соединен с выходом первого элемент а И 21 -1, второй вход последнего из которых соединен с первым входом первого

5 элемента ИЛИ 23-1, входом второго формирователя 19 импульсов и является входом запрета блока 2 запрета, выход второго формирователя 19 импульсов подключен к входу запрета элемента 22 запрета и к первому входу третьего элемента И 21-3, второй вход которого соединен с вторым входом первого элемента ИЛИ 23-1, выход которого подключен к второму входу элемента 22 запрета, J- и К-входы JK-триггера 17 управления подключены, соответственно, к шинам логических уровней О и 1, выход четвертого элемента И 21-4 соединен с входом установки JK-триггера 17 управления, выход которого соединен с входом четвертого формирователя 21 импульсов, выход пятого элемента И 21-5 соединен с первым входом второго элемента ИЛИ 23-2, выход четвертого формирователя 21 импульсов соединен с вторым входом второго элемента ИЛИ 23-2, выход которого является выходом блока 2 запрета.

На фиг. 3 представлены временные диаграммы, поясняющие работу устройства, где а) - признак начала опроса; б) импульсы опроса на входе формирователя 7; в) первый выход четного дешифратора 11; г) первый выход нечетного дешифратора 10; д) второй выход четного дешифратора 11; е) второй выход нечетного дешифратора 10; ж) разрешение записи счетчика 3 импульсов; з) выход JK- триггерэ 4; и) считывание; к) запрет.

На фиг. 4-7 представлены временные диаграммы, поясняющие работу блока 2 запрета, где а) вход запрета блока 2 запрета; б) выход формирователя 18 импульсов; в) выход формирователя 19 импульсов; г) выход формирователя 20 импульсов; д) выход элемента 22 запрета, е) выход блока 2 запрета.

Устройство работает следующим образом.

Датчик 1 частоты генерирует импульсы с частотой, пропорциональной частоте вращения входного вала, поступающие при отсутствии сигнала на входе запрета блока 2 запрета на счетный вход счетчика 3 импульсов. С блока обработки информации или ЦВМ по шине 15 поступают импульсы признака начала опроса (ПНО) и импульсы опроса по шине Опрос. Импульс ПНО устанавливает исходное состояние всех элементов памяти, кроме счетчика 3 импульсов.

Далее импульсы опроса на формирователе 7 тактовых импульсов преобразуются в две серии импульсов - нечетную 1Т и четную 2Т, которые считаются соответственно счетчиками нечетных 8 и четных 9 импульсов. Результаты подсчета дешифруются дешифраторами: нечетным 10 и четным 11, причем счетчик 8, считающий 1Т, дешифруется дешифратором, стробируемым импульсом 2Т, а счетчик 9, считающий 2Т, - дешифратором, стробируемым импульсом 1Т. Первый импульс опроса 1И устанавливает в состояние Г первый 5 и второй 6 RS- триггеры, которые вырабатывают

соответственно сигналы запрета на блок 2 запрета и сигнал разрешения записи информации в регистр 12 сдвига (фиг. 3 к. ж). Второй импульс 2И переписывает информацию со счетчика 3 импульсов в регистр 12 сдвига. Далее третий импульс ЗИ опроса снимает сигнал разрешения записи в регистр 12 сдвига и сбрасывает в исходное состояние счетчик 3 импульсов. Следующий

0 импульс 4И, устанавливая в состояние О первый RS-триггер 5, снимает сигнал запрета и, устанавливая в состояние 1 J«-триггер 4, разрешает прохождение импульсов опроса через первый элемент И 13 управле5 ния на сдвигающий вход регистра 12 сдвига. Данные импульсы сдвигают информацию в регистре 12 задним фронтом, передним стробируют второй элемент И 14 управления, на выходе которого будут фор0 мироваться импульсы последовательного кода, значение которого соответствует количеству импульсов, подсчитанных счетчиком 3 импульсов.

Принцип работы блока 2 запрета заклю5 чается в том, что второй 19 и третий 20 формирователи импульсов формируют длительность больше длительности входного импульса, формируемого первым формирователем 18. Входной импульс с выхода дат0 чика 1 частоты, совпадая с передним фронтом сигнала запрета (фиг. 4), проходит через блок 2 запрета на счетчик 3. То же происходит в случае сдвига импульса входной частоты на ширину импульса входа от5 носительно сигнала запрета (фиг. 5). Входной импульс запоминается до окончания сигнала запрета,если импульс входной частоты находится на середине сигнала запрета при опросе (фиг. 6). Запоминание

0 происходит также в случае совпадения импульса входной частоты с задним фронтом сигнала запрета (фиг. 7).

Передним фронтом сигнала на входе JK- триггеры 16, 17 устанавливаются в 1, а

5 затем устанавливаются в состояние О перепадом заднего фронта, например, с высокого уровня на низкий. Формирователь 19 импульсов формирует сигнал от перепада фронта сигнала запрета с низкого уровня на

0 высокий, а формирователь 20 - при совпадении сигналов на входе и запрета с помощью первого элемента И 21-1.

Одновременно сигнал с выхода формирователя 19 импульсов запрещает про5 хождение информации через элемент 22 запрета. Величина задержки элемента 24 задержки выбирается таким образом, чтобы перекрыть срабатывание всех элементов тракта запрета блока 2. Формирователь 18 импульсов необходим для формирования

стандартной длительности входного импульса, а формирователь 21 - для формирования сигнала на выходе блока 2 запрета в случае, если входной сигнал (сигнал с выхода датчика 1 частоты) запомнился на JK- триггере 17 управления.

Таким образом, формируемые датчиком частоты импульсы не теряются при любой несинхронности сигналов опроса и датчика.

Формула изобретения 1. Устройство для измерения частоты вращения, содержащее импульсный датчик частоты, счетчик импульсов, элемент И управления и RS-триггер, отличающее- с я тем, что, с целью повышения надежности и точности, в него введены блок запрета, JK-триггер, формирователь тактовых импульсов, счетчики нечетных и четных импульсов, нечетный и четный дешифраторы, регистр сдвига, второй RS-триггер и второй элемент И управления, причем импульсный датчик частоты, блок запрета и счетчик импульсов последовательно соединены, выходы счетчика импульсов соединены с входами данных регистра сдвига, выход которого соединен с первым входом второго элемента И управления, выход последнего из которых является выходом устройства, а второй вход второго элемента И соединен с входом сдвига регистра сдвига и выходом первого элемента И управления, первый вход которого соединен с выходом JK-триг- гера, входы которого J- и К- подключены, соответственно, к шинам уровней логической 1 и логического О, а вход сброса соединен с шиной начальной установки, с первыми входами сброса первого и второго RS-триггеров соответственно, с входом установки блока запрета, с входами сброса счетчиков четных и нечетных импульсов, шина опроса соединена с вторым входом первого элемента И управления и с входом формирователя тактовых импульсов, первый выход последнего из которых подключен к информационному входу счетчика нечетных импульсов и входу управления четного дешифратора, информационные входы которого соединены с выходами счетчика четных импульсов, информационный вход которого подключен к второму выходу формирователя тактовых интервалов и к входу управления нечетного дешифратора, информационные выходы которого соединены с выходами счетчика нечетных импульсов, первый выход нечетного дешифратора подключен к входу записи регистра сдвига, вход разрешения записи которого соединен с выходом второго RS-триггера, вход установки которого подключен к первому выходу четного дешифратора и к входу установки первого RS-триггера, выход последнего из которых соединен с входом запрета блока запрета, второй выход нечетного дешифратора подключен к второму входу сброса первого RS-триггера и к входу синхронизации JK-триггера, второй выход четного дешифратора соединен с вторым входом сброса второго RS-триггера и с первым входом

0 сброса счетчика импульсов, второй вход сброса которого соединен с шиной общего сброса.

2. Устройство по п. 1,отличающее- с я тем, что блок запрета содержит JK-триг5 гер коррекции, JK-триггер управления, первый, второй, третий, четвертый формирователи импульсов, пять элементов И, элемент запрета, первый и второй элементы ИЛИ и элемент задержки, причем

0 вход блока запрета подключен к входу первого формирователя импульсов, выход которого соединен с первыми входами первого и второго элементов И, с входом элемента задержки, выход которого соединен с пер5 выми входами четвертого и пятого элементов И, вторые входы которых соединены между собой и подключены к синхронизирующему входу JK-триггера управления и к выходу элемента запрета, первый вход кото0 рого соединен с выходом JK-триггера коррекции, J- и К-входы которого подключены соответственно к шинам логических уровней О и 1, вход установки JK-триггера коррекции соединен с выходом второго эле5 мента И, второй вход которого соединен с первым входом третьего элемента И, выход которого подключен к синхронизирующему входу JK-триггера коррекции, вход сброса которого соединен с входом сброса JK-триг0 гера управления и является входом установки блока запрета, второй вход третьего элемента И соединен с выходом третьего формирователя импульсов, вход которого соединен с выходом первого элемента И,

5 второй вход последнего из которых соединен с первым входом первого элемента ИЛИ, входом второго формирователя импульсов и является входом запрета блока запрета, выход второго формирователя им0 пульсов подключен к входу запрета элемента и к первому входу третьего элемента И, второй вход которого соединен с вторым входом первого элемента ИЛИ, выход которого подключен к второму входу элемента

5 запрета, J- и К-входы JK-триггера управления подключены соответственно к шинам логических уровней О и 1, выход четвертого элемента И соединен с входом установки JK-триггера управления, выход которого соединен с входом четвертого формирователя импульсов, выход пятого элемента И соединен с первым входом второго элемента ИЛИ, выход четвертого формирователя

импульсов соединен с вторым входом второго элемента ИЛИ, выход которого являет ся выходом блока запрета.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления шаговым двигателем | 1977 |

|

SU663058A1 |

| Устройство для сопряжения ЦВМ с абонентами | 1986 |

|

SU1312590A1 |

| Устройство для сдвига информации | 1989 |

|

SU1607017A2 |

| Измеритель временных интервалов | 1983 |

|

SU1155990A1 |

| Многоканальное устройство для реверсирования двигателей постоянного тока | 1987 |

|

SU1573520A1 |

| Устройство для контроля блоков оперативной памяти | 1983 |

|

SU1161993A1 |

| Устройство для тренировки памяти обучаемого | 1989 |

|

SU1683050A1 |

| Устройство передачи информации по волоконно-оптической линии связи | 1988 |

|

SU1675919A1 |

| Автоматизированная система тестового контроля | 1985 |

|

SU1278857A1 |

| Устройство для психологических исследований | 1989 |

|

SU1644908A1 |

Изобретение может быть использовано в устройствах измерения частоты вращения. Цель изобретения - повышение надежности и точности. Цель достигается тем, что в устройство для измерения частоты вращения введены JK-триггер 4, формирователь 7 тактовых импульсов, счетчики нечетных 8 и четных 9 импульсов, нечетный и четный дешифраторы 10, 11, регистр 12 сдвига, второй RS-триггер 6, второй элемент И 14 управления и блок 2 запрета, который содержит JK-триггер коррекции, JK-триггер управления, формирователи импульсов, пять элементов И, элемент запрета, первый и второй элементы ИЛИ и элемент задержки. Устройство также содержит импульсный датчик 1 частоты вращения, счетчик 3 импульсов, элемент И 13 управления и RS-триггер 5. Сущность изобретения заключается в исключении потерь импульсов датчика из-за несинхронности сигналов датчика и опроса. Это достигается путем организации запоминания входного импульса при несинхронности его с сигналами опроса до конца действия сигнала запрета. 1 з.п. ф-лы, 7 ил.

фиг. 2

°(l

a 5 5

г д

П

fltetf

1 о

S

г

д

п

3

i

Уиг.6

3

ФигЗ

а 6

6 г

д е

п

г Т

П

фиг. 7

| АвторскоЈ свидетеп -г тио СССР № , vn G 01 Г( 23/00, 1984. |

Авторы

Даты

1991-07-30—Публикация

1989-07-10—Подача