числа, другие входы являются входами устройства, второй вход блока управления соединен с одним из выходов первого счетчика.

2. Устройство по п.I, о т л и чающееся тем, что блок управления содержит генератор импульсов, формирователь сигналов сброса, третий счетный триггер, дополнительные элементы И, группу формирователей импульсов, делитель частоты, датчик тестовых сигналов, буферный регистр, причем выходы буферного регистра, делителя частоты, первого дополнительного элемента И и инверсные выходы третьего счетного триггера являются одними из выходов блока, прямой выход третьего счетного триггера подключен к nepBcwiy входу первого

дополнительного элемента И, выход генератора импульсов подключен к одному из входов второго дополнительного элемента И, другой.вход которого является первым входом блока, выход второго дополнительного элемента И подключен к входам формирователей импульсов группы, первые выходы которых подключены к входу делителя частоты, вторые выходы - к второму входу первого дополнительного элемента И, третьи выходы являются другим выходом блока, а первый и второй входы третьего счетного триггера являются вторым входом блока, выход формирователя сигналов сброса подключен к третьему входу третьего счетного триггера, выход датчика тестовых сигналов подключен к входам буферного регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля оперативной памяти | 1980 |

|

SU955208A1 |

| Устройство для контроля оперативной памяти | 1982 |

|

SU1022225A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU1014041A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU1001182A1 |

| Устройство для контроля блоков оперативной памяти | 1980 |

|

SU924758A1 |

| Устройство для контроля оперативной памяти | 1975 |

|

SU547837A1 |

| Устройство для контроля оперативной памяти | 1982 |

|

SU1024990A1 |

| Устройство для контроля оперативных запоминающих блоков | 1980 |

|

SU890442A1 |

| Устройство для контроля блоков памяти | 1986 |

|

SU1444896A1 |

| Генератор сигналов | 1985 |

|

SU1335968A1 |

1. УСТРОЙСТВО ДЛЯ КОНТРОЛЯ БЛОКОВ ОПЕРАТИВНОЙ ПАМЯТИ, содержащее блок управления, регистр числа, элемент И, первый и второй счетные триггеры, формирователь импульсов, основные и дополнительные коммутаторы, полусумматор и счетчики с первого по третий, причем выходы первого счетчика, регистра числа и элемента Ни первый выход блока управления являются выходами устройства, второй выход блока управления подключен к первым входам элемента И, первого счетного триггера и формирователя импульсов, к входу третьего счетчика, входам второго счетного триггера, выход элемента И подключен к входу первого счетчика, один из выходов которого подключён к второму и третьему входам первого счетного триггера, выход которого подключен к первому входу полусумматора, входу второго счетчика и второму входу формирователя импульсов, выход которого подключен к второму входу элемента И, второй вход полусумматора подключён к одному из выходов третьего счетчика, а выход - к первым информационным входам основных комт мутаторов, выходы которых подключены соответственно к одним из входов регистра числа, другие входы которого подключены к третьему выходу блока управления, четвертый выход которого подключен к первым управляющим входам основных коммутаторов, вторые информационные входы которых подключены к выходам дополнительных коммутаторов, управляющие и информационные входы которых подключены к выходам второго и третьего счетчиков, третий вход формирователя импульсов подключен к пятому выходу блоку управления. отличающееся тем, что t (Л с целью повьщ1ен 1я достоверности с: контроля, в него введены элементы НЕ, блок сравнения и дешифратор, входы которого подключены к одним из выходов третьего счетчика, а выходы - к третьим информационным входс1м основных коммутаторов и входам элементов НЕ, выходы которых под9д ключены к четвертым информационным входам основных коммутаторов,прямой СО выход второго счетного триггера со подключен к пятым информационным 00 входам одних основных коммутаторов, инверсньй выход второго счетного триггера подключен к пятым информационным входам других основных коммутаторов, вторые и третьи управляющие входы которых подключены соот- . ветственно к шестому и седьмому выходам блока управления, первый вход которого подключен к выходу блока сравнения, одни из входов которого подключены к выходам регистра

Изобретение относится к вычислительной технике и может найти применение в устройствах контроля в динамическом режиме оперативных запоминающих устройств (ОЗУ) с произвольн выборкой.

Известно устройство для контроля блоков памяти, содержащее генератор

.импульсов, блок сравнения, входы которого подключены соответственно к выходу блока эталонной информации и выходам контролируемого устройства а выход соединен с блоком индикации РЗ

Недостаток этого устройства низкая надежность.

Наиболее, близким к изобретению является устройство для контроля блоков оперативной памяти, сЪдержащее блок управления, регистр числа, элемент И, первый и второй счетные триггеры, формирователь импульсов, основные и дополнительные коммутаторы, полусумматор и счетчики, причем выходы первого счетчика и регистра числа выход элемента И и перйый выход блока управления являются выходами устройства, второй выход блока управления соединен с первым входом элемента И, первыми входами первого счетного триггера

и формирователя импульсов и входами второго и третьего счетчиков, выход элемента И подключен к входу, первого счетчика, один из выходов которого соединен с вторым и третьим входами первого счетного триггера, выход которого подключен к первому входу полусумматора и второму входу формирователя импульсов, выхо которого соединен с вторым вхоДом элемента И, второй вход полусумматора подключен к одному из выходов третьего счетчика, а выход - к первым информационным входам основных коммутаторов, выходы которых соединены соответственно с одними из входов регистра числа, другие входы которого подключены к третьему выходу блока управления, четвертьш выход которого соединен с первыми управляющими входами основных коммутаторов, вторые информационные БХ.ОДЫ которых подключены соответственно к выходам дополнительных коммутаторов, входы второго счетйого триггера подклн)чены к первому входу элемента И, а выходы - к информационным входам основных коммутаторов 2.

Недостатком этого, устройства является низкая достоверность контрол

так как тесты типа Дождь, Адресный код и Шахматный код по адресам не обеспечивают полностью проверки оперативной памяти, в частности взаимовлияния ячеек памяти, в которых записаны разряды одного слова, так как во всех разрядах одного слова записывается одинаковая информаци и не проверяется помехозащищенность по отдельным разрядам информационкого слова, существенно зависящая от монтажа в блоке.

Цель изобретения - повышение достоверности контроля. .

Поставленная цель достигается тем, что в устройство для контроля

блоков оперативной памяти, содержащее блок управления, регистр числа, элемент И, первый и второй счетные триггеры, формирователь импульсов, основные и дополнительные коммутаторы, полусумматор и счетчики с первого по третий, причем выходы первого цчетчика, регистра числа и элемента И и первый выход блока управления являются выходами устройства, второй выход блока управления подключен к первым входам элемента И, nepBioro счетного триггера и формирователя импульсов ,к входу третьего счетчика, входам второго счетного триггера, выход элемента И подключен к входу первого счетчика, один из выходов которого подключен к второму и третьему входам первого счетного триггера, выход которого подключен к первому входу полусумматора, входу второго счетчика и второму входу формирователя импульсов, выход которого подключен к второму входу элемента И, второй вхо полусумматора подключен к одному из выходов третьего счетчика, а выход - к первым информационным входам основных коммутаторов, выходы которых подключены соответственно к. одним из входов регистра числа, другие входы которого подключены к третьему вьходу блока управления, четверты выход которого подключен к первым управляющим входам основных коммутаторов, вторые информационные входы которых подключены соответственно к выходам дополнительных коммутаторов, упр дяющие и информационные входы которых подключены соответственно к выходам второго и третьего счетчиков, третий вход формирователя импульсов подключен к пятому ыходу блока управления, введены элементы НЕ, блок сравнения и дешифратор, входы которого подключены к одним из выходов третьего счетчика, а выходы - к третьим информационным входам основных коммутаторов и входам элементов НЕ, выходы которых подключены к четвертым информационным входам основных коммутаторов, прямо выход второго счетного триггера под ключен к пятым информационным входа одних основных коммутаторов, инверсный выход второго счетного триггера подключен к пятым информационным входам других основных коммутаторов вторые и третьи управляющие входы которых подключены соответственно к шестому и седьмому выходам блока управления, первый вход которого поключен к выходу блока сравнения,одн из входов которого подключены к вы ходам регистра числа, другие входы являются входами устройства,второй вход блока управления соединен с одним из выходов первого счетчика.

I Кроме того, блок управления

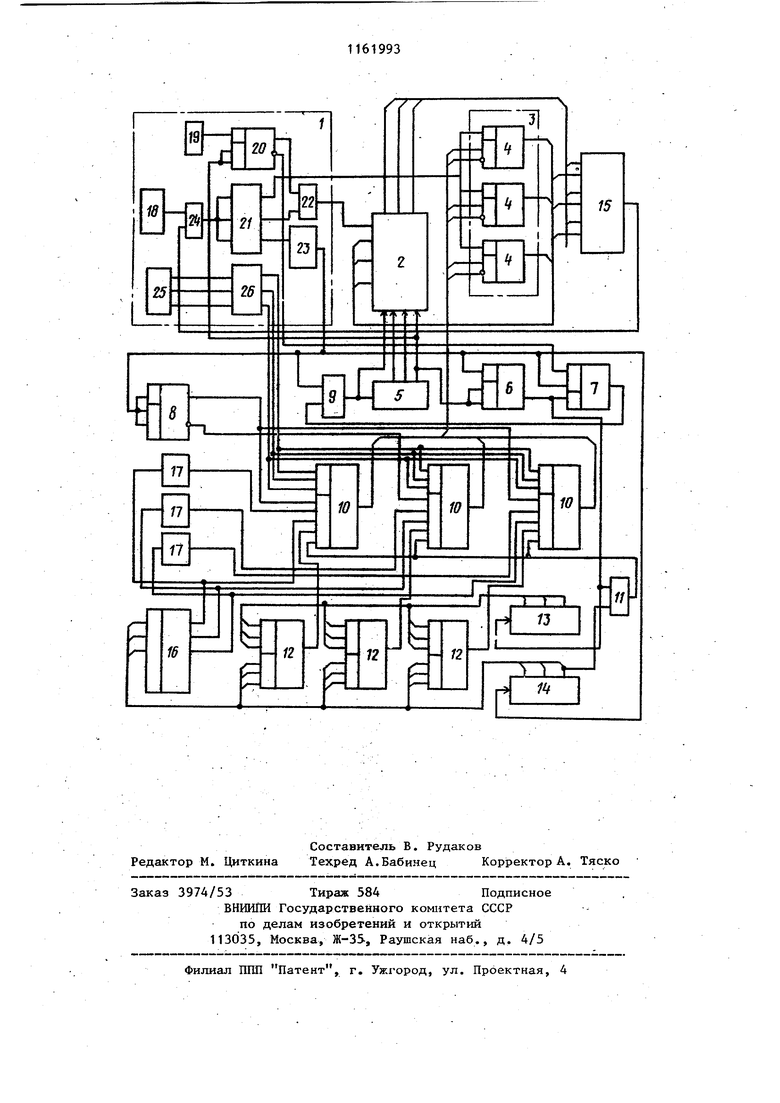

содержит генератор импульсов, форми рователь сигналов сброса, третий счетный триггер, дополнительные, элементы И, группу формирователей импульсов, делитель частоты, датчик тестовых сигналов, буферный регистр, причем выходы буферного регистра, делителя частоты, первого дополнительного элемента И и инверсные выходы третьего счетного триггера являются одними из выходов блока, прямой выход третьего счетного триггера подключен к первому входу первого дополнительного элемента И, выход генератора импульсов подключен к одному из входов второго дополнительного элемента И, другой вход которого является первым входом блока, выход второго дополнительного элемента И подключен к входам формирователей импульсов группы, первые выходы которых подключены к входу делителя частоты, вторые выходы - к второму входу первого дополнительного элемента И, третьи выходы являются другим выходом блока, а первый и второй входы третьего счетного триггера являются вторым входом блока, вьРход формирователя сигналов сброса подключен к третьему входу третьеS . 11 го счетного триггера, выход датчика тестовых сигналов подключен к входам буферного реристра. На чертеже представлена функциональная схема устройства для контроля блоков оперативной памяти. Устройство содержит блок 1 управления, соединенный с контролируемым блоком 2 оперативной памяти, регистр 3 числа, выполненный на . триггерах 4, первый счетчик 5,имеющий разрядность п log А, где А количество адресов, и предназначенный для формирования кода адреса, первый счетный триггер 6, формирователь 7 импульсов, второй счетный триггер 8, элемент И 9, основные коммутаторы tO, полусумматор 11, дополнительные коь 1утаторы 12, второй счетчик 13, третий счетчик 14, блок 15 сравнения, деш 4фатор 16, элементы НЕ 17. Блок 1 управления содержит генератор 18 импульсов, формирователь сигналов сброса, выполненный в виде кнопки 19 начального сброса, третий счетный триггер 20, группу формирователей 21 импульсов, первый дополнительный элемент И 22,делител 23 частоты, второй дополнительный элемент И 24, датчик 25 тестовых сигналов, буферный регистр 26. Второй выход блока 1 управления является тактовым, первый выход бло ка 1 управления задает режИм работы блока ОЗУ Запись-чтение, устанавливаемЕ счетным триггером 20, седь мой, шестой и четвертый выходы зада ют проверочный тест (Дождь, Адре ный код, Шахматный двойной прямой и обратный, Бегущий 0(1) по разря дам) , устанавливаемый датчиком 25 и буферным регистром 26, Счетчик 14 имеет разрядность ). Дешифратор 16 имеет тп log-B входов, где В разрядность инфр1 мационяого слова. Рассмотрим работу устройства в режиме Дождь. В этом режиме источ ником информации, записываемой в регистр 3, является полусумматор 11 При запуске в блоке 1 управления начинает В1фабатываться тактовая последовательность импульсов. В пер вом подцикле счетчики 5 и 14 работают синхронно от одних и тех же та тов блока 1. При этом на пол сумматора 11 код одинаковьй, а на е выходе низкий уровень, соответствующий записи кода О по всем адресам памяти. По окончании первого подцикла формирователь 7 вьщеляет задний фронт сигнала с выхода триггера 6 и производит запрет (в элементе И 9) одного импульса продвижения в счетчик 5. В результате подцикл в счетчике 5 заканчивается на один такт, равный периоду обращения, позже, чем в счетчике 14, и полусумматор 11 фиксирует неравнозначность в конце второго под1Ц1кла. Поэтому во втором подцикле во всех адресах памяти, кроме последнего, записьюаются коды О, а в последнем - код 1. По окончании второго подцикла точно так же происходит запрет еще одного импульса продвижения в счетчик 5. Соответственно неравнозначность фиксируется в двух последних адресах третьего подцикла, куда и записывается код 1. Таким образом, блок 2 оп(еративной памяти, заполненный в первом подцикле всеми нолями, заполняется в следукицих подциклах единицами, т.е. проходит процесс набегания единиц, характерный для теста Дождь, Когда пройдет А подциклов, коды на входе полусумматора 11 будут инверсными и весь блок 2 будет заполнен единицами. В следующие А подциклов точно также начиная с последнего адреса,код единиц сменяется кодом полей. Через 2 А подциклов заканчивается полный (период теста. Рассмотрим работу устройства при формировании теста типа Адресный код. В этом случае управляющие сигналы с блока ,1 подключают к входам регистра 3 числа выходы счетчика 14 (через коммутаторы 12 и 10}. Работа коммутаторов 10 аналогична их работе в реясиме Дождь за исключением того, что источником информации является не полусумматор 11, а счетчик 14, причем счетчики 13 и 14 имеют расхождения по частоте, равное А/2. При этом код числа, записываемый в блок 15, меняется с каждьм адресом и каждый следующий подцикл в адресном коде начинается с разных кодовых комбинаций, чем обеспечивается динамическое смещение информации по подциклам. Благодаря наличию коммутаторов 12, управляемых счетчиком 13, обеспечивается подключение к соответствукмцим разрядам регистра 3 числа различных разрядов счетчика 14 в ра личных подциклах. Этим достигается выравнивание динамики работы разных разрядов. Рассмотрим работу устройства в режиме формирования теста Шахматный код двойной, прямой и обратньй Датчик 25 в блоке управления 1 уста навливается в положение Шахматный код двойной, прямой и обратньш, и с буферного регистра 26 состояния тестов поступают сигналы на управлякшще входы основных коммутаторов 10, которые подключают к входам регистра 3 числа выходы второго счетного триггера 8, Кнопкой 19 начального сбрйса устанавливают триггер 20 в режим Запись, После запуска устройства блок 1 управления вырабатывает тактовую последовательность импульсов, от которой по заднему фронту срабатывает второй счетный триггер 8, Во время первого такта обращения по первому адресу происходит запись в0,2...(В-1) разряды информационного слова нулей, а в 1,3...В разряды - единиц. По заднему фронту первого тактового импульса второй счетньй триггер 8 изменяет свое состояние на противоположное и по второму адресу записывается шахматка обратная, т.е. в 0,2о..(В-1) разряды информационного слова записываются единицы,а в 1,3...В разряды . Таким образом весь блок расписьшается Шахматным двойным и обратньм кодом, по четным адресам, которого записана шахматка прямая, по нечетным - обратная. После окончания подцикла записи информации в контролируемый блок оперативной памяти сигналом с одного из выходов счетчика 5 триггер 20 устанавливается в режим чтения. Из блока управления 1 задается режим чтения информации, в котором информация, считываемая из блока 2, и ин формация с регистра 3 числа сравниваются в блоке 15 сравнения. В случае несравнения информации с выхода блока 15 сравнения поступает сигнал на вход элемента И 24, обеспечивакшрй53 останов временной диаграммы по адресу 1несравнения (органы индикации на чертеже не указаны). 3 По окончании подцикла чтения информации формирователь 7 вьщеляет задний фронт сигнала с выхода триггера 6, что обеспечивается наличием в подцикле чтения на третьем входе формирователя 7 соответствующего управляющего сигнала с,инверсного выхода триггера 20. Импульс, вырабатываемый формирователем 7, поступая на вход элемента И 9, запрещает прохождение первого импульса последующего цикла, что обеспечивает в данном цикле смещение информации на один адрес, то есть запись по четным адресам шахматки обратной, по нечетным прямой. Таким образом проверяется взаимовлияние ячеек как двухстороннее (гальваническое замыкание), так и одностороннее (полупроводниковая связь). Рассмотрим. ..работу устройства при формировании теста Бегущий О по разрядам .Датчик 25 в блоке управления 1 устанавливается в положение Бегущий О по разрядам, и с буферного регистра 26 поступают сигналы на управляющие входы основных коммутаторов 10, которые подключают к входам регистра 3 числа выходы дешифратора 16. После запуска устройства блок 1 управления вырабатывает тактовую последовательность импульсов, запускающих счетчики 5 и 14. В зависимости от рязрядности информационного слова входы деаИЕфратора 16 подключены к младшим выходам счетчика 14. Во время первого такта обращения происходит запись нуля в нулевой и единиц в остальные разряды информационного сдрва по первому адресу. По заднему фронту первого тактового импульса содержание счетчика 14 увеличивается на единицу и по второму адресу записывается информационное слово с нулем в первом и единицей в остальных разрядах информационного слова. Таким образом, в течение В адресов нуль пробежит из младшего разряда в старший. В дальнейшем в подцикле записи первого цикла теста весь блок будет расписан бегущим нулем по разрядам. После окончания подцикла записи информации в контролируемьй блок 2 оперативной памяти сигналом с одного из выходов счетного 5 триггер 20 устанавливается в режим чтения. Из блока управления 1 задается режим чтения информации, в котором инфор9мация считываемая из блока 2 и инфо мация с регистра 3 числа сравнивается в блоке 15 сравнения. В случае несравнения информации с выхода блока 15 сравнения поступает сигнал на вход элемента И 24, обеспечивающий останов временной диаграммы по адресу несравнения. По окончании подцикла информации формирователь импульса 7 вьщеляет задний фронт сигнала с выхода триггера 6, что обеспечивается наличием в подцикле чтения на третьем входе формирователя 7 соответствующего управляющего сигнала с инверсного выхода триггера 20. Импульс, вырабатываемый формирователем 7, поступая на вход элемента И 9, запрещает прохождение первого импульса следующего цикла, что вызывает в следующем цикле смещение бегущего нуля на один разряд влево, т.е. по первому адресу происходит запись поля в первый и единиц в остальные разряды информационного слова, по второму адресу - ноля во вто.рой и единиц в остальные разряды и т.д. Через В циклов заканчивает3ся полньй период теста Бегущей О по разрядам. Работа устройства при формировании теста Бегущая 1 по разрядам аналогична работе при формировании теста Бегупщй О по разрядам. В предлагаемом устройстве применение блоков формирования тестов Шахматный код двойной прямой и обратньй и Бегущая 0(1) по разрядам обеспечивает повьпиение достоверности контроля блоков ОЗУ. Устройство обеспечивает усиление динамических качеств тестовых проверок, позволяет более полно Проверить взаимовлияние ячеек памяти. Особенно эффективно тест Бегущей 0(1) по разрядам в процессе регулировки блоков ОЗУ выявляет уровень помех и пригодность выбранного способа электрического монтажа, обеспечивающего устойчивую работу блоков ОЗУ. Тест Шахматный код двойной прямой и обратный обеспечивает проверку взаимовлияния ячеек памяти, в которых записаны разряды одного слова, как двухстороннего (гальваническое замыкание), так и одностороннего (полупроводниковая связь).

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| 0 |

|

SU407398A1 | |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для контроля блоков оперативной памяти | 1980 |

|

SU924758A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1985-06-15—Публикация

1983-12-13—Подача