Изобретение относится к волоконно- оптическим системам передачи информации и может быть использовано в системах управления автоматизированным оборудованием.

Цель изобретения - повышение достоверности передачи информации и сокращение энергопотребления.

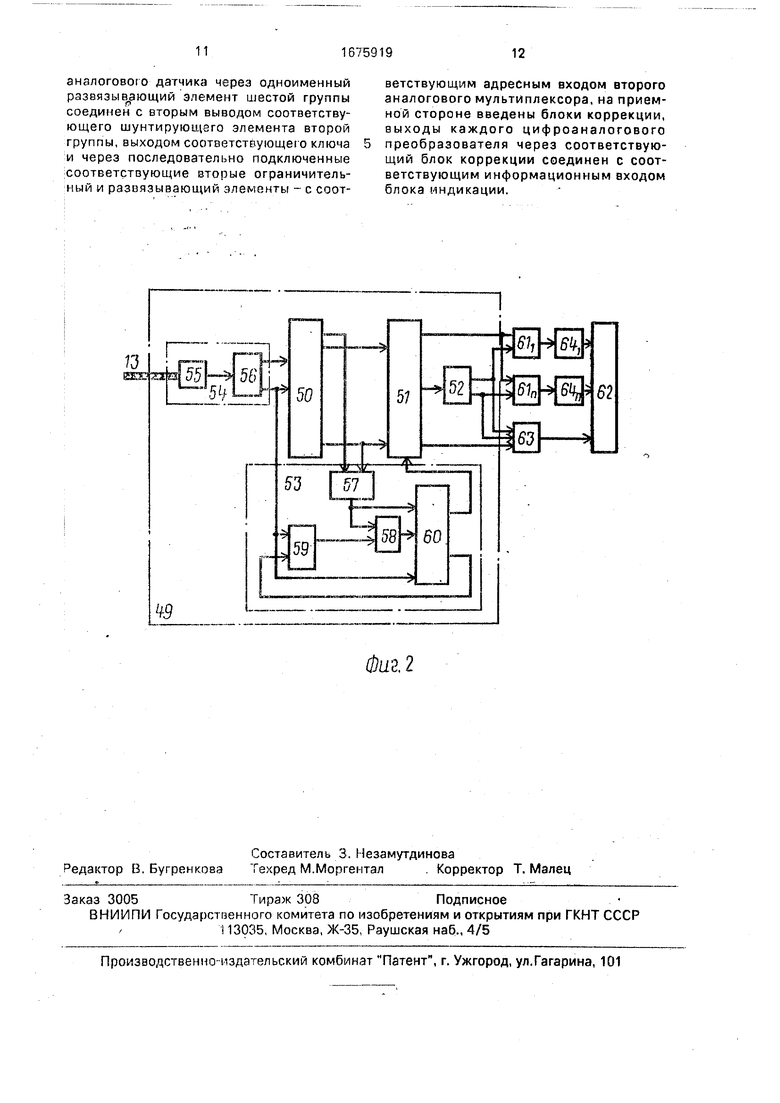

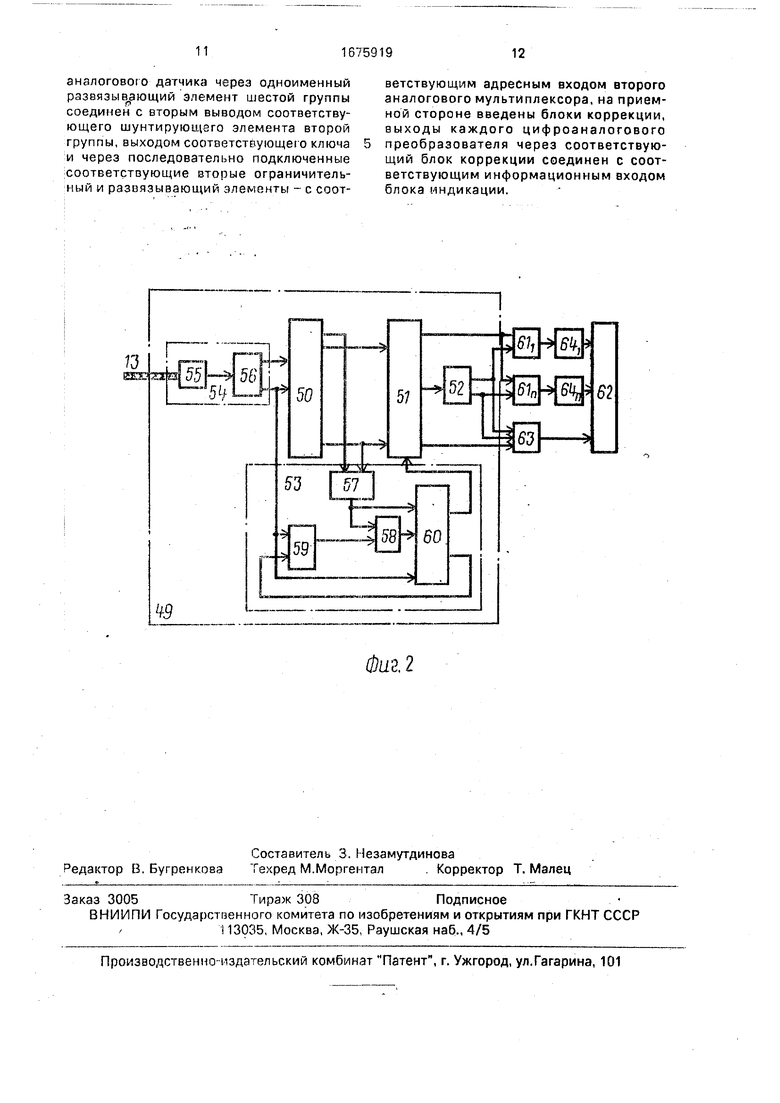

la фиг. 1 и 2 показана структурная блок- схема устройства.

Устройство содержит на передающей стороне 1 блок 2 питания, формирователь 3 сигнала сброса, регистр 4 сдвига, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 5, элемент НЕ 6, элемент И 7, генератор 8 тактовой частоты, делитель 9 частоты, передатчик 10, состоящий из преобразователя 11 кода и электро- оптического преобразователя 12, волоконно-оптическую линию 13 связи, аналоговые 14 и дискретные 15 датчики, счетчик 16 адреса и аналого-цифровой преобразователь 17, аналоговые 18 и 19 и цифровые 20 и 21 мультиплексоры, ключи 22-25, триггер 26, пороговые элементы 27- 30, элементы ИЛИ 31 и 32, элементы 33 и 34 аналоговой памяти, элементы 35 и 36 памяти, аналоговый ключ 37, группы шунтирующих элементов 38-38n, ,n, группы развязывающих элементов 40-45, первые ограничительные элементы 46, развязывающие элементы 47, блок 48 согласования, на приемной стороне 49 регистр 50 сдвига, буферный регистр 51, дешифратор 52 адреса, формирователь 53 импульса записи, приемник 54, содержащий оптоэлектриче- ский преобразователь 55 и преобразователь 56 кода, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 57, элемент И 58, делитель 59 частоты, регистр 60, цифроаналоговые преобразователи 611-61 п. блок 62 индикации1, регистр 63 и блоки коррекции.

Устройство работает следующим образом.

При включении блока 2 сигнал через формирователь устанавливает в исходное состояние элементы 33-36, триггер 26, счетчик 16 адреса и делитель 9 частоты. Включается генератор 8 тактовой частоты, вырабатывающий импульсы с фиксированной частотой, которые поступают на вход делителя 9 частоты. С делителя 9 частоты импульсы частотой 2f поступают на тактовый вход преобразователя 1.1, с третьего выхода - импульсы частотой f поступают на блок 48 согласования (например, трансформатор) и тактовый вход регистра 4 сдвига, с четвертого выхода - импульсы частотой f (N+1) поступают на элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 5 и на И 7, с второго выхода - импульсы частотой faun поступают на тактовый вход аналого-цифрово преобразователя (АЦП) 17, причем Тацп выбирается таким образом, чтобы время преобразования блока было меньше или равно длительмости цикла работы регистра 4. При наличии логического О на входе установки режима регистр 4 сдвига работает в режиме последовательного ввода, С выхода регистра 4 последовательный код поступает на эле0 мент ИСКЛЮЧАЮЩЕЕ ИЛИ 5, а с выхода этого элемента - на последовательный вход регистра 4. При поступлении на элемент ИЛИ 5 импульса частотой f(N+1) с четвертого выхода делителя 9 соответствующий бит

5 последовательного кода инвертируется. При поступлении этого же импульса на элемент И 7 одновременно с присутствием логической 1 на выходе регистра 4 сдвига на выходе элемента И 7 формируется импульс,

0 который переводит регистр 4 сдвига в режим параллельного ввода, причем в послед- ний разряд регистра записывается логический О, который поступает на последний параллельный вход регистра 4 с

5 выхода элемента НЕ 6.

Таким образом, цикл работы параллельно-последовательного регистра 4 сдвига содержит 2 (NM) бит информации, причем в первой и второй половине цикла первые но0 мера бит идентичны, а последний, который играет роль синхроимпульса, инвертируется - в первой половине цикла в качестве синхроимпульса передается логический О, а во второй -логическая 1.

5В соответствии с вышеизложенным на

выходе элемента И 7 формируются импульсы с частотой следования f/2(N+1), которые переводят регистр в режим параллельного ввода, а также запускают АЦП 17, поступа0 ют на счетчик 16 и на триггер 26. По заднему фронту этих импульсов изменяется кодовая комбинация на выходе счетчика 16 адреса, которая подается на шестой вход регистра 4, а также адресные входы цифровых 20 и 21

5 и аналоговых 18 и 19 мультиплексоров.

При этом по заданной программе осуществляется съем информации с датчиков 14 и 15 и опрос состояние линии связи. Так, в момент времени ti осуществляет0 ся опрос линии связи, подключенной к аналоговому датчику 12г по цепи: блок 2 питания, ключ 24, элементы 312, 44i и первый вход аналогового мультиплексора 19 и передача информации с датчика 14i через

5 открытые элементы 43i, 45i на мультиплексор 18, С выхода аналогового мультиплексора 19 напряжение поступает на элементы 27 и 28, где происходит сравнение сигнала с порогом. В том случае, если в линии связи произошло нарушение типа короткое замыкакие (обрыв), на мультиплексор 19 поступает (не поступает) напряжение D блока 2 питания по указанной выше цепи. При коротком замыкании (обрыв) срабатывает элемент 27 (28), в котором происходит сравнение сигнала с порогом и на его выходе появляется сигнал. При поступлении импульса 1/2 f(N+1) происходит запись информации в элемент 33 (34), переключение триггера 2.6 и смена адреса, Триггер 26 выключает ключи 24 и 25 и включают ключи

22и 23. Ключ 22 подключает к цепи второй аналоговый вход мультиплексора 18, третий выход блока 2 и аналоговый датчик 142, а ключ 23 - к цепи второй вход аналогового мультиплексора 19 второй выход блока 2 питания. В рассматриваемом выше случае в линии связи было нарушение типа короткое замыкание (обрыв), поэтому сигнал с датчика 142 не поступает на мультиплексор 18 и на его входе могут быть электромагнитные наводки или неполный сигнал, который поступает на ключ 37. Однако, с приходом импульса 1 /2 f (N+1) ключ 37 запирают сигналом, поступившим с элемента 27 (28) через элемент ИЛИ 31. Таким образом, блокируется вход АЦП 17, и на вход регистра 4 сдвига поступает О с выхода элемента ИЛИ 32, на регистр 4 поступает 1, фиксирующая нарушение в линии связи. Во втором цикле происходит проверка линии связи, соединяющая датчик 14 и третий вход мультиплексора 19,

При отсутствии, сигнала на выходах элементов 27 и 28 в момент, когда поступает импульс 1/2 f (N+1), в элементы 33 и 34 запишется логический О. Сигнал логического О на выходе элемента ИЛ И 31 открывает ключ 37 и снимает сигнал неисправности линии связи, поступающий в предыдущем цикле на седьмой вход регистра 4. При этом аналоговый сигнал с выхода датчика 14з через ключ 37 поступает на АЦП 17 и после преобразования в цифровой код подается на пя гый вход регистра 4 сдвига. В дальнейшем, при поступлении импульса 1/2 f(N+1) цикл работы устройства повторяется.

В том случае, если число входов мультиплексора 6 п больше числа датчиков 14 на n-m входов мультиплексора 19 через элемент, например, 46/, 4бз и элементы 48i, 48а подается напряжение с ключей 23 и 24. Причем нечетные входы подключены к выходам ключей 22 и 24, а нечетные входы - к ключам

23и 25. Напряжение, поступающее на элементы 27 и 28, меньше уставки короткого замыкания и больше уставки. Обрыв линии связи не вызывает срабатывания пороговых

устройств и на регистр 4 сдвига не поступит сигнал нарушения линии связи.

Для времени t1 характерно и то, что с данного момента в течение цикла осуществляется опрос состояния линии связи и передача информации с дискретных датчиков 15i-15. При этом с первого выхода блока 48 положительный полупериод тактовой частоты через элементы 382 и диод 411 поступает на первый вход мультиплексора 21, а отри0 цательный - с второго выхода блока 48 через элементы 45 и 44 и замкнутый контакт датчика 15 на первый вход мультиплексора

20,Таким образом, в течение одного такта осуществляется передача сигнала о состоя5 нии датчика 15i и контроль линии связи, соединяющей датчик 152 и мультиплексор

21.Сигнал с выхода мультиплексора21 поступает на элементы 29 и 30, в которых осуществляется сравнение его с уставкой на

0 короткое замыкание и обрыв в линии связи. В случае, если в линии связи короткое замыкание (обрыв), то срабатывает элемент 29 (30) и сигнал с его выхода поступает на элемент 35 (36). При поступлении импульса с

5 формирователя 43 (содержащий, например, дмфцепочку, выпрямитель и ключ) происходит запись информации в элемент 35 (36). С выхода элемента 35 (36) логическая 1 через элемент ИЛИ 32 поступает на регистр 4,

0 де на соответствующей позиции записывается информация о состоянии линии связи. Одновременно с поступлением 1 на вход элемента ИЛИ 32 на управляющий вход элемента 42 поступает сигнал, запрещая про5 хождение информации с выхода датчика 142 через мультиплексор 20 на регистр 4 сдвига. В следующем такте первого цикла происходит опрос второго датчика и линии связи, соединяющей датчик 14з с мультиплексо0 ром 21.

При числе датчиков К меньше числа мультиплексора 20 -К информационных входов мультиплексора 21 через последовательно включенные элементы 46 и 47 под5 ключаются к блоку 48, причем нечетные входы к первому выходу, а четные к второму. В этом случае на соответствующих тактах сигнал с блока 48 через элементы 46s, 46e, 474, 47s и мультиплексор 21 поступает на

0 элементы 29 и 30. Так как величина напряжения отличается от уставки короткого замыкания и обрыва линии связи, то на выходе элементов 29 и 30 отсутствует сигнал, а следовательно, на седьмой вход регистра 4

5 сдвига не будет поступать сигнал нарушения в линии связи. В следующем цикле последовательный опрос датчиков и линии связи выполняется аналогично предыдущему циклу. Мультиплексированные

сигналы с датчиков 15i-15n с выхода муль- шплексооэ 20 поступают на шестой вход регистра 4 сдвига.

С выхода регистра А последовательный код поступает на информационный вход преобразователя 11, на тактовый вход которого подаются импульсы частотой 2f с пер- оого выхода делителя 9. Преобразователь 11 осуществляет преобразование последовательного кода без возвращения к нулю в линейный самосинхронизирующий код, который поступает на вход электроотическо- го преобразователя 12, преобразующего электрические сигналы о оптические. Оптический сигнал с выхода электрооптического преобразователя 12 через волоконно-оптический кабель 13 поступает на вход оптоэ- лектрмческого преобразователя 55, осуществляющий обратное преобразование. С выхода оптоэлектрического преобразователя 55 линейный самосинхронизирующий код поступает на вход преобразователя 56, который производит его преобразование в последовательный код без возвращения к нулю и выделения тактовой частоты, Последовательный код и импульсы тактовой частоты с выхода преобразователя 56 поступают на соответствующие входы регистра 50, который имеет Мн-2 параллельных выходов, и таким образом, на его первом и последнем выходах одновременно будут находиться биты кодовой посылки с одинаковыми порядковыми номерами. В элементе ИСКЛЮЧАЮЩЕЕ ИЛИ 57 блока 53 происходит поразрядное сравнение соответствующих битов кодовой посылки из первой и второй частей цикла передачи. При их неидентичности на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 57 появляется логическая 1, а с приходом следующего тактового импульса на первом выходе регистра 60 также появляется логическая 1 и делитель 59 сбрасывается в О, на выходе делителя 59 логическая 1 появится только в том случае, если N бит в первой и второй половинах цикла передачи будут идентичны.

С приходом синхроимпульса, который постоянно инвертируется, на выходах элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 57 и делителя 59 одновременно появляется логическая 1 и, таким образом, на выходе элемента И 58 - тоже. С приходом следующего тактового импульса на выходе регистра 51 формируется импульс записи, информация с первых выходов регистра 50 сдвига переписывается в регистр 51. Если в кодовой посылке содержится ошибка - в первой и второй частях цикла передачи какой-либо из информационных битов не совпадает - записи в регистр 51 не происходит. С второго выхода

регистра 51 код адреса поступает на вход дешифратора 52, который осуществляет распределение импульсов записи в ячейки регистра 63 и преобразователи 61i-61n.

Информационный выход регистра 63 соединен с третьим выходом регистра 51. В соответствии с кодом адреса информация с этого выхода регистра 51 записывается в определенные ячейки регистра 63 и сохра0 няется на его выходах в течение цикла изме- нения кода адреса. С первого выхода регистра 51 информация поступает на информационные входы преобразователей . В соответствии с кодом адреса ин5 формация записывается в регистр определенного преобразователя 55i-55n, преобразуется в аналоговый сигнал и через блок поступает на панель индикации или исполнительное устройство (уста0 новленное на контролируемом пункте). В блоке осуществляется вычитание напряжения, которое на передающей стороне использовалось для устранения влияния элементов 38i-38n, на передачу

5 аналоговых сигналов с датчиков на мультиплексор 18.

При наличии сигнала Обрыв (короткое замыкание) линии связи оператор может своевременно обнаружить неисправность и

0 при последующем анализе определить к какой группе датчиков (аналоговых или дискретных) следует отнести данную неисправность. Такое решение позволяет исключить аварийные ситуации, возникаю5 щие при передаче аналоговой и дискретной информации, например об уровне концентрации метана.

Формула изобретения Устройство передачи информации по

0 волоконно-оптической линии связи, содержащее на передающей стороне аналоговые и дискретные датчики, регистр сдвига, генератор тактовой частоты, выход которого соединен с входом делителя частоты, первый

5 выход которого соединен с первым входом передатчика, второй выход - соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛ И и элемента И, третий выход - соединен с входом аналого-цифрового преобразова0 теля, четвертый выход- подключен к первому управляющему входу регистра сдвига, выход которого подключен к второму входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, элемента И, передатчика и через элемент НЕ - к сво5 ему второму управляющему входу, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с третьим управляющим входом регистра сдвига, выход элемента И подключен к четвертому управляющему входу регистра, управляющему входу аналого-цифрового

преобразователя и входу счетчика адреса, первые цифровой и аналоговый мультиплексоры, выход передатчика соединен с входом волоконно-оптической линии связи, на приемной стороне - приемник, вход которого соединен с выходом волоконно-оптической линии связи, первый выход приемника соединен с информационным входом регистра сдвига и первым входом формирователя импульса записи, информационные входы которого объединены с соответствующими входами буферного регистра и подключены к соответствующим выходам регистра сдвига, первый выход буферного регистра соединен с входом дешифратора адреса, второй и третий выходы буферного регистра подключены к объединенным информационным входам цифроаналоговых преобразователей и входу регистра, каждый из выходов дешифратора адреса подключен к входу каждого цифроаналогового преобразователя и соответствующему информационному входу регистра, выход которого соединен с входом блока индикации, отличающееся тем, что, с целью повышения достоверности и сокращения энергопотребления, в него введены на передающей стороне блок питания, пороговые элементы, группы шунтирующих элементов, вторые цифровой и аналоговый мультиплексоры, блок согласования, элементы аналоговой памяти, триггер, элемент запрета, формирователь импульса, аналоговый ключ, элементы памяти, элементы ИЛИ, ключи, формирователь сигнала сброса, ограничительные элементы, группы развязывающих элементов, первый вывод каждого дискретного датчика соединен с первым выводом соответствующего шунтирующего элемента первой группы и через соответствующий развязывающий элемент первой группы подключен к соответствующему информационному входу первого цифрового мультиплексора и через соответствующий развязывающий элемент второй группы - к соответствующему информационному входу второго цифрового мультиплексора, второй вывод каждого дискретного датчика через одноименный развязывающий элемент третьей группы соединен с вторым выводом соответствующег мунтирующего элемента первой группы и через последовательно подключенные соответствующие первые ограничительный и развязывающий элементы - с соответствующим адресным входом первого цифрового мультиплексора, выход первого аналогового мультиплексора подключен соответственно через первый и второй пороговые элементы к первым входам первого и второго элементов аналоговой памят-л, (зыход первого дискретного мультиплексора соединен соответственно ч. :рез третий и четвертый пороговые элементы с первыми входами первого и второго

элементов памяти, первый выход блока питания через формирователь сигнала сброса соединен с установочным входом делителя частоты, триггера, элементов памяти, счетчика адреса, элементов аналоговой памяти,

0 выходы первого и второго элементов аналоговой памяти соединены соответственно с первым и вторым входами первого элемента ИЛИ, выход которого подключен к первому входу аналогового ключа и второго эпемен5 га ИЛИ, второй и третий входы которого соединены с выходами соответственно первого и второго элементов памяти, выходы второго элемент а ИЛИ и аналого-цифрового преобразователя подключены соответст0 венно к первому и второму сходам регистра сдвига, выход счетчика адреса соединен с третьим входом регистра сдвига и управляющим входом первых и вторых аналоговых и цифровых мультиплексоров, выход второ5 го цифрового мультиппексора подкпючен к прямому входу элемента запрета, инверсный вход которого соединен с выходом второго элемента памяти, выход элемента запрета подключен к четвертому входу реги0 гтра сдвига, вторые выводы всех шунтирующих элементов первой группы подключены к соответствующим выходам блока согласования и через формирователь импульса - к второму входу первого и второго элементов

5 памяти, выход элемента И соединен с входом триггера и вторыми входами элементов аналоговой памяти, выход второго аналогового мультиплексора подключен к второму входу аналогового ключа, выход которого

0 подключен к информационному входу аналого-цифрового преоЬразооэтеля, четвертый выход делителя частоты подключен к входу блока согласования, прямой ч инверсный выходы триггера соединены с первы5 ми входами соответственно первого, второго, третьего и четвертого ключей, второй и третий выходы блока питания подключены к вторым входам соответственно первого,четвертого и второго, третье; о клю0 чей, первый вывод .каждого аналогового датчика соединен с первым выводом соответствующего шунтирующего элемента второй группы и через соответствующий развязывающий элемент четвертой группы

5 -с соответствующим информационным входом первого аналогового мультиплексора и через соответствующий развязывающий элемент пятой группы -с соответствующим информационным входом второго аналогового мультиплексора, второй вывод каждого

аналоговою датчика через одноименный развязывающий элемент шестой группы соединен с вторым выводом соответствующего шунтирующего элемента второй группы, выходом соответствующего ключа и через последовательно подключенные соответствующие вторые ограничительный и развязывающий элементы - с соответствующим адресным входом второго аналогового мультиплексора, на приемной стороне введены блоки коррекции, выходы каждого цифроаналогового преобразователя через соответствующий блок коррекции соединен с соответствующим информационным входом блока индикации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство передачи информации по волоконно-оптической линии связи | 1987 |

|

SU1413655A1 |

| Измеритель аналоговых сигналов | 1988 |

|

SU1599869A1 |

| Станция геолого-технологических исследований | 1988 |

|

SU1548421A1 |

| Устройство для контроля температуры | 1988 |

|

SU1515176A1 |

| Устройство для регистрации одиночных ударов | 1987 |

|

SU1479878A1 |

| Устройство для ввода информации от аналоговых датчиков | 1985 |

|

SU1298734A1 |

| Полевой модуль | 1987 |

|

SU1550451A1 |

| УСТРОЙСТВО ОБРАБОТКИ АНАЛОГОВЫХ СИГНАЛОВ С ПРИМЕНЕНИЕМ ЦИФРОВОЙ ФИЛЬТРАЦИИ | 2021 |

|

RU2777306C1 |

| Программируемая линия задержки | 1990 |

|

SU1723656A1 |

| УСТРОЙСТВО ДЛЯ ВВОДА АНАЛОГОВЫХ СИГНАЛОВ | 1991 |

|

RU2017203C1 |

Изобретение относится к волоконно-оптическим системам передачи информации. Цель - повышение достоверности передачи и сокращение энергопотребления. Передача информации осуществляется после предварительного опроса линии связи, соединяющей аналоговые и дискретные датчики 14i-14n, 15i-15i и мультиплексоры 18, 19, 20, 21. При коротком замыкании (обрыве) в линии связи срабатывают пороговые элементы 27-30, которые запрещают прохождение сигнала на передатчик и формируют сигнал аварийного состоянии линии связи. Устройство содержит на передающей стороне 1. блок 2 питания, формирователь 3 сигнала сброса, регистр 4 сдвига, элемент ИСКЛЮЧАЮЩЕЕ ИЛ И 5, элемент НЕ 6, элемент И 7, генератор 8 тактовой частоты, делитель 9 частоты, передатчик 10, волоконно-оптическую линию связи, ключи 22-25, элементы 33,34 аналоговой памяти, триггер 26, элементы ИЛИ 31, 32, элементы 35. 36 памяти, аналоговый ключ 37, группы шунтирующих элементов 38, 39, группы развязывающих элементов 40-45, ограничительные элементы 46, развязывающие элементы 47, блок 48 согласования. На приемной стороне - регистр сдвига, буферный регистр, дешифратор адреса, формирователь импульса записи, приемник, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент И, делитель частоты, регистр, ЦАП, блок индикации, регистр и блоки коррекции. 2 ил. w Ё 0 VI ел о ю

Фиг 2

| Устройство передачи информации по волоконно-оптической линии связи | 1987 |

|

SU1413655A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1991-09-07—Публикация

1988-11-05—Подача