(54) РЕВЕРСИВНЫЙ РАСПРЕДЕЛИТЕЛЬ ИМПУЛЬСОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Реверсивный распределитель импульсов | 1978 |

|

SU752806A1 |

| Устройство для формирования пачек импульсов | 1991 |

|

SU1812617A1 |

| Устройство для управления положением исполнительных элементов | 1983 |

|

SU1226413A2 |

| Цифровой измеритель центра тяжести видеосигналов | 1990 |

|

SU1723559A1 |

| Устройство для предварительной обработки изображений | 1989 |

|

SU1654849A1 |

| Мажоритарное декодирующее устройство | 1986 |

|

SU1372627A1 |

| Устройство для симметрирования токов трехфазных сетей | 1988 |

|

SU1686600A1 |

| Электронные часы | 1985 |

|

SU1262445A1 |

| Устройство для управления шаговым двигателем | 1987 |

|

SU1520646A1 |

| Малогабаритный цифровой твердомер | 1984 |

|

SU1359716A1 |

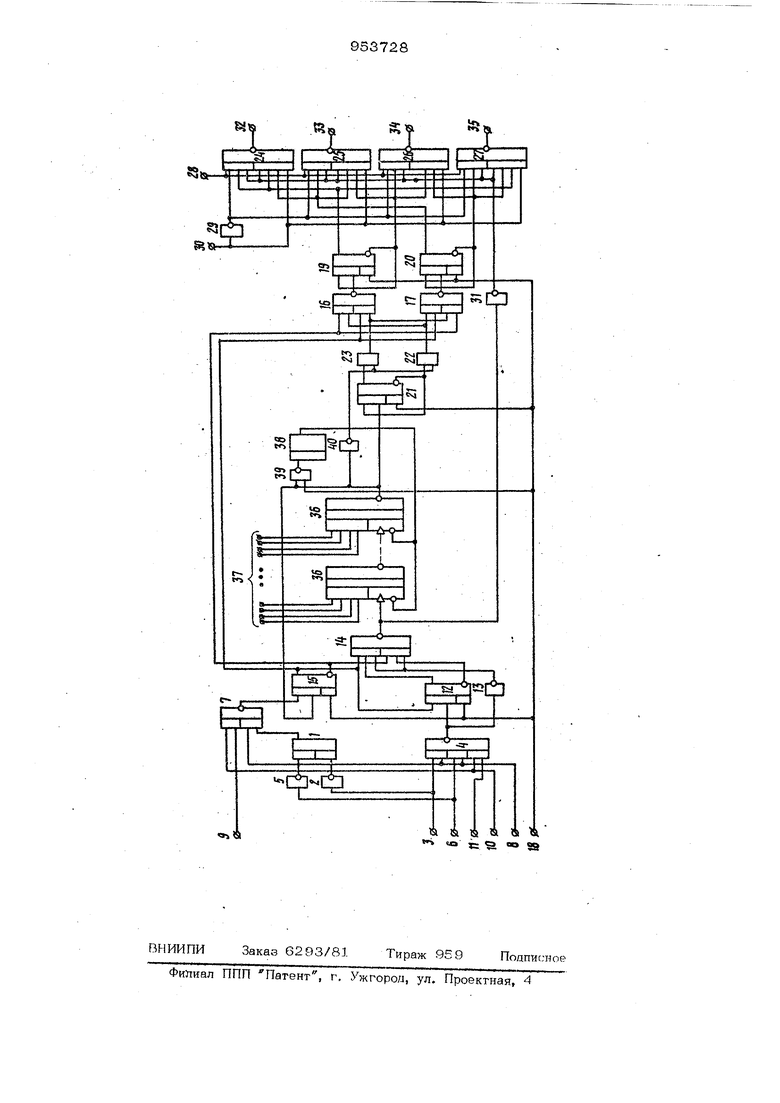

Изофетение относится к автоматике. Наиболее близким техническим решением к изобретению является реверсивный распределитель импульсов, содержащий RS -триггер, R -вход которого через первый инвертор соединен с шиной npsiMoro хода и первым входом элет 1ента 2И-ЗИЛИ-НЕ, 5 -вход через второй инвертор - с шиной обратного хода и треть им входом элемента 2И-ЗИЛИ-НЕ, а единичный выход подключен к первому входу первого элемента 2И-2ИЛИ-НЕ, второй вход которого соединен с улравляюшей шиной и вторым и нетверд тым входами элемента 2И-ЗИЛИ-НЕ, третий вход- с шиной реверса, а четвертый вход подключен к второй управляющей шине и пятому входу 2ИЗИЛИ-НЕ, шестой вход которого сюеяинен с шиной тактирования, а выход подкл чен к С-входу первого Ot -тригг и и через третай инвертор - к первому и четвертому входам элемента ЗИ-2ИЛИНЕ, вход которого соединен с ну левым щоходом первого О -триггдза, третий вход - с нулевым ш кодом второго D -триггера и первыми входами второго и третьего элементов 2И-2ИЛИ-НЕг пятый вход - с единичным выходом пер- вого Dt -триггера, а шестой вход подключен к D -Фходу первого D -тригг а, третьим входам второго и третьего элементов 2И-2ИЛИ-НЕ и единичному-выходу второго D -триггера, D -вход которого соединен с выходсм первого элемента 2И-2ИЛИ-НЕ,а R -«ход - с шиной сброса и R -входами перво1х, третьего, четв ихяго и пятого -триггеров, О -вход последнего из которых подключен к своему нулевому выходу и первсллу входу первого элемента И, а единичный выход - к первому входу второго элемента И, выход которого соединен с четвертым входом второго элемента 2И2ИЛИ-НЕ и вторым входом т зетьего элемента 2И-2ИЛИ-НЕ, четвертый вход котсрого подключен к выходу первого элемента И и к третьему входу второго элемента 2И-2ИЛИ-НЕ, воыход которого соедш ен с С-входом третьего D. -трю гера, нулевой; выход которого соединен с своим D -входом, при этом нулевой выход четвертого D -триггера соедянен с своим D входом, а С-вход подключен к выходу третьего элемента 2И 2ИЛИ-НЕ 13 . К недостаткам известного устройства относятся узкие функциональные возможкости. Цепью изобретешш является расширение фун1шиональнь1х возможностей реверсивного распределителя импульсов. Указанная цепь достигается тем, что в реверсивный распределитель импульсов, содержащий R5 -триггер, R -вход которого через первый инвертор соединен с шиной прямого хода и первым входом элемента 2И-ЗИЛИ-НЕ, 5 -вход через второй инвертор с шиной обратного хода и третьим входом элемента 2ИЗИЛИ-НЕ, а единичный выход подключен к первому входу первогю элемента 2И2ИЛИ НЕ, второй вход которого соединен с первой управляющей шиной и вторы и четвертым входами элемента 2И-ЗИЛИ НЕ, третий вход - с шиной реверса, а четвертый вход подключен к второй узярав ляющей шине и пятому входу элемента 2И ЗИЛИ-МЕ, шестой вход которого соединен с шиной тактирования, а выход подключен к С входу первого D -тр5лггера и через третай инвертор - к первому и четвертому входам элемента ЗИ2ИЛИ-НЕ, второй вход которого соединен с нулевым выходом первого 0 -триггера, третий вход - с нулевым выходом второго D -триггера н первыми входами второго и третьего элементов 2И-2ИЛИНЕ, пятый вход - с единичным выходом первого D t -триггера, а шестой вход подключен к D -входу первого D -триг гера, третьим входам второххэ и третьего элеметхэв 2И-2ИЛИ-НЕ и единичному выходу второго D -триггера, D -вход KOTopoiX) соединен с выходом первого элемента 2И-2ИЛИ-НЁ, а R -вход - с шиной сброса и R -входами первого, третьего, четвертого и пятого D -триг -вход последнего из которых подключен к своему нулевому выходу и первому входу первого элемента И, а единичный выход - к первому входу вторсйго элемйгга И, выход которого соеди- нен с четвертым входом второго элемен 211-2ИЛ11-НЕ и вторым входом третьего элемента 211-2ИЛИ-НЕ, четвертый вход которого подключен к выходу первого элемента И и третьему входу второго элемента 2И-2ИЛИ-НЕ, выход которого соединен с С-входом третьего -триггера, нулевой выход которого соединен с своим D -входом, при этом нулевой выход четвертогЬО -триггера соединен со своим D -входом, а С-вход подключен к выходу третьего элемента 2И2ИЛИ-НЕ, введены счетчики, элемент ИЛИ-НЕ, одновибратор, три дополнительных инвертора и четьфе элемента 4И2ИЛИ-НЕ, первые входы которых подключены к шине единичного логического ; ровня, вторые входы через первый дополнительный инвертор - к третьей управЛ5пащей шине, четвертые и пятые входы через второй дополнительный инвертор соешшены с выходом элв 1ента ЗИ-2ИЛИНЕ, а восьмые входы - с третьей управляющей шиной, при этом третгий и шестой входы первого элемента 4И-2ИЛИ-НЕ подключены к седьмому входу четвертого элемента 4И-2ИЛИ-НЕ И единичномувыходу третьего D -триггера, седьмой вход - к третьему и шестому входам второго элемента 4И-2ИЛИ-НЕ и единичному выходу четвертого D -диггера, а выход - к первой выходной шине, седьмой вход второго элемента 4И-2ИЛИНЕ соединен с третьим и шестым входами третьего элемента 4И-2ИЛИ-НЕ и нулевым входом третьего D -триггера, а выход - с второй выходной шиной, седьмой вход третьего элемента 4И2ИЛИ-НЕ подключен к третьему и шестому входам четвертого элемента 4И2ИЛИ-НЕ и нулевому выходу четвертого D - триггера, а выход - к третьей выходной шине, выход четвертого элемента 4И-2ИЛИ-НЕ соединен с четвертой выходной шиной, при этом ра яднь1е входы счетчиков соединены с информационными входными шинами, а управляющие ходы с вьрсодом одновибратора, вьгчитаюший вход последующего счетчика подключен к выходу Заем предьщушего счетчшса, вычитающий вход первого счетчика соеди нен с выходом элемента ЗИ-2ИЛИ-НЕ, а выход заема последнего счетчика - с С-входами второго и пятого 0 -триггеров, первым входом элемента ИЛИ-НЕ и через третий дополнительный инвертор с вторыми входами первого и второ1-о элементов И, при этом второй вход элемента ИЛИ-НЕ подключен к шине сброса, а выход соединен с вхоаом опиовибратора. 59 На чертеже представлена функциоиаль ная схема реверсивного распред язеггепя I импульсов. Схема содержит RS -триггер 1, Я вход которого через инвертор 2 соедЕСнен с шиной 3 прямого хода и первым входом элемента 2И-ЗИЛИ-НЕ 4, 5 -вход через инвертор 5 - с шиной 6 офатного хода н третьим входом элемента 2И-ЗИЛИ-. НЕ 4, а едшшчный выход подключен к первому входу элемента 2И-2ИЛИ-НЕ 7, второй вход которого соединен с управляющей шиной 8 и вгорым и четвертым входами элемента 2И-ЗИЛИ-НЕ 4, третий вход с шиной 9 реверса, а четвертый вход подключен к управл5псядей шине 10 и пятому входу элемента 2И-ЗИЛИНЕ 4, шестой вход которого соединен с шиной 11 тактирования, а выход подключен к С-входу D -триггера 12 и через инвертор 13 - к первому и четвертому входам элемента ЗИ-2ИЛИ-НЕ 14, второй вход которого соединён с нулевым выходом D -тртггера 12, третий вход ., f . С нулевым выходом D -триггера 15 и первыми входами элементов 2И-2ИЛИ-НЕ 16 и 17, пятый вход - с единичным выходом D -триггера 12, а шестой вход подключен к С -входу D -триггера 12 третьим входам элементов 2И-2ИЛИ-НЕ 16 я 17 и единичному выходу D -триггера 15, D -вход которого соединен с выходом элемента 2И-2ИЛИ-НЕ 7, а R -вход с шиной 18 сброса и R -входами первого, третьего, четвертохх) и пятого О -триггеров 12, 19, 20 и 21, D -вход последнего из которых подключен к своему нулевому выходу и первому входу элемента И 22, а единичный выход - к первому входу элемента И 23, выход которого соединен с четвертым входом элемента 2И-2ИЛИ-НЕ 16 и вто. рым.входом элемента 2И-2ИЛИ-.НЕ 17, четвертый вход которого подключен к выходу элемента И 22 и третьему входу элемента 2И-2ИЛИ-НЕ 16, выход кеугорого соединен с С-входом D - триггера 19, нулевой выход которого соединен с своим D -входом; нулевой выход D - триггера 20 соединен с своим -входом, С-вход подключен к выходу элемента 2И-2ИЛИ-НЕ 17, элементы 4И-2ИЛИ НЕ 24 - 27, первые входы которых подетпочены к шине 28 единичного логического уровня, вторые входы через янвертер 29 - к управляющей шине 30, че гвертые и пятые входы через ипврртор 31 соединены с выходом элемента ЗИ- 28 2ИЛИ-НЕ 14, а восьмые входы - с управляющей шиной 30, третий и шестой входы элемента 4И-2ИЛИ-НЕ 24 подключены к седьмому входу элемента 4И-2ИЛИ-НЕ 27 н единичному выходу О -триггера 19, седьмой вход - к третьему и шестому входам элемента 4И-2ИЛИ-НЕ 2 5 и единичному выходу D -триггера 2О, а выход - к выходной шине 32, седьмой вход элемента 4И2ИЛИ-НЕ 25 соединен с третьим и шестым входами элемента 4И-2ИЛИ-НЕ 26 и нулевым выходом и t-триггере 19 а выкод - с выходной шиной 33, седьмой ВХОД элемента 4И-2ИЛИ-НЕ 26 подключен к третьетлу и шестому входам элемента 4И-2ИЛИ-НЕ 27 и нулевсж у ныходу D -оршт ра 20, а выход - к выходной шине 34, выход элемента 4И2ИЛИ-НЕ 27 соединен с выходной швной 35, разрядные входы счетчиков 36 соединены с информационными входвоыми шинами 37, а управляющие входы - с выходом одаовибратора 38} вычитающий ВХОД последующего счетчика 36 подклю rf tr TTrf 4Tr r 4fT/lCTTr/ T Wf lMfVItf f Oft ./ Иццц чен к выходу Заем предыдущего счетчика 36, вычитающий вход счетчика 36 соединен с выходом элемаата ЗИ-2ИЛИНЕ 14, а выход Заем последнего счетчика - с С-входами О -тршт хж 15 И 21, первым входом элемента ИЛИ-ИЕ 39, через 4О - с вторыми входами элементов И 22 и 23, трз этсм второй вход элемента ИЛИ-НЕ 3 9 подключен к шине 18 сброса, а выход соединен с входом одновнбрагора 38. Реверсивный распределитель и шупь- сов работает следующим образом. В исходном состоянии по щвне 18 сброса D -триггеры 12, 15, 19, 20 И 21 устанавливаются в нулевое состояние, а в счетчики 36 записываеггся информация, определяемая состоянием ивформаиионных входных шин 37. В первом режиме имдупьсы по шине 11 тактирования через элемент 2И-ЗИЛИ-НЕ 4 поступают на С-вход Dg -триггера 12 и инвертор 13 - на входы элемента ЗИ-2ИЛИ-НЕ 14, с выхода ксггорого указанные импульсы поступают на выч1ггаю- дни вход первого счетчика 36 и через инвертор 31 - на входы элементов 4И-2ИЛИ-ЛЕ 24 - 27. По окоачанш счзэтывания ВЕфсрмации вэ счетчиков 36 на выходе За&л последнего- счетчика 36 появляется импульс, постутшюршй на С-входы D - триггеров 15 и 21{ через инвертор 40 - па вторые входы элемен- . тов и 22 и 23, а также через элемент И ЛИ-НЕ 39 на вход одновибратора 38. Одновибратор 38 по окончаний у1шзанного импульса формирует сигнал, осуществляющий перезапясь информации в счетчйкн 36 с шформаяионных входных шин 37. В результате на выходе последнего счетчика 36 формируется серия импульсов с частотой следования i - i /п + а на выходах элементов И 22 и 23 появляются две последовательности импуль сов, сдвинутые на поллериода относитель яо друг друга и с частотой следования f 3 ia/2 (П+ 1)/где fo частота импульсов, поступаюищх по шин 11 тактирования, |1 - число, записанное в счетчики 36, С выходов элементов И И 22 и И 23 две последовательности итчшульсов приходят на вход элементов 2И-. 16 и 17ГЕсли1) триггер 15 по шине 9 реверса установлен в нулевое состояние, то импульсы с выхода эл-емента И 22 через элемент 2И-2ИЛИ НЕ 16 поступают на С-вход D -тригге ра 19, а импульсы с выхода элемента И 22 через элемент 2И-2ИЛИ-НЕ 17 на С-вход D -триггера 2О. Если 0 -три гер 15 по шипе 9 реверса установлен в едшшчное состояние, то импульсы с выходов элементов И 22 и 23 меняются . каналами следования. При каждом изменении потенциала на шине 9 реверса D-j. -триггер 15 устанавливается в соот ветствукдцее состояние по окончании ближайшего шипульса, поступающего по информационной входной шине 37. Это позволяет вырабатывать команду Реверс в произвольный момент времени, так как исключается ее вьшопнение до момента счзкпъшания информации из счетчиков 36. Кроме того, переключение D - григгера 15 приводит к изменению информации на D -входе триггера 12 и блокирует прохождение следующего такто вого импульса через первую группу входов элемента ЗИ-2ИЛИ-НЕ 14. I. Но, одновременно, D -триггер 12 блокирует прохождение этого импульса и через вторую группу входов элемента ЗИ-2ИЛИ-НЕ 14. По окончании дашгого импульса D -триггер 12 переключается Б состошше, аналопгчное состоянию D триггера 15, и вторая группа входов элемента ЗИ-2ИЛИ-НЕ 14 оказывается открытой для прохождения последующих импульсов. Такая .работа особенно важна осли в счетчики 36 не заносятся инфор- мшдая, т.е. все его разр5ЭДЬ1 с информационных входов шин 37 устанавливаются в нулевое состояние. При этом нет задержки для реверса на время считывания информации из счетчиков 36, ас выхода Заем последнего счетчика 36 на С-вход D -TfOirrepa 15 .будут поступать импульсы с частотой тактирования. Переключение D -триггеров 19 и 20 приводит к формированию на их выходах четырехканальной последовательности пере1фывающихся импульсов, поступающих иа соответствующие входы элементов 4И-2ИЛИ НЕ 24 - 27, на другие входы которых приходят тактирующие импульсы и сигналы управления с управляющей щины 30 режима формирования серий импульсов. Если на управляющей шине ЗО низкий уровень, то первые группы входов каждого элемента 4И-2ИЛИ-НЕ 24-27 открыты, а вторые закрыты. При этом сигналы с выходов D -триггеров 19 и 20 таким образом коммутпируют прохождение тактасрукшшх импульсов через элементы 4И-2ИЛИ-НЕ 24 - 27, что на их выходах 32-35 форуЩруются серии из четного числа импульсов, количество которых в серии равно 2( h + 1), где п - число, записанное в счетчики 36. Кроме того, каждая серия импульсов начинается после прохождения половины импульсов в серии предыдущего канала. Если на управляющей шине ЗО высокий уровень, то первые грутагы входов элементов 4И-2ИЛИ-НЕ 24 - 27 закрыты, а вторые открыты. При этом прохождением тактирующих импульсов через вторые труппы входов элементов 4И-2ИЛИ-НЕ 24-27 управляют два соответствующих сигаала от D -триггеров 19 и 20. Это приводит к формированию на выходах элементов 4И-2ИЛИ-НЕ 24-27 серий импульсов, количество которых в каждой из них равно П + 1. В данном случае каждая серия импульсов начинается после прохождения всех импульсов в серии предьщущего канала. Во втором режиме на соответствующие входы элемента 2И-ЗИЛИ-НЕ 4 по щзшам прямого и обратного ходов 3 и 6 поступают импульсы. Одновременно через инверторы 2 и 5 импульсы проходят на соответствующие входы RS -триггера 1. Дальнейшая работа реверсивного распределителя импульсов в этом режиме аналогична рассмотренному режиму. Таким образом, за счет введения счетчиков, одновибратора, элементов ИЛИ-НЁ и 4И-2ИЛИ-НЕ, а также шгоерторов в изобретении достигается расш&ренке фуншшональных возможностей реверсивного распредешггепя импульсов, так как обеспечивается формирование на его выходах требуемых серий имнупь сов. Формула изобретений Ревфсивный распределитегаь импульсов, содержаний RS -триггер, R -вход которого через первый инвертер соединен с шиной прямого хода и первым входом элемента 2И-ЗИЛИ-НЕ, 5 -вход через второй инвертор - с шиной обратного хода- и третьим входом элемента- 2ИЗИЛИ-НЕ, а единичный выход подключен к первому входу первого .элемента 2И2ИЛИ-НЕ, второй вход которого соединен с первой управляющей шиной И вторым и четвертым входами элемента 2ИЗИЛИ-НЕ, третий вход - с шиной реверса, а четвертый вход подключен к второй управляющей шине и пятому входу элемента 2И-ЗИЛИ-НЕ, шестой вход которого соединен с шиной тактирования, а выход подключен к С-входу первого D -триггера, и через третий инвертор к первому и четвертому входам элемента ЗИ-2ИЛИ-НЕ, второй вход которого соединен с нулевым выходом первого t) j. триггера, третий вход - с нулевым выхо дом второго D -триггера и первыми входами второго и третьего элементов 2И-2ИЛИ-НЕ, пятый вход - с единичным выходом первого О -тригг а, а шестой вход подключен к D -входу первого f t триггера, третьим входам второго и третьего элементов 2И-2ИЛИ-НЕ и единичному выходу второго О -триггера, D -вход которогчэ соединен с выходом первого элемента 2И-2ИЛИ-НЕ, а R - Ъход - с шиной сброса и R -входами перво третьего, четвертогчэ и пятого D -триггеров, р -вход последнего из которых подключен к своему нулевому выходу и первому входу первого элемента И, а единичный выход - к первому входу второго элемента И, выход которого соединен с четвертым входом второго элемен- та 2И-2ИЛИ-НЕ и вторым входса.1 треть его элемента 2И-2ИЛИ-НЕ, четвертый вход которого подключен к выходу перво го элемента И и третьему входу второго элемента 2И-2ИЛИ-НЕ, выход которсях) с оединен с С-входом третьего D гера, нулевой выход которого соединен со .своим D -входом, при этом нулевой выход четвертого Dt --триггера соединен с своим D -входом, а Счвход подключен к вькоду третьего элемента 2И-2ИЛИНЕ, отличающийся тем, что, с целью расширения функциональных возможностей, введены счетчики, эяемент ИЛИ-НЕ, одновибратор, три допошштепьных инвертора и четыре элемента 4И2ИЛИ-НЕ, первые входы иодюшчезш к шине единичного логического уровня, вторые входы через первый дополнительный инвертор - к третьей управляющей шине, четвертые и пятые входы ч&рез второй дополнЕГгельный инвертер со&динены с выходом элемента ЗИ-2ИЛИНЕ, а восьмые входы - с третьей управляющей шиной, при этом третий и шестой входы первого элемента 4И-2ИЛИНЕ подключояы к седьмому входу чет вертого элемента 4И-2ИЛИ-НЕ и единичному выходу третьего D -триггера; седьмой вход - к третьему и шестому входам второго элемента 4И-2ИЛИ-НЕ и единичному выходу четвертого D триггера, а выход - к первой выходной шине, седьмой вход BTqporo элемента 4И-2ИЛИ-НЕ соединен с третьим и шестым входами третьего элемента 4И2ИЛИ-НЕ и нулевым выходом третьего р -триггера, а выход - с выхо;н ной шиной, седьмой вход третьего элемента 4И-2ИЛИ-НЕ подключен к третьему и шестому входам четвертого элемента 4И-2ИЛИ-НЕ и нулевому выходу четвертого D -/триггера, а выход - к третьей выходной шине, выход четвертого эл&меетга 4И-2ИЛИ-НЕ соединен с той выходной шиной, при этом разр5здные входы счетчиков соединены с ирформационными входными шинами, а управляюшие входы - с выходом одновИбратор% вычитаюший вход последующего счетчика подахаочен к выходу Заем предыдущего счетчика, вычитающий вход первого счет чика соединен с выходом элемента ЗИ2ИЛИ-НЕ, а выход заема последнего счет«чика - с С-входами второго и пятого Dt-чгриггеров, первым входом элемента ИЛИ-НЕ и через трегшй дополнительный инвертор - с вторыми входами первого и второго элементов И, щя этом второй вход элемеонта ИЛИ-НЕ подключен к шШ1е сброса, а выход соединен с входом однови6paтqpa. Источники информации, призаятые во внимание при эЬспертизе 1. ABTqpOTOe свидетельство СССР № 752806; вп. Н 03 К 17/62, 26.О9.78 (щютопш).

« i О SS

Авторы

Даты

1982-08-23—Публикация

1981-01-27—Подача