Изобретение относится к электротехнике и может найти применение в источниках электропитания радиоэлектронной аппаратуры.

Целью изобретения является повышение качества выходного напряжения.

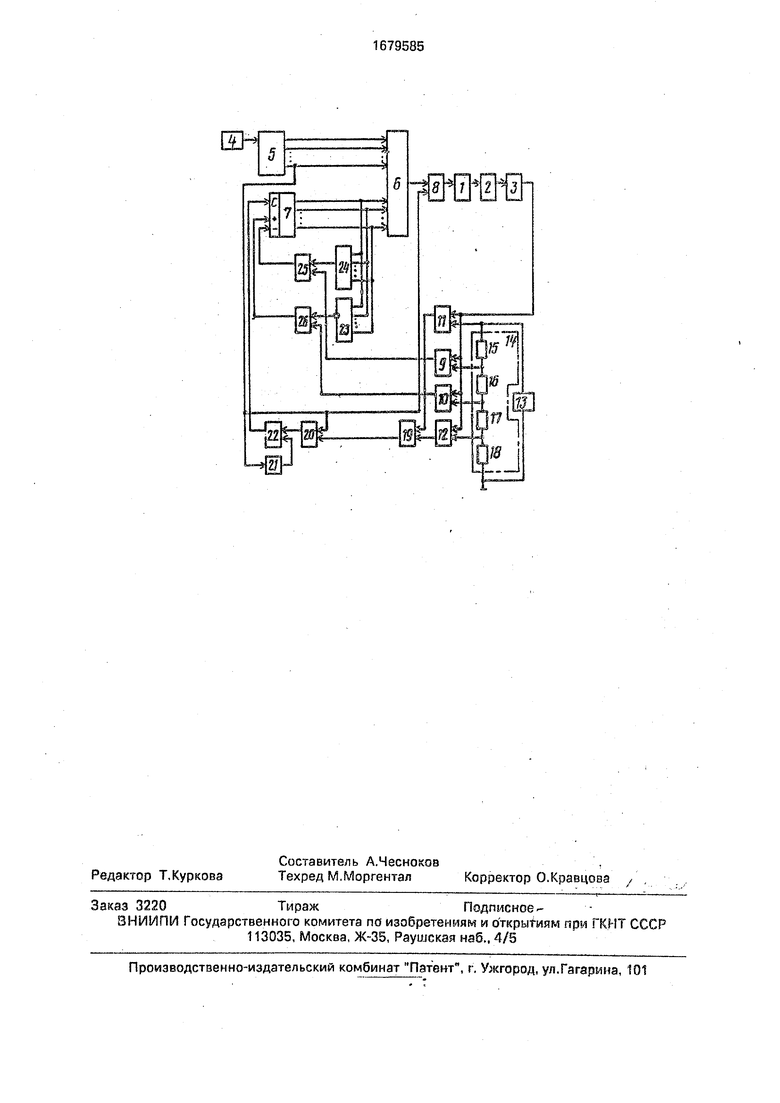

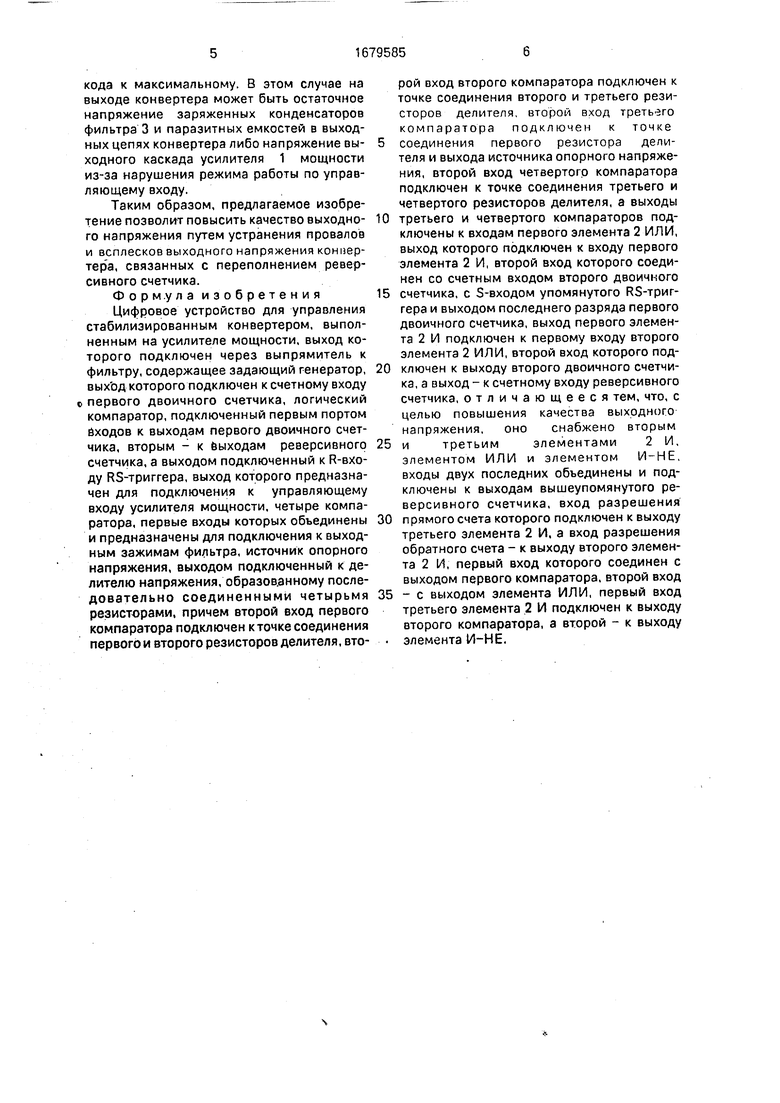

На чертеже приведена схема стабилизированного конвертера.

Конвертер выполнен на усилителе 1 мощности, выход которого подключен через

выпрямитель 2 к фильтру 3. Цифровое устройство для управления стабилизированным конвертером содержит задающий генератор 4, выход которого подключен к счетному входу первого двоичного счетчика 5, логический компаратор 6, первый порт входов которого подключен к выходам первого двоичного счетчика 5, второй - к выходам реверсивного счетчика 7, а выход - к R-входу RS-триггера 8, выход которого предназначен для подключения к управляющему входу усилителя 1 мощности. Оно также включаете себя четыре компаратора 9-12, первые входы которых предназначены для подключения к выходным зажимам фильтра 3, и источник 13 опорного напряжения, выходные зажимы которого подключены к делителю 14 напряжения, образованному последовательным соединением четырех резисторов 15-18. Второй вход первого компаратора 9 подключен к точке соединения первого 15 и второго 16 резисторов, второй вход второго компаратора 10 подключен к точке соединения второго 16 и третьего 17 резисторов, второй вход третьего компаратора 11 подключен к общей точке соединения перваго резистора 15 делителя 14 напряжения и первого выхода источника 13 опорного напряжения, а второй вход четвертого компаратора 12 подключен к точке соединения третьего 17 и четвертого 18 резисторов делителя 4 напряжения. Выходы третьего 11 и четвертого 12 компараторов подключены к входам элемента 2 ИЛИ 19, выход которого подключен к первому входу первого элемента 2 И 20, второй вход которого объединен с S-входом RS-триггера 8, счетным входом второго двоичного счетчика 21 и подключен к выходу последнего разряда первого двоичного счетчика 5. Первый и второй входы второго элемента 2 ИЛИ 22 подключены соответственно к выходам первого элемента 2 И 20 и второго двоичного счетчика 21, а выход- к счетному входу реверсивного счетчика 7. Входы элемента И-НЕ 23 и элемента ИЛИ 24 подключены к выходам реверсивного счетчика 7. Входы второго элемента 2 И 25 подключены соответственно к выходу элемента ИЛИ 24 и к выходу первого компаратора 9, а выход - к входу разрешения обратного счета реверсивного счетчика 7. Входы третьего элемента 2 И 26 подключены соответственно к выходу элемента И-НЕ 23 и к выходу второго компаратора 10, а. выход - к входу разрешения прямого счета- реверсивного счетчика 7.

Цифровое устройство для управления стабилизированным конвертером работает следующим образом.

При подаче на конвертер первичного питания схемой обнуления (на чертеже не показана) на всех выходах двоичных счетчиков 5 и 21 и реверсивного счетчика 7 устанавливаются сигналы логического нуля. На выходе элемента И-НЕ 23 при этом устанавливается высокий уровень сигнала, а на выходе элемента ИЛИ 24 - низкий уровень сигнала. На вторых входах компараторов 9-12 появляется напряжение от источника

13 опорного напряжения. Компараторы 9- 12 включены так, что в первый момент времени после подачи на конвертер напряжения питания, когда его выходное напряжение равно нулю, на выходах компаратороа 9 и 11 формируется низкий уровень сигнала, а на выходах компараторов 10 и 12 - высокий уровень. Высокий уровень сигнала с выхода компаратора 10

0 поступает через элемент 2 И 26 на вход разрешения прямого счета реверсивного счетчика 7, в котором режим обратного счета запрещен низким уровнем сигнала с выхода элемента 2 И 25, на входы которого

5 поданы сигналы низкого уровня с первого компаратора 9 и элемента ИЛИ 24.

Сигнал высокого уровня с выхода четвертого компаратора 12 разрешает подачу импульсов с последнего выхода двоичного

0 счетчика 5 через элемент 2 И 20 и элемент 2 ИЛИ 22 на счетный вход реверсивного счетчика 7. Увеличение кода в реверсивном счетчике 7 приводит к увеличению времени сравнения с кодом двоичного счетчика 5 в

5 логическом компараторе 6, за счет чего увеличивается длительность широтно-модули- рованного импульса и повышается выходное напряжение конвертера. Если величина наброса нагрузки не позволяет за

0 счет увеличения длительности широтно-мо- дулированного импульса повысить выходное напряжение конвертера до уровня срабатывания второго компаратора 10, то код в реверсивном счетчике 7 достигает

5 максимального значения (все единицы на выходах счетчика). При этом сработает элемент И-НЕ 23, с выхода которого сигнал низкого уровня через элемент 2 И 26 поступает на вход разрешения прямого счета им0 пульсов, тем самым исключая провал выходного напряжения от переключения реверсивного счетчика 7 с максимального кода к нулевому. Дальнейшая работа устройства происходит с максимальной дли5 тельностью широтно-модулированного импульса до сброса нагрузки.

Аналогично, если при сбросе нагрузки уменьшение длительности широтно-модулированного импульса не позволяет сни0 зить напряжение на выходе конвертера до уровня срабатывания первого компаратора 9, то реверсивный счетчик 7 переходит в нулевое состояние. При этом сработает элемент ИЛИ 24, с выхода которого сигнал низ5 кого уровня через элемент 2 И 25 поступает на вход разрешения обратного счета реверсивного счетчика 7 и прекращает счет импульсов, тем самым исключая вплеск;, выходного напряжения от переключения реверсивного счетчика 7 с нулевого

кода к максимальному. В этом случае на выходе конвертера может быть остаточное напряжение заряженных конденсаторов фильтра 3 и паразитных емкостей в выходных цепях конвертера либо напряжение выходного каскада усилителя 1 мощности из-за нарушения режима работы по управляющему входу.

Таким образом, предлагаемое изобретение позволит повысить качество выходного напряжения путем устранения провалов и всплесков выходного напряжения конпер- тер а, связанных с переполнением реверсивного счетчика.

Формула изобретения Цифровое устройство для управления стабилизированным конвертером, выполненным на усилителе мощности, выход которого подключен через выпрямитель к фильтру, содержащее задающий генератор, выход которого подключен к счетному входу первого двоичного счетчика, логический компаратор, подключенный первым портом входов к выходам первого двоичного счетчика, вторым - к выходам реверсивного счетчика, а выходом подключенный к R-вхо- ду RS-триггера, выход которого предназначен для подключения к управляющему входу усилителя мощности, четыре компаратора, первые входы которых объединены и предназначены для подключения к выходным зажимам фильтра, источник опорного напряжения, выходом подключенный к делителю напряжения, образованному последовательно соединенными четырьмя резисторами, причем второй вход первого компаратора подключен к точке соединения первого и второго резисторов делителя, второй вход второго компаратора подключен к точке соединения второго и третьего резисторов делителя, второй вход третьего компаратора подключен к точке

соединения первого резистора делителя и выхода источника опорного напряжения, второй вход четвертого компаратора подключен к точке соединения третьего и четвертого резисторов делителя, а выходы

третьего и четвертого компараторов подключены к входам первого элемента 2 ИЛИ, выход которого подключен к входу первого элемента 2 И, второй вход которого соединен со счетным входом второго двоичного

счетчика, с S-входом упомянутого RS-триггера и выходом последнего разряда первого двоичного счетчика, выход первого элемента 2 И подключен к первому входу второго элемента 2 ИЛИ, второй вход которого подключей к выходу второго двоичного счетчика, а выход - к счетному входу реверсивного счетчика, отличающееся тем, что, с целью повышения качества выходного напряжения, оно снабжено вторым

и третьим элементами 2 И, элементом ИЛИ и элементом И-НЕ, входы двух последних объединены и подключены к выходам вышеупомянутого реверсивного счетчика, вход разрешения

прямого счета которого подключен к выходу третьего элемента 2 И, а вход разрешения обратного счета - к выходу второго элемента 2 И, первый вход которого соединен с выходом первого компаратора, второй вход

- с выходом элемента ИЛИ, первый вход третьего элемента 2 И подключен к выходу второго компаратора, а второй - к выходу элемента И-НЕ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровое устройство для управления стабилизированным конвертором | 1986 |

|

SU1372526A1 |

| Цифровое устройство для управления стабилизированным конвертором | 1989 |

|

SU1702497A1 |

| Устройство для измерения вертикальных перемещений бурильной колонны | 1988 |

|

SU1557315A1 |

| МОДУЛЯЦИОННЫЙ РАДИОМЕТР | 2001 |

|

RU2187824C1 |

| Устройство для управления инвертором | 1990 |

|

SU1709482A1 |

| ПРОТИВОУГОННАЯ СИСТЕМА | 1995 |

|

RU2086437C1 |

| Устройство для управления однотактным преобразователем постоянного напряжения | 1990 |

|

SU1720134A1 |

| Устройство для контроля и управления процессом турбинного бурения | 1987 |

|

SU1461881A1 |

| Устройство для управления конвертором | 1988 |

|

SU1628165A1 |

| МОДУЛЯЦИОННЫЙ РАДИОМЕТР | 2002 |

|

RU2220426C1 |

Изобретение относится к электротехнике и может найти применение при создании источников вторичного электропитания радиоэлектронной аппаратуры. Целью изобретения является повышение качества выходного напряжения конвертера Цифровое устройство для управления стабилизированным конвертером содержит задающий генератор 4, выходом подключенный к первому двоичному счетчику 5, логический компаратор 6, RS-триггер 8, выход которого предназначен для подключения к управляющему входу конвертера. Выход фильтра 3 конвертора подключен к первым входам четырех компараторов 9-12, вторые входы которых подключены к соответствующим точкам резистивного делителя 14 напряжения. Выходы третьего 11 и четвертого 12 компараторов подключены к входам первого элемента 2 ИЛИ 19, выходом подключенного к входу первого элемента 2 И 20. второй вход которого соединен со счетным входом второго двоичного счетчика 21, S- входом RS-триггера 8 и выходом последнего разряда первого двоичного счетчика 5 Выход элемента 2 И 20 подключен к первому входу второго элемента 2 ИЛИ 22, второй вход которого соединен с выходом второго двоичного счетчика 21, а выход - к счетному входу реверсивного счетчика 7. В отличии от известного предлагаемое цифровое устройство снабжено вторым 25 и третьим 26 элементами 2 И, элементами ИЛИ 24 и И-НЕ 23. Соединение указанных элементов не позволяет переключать код реверсивного счетчика с максимального к нулевому и наоборот при переполнении последнего, тем самым устраняя возможные провалы и выплески выходного напряжения конвертера. 1 ил сл с о XI о сл 00 сл

| Устройство для управления широтно-импульсным преобразователем | 1983 |

|

SU1145425A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Цифровое устройство для управления стабилизированным конвертором | 1986 |

|

SU1372526A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1991-09-23—Публикация

1989-10-30—Подача