о

§

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРЕОБРАЗОВАТЕЛЬ ЭНЕРГИИ ЭЛЕКТРОПРИВОДА С ГЕНЕРАТОРНЫМ ТОРМОЖЕНИЕМ | 2008 |

|

RU2392729C1 |

| Устройство для управления грузоподъемным электромагнитом | 1990 |

|

SU1817144A1 |

| Устройство для управления вентильным преобразователем | 1980 |

|

SU1146781A1 |

| РЕКУПЕРИРУЮЩИЙ ЭЛЕКТРОПРИВОД ПЕРЕМЕННОГО ТОКА С ДВУХЗВЕННЫМ ПРЕОБРАЗОВАТЕЛЕМ ЧАСТОТЫ | 2014 |

|

RU2584002C1 |

| СПОСОБ УПРАВЛЕНИЯ ПРЕОБРАЗОВАТЕЛЕМ ТРЕХФАЗНОГО НАПРЯЖЕНИЯ В ВЫСОКОЧАСТОТНОЕ ОДНОФАЗНОЕ И УСТРОЙСТВО ДЛЯ РЕАЛИЗАЦИИ ЭТОГО СПОСОБА | 2007 |

|

RU2337462C1 |

| Трехфазный тиристорный ключ | 1979 |

|

SU851777A1 |

| Устройство для управления тиристорами преобразователя | 1986 |

|

SU1399868A1 |

| МАТРИЧНЫЙ ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ И СПОСОБ УПРАВЛЕНИЯ ИМ | 2004 |

|

RU2251199C1 |

| Преобразователь трехфазного переменного напряжения в постоянное | 1989 |

|

SU1695468A1 |

| Устройство для подачи сварочной проволоки | 1989 |

|

SU1720825A1 |

Изобретение относится к электротехнике и может быть использовано в системах управления вентильными преобразователями. Цель изобретения - повышение помехоустойчивости, надежности и обеспечение унификации входных цепей устройства- для подключения к любой трехфазной сети переменного тока (включенной по схеме, звезда или треугольник). Устройство содержит первый 1, второй 2 и третий 3 усилители-ограничители (УО), логические входы которых подключены к выходу генератора 4 тактовых импульсов и через инвертор 5 соединены с входом записи буферного регистра 6 (БР). Выходы УО 1,2, 3, подключены к входам первого, второго и третьего разрядов БР 6. Выходы первого, второго и третьего разрядов БР 6 соединены с входами четвертого, пятого и шестого разрядов БР 6. Каждый выход БР 6 связан с соответствующим входом формирователя импульсов (ФИ) 7. Выход ФИ 7 является выходом 14 предлагаемого устройства. Первый вход каждого УО подключен через резистор 15 к катоду диода 18 и к базе транзистора 19, коллектор которого через первичную обмотку импульсного трансформатора (ИТр) 20 соединен с эмиттером транзистора 19, анодом диода 18 и через резистор 16 подключен к второму входу УО. Начало вторичной обмотки ИТр 20 является выходом УО и через резистор 17 соединено с входом 21 питания устройства. 7 ил. сл с

Изобретение относится к электротехнике и может быть использовано в системах управления вентильными силовыми преобразователями электроприводов.

Целью изобретения является повышение надежности, помехозащищенности и обеспечение унификации устройства.

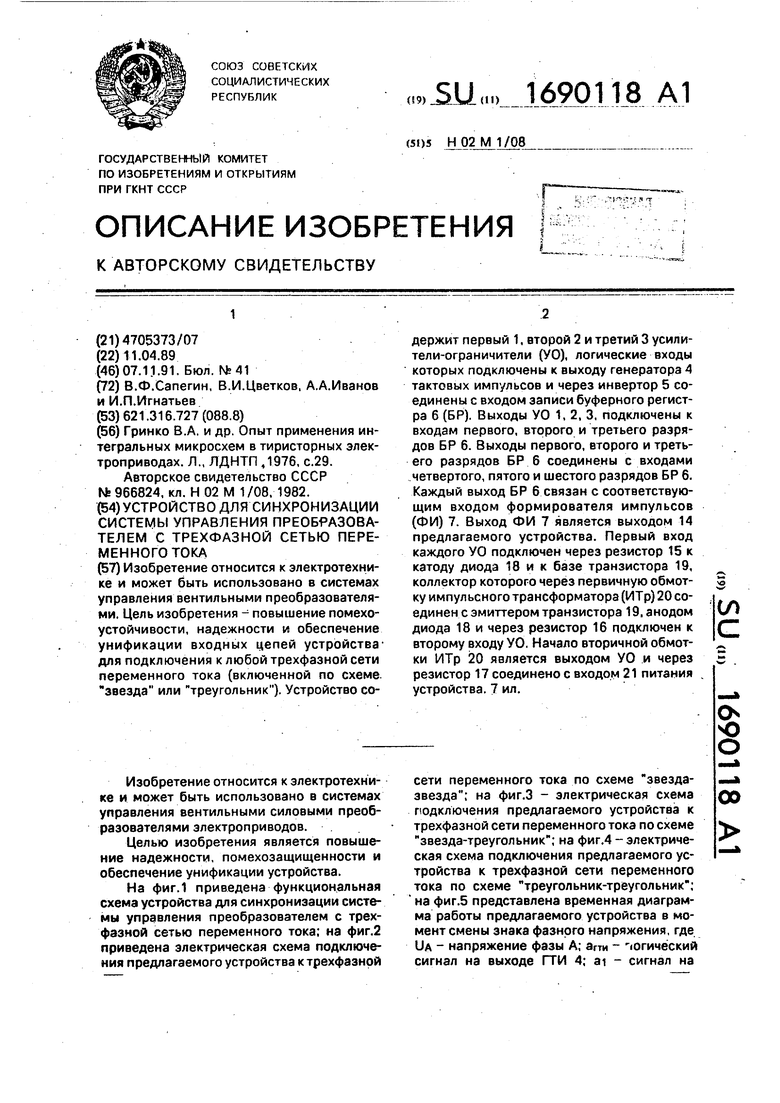

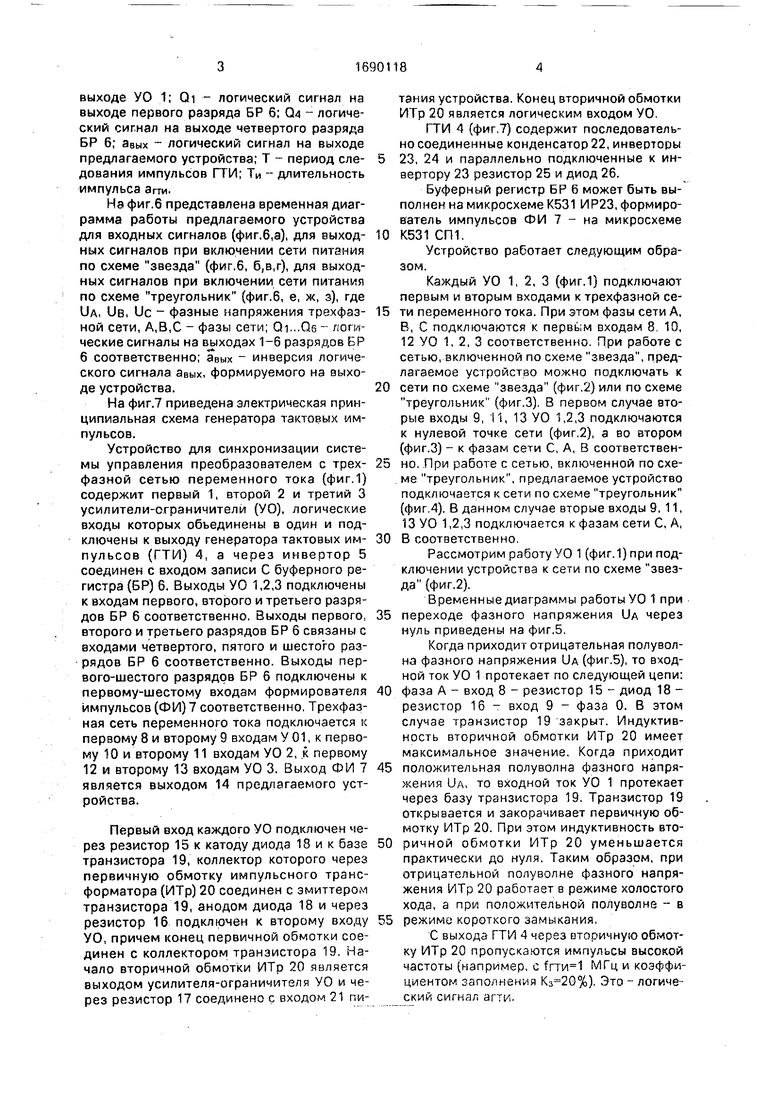

На фиг.1 приведена функциональная схема устройства для синхронизации системы управления преобразователем с трехфазной сетью переменного тока; на фиг.2 приведена электрическая схема подключения предлагаемого устройства к трехфазной

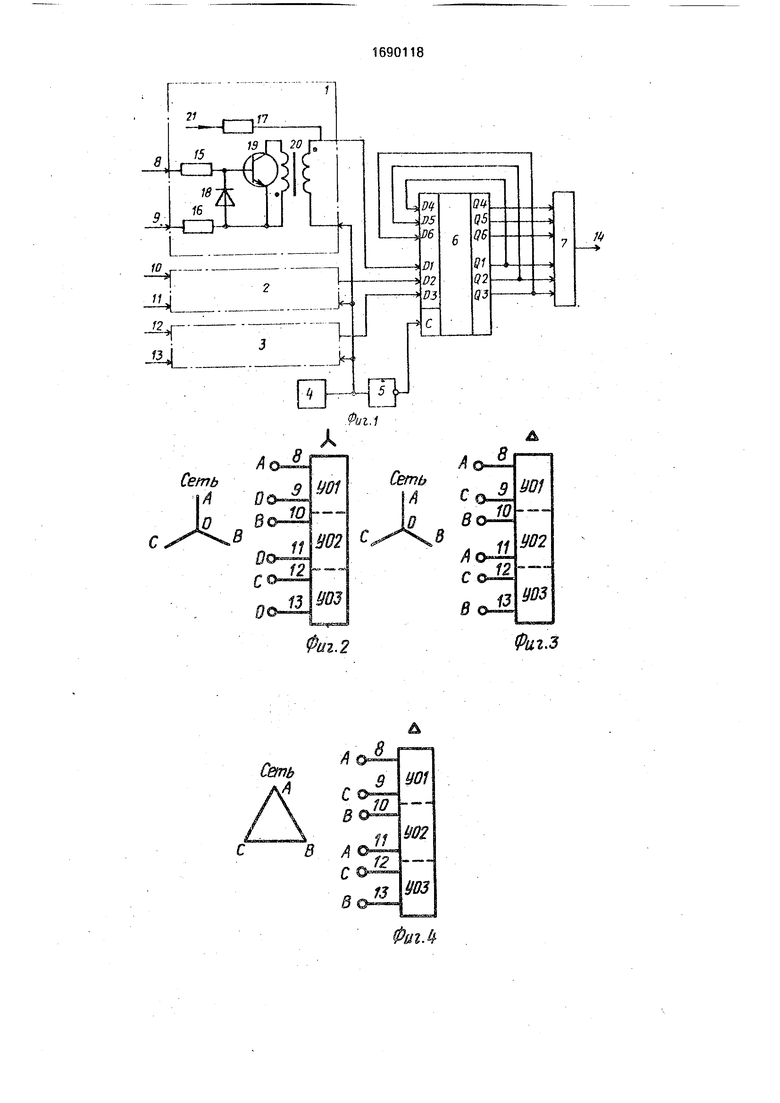

сети переменного тока по схеме звезда- звезда ; на фиг.З - электрическая схема подключения предлагаемого устройства к трехфазной сети переменного тока по схеме звезда-треугольник ; на фиг.4 - электрическая схема подключения предлагаемого устройства к трехфазной сети переменного тока по схеме треугольник-треугольник ; на фиг.5 представлена временная диаграмма работы предлагаемого устройства в момент смены знака фазного напряжения, где UA - напряжение фазы А; а™ - югичёский сигнал на выходе ГТИ 4; ai - сигнал на

00

выходе УО 1; Qi - логический сигнал на выходе первого разряда БР 6; CU - логический сигнал на выходе четвертого разряда БР 6; авых - логический сигнал на выходе предлагаемого устройства; Т - период следования импульсов ГТИ; Ти - длительность импульса Эгти.

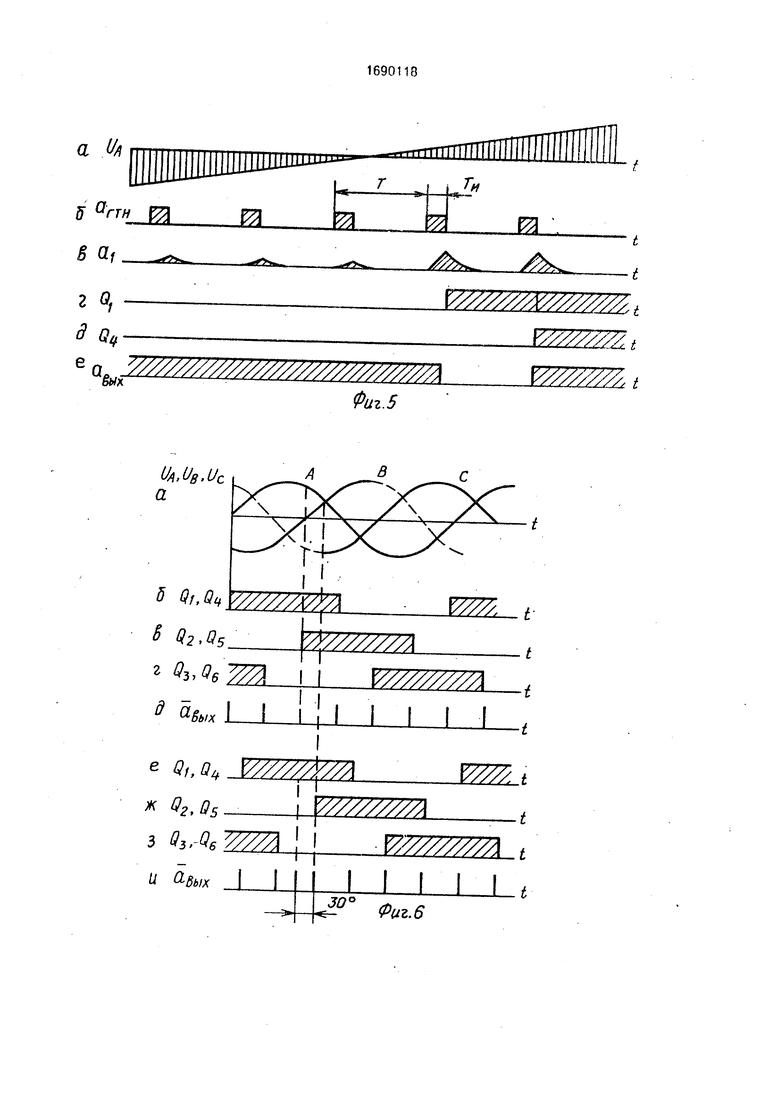

Нэ фиг.б представлена временная диаграмма работы предлагаемого устройства для входных сигналов (фиг.6,а), для еыход- ных сигналов при включении сети питания по схеме звезда (фиг.б, б,в,г), для выходных сигналов при включении сети питания по схеме треугольник (фиг.б, е, ж, з), где UA, UB, Uc - фазные напряжения трехфазной сети, А,В,С - фазы сети; QI...QS - логические сигналы на выходах 1-6 разрядов БР б соответственно; авых - инверсия логического сигнала авых, формируемого на выходе устройства.

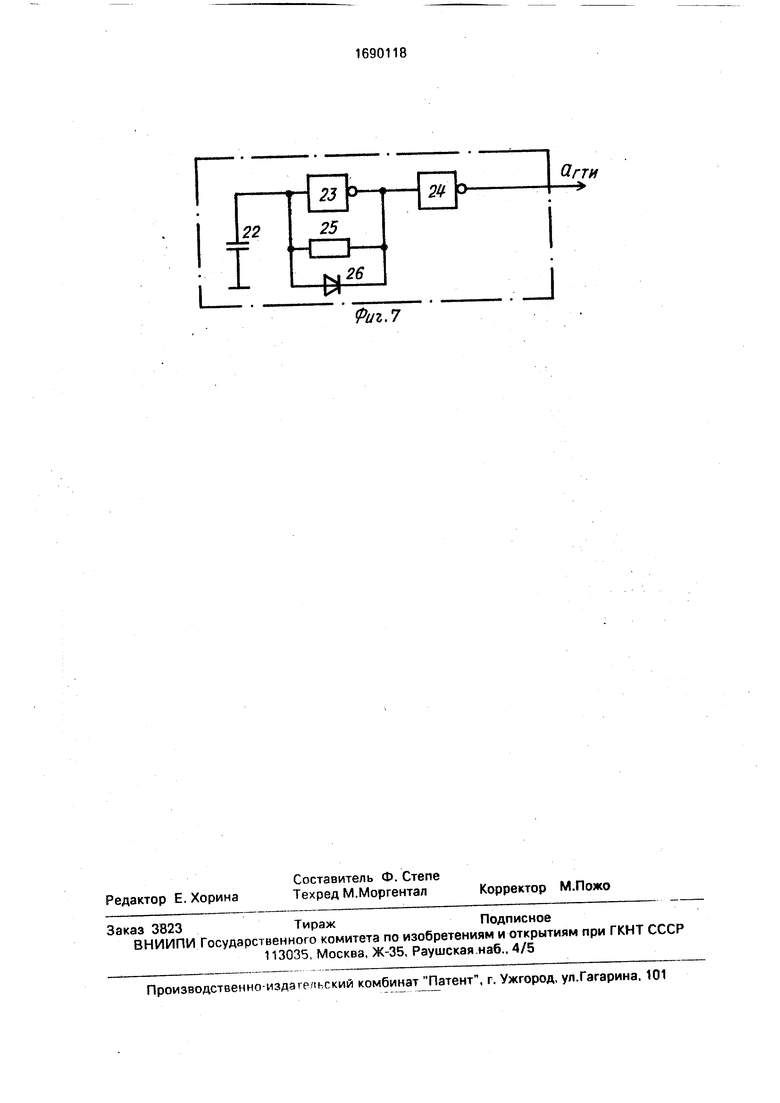

На фиг.7 приведена электрическая принципиальная схема генератора тактовых импульсов.

Устройство для синхронизации системы управления преобразователем с трехфазной сетью переменного тока (фиг.1) содержит первый 1, второй 2 и третий 3 усилители-ограничители (УО), логические входы которых объединены в один и подключены к выходу генератора тактовых импульсов (ГТИ) 4, а через инвертор 5 соединен с входом записи С буферного регистра (БР) 6. Выходы УО 1,2,3 подключены к входам первого, второго и третьего разрядов БР 6 соответственно. Выходы первого, второго и третьего разрядов БР 6 связаны с входами четвертого, пятого и шестого разрядов БР 6 соответственно. Выходы пер- вого-шестого разрядов БР б подключены к первому-шестому входам формирователя импульсов (ФИ) 7 соответственно. Трехфазная сеть переменного тока подключается к первому 8 и второму 9 входам У 01, к первому 10 и второму 11 входам УО 2, к первому 12 и второму 13 входам УО 3. Выход ФИ 7 является выходом 14 предлагаемого устройства.

Первый вход каждого УО подключен через резистор 15 к катоду диода 18 и к базе транзистора 19, коллектор которого через первичную обмотку импульсного трансформатора (ИТр) 20 соединен с эмиттером транзистора 19, анодом диода 18 и через резистор 16 подключен к второму входу УО, причем конец первичной обмотки соединен с коллектором транзистора 19. Начало вторичной обмотки ИТр 20 является выходом усилителя-ограничителя УО и через резистор 17 соединено с входом 21 питания устройства. Конец вторичной обмотки ИТр 20 является логическим входом УО.

ГТИ 4 (фиг.7) содержит последовательно соединенные конденсатор 22, инверторы 23, 24 и параллельно подключенные к инвертору 23 резистор 25 и диод 26.

Буферный регистр БР 6 может быть выполнен на микросхеме К531 ИР23, формирователь импульсов ФИ 7 - на микросхеме 0 К531 СП1.

Устройство работает следующим образом.

Каждый УО 1, 2, 3 (фиг.1) подключают

первым и вторым входами к трехфазной се5 ти переменного тока. При этом фазы сети А,

В, С подключаются к первь.м входам 8 10,

12УО 1, 2, 3 соответственно. При работе с сетью, включенной по схеме звезда, предлагаемое устройство можно подключать к

0 сети по схеме звезда (фиг.2) или по схеме треугольник (фиг.З). В первом случае ато- рые входы 9, 11, 13 УО 1,2,3 подключаются к нулевой точке сети (фиг.2), а во втором (фиг.З) - к фазам сети С, А, В соответствен5 но. При работе с сетью, включенной по схеме треугольник, предлагаемое устройство подключается к сети по схеме треугольник (фиг.4). В данном случае вторые входы 9,11,

13УО 1,2,3 подключается к фазам сети С, А, 0 В соответственно.

Рассмотрим работу УО 1 (фиг.1) при подключении устройства к сети по схеме звезда (фиг.2).

Временные диаграммы работы УО 1 при

5 переходе фазного напряжения UA через нуль приведены на фиг.5.

Когда приходит отрицательная полуволна фазного напряжения UA (фиг.5), то входной ток УО 1 протекает по следующей цепи:

0 фаза А - вход 8 - резистор 15 - диод 18 - резистор 16 - вход 9 - фаза 0. В этом случае транзистор 19 закрыт. Индуктивность вторичной обмотки ИТр 20 имеет максимальное значение. Когда приходит

5 положительная полуволна фазного напряжения UA, то входной ток УО 1 протекает через базу транзистора 19. Транзистор 19 открывается и закорачивает первичную обмотку ИТр 20. При этом индуктивность вто0 ричной обмотки ИТр 20 уменьшается практически до нуля. Таким образом, при отрицательной полуволне фазного напряжения ИТр 20 работает в режиме холостого хода, а при положительной полуволне - в

5 режиме короткого замыкания,

С выхода ГТИ 4 через вторичную обмотку ИТр 20 пропускаются импульсы высокой частоты (например, с МГц и коэффициентом заполнения ). Это - логический сигнал агти.

В зависимости от знака фазного напряжения UA меняются параметры цепи прохождения сигнала агти, который формируется на выходе ГТИ 4. При этом логический сигнал ai, формируемый на выходе УО 1, принимает следующие значения:

при UA О,

при UA 0.

Состояние выхода УО 1 записывается только по заднему фронту импульса агти в первый разряд буферного регистра 6.

Аналогично работают и УО 2,3. Состояния выходов УО 2, 3 записываются в разряды 2 и 3 БР 6 соответственно. Состояния выходов УО 1, 2, 3 однозначно соответствуют знакам фазных напряжений UA, UB, Uc. В разрядах 1, 2,3 БР б хранятся состояния выходов УО 1, 2,3, соответствующие моменту , а в разрядах 4, 5,6 - состояния выходов УО 1, 2,3 , соответствующие предыдущему моменту времени (n-1), где п - номер такта дискретизации устройства. Эти состояния фазных напряжений сети записываются в БР 6 по заднему фронту импульса агти.

Таким образом, новое состояние выходов УО 1, 2, 3 записывается в разряды 1,2,3, а старое переписывается с выходов разрядов 1, 2, 3 в разряды 4, 5, 6 соответственно. Эти состояния различны только в момент перехода одного из фазных напряжений А, В или С через нуль. В остальное время соседние состояния выходов УО 1, 2, 3 одинаковы. Соседние состояния выходов УО 1, 2, 3 подаются на ФИ 7, который представляет собой схему сравнения. ФИ 7 формирует на своем выходе импульс авых несовпадения соседних состояний длительностью Т. (фиг.5). Этот импульс является выходным импульсом синхронизатора. Он формируется, когда соседние состояния выходов УО 1, 2,3, зафиксированные в БР 6, не одинаковы. Для промышленной сети питания с частотой 50 Гц формирование импульсов авых на выходе устройства для синхронизации осуществляется с частотой 300 Гц.

Сигнал авых используется в схеме цифровой системы импульсно-фазового управления (ДСИФУ), которая формирует импульсы управления тиристорами. Группа сигналов Qi, Q2, Оз (или группа сигналов CU. 0.5, Об), формируемая на выходах БР 6. также используется в ЦСИФУ.

Характер изменения входных и выходных сигналов устройства представлен на фиг.6.

Работа устройства при подключении его к сети переменного токз по схема ipeyt оль ник (фиг.З и 4) происходит аналогично ра боте устройства при подключении его к сети по схеме звезда (фиг.2).

Формула изобретения Устройство для синхронизации системы

управления преобразователем с трехфазной сетью переменного тока, содерж-ащее формирователь импульсов, первый, второй и третий усилители-ограничители, отличающееся тем, что, с цельго повышения

надежности у, помехоустойчивости и обеспечения унификации устройства введены буферный регистр, генератор тактовых импульсов и инвертор, причем каждый из трех усилителей-ограничителей содержит первый, второй и третий резисторы, диод, транзистор и импульсный трансформатор, начало вторичной обмотки которого является выходом усилителя-ограничителя, а конец - его входом, подключенным к выходу

генератора тактовых импульсов, а через инвертор - к входу записи буферного регистра, входы первого, второго и третьего разрядов которого подключены к аыходам первого, второго и третьего усилителей-ограничителей соответственно, а входы четвертого, пятого и шестого разрядов буферного регистра соединены с выходами первого, второго и третьего разрядов буферного регистра соответственно, выходы

первого, второго, третьего и выходы четвертого, пятого, шестого разрядов буферного регистра соединены соответственно с первой и второй группой входов формирователя импульсов, одноименные входы

которого объединены по схеме несовпаде- ния( выход формирователя импульсов является выходом устройства, при этом первый вход каждого усилителя-ограничителя подключен через первый резистор к

катоду диода и к базе транзистора, коллектор которого через первичную обмотку импульсного трансформатора соединен с эмиттером транзистора, причем конец первичной обмотки соединен с коллектором транзистора, качало вторичной обмотки импульсного трансформатора подключено через третий резистор к входу питания устройства, а эмиттер транзистора подключен к аноду диода и через второй

резистор к второму входу усилителя-ограничителя.

а Щ

5 °гтн УЯ

В Ъ

г о1

д Q

еае

&/

Фиг.5

UA,UB,UC а

/У///////Л

УЯЯ. t

t

Qi.Qtt

Q2,Q5

I I W////////A t

йл/х I I I { I I I I -I f

I Qi.Q W///// /ft

93Л%%Я 1

I Г

KZZt Y//S/77Z7 t

У/У///////Л f

U О-Вых JI

s й

&ШЈ&ь

Ш7//7/7/,.

Фиг.5

УЯЯ. t

t

У/У///////Л f

Mill.

30l

Фиг.6

| Гринко В.А | |||

| и др | |||

| Опыт применения интегральных микросхем в тиристорных электроприводах | |||

| Л., ЛДНТП ,1976, с.29 | |||

| Устройство для синхронизации системы управления преобразователем с трехфазной сетью переменного тока | 1981 |

|

SU966824A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1991-11-07—Публикация

1989-04-11—Подача