СО

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления двухканальным трехфазным преобразователем | 1991 |

|

SU1826116A1 |

| Преобразователь с многофазной широтноимпульсной модуляцией | 1991 |

|

SU1793523A1 |

| Однофазный преобразователь с многофазной ШИМ | 1991 |

|

SU1823113A1 |

| Устройство для коммутации многоадресных сообщений | 1986 |

|

SU1387007A1 |

| Преобразователь постоянного напряжения в регулируемое трехфазное | 1986 |

|

SU1334323A1 |

| Устройство для управления преобразователем постоянного напряжения в квазисинусоидальное с промежуточным высокочастотным преобразованием | 1981 |

|

SU1297198A1 |

| Способ приработки двигателя внутреннего сгорания и устройство для его осуществления | 1989 |

|

SU1663477A1 |

| Устройство для управления трехфазным инвертором | 1986 |

|

SU1791939A1 |

| Устройство для управления преобразователем постоянного напряжения в квазисинусоидальное трехфазное | 1985 |

|

SU1304150A1 |

| Трехфазный преобразователь | 1985 |

|

SU1443099A1 |

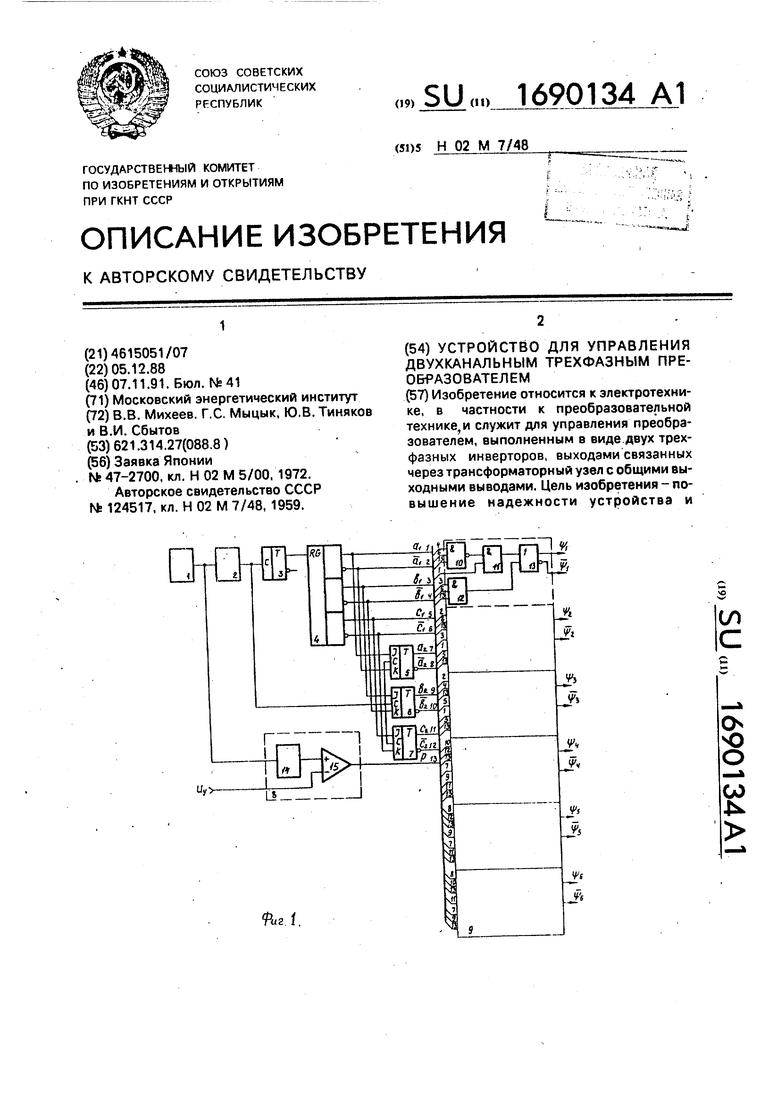

Изобретение относится к электротехнике, в частности к преобразовательной технике,и служит для управления преобразователем, выполненным в виде двух трехфазных инверторов, выходами связанных через трансформаторный узел с общими выходными выводами. Цель изобретения - повышение надежности устройства и

а ю о

00

расширения функциональных возможностей. Устройство содержит последовательно связанные между собой задатчик 1 частоты, делитель 2, Т-триггер 3, первый формирователь 4 управляющих импульсов. Выходы формирователя 4 соединены с соответствующими входами IK-триггеров 5-7, образующих второй формирователь импульсов. Счетные входы триггеров 5-7 соединены с выходом делителя 2. Модулятор 8 ширины импульсов тактовым входом связан с выходом задатчика 1. Информационный вход модулятора 8 является управляющим входом устройства.-Выходной вывод рмодулятора 8 и парафазные выходы первого и второго формирователей импульсов ai, ai,

bl, bl, C1, C1, 32, 32,D2. D2, C2, C2 ПОДКЛЮЧ6НЫ

Изобретение относится к электротехнике, в частности к преобразовательной технике, и может быть использовано при построении преобразователей постоянного напряжения в регулируемое или стабилизи- рованное по величинетр ехфазное напряже- ние как в системах управляемого электропривода, так и в автономных системах централизованного питания в тех случаях, когда требуются предельно высокие массогабаритные показатели и повышенная функциональная надежность.

Цель изобретения - повышение надежности устройства за счет исключения возможности расфазировки импульсов и расширение функциональных возможностей за счет обеспечения регулирования величины выходного напряжения.

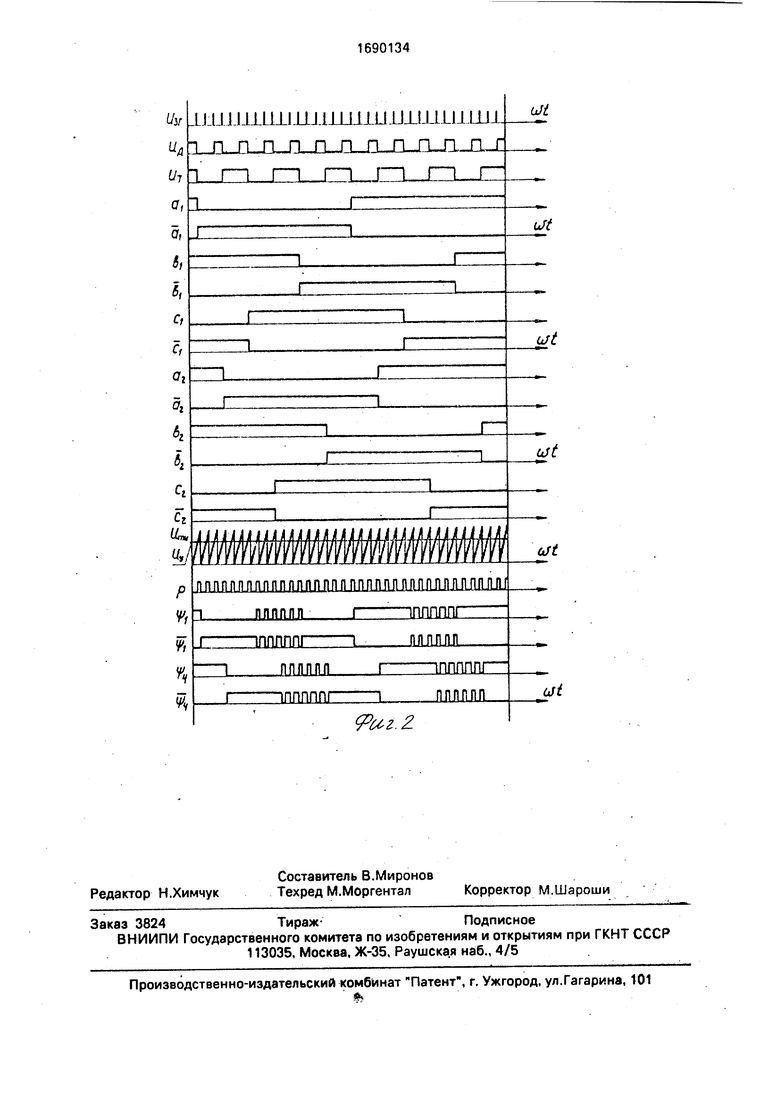

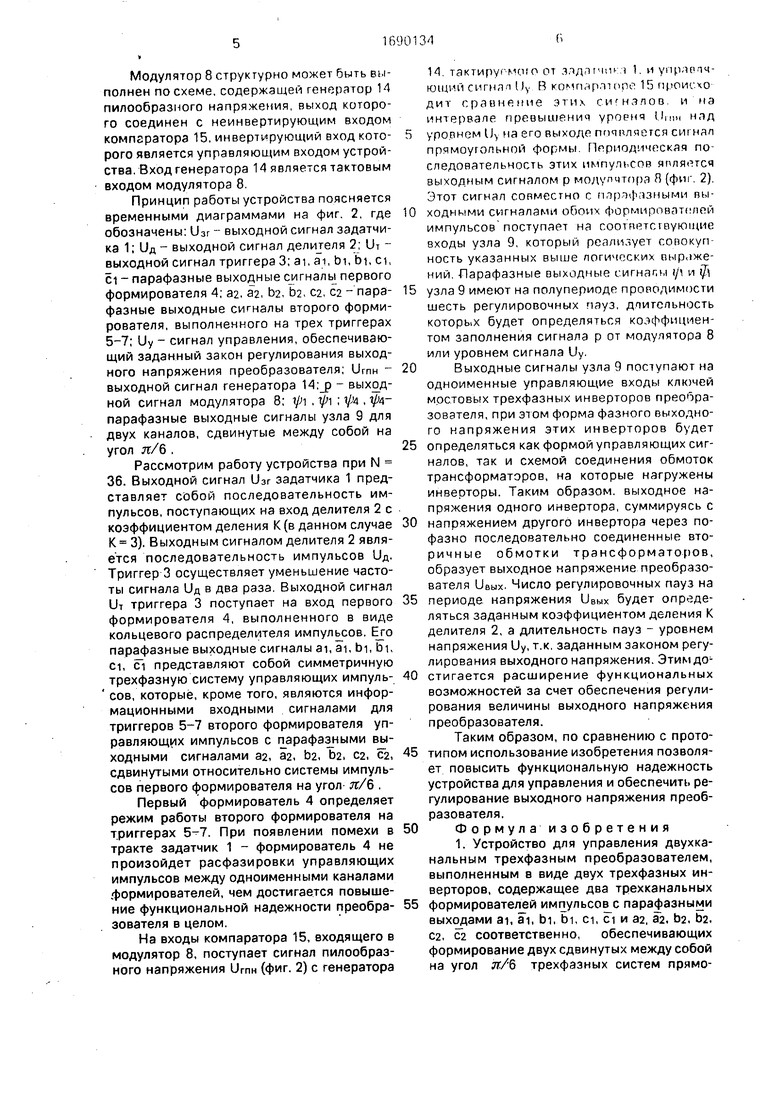

На фиг. 1 представлена структурная схема устройства; на фиг. 2 - временные диаграммы работы устройства управления.

Устройство содержит последовательно связанные между собой задатчик 1 частоты, делитель 2 частоты, Т-триггер 3, первый формирователь 4 управляющих импульсов. Выходы формирователя 4 соединены с I- и К-входами IK триггеров 5-7, образующих второй формирователь упавляющих импульсов. Счетные входы триггеров 5-7 соединены с выходом делителя 2. Модулятор 8 ширины импульсов тактовым входом связан с выходом задатчика 1. Информационный вход модулятора 8 является управляющим входом устройства. Выходной вывод р модулятора 8 и парафазные выходы первого и второго формирователей ai, ai, bi, bi, ci, ci,

к соответствующим входам логического узла 9 с парафазными выходами ty ,$, где I И,6, логический узел 9 обеспечивает реализацию логических выражений:

Vi а 1 (bi d р) + bl ci р , #2 bi (ai ci p) + ai ci p , Vu ci (ai bi p) + ai bi p ,

1A 32 ( Ь2 С2 p ) + D2 C2 p , #5 b2 ( 32 C2 P ) + 32 . C2 P , Yfc C2 ( 32 P ) + 32 D2 P ,

2 з.п,ф-лы, 2 ил.

32, 32, D2, D2, C2, C2 ПОДКЛЮЧвНЫ К СООТВвТСТвующим входам логического узла (ЛУ) 9 с парафазными выходами fyft так, что при соответствующем выполнении каналов ЛУ 9 обеспечивается реализация логических выражений

Vi э 1 (bi ci p) + bici p,

t/fc bi (ai ci p) +31 ci p, #3 ci ( bi p) + ai bi p ,

32 ( Ь2 С2 P ) + Ь2 С2 P , 1р5 Ь2(Э2С2Р)+Э2 С2Р, C2 ( 32 b2 P ) + 32 D2 P ,

В качестве примера выполнения одного из кзналов узла 9 на фиг. 1 изображена структурная схема, содержащая элемент ЗИ-НЕ, входами связанный с выходами bi, ci формирователя и выходом р модулятора 8 и своим выходом соединенный с первым входом элемента 2И 11, второй вход элемента 2И 11 соединен с выходом ai формирователя 4. Входы элемента ЗИ 12 соединены с выходами bi, ci формирователя 4 и выходом р модулятора 8. Выходы элементов 11 и 12 связаны гс входами элемента 2ИЛИ 13, име- прямой и инверсный выходы и 1 соответственно. Аналогично выпол- нены остальные каналы узла 9, выходы ул и$ которого используются как выходы устройства при регулировании выходного напряжения.

Модулятор 8 структурно может быть выполнен по схеме, содержащем генератор 14 пилообразного напряжения, выход которого соединен с неинвертирующим входом компаратора 15, инвертирующий вход кото- рого является управляющим входом устройства. Вход генератора 14 является тактовым входом модулятора 8

Принцип работы устройства поясняется временными диаграммами на фиг. 2, где обозначены: U3r - выходной сигнал задатчи- ка 1; ид - выходной сигнал делителя 2, UT - выходной сигнал триггера 3; ai, at, bi, bi, ci, C1 - парафазные выходные сигналы первого формирователя 4; 32. 32, 02, Ь2. С2, С2 - пара- фазные выходные сигналы второго формирователя, выполненного на трех триггерах 5-7; Uy - сигнал управления, обеспечивающий заданный закон регулирования выходного напряжения преобразователя, Утн - выходной сигнал генератора - выходной сигнал модулятора 8; , 1 ; V 4 , Ф4 парафазные выходные сигналы узла 9 для двух каналов, сдвинутые между собой на угол я/6 .

Рассмотрим работу устройства при N 36. Выходной сигнал U3r задатчика 1 представляет собой последовательность импульсов, поступающих на вход делителя 2 с коэффициентом деления К (в данном случае К 3). Выходным сигналом делителя 2 является последовательность импульсов 11д. Триггер 3 осуществляет уменьшение частоты сигнала 11Д в два раза Выходной сигнал UT триггера 3 поступает на вход первого формирователя 4, выполненного в виде кольцевого распределителя импульсов. Его парафазные выходные сигналы ai,Ґi, bi, bi, ci, ci представляют собой симметричную трехфазную систему управляющих импуль- сов, которые, кроме того, являются информационными входными сигналами для триггеров 5-7 второго формирователя управляющих импульсов с парафазными выходными Сигналами 32, 32, Ь2, D2, С2, ,

сдвинутыми относительно системы импульсов первого формирователя на угол я/6 .

Первый формирователь 4 определяет режим работы второго формирователя на триггерах 5-7. При появлении помехи в тракте задатчик 1 - формирователь 4 не произойдет расфазировки управляющих импульсов между одноименными каналами формирователей, чем достигается повышение функциональной надежности преобра- зователя в целом.

На входы компаратора 15, входящего в модулятор 8, поступает сигнал пилообразного напряжения Огпн (фиг. 2) с генератора

14 тактирус мою от пдлгин ) 1 иупрлгпч- ющий сигнал Us В ком пнр попе 15 прсни хо дит г рай не кие этих си нэпов и па интервале превышения урорнч II,м над уровнем UY на его выходе появляется cm ндл прямоугольной формы Периодическая по следовательчогль этих импутьсор япляетсч выходным сигналом р модупчтпра В (фш 2) Этот сигнал совместно г илртф зными выходными сигналами обоих формирователей импульсов поступает на соответствующие входы узла 9, который реализует сопокуп ность указанных выше ЛОГИЧРСКИХ выражений Ларафазные выходные (.игнапм i/ и tf узла 9 имеют на полупериоде проводимости шесть регулировочных пауз, длительность которых будет определяться коэффициентом заполнения сигнала р от модулятора 8 или уровнем сигнала Uy

Выходные сигналы узла 9 поступают на одноименные управляющие входы ключей мостовых трехфазных инверторов преобразователя, при этом форма фазного выходного напряжения этих инверторов будет определяться как формой управляющих сигналов, так и схемой соединения обмоток трансформаторов, на которые нагружены инвесторы. Таким образом выходное напряжения одного инвертора, суммируясь с напряжением другого инвертора через по- фазно последовательно соединенные вторичные обмотки трансформаторов, образует выходное напряжение преобразователя Увых Число регулировочных пауз на периоде напряжения 11Вых будет определяться заданным коэффициентом деления К делителя 2, а длительность пауз - уровнем напряжения Uy, т.к заданным законом регулирования выходного напряжения. Этимдо- стигается расширение функциональных возможностей за счет обеспечения регулирования величины выходного напряжения преобразователя.

Таким образом, по сравнению с прототипом использование изобретения позволяет повысить функциональную надежность устройства для управления и обеспечить регулирование выходного напряжения преобразователя.

Формула изобретения

2,Устройство по п. 1,отличающее: с я тем, что указанная связь входа Т-триг- гера и выхода задатчика частоты осуществлена непосредственно.

К N/12, где N- число регулировочных пауз на периоде выходного напряжения, модулятором ширины импульсов с выходным сигналом р и шестиканальным логическим уз- лом с парафазными выходами $ , i/i, где I

1,6, причем указанная связь задатчика частоты и Т-триггера осуществлена так, что

ходы делителя частоты и модулятора ширины импульсов подключены к выходу задатчика частоты, выход делителя частоты подключен к входу Т-триггера, выход модулятора ширины импульсов подключен к одним входам логического узла, другие входы которого подключены к выходам первого и второго формирователей управляющих импульсов, структура логического узла определяется выражениями:

Vi а 1 (bi ci р) + bi ci р , Vfc bi (ai p) 4- aici р . трз - ci ( bi p ) + ai bi p ,

t/M 32 ( 02 C2 P ) + D2 C2 P , 5 D2 ( 32 C2 P ) + 32 C2 P

Vfc C2 ( 32 02 P ) + 32 02 P ,

а вход управления модулятора ширины импульсов использован для подключения источника управления, а выходы логического узла использованы как выходы устройства управления.

| Способ очищения сернокислого глинозема от железа | 1920 |

|

SU47A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Преобразователь постоянного тока в переменный | 1959 |

|

SU124517A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1991-11-07—Публикация

1988-12-05—Подача