Изобретение относится к электротехнике и предназначается преимущественно для управления инверторами в системах электропитания и электропривода для преобразования постоянного напряжения в многофазное переменное напряжение с широтно-импульсной модуляцией по закону, близкому к синусоидальному.

Целью изобретения является повышение надежности.

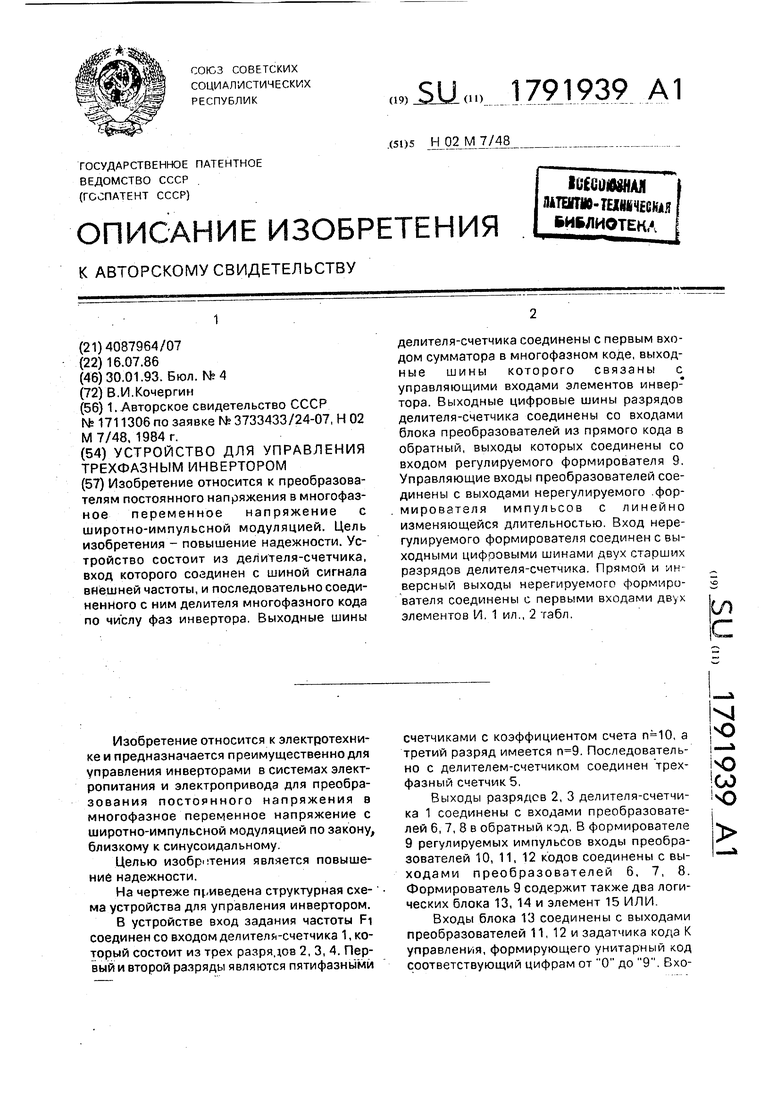

На чертеже приведена структурная схе- ма устройства для управления инвертором.

В устройстве вход задания частоты FI соединен со входом делителя-счетчика 1, который состоит из трех разрядов 2, 3, 4. Первый и второй разряды являются пятифазнымй

,- - .. -.. -;ч.Д ;15ЖйжХ;,:М4а:Л(( ;

счетчиками с коэффициентом счета , а третий разряд имеется . Последовательно с делителем-сч етчико ШёдйШ н трехфазный счетчик 5,

Выходы разрядов 2, 3 делителя-счетчика 1 соединены с входами преобразователей 6,7, 8 в обратный код. В формирователе 9 регулируемых импульсов входы преобразователей 10, 11, 12 кодов соединены с выходами преобразователей 6, 7, 8. Формирователь 9 содержит также два логических блока 13, 14 и элемент 15 ИЛИ.

Входы блока 13 соединены с выходами преобразователей 11, 12 и задатчика кода К управления, формирующего унитарный код соответствующий цифрам от О до 9. ВхоХ|

ю

ю со

sQ

ды блока 14 соединены с выходами преобразователей 10,11, 12 и также с задзтчиком кода К. Выходы блоков 1.3. 14 и старший разряд кода К соединены с входами элемента 15, выход которого является выходом формирователя 9. Выход элемента 15 соединен с первыми вход ами элементов 16, 17 И. Входы нерегулируемого формирователя 18 импульсов с линеДно изменяющейся дли- т л ьностёю йЦпуЯЙсЬв оединены с выходами двух cTavp;ul lixj разрядов 3, 4 дедителя-Й ётчика 1; а прямой и инверсный Выходы соединены с управляющими входами преобразователей 6, 7, 8 и вторыми вхо- дами элементов 1.6, 17, Выходы элементов 16, 17 соединены со входами W и V логического сумматора 19, Другие входы которого соединены с выходом счетчика 5. Выходы сумматора 19 соединены с управляющими входами силовых элементов, например, транзисторов инвертора 20.

Логические выражения, определяющие структуры преобразователей б, 7, имеют вид /V ,..;... ;... ;:, ./-:/ .. - /

структура преобразователя 8 описывается уравнением

где аг, сигналы на соответствующих выходах преобразователей; , c i - на выходах разрядов 2, 3, 4; р - на выходах формирователя 18. .- .Структура преобразователей 10 и 11 определяется уравнениями . согнав, ,

l&Haaas. ,

уа-аза5, ,

, .

где a... t - сигналы на выходах преобразователей 10 и. 11.

ai - сигналы на выходах преобразователей 6 или 7.

Преобразователь 12 формирует на выходе сигналы по следующим логическим выражениям

tc C1C5; ZC C2C5: .

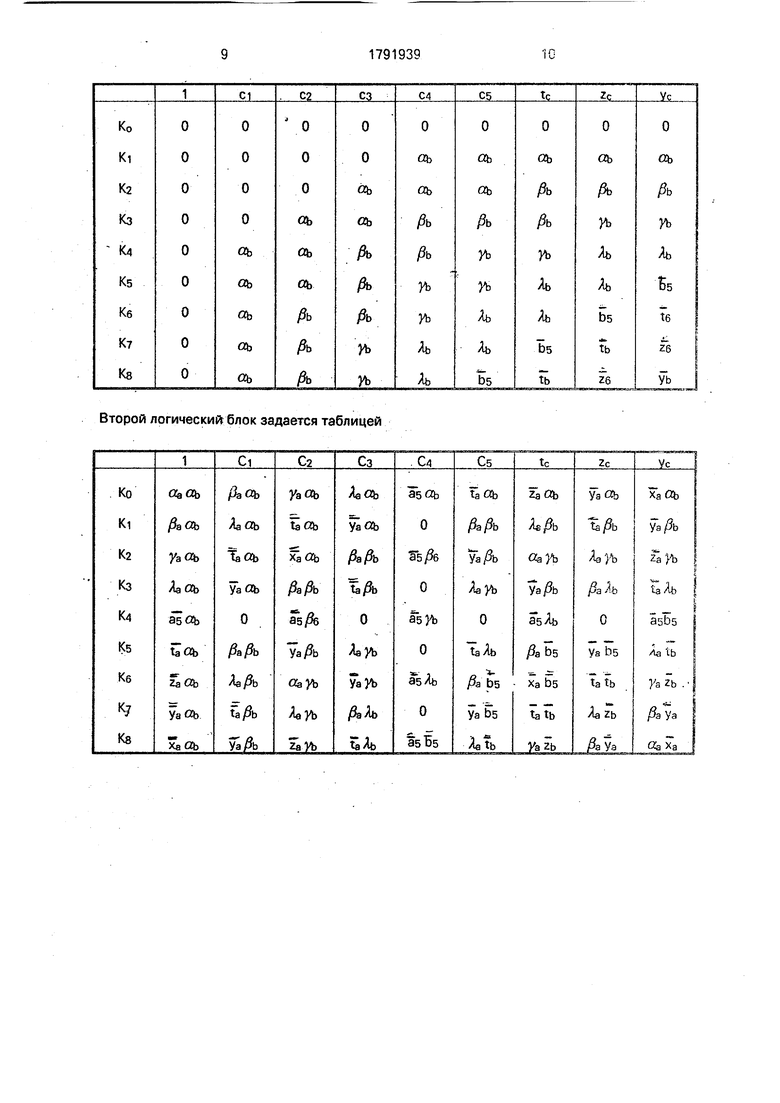

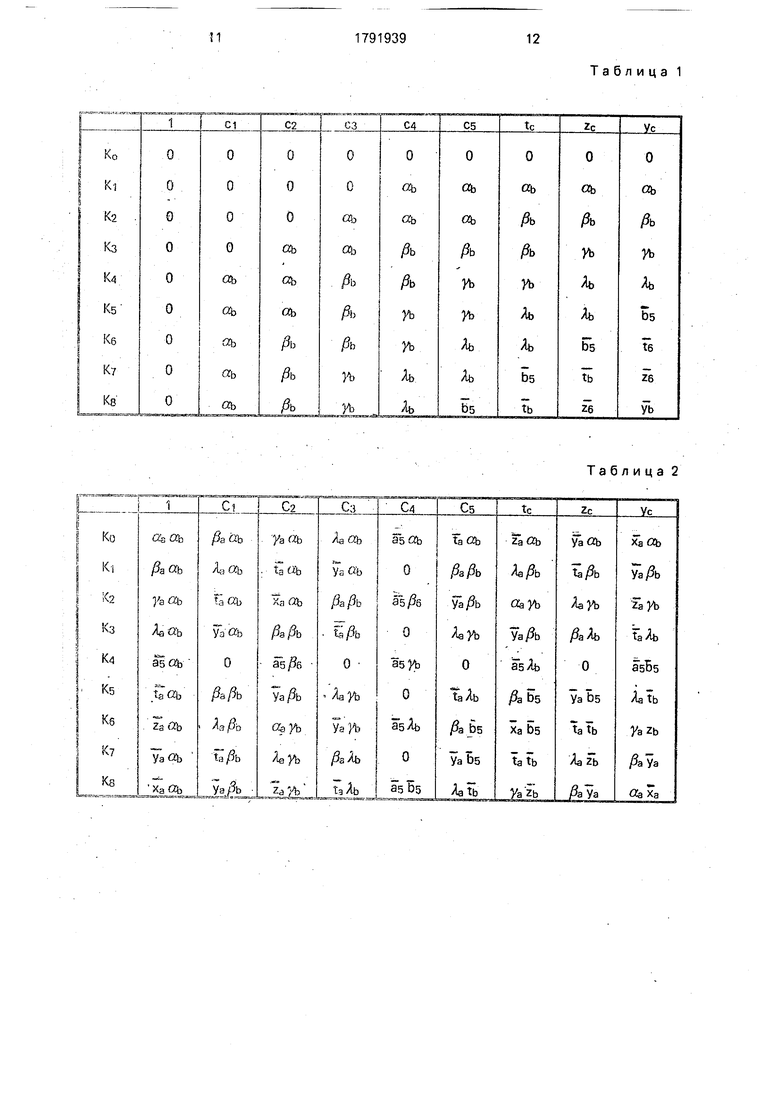

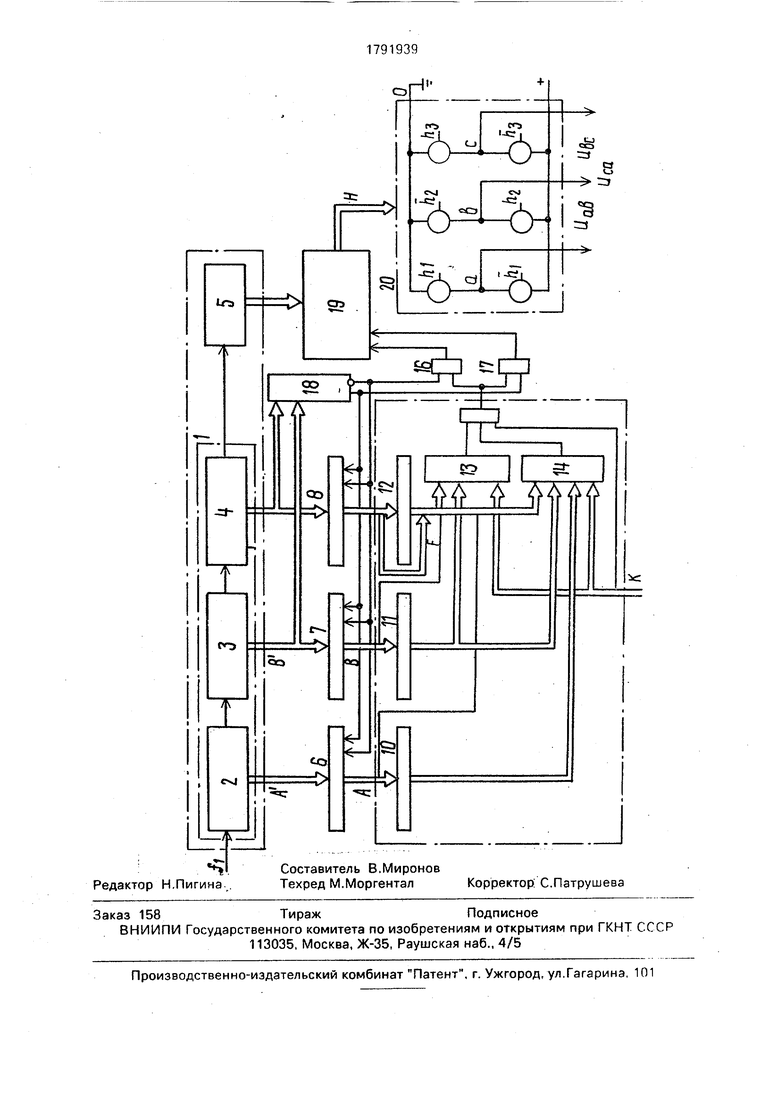

Структура блоков 13, 14 строится в соответствии с дизъюнкцией всех логических произведений, определяемых соответствующим сигналом кода К, указанного в строке таблиц 1,2, выходилм сигналом преобразователя 12 или разряда 4, указанных в столбце таблиц и выходных сигналов

Оа, , Уа, Аа, 35, Ха, уа, Za, ta, «b. , УЬ, Ab, Ьб.

хь, уь, zb, tb преобразователей 10, 11 и 6,7,указанных на пересечении соответствующей строки и столбца.

Построение формирователя 18 определяется следующим логическим выражением v Бз bgca v b4 ЬБСЗ v Fsc4

V blC5 V b2C5C1 V ЬзС5С2 V Ь4Сб5з.

Структура сумматора 19 определяется логическими выражениями: w v ds v v e

w v di v v e w F, v da v v Ј w v, e did2v didsv dads

Устройство работает следующим образом.

При любых значениях входного кода К делитель-счетчик 1 и последовательно соединенный с ним счетчик 5 осуществляют счет входных импульсов частоты fi, когда за каждый цикл переключения предыдущего

разряда; последующий разряд увеличивает свое значение на единицу.

При максимальном значении входного: кода на третьем входе элемента 15 и соответственно на первых водах элементов

16, 17 всегда имеется сигнал . Поэтому на первом входе сумматора 19 присутствуют только сигналы с выходов формирователя 18 , .

В исходном состоянии делителя-счетчика 1 на выходе формирователя 18 существует сигнал . Это значение выходного сигнала будет существовать в течение первого цикла переключения первого разряда 2 делителя-счетчика 1, когда состояние второго разряда 3 равно 0. При дальнейшем счете входных импульсов, когда первый разряд 2 совершит еще девять циклов, а состояние второго разряда 3 при этом будет изменяться от 1 до 9, значение сигнала на

выходе формирователя 18 сохраняется нулевым .

Таким образом, за цикл переключения первых двух разрядов 2 и 3, когда состояние третьего разряда 4 равно на выходе формирователя 18 будет существовать сигнал длительностью в 10 периодов входной частоты, а сигнал будет иметь длительность в 90 периодов входной частоты.

Второй цикл переключения первых двух

разрядов 2 и 3 делителя-счетчика 1 начинается, когда третий разряд 4 устанавливается в состояние 1 и . Это значение сигнале будет существовать в течение первых двух циклов переключения разряда 2 делителя-счетчика 1, когда состояние второго разряда.З изменяется от 0 до 1 включительно. При дальнейшем счете когда первый разряд 2 совершит ещё восемь цйклрв, а состояние второго рёзряДаЗ при этом будет изменяться; от 2 до 9, значение сигнала на выходе формирователя 18 будет нулевое . Следовательно, за цикл переключения первых двух разрядов вi первом Состоянии разряда 4 на выходе формирователя 18 бу- . детсформирован сигнал длительностью в 20 периодов входной частоты, а сигнал будет иметь длительность в 80 периодов входной частоты и т.д. вплоть до восьмого состояния разряда 4, когда за цикл пере- ключеййя первых: Двух разрядов на выходе формирователя 18 будет сформирован сиг нал р I длительностью в 90 периодов вход- ной частоты, а сйгйал будет иметь длительность :в 10 периодов входной часто- ты;;; ; : .).: -:-: У

Линейно возрастающие по длительно- сти сигналь р и их инверсии pf которое соответственно увеличивают на единицу лй- бо передают на выход сумматора 19 трех- фазные сигналы счетчика 5 без изменения, формируют на выходных шй нах инвертора 20 максимальные значения трёхфазных напряжений Uab. Ubc, Uca по трапецеидально му закону, ./ - - : ч;ч;.;::::V-}: ..;-;;:: -.:: i: / При значениях входного кода К от 8 до О блоки 13, 14 формируют линейно изменя ющиеся импульсы на выходе элемента 15. Причём при наличии сигнала преобразователи 6, 7, 8 передают сигналы разряддв делителя-счетчика 1 на входы преобразователей 10,11,12 в прямом коде, а при сигнале - в обратном коде.: ч/ ;

Пусть в исходном состояний делителя- счетчика , тогда разряды 2, 3 и 4 в исход- ном нулевом состояний, а на выходе формирователя 18 существует сигнал .

За первый цикл переключения первых двух разрядов, когда третий разряд сохраняет исходное состояние в течение времени 10 периодов частоты fi на вход блоков 13, 14 подаются сигналь/ в прямом коде, а в оставшиеся 90 периодов частоты fi этого цикла - в обратном коде. За второй цикл переключения, когда разряд 4 находится а первом состоянии 1, в прямом коде подаются сигналы в течение 20 периодов часто ты fi и в обратном коде - в течение 80 периодов этой частоты цикл и т.д.

При подаче сигналов на входы блоков 13, 14 в прямом коде и изменений состоящий третьего разряда от 0 до 8 на входе v сумматора 19 формируются линейно нарастающие импульсы соответственно длительностью в 9, 10, 27. 36, 45,54, 63, 72 и 81

период частоты fi. каждый из которых располагается 1i переключения первых двух разрядов 2 и 3. При подаче Сйгйалов на входы блоков 13, 14 в обратном коде и изменении состояния разряда 4 от О до 8 на входе w сумматора 19 формируются линейно спадающие импул ьсы с оЬтвётст- вёнйо длительностью в 81, 72, 63, 54, 45,36, 27; 18, 9 периодов частоты fi, каждый из которых расположен в:конце цикла переключений разрядов 2 и-3. 7

(Иёаду мпуЛ са К.о дШг б цШлё йёре- ключеШя разрядов 2 и 3 существует пауза в 10 периодов частоты fj, когда на входах сумматора 19 отсутствуют сигналы н и v.

При дальнейшем уменьшений значения входного кода К происходит пропорцио- На л оё уме н biii ёние л иней но изменя ющих- УСЯ импульсов и увёлйчёкие паузы между импульсами одного цикла пёрёключёйия : разрядов 2 и 3. При этом линейно возрастающие сигналы у и лй нейнб спадающие w собтветСтёёнйЪ увёййч йёаЪт tia единицу либо передают на входы сумматора .19 трехфазные сигналы счётчики 5 без изменения, а при их-отсутствий сигнёй ё йтйрйваёт вер- хние ключи MocfffBdru Мвертбp ai а сигнал е -нижние. Следовательно, на выходах инвертора будут сформированы трехзначные напряжения иаь, , Uca по трапецеидальному закону, когда входной код К пропор- цйбнально изменяет Длйтёль йость всех импульСОв, из которых составлены эти прйжёния;- л : ;;; -Г: г; .: : :---.--- Л -s:. -,,- Уменьшение аппаратурных затрат и по- вышенйе надёжности объясняется исполь- только двух логических блоков. ; Ф 6 р м у л а изобретения

Устройство для управления трехфазным инвертором, содержащее делитель-счётчик, состоящий из последовательно включенных трёх разрядов и трехфазного счетчика, первые два разряда являются пятифазными счетчиками, третий - пятифазным счетчиком с коэффициентом пересчета равным девяти, формирователь регулируемых импульсов, состоящий из трех преобразователей кодов, двух логических блоков и элемента ИДИ, входы преообразователей кодов являются первыми входами формирователя регулируемых ймпуйьсов;: выходы преобразователей кодов подключены к одним входам логических блоков, другие входы которых пред назначен для подключены к задатчику кода управлений, третьи входы логических блоков являются вторыми входами формирователя регулируемых ймпуЛь- сов, которые подключены к разрядам делителя-счетчика , структура первых двух

преобразователей кодов определяется уравнениями

a , ,

, ,

;- . ,. .:: ,, : /tafias ., / ...,. ,-...-. где функции а. ... to ripe Деля ют сигналы на выходах преобразователя кода, аргументы 3i-сигнал на |-м выходе разряда делителя сметчика, выход элемента ИЛИ является выходом формирователя регулируемых им- пульСов, два элемента И и логический сумматор, входы которого соединены с выходами элементов И и выходами трехфазного счетчика делителя-счетчик а, л о гич ее кий су м мато р р еал и зует л о гич еСКЙе ФУНКЦИЙ 7 1 ; о ., ;:; . Y-V;.;. -.....,. wy у у е w Г, .,: Ч h2 d2;wv di vy fw7, ; : ; ;.

(з w у d2V v eWv; ... ; ; v dida v 32d3, . . I.,,. где Bi --;сйгнал) на сбответствующйх ЁЫХОдйгх трехфазнЬгЬ счётчика; .;: ; w И у f: сигналы на выходах первого и втЬ йрэлеме тов И; . . ; ; СИГЙЙ71Ы на(выходах логического Сумматора, которые являются выходами ус; ;Тр;6ЙСТ)ва,..x - Y оIT;Жи ч а нэ щ ф ё с я тем, что; с Ц&пыб повышения надежности, оно снабжено тремя преобразователями в обратный код и .ф6(мйрЬвателем йёрегулируемых импульсов, причем входы формирователя нерегу- л и уёмгых ймгтул сОв Нодкл(рч выхйддм второго и третьего разрядов делителя счетчика, прямой и инверсный выходы СЬёдййёнйic первыми (Выходами преобразователе в обратный код и сротвётственйр с пеьвымй входами первого и второго зле- ментов И, функция, реализуемая формиро- ватёйёмI нерегулируемых импульсов j c-biBjaercji уравнением 4 - Y

v babsct v ЬзБ&са v Ь Ббсз у Ьбсг

-V blCS V bjTcsCl уЪзС5С2 vb4C5C3, у ;, ;,л ,

:где р- сигнал на прямом выходе, Bi и (л - сйгйалы йа соетветствующих- выходах второго и третьего разрядов дёйй;гёля-счётчй- ka, вторые входы преобразователей в обратный код подключены, к выходам соот;; вётствующйх разрядов делителя-счетчика, структуры первого и второго преобразова0

5

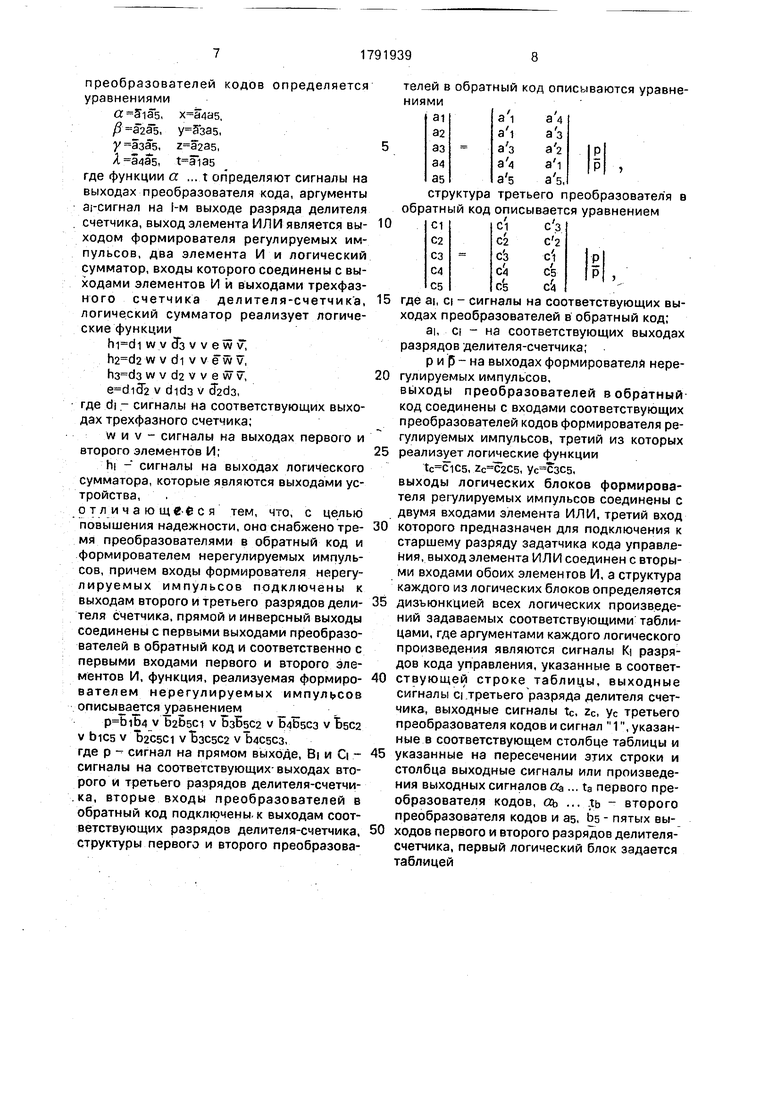

тел ей в обратный код описываются уравнениями

31

32

аз

34

asa s структура третьего преобразователя в обратный код бпйсывается уравнением

С1

a i a i а з а 4

а 4 а з а 2 a i а 5,

С2 СЗ С4 С5

С 1 6 СЗ С 4 С/5

с з

С 2 С 1

с 5

С 4

Ј Р

где ai, ci - сигналы на соответствующих выходах преобразователей в обратный код;

ai, ci - на соответствующих выходах разрядов делителя-счетчика;

р и |5 - на выходах формирователя нере0 гулйруемых импульсов,

вйходы преобразователей в обратный код соединены с входами соответствующих преобразователей кодов формирователя регулируемых импульсов, третий из которых

5 реализует логические функции

;:., , , ,

выходы логических блоков формирователя регулируемых импульсов соединены с двумя входами элемента ИЛИ, третий вход

0 которого предназначен для подключения к старшему разряду задатчика кода управления, выход элемента ИЛ И соединен с вторыми входами обоих элементов И, а структура каждого из логических блоков определяется

5 дйзьюнкцйей всех логических произведений задаваемых соответствующими таблицами, где аргументами каждого логического произведения являются сигналы К| разрядов кода управления, указанные в соответ0 ствующей строке таблицы, выходные

сигналы ci .третьего разряда делителя счетчика, выходные сигналы tt , zc, Ус третьего преобразователя кодов и сигнал 1, указанные в сортветствующем столбце таблицы и

5 указанные на пересечении этих строки и столбца выходные сигналы или произведения выходных сигналов а&... ta первого преобразователя кодов, аь ... -tb второго преобразователя кодов и as, bs - пятых вы0 ходов первого и второго разрядов делителя- счетчика, первый логический блок Задается таблицей

Второй логический 5лок задается таблицей

Та б л и ц а 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления инвертором с широтно-импульсной модуляцией | 1984 |

|

SU1711306A1 |

| Цифроаналоговый преобразователь с многофазным выходом | 1987 |

|

SU1476611A1 |

| Устройство для управления многофазным инвертором | 1978 |

|

SU955837A1 |

| Электропривод переменного тока | 1979 |

|

SU961087A1 |

| Цифровой электропривод постоянного тока | 1986 |

|

SU1343531A1 |

| Преобразователь угла поворота вала в код | 1983 |

|

SU1129636A1 |

| Многоразрядное устройство для сложения и вычитания | 1981 |

|

SU993264A1 |

| Устройство для вычисления параметров нелинейных колебательных систем | 1985 |

|

SU1302243A1 |

| Цифроаналоговый преобразователь с многофазным выходом | 1985 |

|

SU1356225A1 |

| Имитатор цифрового телевизионногоСигНАлА | 1978 |

|

SU815966A1 |

Изобретение относится к преобразователям постЬянйбго напряжения в многофазное переменное напряжение с щиротно-импульсИой модуляцией. Цель изобретения - повышение надежности. Ус- т ро йстб Ь с ост о ит из дел ите л я -счетч и ка, вход которого соединен с шиной сигнала внешней частоты, и последовательно соединенного с ним делителя многофазного кода по числу фаз инвертора. Выходные шины f- t..,ki:m:j j:дел ите л я-счетчика сое ди йена с п ё ршм° Wo- дом сумматора в многофазном коде, выходные шин;ы ;ч; kpfo o-r isaalV nf41- управляющими вх6дШ эле ментбв йнвёр тора. Выходные цифровые шины разрядов делителя-счетчика сбёдиненыг сЪ вводами блока преобразователей из прямого кода в обратный, выходы которых соединена со входом регулируемого формирователя 9, Управляющие входы преобразователей соединены с выходами нерегулируемого .формирователя импульсов с лийё йно изменяющейся длительностью. Вход нерегулируемого формирователя соединен с выходными цифровыми шинами двух старших разрядов делителя-счетчика, Прямой и инверсный выходы нерегируёмого формиро- вателя соединены с первыми входам1/гд йух элементов И, 1 ил., 2 табл. on С

Та блица 2

Редактор НЛигинаv

Составитель В.Миронов Техред М.Моргентал

Заказ 158Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., 4/5

Корректор: С.Патрушева

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для управления инвертором с широтно-импульсной модуляцией | 1984 |

|

SU1711306A1 |

| ; | |||

Авторы

Даты

1993-01-30—Публикация

1986-07-16—Подача