7-/V- F/r- Э

А1

-

Tf

С О О

СО

| название | год | авторы | номер документа |

|---|---|---|---|

| РАДИОВЫСОТОМЕР | 2001 |

|

RU2212684C1 |

| РАДИОДАЛЬНОМЕР | 2000 |

|

RU2197000C2 |

| РАДИОДАЛЬНОМЕР | 2000 |

|

RU2197001C2 |

| СПОСОБ КОДИРОВАНИЯ РЕЧЕВЫХ СИГНАЛОВ | 1993 |

|

RU2120700C1 |

| УСТРОЙСТВО ПЕРЕДАЧИ И ПРИЕМА ДЛЯ ШИРОКОПОЛОСНОЙ РАДИОСВЯЗИ | 1980 |

|

SU1840131A1 |

| СПОСОБ ОБРАБОТКИ ШИРОКОПОЛОСНЫХ СИГНАЛОВ И УСТРОЙСТВО ФАЗИРОВАНИЯ АНТЕНН ПРИЁМА ШИРОКОПОЛОСНЫХ СИГНАЛОВ, ПРЕИМУЩЕСТВЕННО ДЛЯ АНТЕНН НЕЭКВИДИСТАНТНОЙ РЕШЁТКИ | 2015 |

|

RU2594385C1 |

| НЕЛИНЕЙНЫЙ РАДАР ДЛЯ ДИСТАНЦИОННОГО МОНИТОРИНГА ПРОДУКТОПРОВОДОВ | 2007 |

|

RU2343499C1 |

| СПОСОБ СТАБИЛИЗАЦИИ ВРЕМЕННОГО ПОЛОЖЕНИЯ СВЕРХШИРОКОПОЛОСНОГО СИГНАЛА И ЛОКАТОР ДЛЯ МОНИТОРИНГА ЖИВЫХ ОБЪЕКТОВ, РЕАЛИЗУЮЩИЙ ЭТОТ СПОСОБ | 2004 |

|

RU2258942C1 |

| Система автоматической регулировки усиления с задержкой сигнала на время оценки мощности аддитивной смеси сигнала и помехи | 2021 |

|

RU2776776C1 |

| АНАЛИЗАТОР СПЕКТРА | 1992 |

|

RU2054682C1 |

Изобретение относится к радиотехнике и может быть использовано в радиолокации, телеметрии, радиоуправлении, радиосвязи. Цель изобретения - обеспечение регулируемой задержки широкополосных сигналов. Для этого в состав устройства введены полосовые фильтры 1-1... 1-т, смесители 2-1... 2-(гп-1) для понижения частоты, аналого-i цифровые преобразователи 3-1... 3-т, т-6 адресных счетчиков 4-1... 4-т записи, оперативные запоминающие устройства 5-1... 5- т, управляемые счетчики 6-6... 6-гл считывания, цифроаналоговые преобразователи 7-1,,, 7-т, смесители 8-1... 8-т для повышения частоты, сумматор 9, блок 10 гетеродинов. Кроме того, в состав устройства входят шесть адресных счетчиков 4-1... 4-6 записи, и генератор 11 тактовых импульсов. Введенные элементы обеспечивают возможность программно-управляемой задержки сигналов,имеющих широкий спектр, верхняя граничная частота которого может значительно превышать допустимую частоту цифровой обработки. 5 ил., 1 табл, И

:7-г,

ъ:.

S-(m-i

ту

Изобретение относится к радиотехнике м может быть использовано в радиолокации, телеметрии, радиоуправлении, радиосвязи, измерительной и вычислительной технике, а также в других областях техники, где необходима регулируемая задержка Сигнала,

Цель изобретения - обеспечение регулируемой задержки широкополосных сигналов.

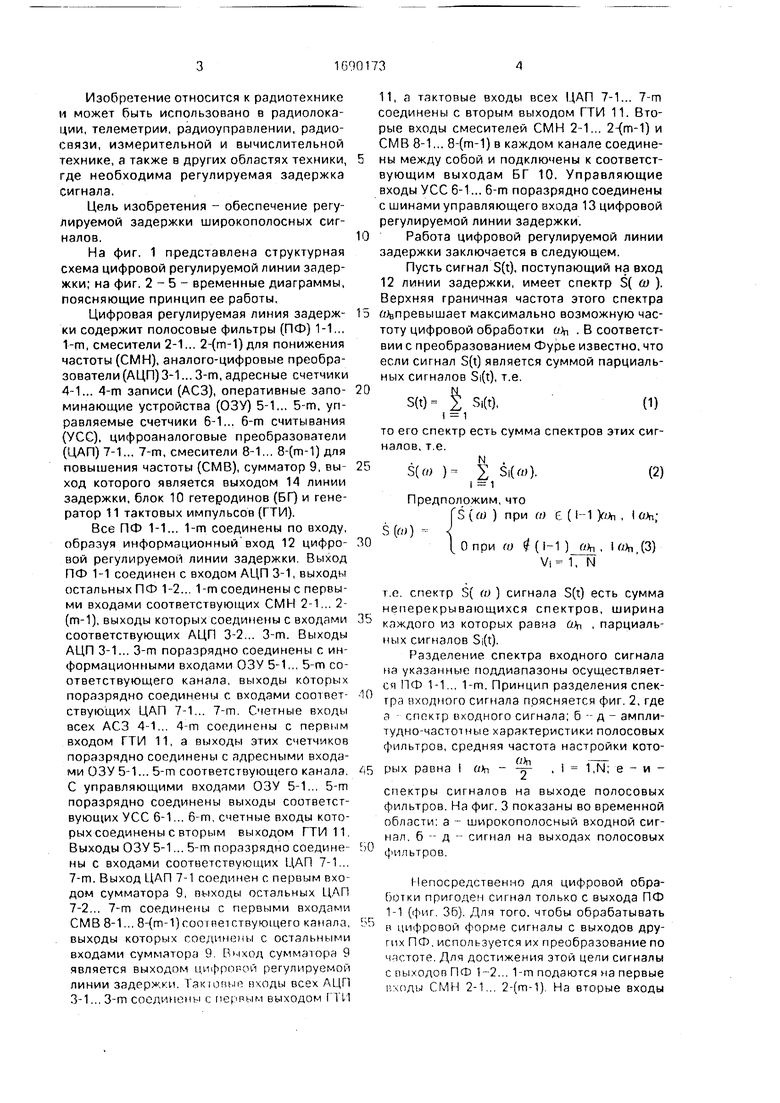

На фиг. 1 представлена структурная схема цифровой регулируемой линии задержки; на фиг. 2 - 5 - временные диаграммы, поясняющие принцип ее работы.

Цифровая регулируемая линия задержки содержит полосовые фильтры (ПФ) 1-1... 1-т, смесители 2-1... 2-(т-1)для понижения частоты (СМИ), аналого-цифровые преобразователи (АЦП) 3-1... 3-т, адресные счетчики 4-1... 4-т записи (АСЗ), оперативные запоминающие устройства (ОЗУ) 5-1... 5-гл, управляемые счетчики 6-1... 6-т считывания (УСС), цифроаналоговые преобразователи (ЦАП) 7-1,,. 7-т, смесители 8-1... 8-(т-1) для повышения частоты (СМВ), сумматор 9, выход которого является выходом 14 линии задержки, блок 10 гетеродинов (БГ) и генератор 11 тактовых импульсов (ГТИ).

Все ПФ 1-1... 1-т соединены по входу, образуя информационный вход 12 цифровой регулируемой линии задержки. Выход ПФ 1-1 соединен с входом АЦП 3-1, выходы остальных ПФ 1-2... 1-т соединены с первыми входами соответствующих СМИ 2-1... 2- (т-1), выходы которых соединены с входами соответствующих АЦП 3-2... 3-т. Выходы АЦП 3-1... 3-т поразрядно соединены с информационными входами ОЗУ 5-1... 5-т соответствующего канала, выходы которых поразрядно соединены с входами соответствующих ЦАП 7-1... 7-т. Счегные входы всех АСЗ 4-1... 4-т соединены с первым входом ГТИ 11, а выходы этих счетчиков поразрядно соединены с адресными входами ОЗУ 5-1... 5-т соответствующего канала. С управляющими входами ОЗУ 5-1... 5-т поразрядно соединены выходы соответствующих УСС 6-1... 6-т, счетные входы которых соединены с вторым выходом ГТИ 11. Выходы ОЗУ 5-1... 5-т поразрядно соединены с входами соответствующих ЦАП 7-1... 7-т. Выход ЦАП 7-1 соединен с первым входом сумматора 9, выходы остальных ЦАП 7-2... 7-т соединены с первыми входами СМВ 8-1... 8-(т-1)соответствующего канала, выходы которых соединены с остальными входами сумматора 9 Выход сумматора 9 является выходом цифровой регулируемой линии задержки. Такюпып входы всех АЦП 3-1... 3-т соединены с первым выходом I IL1

11, а тактовые входы всех ЦАП 7-1... 7-т соединены с вторым выходом ГТИ 11. Вторые входы смесителей СМИ 2-1... 2-(т-1) и СМВ 8-1... 8-(т-1) в каждом канале соединены между собой и подключены к соответствующим выходам БГ 10. Управляющие входы УСС 6-1... 6-т поразрядно соединены с шинами управляющего входа 13 цифровой регулируемой линии задержки.

0 Работа цифровой регулируемой линии задержки заключается в следующем.

Пусть сигнал S(t), поступающий на вход 12 линии задержки, имеет спектр S( (о ), Верхняя граничная частота этого спектра

5 превышает максимально возможную частоту цифровой обработки а . В соответствии с преобразованием Фурье известно, что если сигнал S(t) является суммой парциальных сигналов Si(t), т.е.

0N

s(t) Ј Si(t).(1)

i 1

то его спектр есть сумма спектров этих сигналов, т.е.

5 S(a )- X Si(w).(2)

i 1

Предположим, что

{S (ш ) при а) Ј (1-1 , I cv О при (о $ (1-1 ) ftJn . lwn,(3) Vi 1, N

г.е. спектр S( t) } сигнала S(t) есть сумма неперекрывающихся спектров, ширина каждого из которых равна сон . парциальных сигналов Si(t).

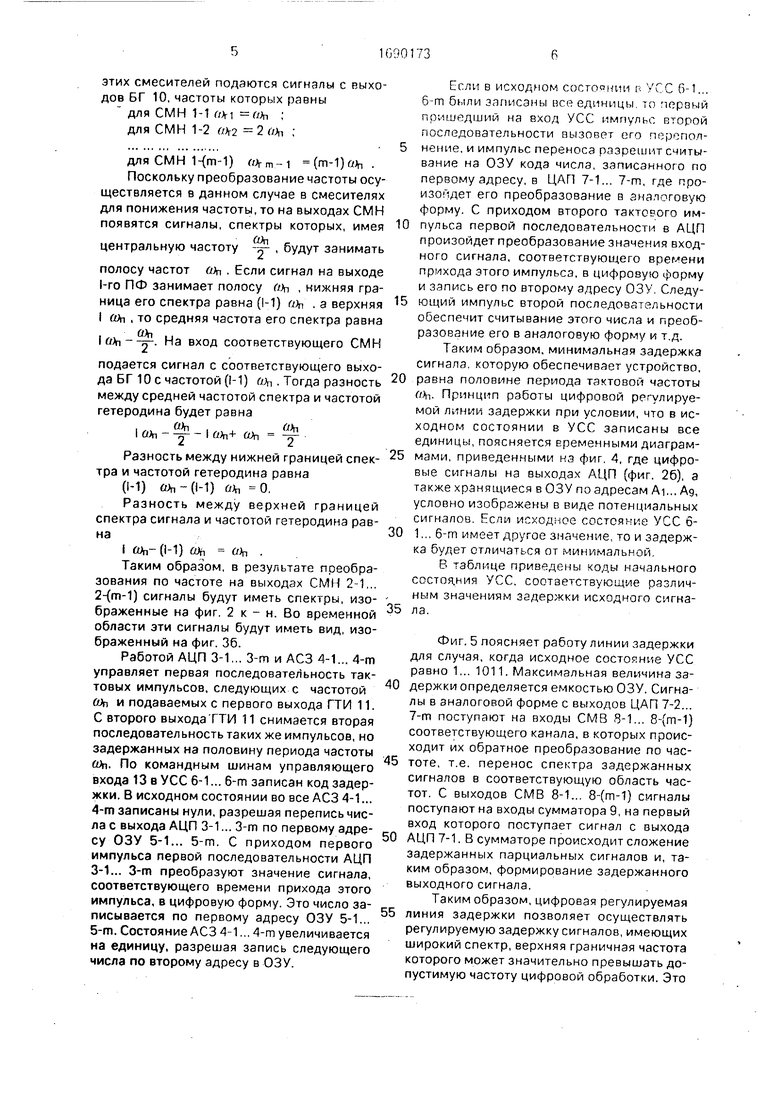

Разделение спектра входного сигнала на указанные поддиапазоны осуществляется ПФ 1-1... 1-т. Принцип разделения спектра входного сигнала поясняется фиг. 2. где а спектр входного сигнала; б - д - амплитудно-частотные характеристики полосовых фильтров, средняя частота настройки котоi Ш; е

рых равна

ом - Ј

и О

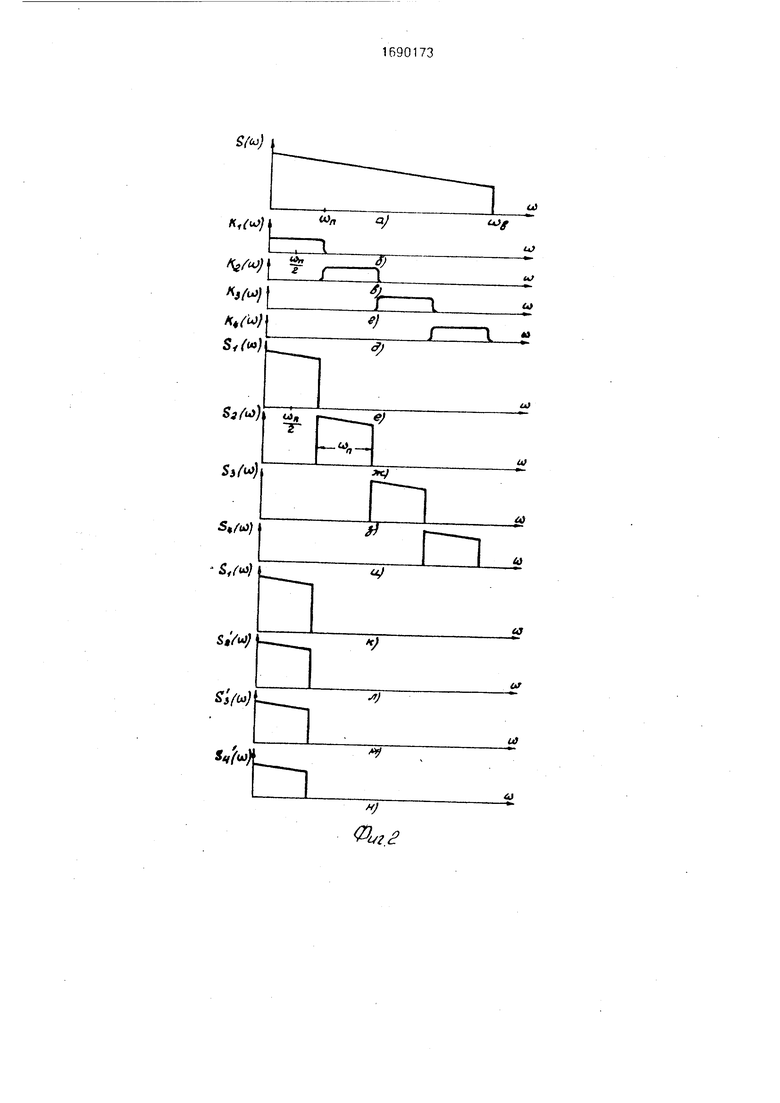

спектры сигналов на выходе полосовых фильтров. На фиг. 3 показаны во временной области: а - широкополосный входной сигнал, б - д -- сигнал на выходах полосовых фильтров.

Непосредственно для цифровой обработки пригоден сигнал только с выхода ПФ 1-1 (фиг. 36). Для того, чтобы обрабатывать в цифровой форме сигналы с выходов других ПФ. используется их преобразование по частоте. Для достижения этой цели сигналы с выходов ПФ 1-2... 1-т подаются на первые РАОДЫ СМИ 2-1 .. 2-(т-1) На вторые входы

этих смесителей подаются сигналы с выходов БГ 10, частоты которых равны для СМИ 1-1 Од1 : для СМИ 1-2 «г2 2 (On :

для СМИ 1-{m-1) oVm-1 (m-1)GJh Поскольку преобразование частоты осуществляется в данном случае в смесителях для понижения частоты, то на выходах СМИ появятся сигналы, спектры которых, имея

(On

центральную частоту

, будут занимать

полосу частот (On . Если сигнал на выходе 1-го ПФ занимает полосу (On , нижняя граница его спектра равна (1-1) Wn . а верхняя I (On , то средняя частота его спектра равна

I . На вход соответствующего СМИ

подается сигнал с соответствующего выхода БГ 10 с частотой (i-1) (On . Тогда разность между средней частотой спектра и частотой гетеродина будет равна

luAi

,

- I (Оп+ (On Y

Разность между нижней границей спектра и частотой гетеродина равна

(1-1) Юц-(И) 0)п 0,

Разность между верхней границей спектра сигнала и частотой гетеродина равна

i Шп- (1-1) Ып «п .

Таким образом, в результате преобразования по частоте на выходах СМИ 2 1... 2-{т-1) сигналы будут иметь спектры, изображенные на фиг. 2 к - н. Во временной области эти сигналы будут иметь вид, изображенный на фиг. 36.

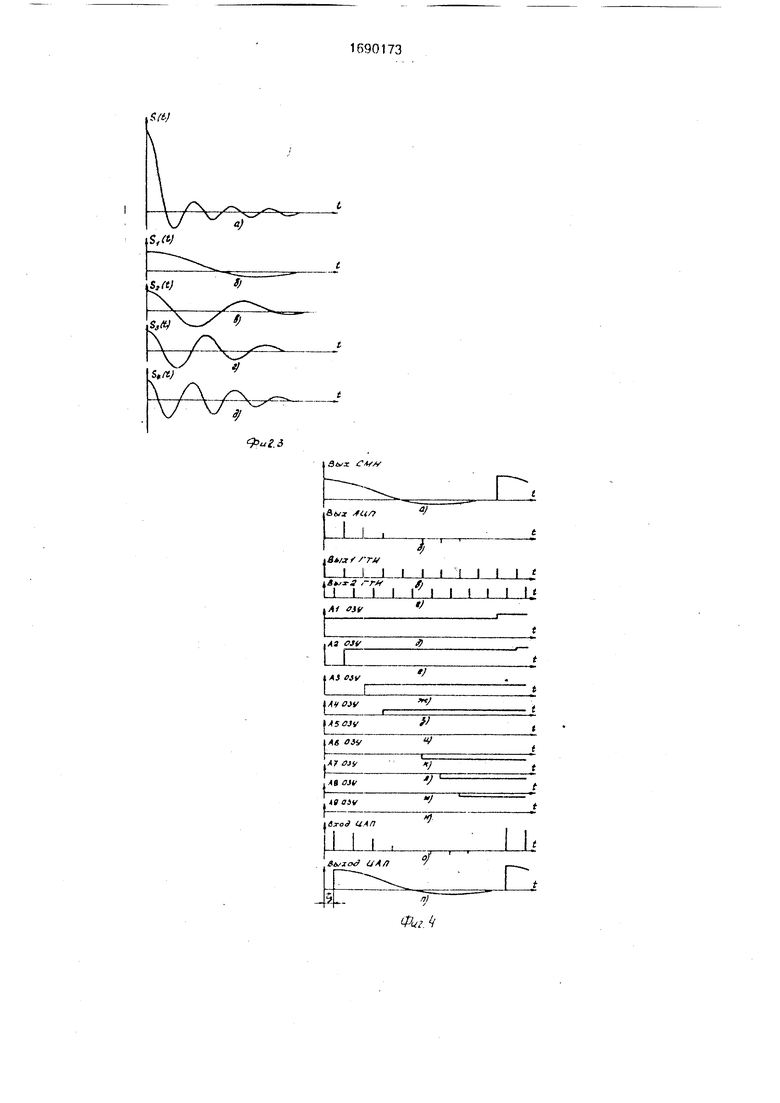

Работой АЦП 3-1... 3-т и АСЗ 4-1... 4-т управляет первая последовательность тактовых импульсов, следующих с частотой Шп и подаваемых с первого выхода ГТИ 11. С второго выхода ТТИ 11 снимается вторая последовательность таких же импульсов, но задержанных на половину периода частоты Шп. По командным шинам управляющего входа 13 в УСС 6-1... 6-т записан код задержки. В исходном состоянии во все АСЗ 4-1... 4-т записаны нули, разрешая перепись числа с выхода АЦП 3-1... 3-т по первому адресу ОЗУ 5-1... 5-т. С приходом первого импульса первой последовательности АЦП 3-1... 3-т преобразуют значение сигнала, соответствующего времени прихода этого импульса, в цифровую форму. Это число записывается по первому адресу ОЗУ 5-1... 5-т. Состояние АСЗ 4-1... 4-т увеличивается на единицу, разрешая запись следующего числа по второму адресу в ОЗУ.

Если в исходном состоянии г VCC 6-1... 6-т были записаны все единицы то первый пришедший на вход УСС импульс пторой последовательности вызовет его перопоп5 нение, и импульс переноса разрешит считывание на ОЗУ кода числа, записанного по первому адресу, в ЦАП 7-1... 7-гп, где про- изомдет его преобразование в аналоговую форму. С приходом второго тактового им0 пульса первой последовательности в АЦП произойдет преобразование значения входного сигнала, соответствующего времени прихода этого импульса, в цифровую форму и запись его по второму адресу ОЗУ Следу5 ющий импульс второй последовательности обеспечит считывание этого числа и преобразование его в аналоговую форму и т.д.

Таким образом, минимальная задержка сигнала, которую обеспечивает устройство,

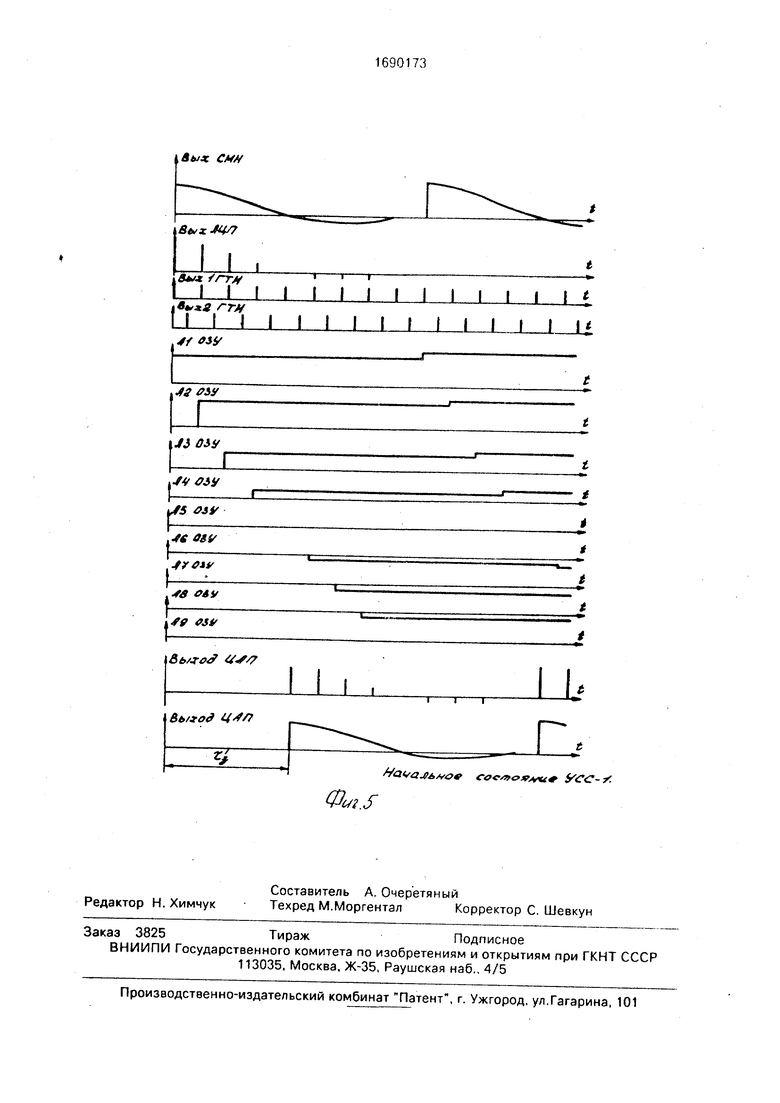

0 равна половине периода тактовой частоты (On. Принцип работы цифровой регулируемой линии задержки при условии, что в исходном состоянии в УСС записаны все единицы, поясняется временными диаграм5 мами, приведенными нз фиг. 4, где цифровые сигналы на выходах АЦП (фиг. 26), а также хранящиеся в ОЗУ по адресам Ai... Ag, условно изображены в виде потенциальных сигналов. Если исходное состояние УСС 60 1... 6-т имеет другое значение, то и задержка будет отличаться от минимальной,

В таблице приведены коды начального состояния УСС, соответствующие различным значениям задержки исходного сигна5 ла.

Фиг. 5 поясняет работу линии задержки для случая, когда исходное состояние УСС равно 1... 1011. Максимальная величина за0 держки определяется емкостью ОЗУ. Сигналы в аналоговой форме с выходов ЦАП 7-2... 7-т поступают на входы СМВ 8-1... 8-(гп-1) соответствующего канала, в которых происходит их обратное преобразование по час5 тоте, т.е. перенос спектра задержанных сигналов в соответствующую область частот. С выходов СМВ 8-1... 8-(гп-1) сигналы поступают на входы сумматора 9, на первый вход которого поступает сигнал с выхода

0 АЦП 7-1. В сумматоре происходит сложение задержанных парциальных сигналов и, таким образом, формирование задержанного выходного сигнала.

Таким образом, цифровая регулируемая

5 линия задержки позволяет осуществлять регулируемую задержку сигналов, имеющих широкий спектр, верхняя граничная частота которого может значительно превышать допустимую частоту цифровой обработки. Это

позволяет использовать ее для задержки случайных и детерминированных широкополосных сигналов.

Формула изобретения Цифровая регулируемая линия задержки, содержащая шесть адресных счетчиков записи и генератор тактовых импульсов, о т- личающаяся тем, что, с целью обеспечения регулируемой задержки широкополосных сигналов, в нее введены блок гетеродинов, сумматор, первый канал, состоящий из последовательно соединенных полосового фильтра, аналого-цифрового преобразователя, оперативного запоминающего устройства и цифроаналогового преобразователя, выход которого является выходом первого канала, гл-1 идентичных каналов, каждый из которых содержит соединенные последовательно полосовой фильтр, смеситель понижения частоты, аналого-цифровой преобразователь, оперативное запоминающее устройство, цифроаналоговый преобразователь и смеситель повышения частоты, выход которого является выходом соответствующего канала, а также т-6 адресных счетчиков записи и М управляемых счетчиков считывания, причем выход аналоге цифрового преобразователя каждого канала и информационный вход соответствующего оперативного запоминающего устройства, а также информационный выход последнего и вход соответствующего цифроаналогового преобразователя соединены между собой поразрядно, к адресному входу каждого

оперативного запоминающего устройства поразрядно подключен выход соответствующего адресного счетчика записи, счетный вход которого соединен с первым выходом генератора тактовых импульсов, а к управляющему входу каждого оперативного запо- минающего устройства поразрядно подключен выход соответствующего управляемого счетчика считывания, счетный вход которого соединен с вторым выходом генератора тактовых импульсов, а управляющий вход соединен поразрядно с командными шинами управляющего входа линии задержки, тактовые входы аналого-цифровых преобразователей подключены к первому

выходу генератора тактовых импульсов, а тактовые входы цифроаналоговых преобразователей - к второму выходу генератора тактовых импульсов, вторые входы обоих смесителей каждого канала соединены между собой и подключены к соответствующему выходу блока гетеродинов, все полосовые фильтры по входу соединены между собой, образуя информационный вход линии задержки, выход каждого канала соединен с

0 соответствующим входом сумматора, выход которого является выходом цифровой регулируемой линии задержки.

n

&

to

P

П

&

т

«

n

t

(н

to (у Ј

fr

&

hie

V

(9

(

Kf-5 H S

AV S -

Hfs (vfs

fe

(

I

7у

Ј:

-Г i

4

K S Hfv

(

{)

CZ.10691

.Sr0

Bb foJ 4S/7

Bbtto

Ч

Морально cofw ЛТ-Х

| Цифровая регулируемая линия задержки | 1972 |

|

SU457158A1 |

| кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Цифровая регулируемая линия задержки | 1980 |

|

SU917303A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1991-11-07—Публикация

1988-09-26—Подача