Изобретение относится к радиотехнике и может использоваться для приёма широкополосных сигналов в системе сбора телеметрической информации от бортовой аппаратуры космических аппаратов.

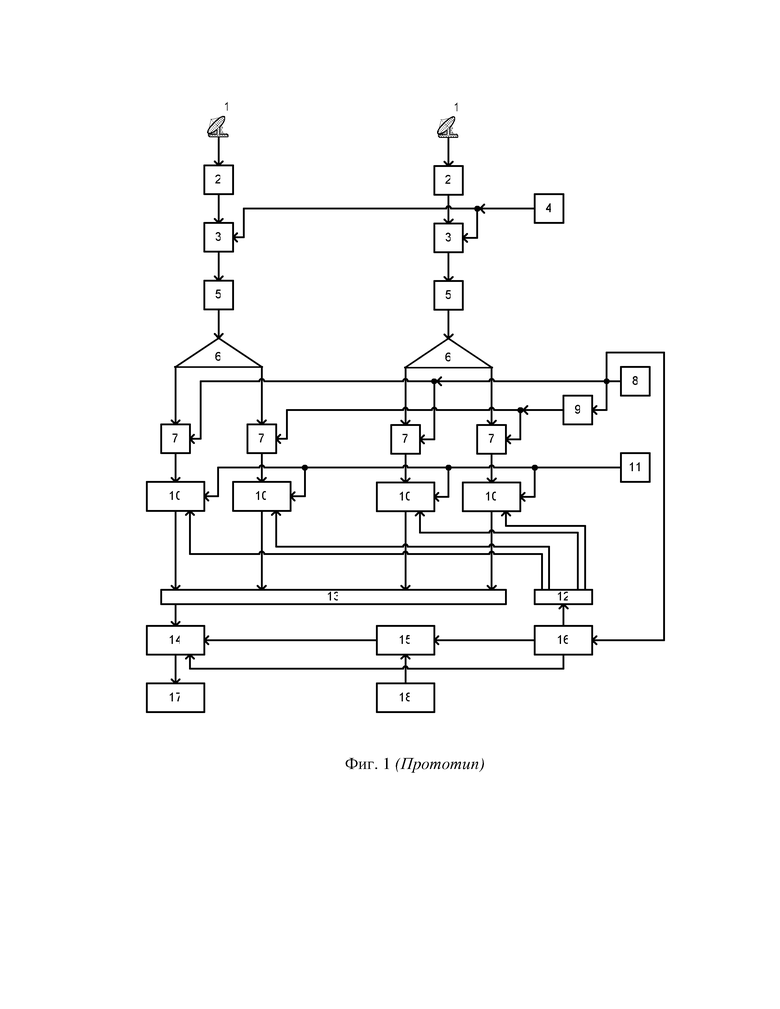

Известен способ формирования диаграммы направленности антенной решётки введением фазового сдвига в числовые последовательности отсчётов сигналов с антенн решётки [см. Проблемы антенной техники/ под ред. Л.Д. Бахраха, Д.И. Воскресенского. - М.: Радио и связь, 1989. - 368 с.: ил. - ISBN5-256-00335-6]. Для сравнительно небольшого количества антенн этот способ реализуется последовательной схемой, представленной на фиг. 1, где: 1 - приёмная антенна; 2 - входной малошумящий усилитель (МШУ) и фидер до смесителя; 3 - смеситель; 4 - первый гетеродин; 5 - усилитель промежуточной частоты с полосовым фильтром (УПЧ-ПФ); 6 - делитель; 7 - синхронные фазовые детекторы (СФД); 8 - второй гетеродин; 9 - постоянный фазовращатель на 90°; 10 - аналого-цифровые преобразователи (АЦП); 11 - генератор тактовых импульсов (ГТИ); 12 - дешифратор адресного сигнала; 13 - шина данных; 14 - процессор формирования диаграммы направленности (ПФДН); 15 - запоминающее устройство (ЗУ); 16 - устройство управления (УУ); 17 - приёмник; 18 - управляющая ЭВМ.

Выход каждой приёмной антенны 1 соединён со входом соответствующего МШУ 2, выход каждого МШУ 2 соединён с сигнальным входом соответствующего смесителя 3, гетеродинный вход которого соединён с выходом первого гетеродина 4, выход каждого смесителя 3 соединён со входом соответствующего УПЧ-ПФ 5, выход которого соединён со входом соответствующего делителя 6, первый выход каждого делителя 6 соединён с сигнальным входом первого, а второй выход делителя соединён с сигнальным входом второго из соответствующей пары синхронных фазовых детекторов 7, причём гетеродинный вход каждого первого в соответствующей паре СФД 7 соединён с выходом второго гетеродина 8, а гетеродинный вход каждого второго в соответствующей паре СФД 7 соединён с выходом постоянного фазовращателя на 90° 9, вход которого соединён с выходом второго гетеродина 8, выход каждого СФД 7 соединён с сигнальным входом соотвествующего АЦП 10, вход импульсов запуска которого соединён с выходом ГТИ 11, а адресный вход соединён с соответствующим выходом дешифратора адресного сигнала 12, вход которого соединён с первой адресной шиной УУ 16, вход синхронизации УУ 16 соединён с выходом ГТИ 11, выход данных каждого АЦП 10 соединён с соответствующим входом шины данных 13, выход которой соединён с первым входом данных ПФДН 14, причём второй вход данных ПФДН 14 соединён с выходом данных ЗУ 15, а вход управления ПФДН 14 соединён с выходом управления УУ 16, адресная шина ЗУ 15 соединена со второй адресной шиной УУ 16, выход данных ПФДН 14 соединён со входом данных приёмника 17, шина данных и адреса ЗУ 15 соединена с шиной данных и адреса управляющей ЭВМ 18.

На антенны 1 решётки падает фронт волны радиосигнала со сдвигом для антенны № i на время разности хода лучей Δtio относительно опорной антенны № o. Принятый антенной сигнал усиливают в соответствующем малошумящем усилителе 2, понижают по частоте с использованием первого гетеродина 4 и смесителя 3, усиливают и ограничивают по полосе частот с использованием усилителя промежуточной частоты и полосового фильтра 5, разветвляют на два сигнала делителем 6, формируют квадратурные сигналы с помощью соответствующего синхронного фазового детектора 7, второго гетеродина 8 и постоянного фазовращателя на 90° 9, после чего на аналого-цифровом преобразователе 10 под воздействием импульсов с частотой дискретизации fд от генератора тактовых импульсов 11 формируют цифровые отсчёты значений квадратурных сигналов Siс = Ai·cos(2пfst) и Sis = Ai·sin(2пfst) со средней частотой спектра fs, причём под воздействием адресных сигналов с дешифратора 12, поступающих от устройства управления 16 по приходу импульса синхронизации с ГТИ, отсчёты сигналов разных антенн решётки последовательно вводят через шину данных 13 в процессор формирования диаграммы направленности 14, на котором формируют индивидуальные фазовые сдвиги сигнала каждой антенны на основе данных об относительных задержках сигнала одного фазового фронта на разных антеннах Δtio, которые хранят в запоминающем устройстве 15 и рассчитывают заранее по целеуказаниям в управляющей ЭВМ 18. Процессор формирования диаграммы направленности 14 на основе относительных задержек Δtio фронта волны вычисляет разности фаз сигналов на средней частоте fs спектра сигнала после АЦП по формуле Δφio = 2пfsΔtio, определяет результирующие сфазированные сигналы по формуле SiΔ = Ai·cos(2пfst + Δφio) = Ai·[cos(2пfst)·cos(Δφio) - sin(2пfst)·sin(Δφio)] = Siс·cos(Δφio) - Sis·sin(Δφio) и вычисляет суммарный сигнал со всех антенн решётки, после чего выдаёт его в приёмник 17.

Основные недостатки известного решения для формирования диаграммы направленности антенной решётки введением фазового сдвига в числовые последовательности отсчётов сигналов с антенн решётки состоят в его относительной трудоёмкости и непригодности для передачи широкополосных сигналов. Действительно, при фазировании сигналов от N антенн требуется 2N сравнительно трудоёмких операций умножения и N-1 операция сложения. Кроме того, при достаточно широком спектре набеги фаз в достаточно далеко отстоящих по частоте симметричных гармониках разных антенн приводят к недопустимому искажению передаваемого сигнала. Например, гармоники по краям спектра при передаче телеметрической информации (ТМИ) со скоростью 3 Мбит/с, отстоящие примерно на Δf = 6 МГц, при разности хода лучей между антеннами в ΔL = 30 метров дадут набег фаз Δφ =2п·Δf·Δt = 2п·Δf·(ΔL/c) = 2п·6·106·30/(3·108)= 1,2п. Гармоники из средней части спектра сигнала ТМИ, отстоящие примерно на Δf = 3 МГц, дадут набег фаз 0,6п. Поскольку при детектировании симметричные частоты спектра радиосигнала складываются, то указанные набеги фаз приведут к сильным искажениям передаваемых широкополосных сигналов.

В свою очередь, перечисленные выше недостатки устранены в предлагаемом способе обработки широкополосных сигналов, а также в предлагаемом устройстве фазирования антенн приёма широкополосных сигналов, используемых по преимуществу в неэквидистантных антенных решётках средств приёма широкополосных сигналов. Использование предложенных способа и устройства обеспечит приём и обработку широкополосных сигналов без искажений при одновременном обеспечении быстродействия устройства фазирования антенн антенного поля при приёме от антенного поля широкополосных сигналов, несущих, например, телеметрическую информацию о состоянии бортовых систем космических аппаратов, например низкоорбитальных.

Предложен способ обработки широкополосных сигналов, предусматривающий прием сигнала антеннами, являющимися частью антенной решетки, и формирование дискретных (цифровых) отсчетов принятого сигнала с последующим суммированием дискретных (цифровых) отсчетов от нескольких антенн при контроле времени хода сигнала от опорной и ведомых антенн антенной решетки до своего устройства аналого-цифрового преобразования. В отличие от аналога сигналы, принятые указанными антеннами, сдвигают (задерживают) на доли периода дискретизации, равные остатку от деления разности времен хода сигналов от фазовых центров ведомых и опорной антенн до соответствующих входов в свои устройства аналого-цифрового преобразования. Сформированные дискретные (цифровые) отсчеты принятых сигналов от каждой антенны записывают каждый в свой соответствующий индексированный массив памяти в ячейку с соответствующим индексом, относящимся к текущему фронту волны сигнала. С задержкой, достаточной для прихода сигнала от антенны с наибольшей положительной разностью времен хода сигналов от фазовых центров ведомой и опорной антенн до соответствующих входов в свои устройства аналого-цифрового преобразования, выбирают из соответствующих массивов и суммируют дискретные (цифровые) отсчеты по одному от каждой антенны с индексами, относящимися к одному фронту волны сигнала.

Предложено устройство фазирования антенн приема широкополосных сигналов, содержащее совокупность трактов приема сигналов от антенн, являющихся частью антенной решетки. Каждый из трактов приема сигналов связан с шиной данных и включает аналого-цифровой преобразователь, связанный с генератором тактовых импульсов и через дешифратор адресного сигнала с устройством управления. Устройство управления, дешифратор адресного сигнала и генератор тактовых импульсов являются общими для каждого из трактов приема сигналов. Также, каждый из трактов приема сигналов включает приемную антенну, входной малошумящий усилитель с фидерами до смесителя, смеситель, общий для каждого из трактов приема сигналов гетеродин, усилитель промежуточной частоты с полосовым фильтром. Выход приемной антенны соединен со входом соответствующего малошумящего усилителя с фидером до смесителя, каждый малошумящий усилитель через фидер соединен с сигнальным входом смесителя, гетеродинный вход которого соединен с выходом гетеродина, выход каждого смесителя соединен со входом соответствующего усилителя промежуточной частоты с полосовым фильтром, а выход усилителя промежуточной частоты с полосовым фильтром соединен с сигнальным входом аналого-цифрового преобразователя. Также, общими для каждого из трактов приема сигналов являются процессор (блок) формирования диаграммы направленности, запоминающее устройство, приемник, управляющая ЭВМ. Адресный вход аналого-цифрового преобразователя в каждом тракте приема сигналов соединен с соответствующим выходом дешифратора адресного сигнала, вход которого соединен с первой адресной шиной устройства управления. Выход данных аналого-цифрового преобразователя в каждом тракте приема сигналов соединен с соответствующим входом шины данных.

Вход данных процессора формирования диаграммы направленности соединен с первым выходом данных запоминающего устройства, вход управления процессора формирования диаграммы направленности соединен с выходом управления устройства управления. Адресная шина запоминающего устройства соединена со второй адресной шиной устройства управления. Шина данных и адресная шина запоминающего устройства соединена с шиной данных и адресной шиной управляющей ЭВМ. Выход данных процессора формирования диаграммы направленности соединен со входом приемника.

В отличие от аналога каждый из трактов приема сигналов включает блок задержки. У блока задержки вход данных соединен с соответствующим выходом на блок задержки шины данных, адресный вход соединен с соответствующим выходом дешифратора адресного сигнала, вход импульсов фазирования соединен с выходом генератора тактовых импульсов, вход импульсов дискретизации соединен с выходом счетчика-делителя, выход задержанных импульсов дискретизации соединен со входом импульсов запуска соответствующего аналого-цифрового преобразователя. Вход счетчика-делителя соединен с выходом генератора тактовых импульсов, с выходом счетчика-делителя соединен вход синхронизации устройства управления. Второй выход данных запоминающего устройства соединен со входом данных от запоминающего устройства шины данных, а выход данных на запоминающее устройство шины данных соединен со входом данных запоминающего устройства.

Блок задержки содержит буферный регистр доли периода дискретизации, регистр доли периода дискретизации, схему сравнения, счетчик, схему И, триггер. Вход данных буферного регистра доли периода дискретизации соединен со входом данных блока задержки, вход записи буферного регистра доли периода дискретизации соединен с адресным входом блока задержки, выход буферного регистра доли периода дискретизации соединен со входом данных регистра доли периода дискретизации, выход регистра доли периода дискретизации соединен с первым входом схемы сравнения. Второй вход схемы сравнения соединен с выходом счетчика, выход схемы сравнения соединен с выходом задержанных импульсов дискретизации блока задержки, со входом установки в ноль триггера и со входом обнуления счетчика. Вход импульсов дискретизации блока задержки соединен со входом установки в единицу триггера и со входом записи регистра доли периода дискретизации. Единичный выход триггера соединен с первым входом схемы И, второй вход схемы И соединен со входом импульсов фазирования блока задержки, выход схемы И соединен со счетным входом счетчика.

Схема предложенного устройства фазирования антенн приема широкополосных сигналов приведена на фиг. 2, где: 1 - приемная антенна; 2 - входной малошумящий усилитель (МШУ) и фидер до смесителя; 3 - смеситель; 4 - первый гетеродин; 5 - усилитель промежуточной частоты с полосовым фильтром (УПЧ-ПФ); 10 - аналого-цифровые преобразователи (АЦП); 11 - генератор тактовых импульсов (ГТИ); 12 - дешифратор адресного сигнала; 13 - шина данных; 14 - процессор формирования диаграммы направленности (ПФДН); 15 запоминающее устройство (ЗУ); 16 - устройство управления (УУ); 17 - приемник; 18 - управляющая ЭВМ; 19 - счетчик-делитель; 20 - блок задержки.

В этом предложенном устройстве фазирования устранены (см. фиг. 1) делители - 6, синхронные фазовые детекторы - 7, второй гетеродин - 8, постоянный фазовращатель на 90° - 9, вдвое сокращено количество АЦП (по одному на каждую антенну 1) и введены (см. фиг. 2) счетчик- делитель 19 и блоки задержки 20 (по одному на каждую антенну 1). Выход каждой антенны 1 соединён со входом соответствующего МШУ 2, выход каждого МШУ 2 соединён через фидер с сигнальным входом соответствующего смесителя 3, гетеродинный вход которого соединён с выходом первого гетеродина 4, выход каждого смесителя 3 соединён со входом соответствующего УПЧ-ПФ 5, выход которого соединён с сигнальным входом соответствующего АЦП 10, адресный вход которого соединён с соответствующим выходом дешифратора адресного сигнала 12, вход которого соединён с первой адресной шиной УУ 16. Вход счётчика-делителя 19 соединён с выходом ГТИ 11. У каждого блока задержки 20 вход данных 1 соединён с соответствующим выходом на блок задержки шины данных 13, адресный вход 2 соединён с соответствующим выходом дешифратора 12, вход которого соединён с первой адресной шиной УУ 16. Вход импульсов фазирования 3 соединён с выходом ГТИ 11, вход импульсов дискретизации 4 соединён с выходом счётчика-делителя 19, выход задержанных импульсов дискретизации 5 соединён со входом импульсов запуска соответствующего АЦП 10. Второй выход данных ЗУ 15 соединён со входом данных от ЗУ шины данных 13, выход данных каждого АЦП 10 соединён с соответствующим входом шины данных 13, выход данных на ЗУ которой соединён со входом данных ЗУ 15. Вход данных ПФДН 14 соединён с первым выходом данных ЗУ 15, вход управления ПФДН 14 соединён с выходом управления УУ 16, выход данных ПФДН 14 соединён со входом данных приёмника 17. Адресная шина ЗУ 15 соединена со второй адресной шиной УУ 16, вход синхронизации УУ 16 соединён с выходом счётчика-делителя 19, шина данных и адреса ЗУ 15 соединена с шиной данных и адреса управляющей ЭВМ 18.

Схема блока задержки 20 представлена на рис. 3, где: 21 - буферный регистр доли периода дискретизации; 22 - регистр доли периода дискретизации; 23 - схема сравнения; 24 - счётчик; 25 - схема И; 26 - триггер.

В блоке задержки 20 вход данных буферного регистра доли периода дискретизации 21 соединён со входом данных 1, а вход записи буферного регистра доли периода дискретизации 21 соединён с адресным входом 2. Выход буферного регистра доли периода дискретизации 21 соединён со входом данных регистра доли периода дискретизации 22, выход которого соединён с первым входом схемы сравнения 23. Второй вход схемы сравнения 23 соединён с выходом счётчика 24, а выход схемы сравнения 23 соединён с выходом задержанных импульсов дискретизации 5 блока задержки 20, со входом установки в ноль триггера 26 и со входом обнуления счётчика 24. Вход импульсов дискретизации 4 блока задержки 20 соединён со входом установки в единицу триггера 26 и со входом записи регистра доли периода дискретизации 22. Единичный выход триггера 26 соединён с первым входом схемы И 25, второй вход которой соединён со входом импульсов фазирования 3 блока задержки 20, а выход соединён со счётным входом счётчика 24.

При осуществлении предложенного способа и работе предложенного устройства, также, как и в прототипе, на антенны 1 решётки падает фронт волны радиосигнала со сдвигом для антенны № i на время разности хода лучей Δtio относительно опорной антенны № о. Принятый антенной сигнал усиливают в соответствующем МШУ 2, понижают по частоте с использованием первого гетеродина 4 и смесителя 3, усиливают и ограничивают по полосе частот с использованием УПЧ-ПФ 5. Затем, на i-ом АЦП под воздействием задержанных на блоке 20 задержки импульсов дискретизации с частотой дискретизации fд от счётчика- делителя 19 частоты следования импульсов фазирования fф от генератора тактовых импульсов 11 формируют цифровые отсчеты принятого сигнала SiΔ, задержанные на заданную в регистре 22 i-го блока задержки долю периода дискретизации. Под воздействием адресных сигналов с дешифратора 12 от устройства управления 16 отсчеты сигналов разных антенн решетки последовательно вводят через шину данных 13 в ЗУ 15 и запоминают каждый в очередной ячейке своего индексированного массива отсчетов. Под воздействием управляющих сигналов от устройства управления 16 процессор формирования диаграммы направленности 14 вводит из индексированных массивов и складывает отсчеты разных антенн с индексами, относящимися к одному фронту волны принимаемого сигнала на разных антеннах. В результате при надлежащем выборе индексов цифровые сигналы разных антенн складывают в фазе.

То есть, с некоторой задержкой, достаточной для прихода сигнала от самой дальней антенны, в каждый такт дискретизации из каждого массива памяти выбираются по одному отсчету сигнала каждой антенны, индексы которых соответствуют одному фронту волны радиосигнала, падающего на антенную решетку, и складываются в фазе в процессоре (блоке) формирования диаграммы направленности 14. В качестве процессора формирования диаграммы направленности 14 может быть использован сигнальный процессор или программируемая логическая интегральная схема (ПЛИС). Перенос процесса фазирования сигналов разных антенн из блока формирования диаграммы направленности (см. прототип) в схемно реализованные блоки задержки для задержки сигнала на дробную долю периода дискретизации и в индексированные массивы ячеек памяти для хранения дискретных отсчетов для задержки сигнала на целочисленное количество периодов дискретизации, содержащихся в разности хода сигнала от фазовых центров ведомой и опорной антеннн до соответствующих входов в свои устройства аналого-цифрового преобразования, увеличивает быстродействие устройства фазирования не только узкополосных, но и широкополосных сигналов антенн неэквидистантной решетки антенного поля, поскольку процессору формирования диаграммы направленности ПФДН 14 в каждом периоде дискретизации остается только извлечь и сложить дискретные отсчеты разных антенн из ячеек соответствующих массивов с индексами ячеек, относящимися к тому же фронту волны сигнала, что и текущий индекс опорной антенны решетки. Разности между индексами ячеек массивов ведомых и опорной антенны для каждого периода дискретизации рассчитываются по целеуказаниям управляющей ЭВМ 18 и заносятся для ПФДН 14 в соответствующие массивы исходных данных ЗУ 15 по шине данных и адреса.

Таким образом, фазирование сигнала идет схемно, за счет использования счетчика-делителя 19, блока задержки 20 и индексированных массивах памяти за счет сдвигов по фазе сигналов разных антенн на целое число периодов дискретизации. Быстродействие устройства фазирования обеспечивается за счет снижения нагрузки на ПФДН 14, который только выбирает из массива и складывает отсчеты сигналов, предварительно записанные в ЗУ 15. Использование счетчика-делителя 19 и блока задержки 20 позволит отказаться от сложной процедуры обработки сигнала в процессоре (см. описание работы аналога), предусматривающей перемножение комплексных чисел. Также, использование блока задержки 20 обеспечит прием всех сигналов от антенн системы - сигнала опорной антенны (сигнал принимают раньше других), прочих антенн системы, а также сигнала от наиболее удалённой антенны (сигнал принимают последним). В результате, за счёт использования счётчика-делителя 19 и блока задержки 20, работающих описанным выше образом, значительно уменьшается искажение принимаемого сигнала. То есть, обеспечивается возможность приёма и фазирования широкополосных сигналов.

Блок задержки 20 работает следующим образом. По импульсному сигналу с адресного входа 2 сигнал доли периода дискретизации со входа 1 данных записывают в буферный регистр 21 доли периода дискретизации, по импульсному сигналу дискретизации со входа 4 импульсов дискретизации сигнал доли периода дискретизации переписывают с выхода буферного регистра 21 доли периода дискретизации в регистр 22 доли периода дискретизации. Одновременно импульсный сигнал дискретизации с входа 4 импульсов дискретизации поступает на вход установки в единицу триггера 26 и устанавливает триггер 26 в единичное состояние, при этом на первый вход схемы И 25 подаётся единичный сигнал, а со входа 3 импульсов фазирования через схему И 25 на счётный вход счётчика 24 начинают поступать импульсные сигналы фазирования. Счётчик 24 подсчитывает импульсные сигналы фазирования. Схема сравнения 23 по достижении сигнала на выходе счётчика 24 значения сигнала на выходе регистра 22 доли периода дискретизации вырабатывает на своём выходе задержанный импульсный сигнал дискретизации. Задержанный импульсный сигнал дискретизации поступает на выход 5 задержанных импульсов дискретизации и одновременно на вход установки в ноль триггера 26, устанавливая его в нулевое состояние, и на вход обнуления счётчика 24, обнуляя его содержимое перед следующим циклом дискретизации. При этом с выхода единичного сигнала триггера 26 на первый вход схемы И 25 подаётся нулевой сигнал, и со входа 3 импульсов фазирования через схему И 25 на счётный вход счётчика 24 перестают поступать импульсные сигналы фазирования. С приходом импульсного сигнала дискретизации со входа 4 импульсов дискретизации цикл работы блока задержки 20 повторяется.

Для гарантированно правильной работы предлагаемого устройства цифрового фазирования антенн, например, неэквидистантной решётки для приёма широкополосных сигналов необходимо, чтобы фронт сигнала с опорной антенны приходил на её АЦП раньше прихода этого же фронта сигнала с остальных антенн на соответствующие АЦП.

Поскольку время распространения фронта волны Tрi до АЦПi равно Tрi = Tпi + Tфi + Tа , где Tпi - время распространения фронта волны в свободном пространстве до фазового центра антенны № i, Tфi - время распространения фронта волны по фидеру антенны № i, Tа - время задержки сигнала в аппаратуре, то разность времён распространения фронта волны до АЦПi антенны № i и АЦПо опорной антенны № о равна ΔTiо = ΔTпiо + Tфi - Tфо , где ΔTпiо - разность хода фронта волны между фазовыми центрами антенн № i и № o.

Поскольку задержка прихода фронта волны на АЦПi измеряется относительно момента времени прихода фронта волны на АЦПо и суммарный сигнал может быть сформирован только после прихода фронта волны с последней антенны, то должно выполняться условие ΔTiо > 0, то есть, ΔTпiо + Tфi - Tфо > 0. Это условие выполняется при любых азимутах и углах места цели, если Tфi - Tфо > Liо/c, где Liо - максимально возможное расстояние между фазовыми центрами антенн № i и № о, c - скорость света в свободном пространстве. Поскольку скорость света в кабеле равна cк = c/ε1/2 , где ε - диэлектрическая проницаемость диэлектрика кабеля, то длины фидерных кабелей должны выбираться из условия: Lфi/cк - Lфо/cк > Liо/c или Lфi - Lфо > Liо/ε1/2.

Времена прихода фронта волны на АЦПi антенны № i и АЦПо опорной антенны № о отличаются на Δniо = ΔTiоfд = ΔTiоfд + (ΔTiоfд - ΔTiоfд) тактов дискретизации сигнала с частотой fд, где знак X обозначает целую часть числа X. При этом (ΔTiоfд - ΔTiоfд) - это дробная часть числа тактов дискретизации до момента времени, когда должен быть взят отсчёт сигнала на АЦПi из того же фронта, что пришёл на АЦПо опорной антенны ΔTiоfд тактов дискретизации назад.

Поскольку частота следования импульсов фазирования fф в fф/fд раз больше частоты следования импульсов дискретизации, то на дробной части такта дискретизации поместится (ΔTiоfд - ΔTiоfд)·fф/fд импульсов фазирования. Именно это значение должен иметь цифровой сигнал, вводимый в регистр 22 доли периода дискретизации блока задержки 20. Количества импульсов фазирования на дробной части такта дискретизации для каждой антенны рассчитывают заранее по целеуказаниям в управляющей ЭВМ 18 и вводят в запоминающее устройство 15.

С задержкой относительно момента времени взятия и записи в соответствующий индексированный массив памяти отсчёта сигнала с опорной антенны не менее LАП/c, где LАП - максимальный размер антенного поля, устройство управления 16 начинает очередной цикл формирования суммарного сигнала антенной решётки. Под воздействием импульса синхронизации с выхода счётчика-делителя 19 устройство управления 16 формирует на своей второй адресной шине для ЗУ 15 последовательность адресных сигналов ячеек индексированных массивов отсчётов сигналов антенн, причём начинает с очередного индекса массива отсчётов опорной антенны № о, а затем выдаёт адресные сигналы ячеек индексированных массивов отсчётов остальных антенн, при этом отсчёт сигнала с антенны № i берут из массива отсчётов сигнала антенны № i со сдвигом индекса массива на ΔTiоfд ячеек в сторону запаздывания относительно текущего индекса массива отсчётов сигнала опорной антенны. Параллельно УУ 16 формирует на своём выходе управления для процессора формирования диаграммы направленности 14 последовательность управляющих сигналов, получая которые по входу управления ПФДН 14 последовательно вводит цифровые сигналы отсчётов по входу данных от ЗУ 15 и формирует отсчёт суммарного сигнала и выдаёт его по выходу данных в приёмник 17. В результате формирование суммарного сигнала осуществляют за N - 1 операцию сложения, что существенно менее трудоёмко, чем в прототипе.

Таким образом, предложены способ и устройства, которые обеспечат приём и обработку широкополосных сигналов без искажений при сохранении быстродействия устройства фазирования антенн антенного поля при приёме от антенного поля широкополосных сигналов, несущих, например, телеметрическую информацию о состоянии бортовых систем космических аппаратов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ и устройство фазирования и равносигнально-разностного автосопровождения неэквидистантной цифровой антенной решётки приёма широкополосных сигналов | 2017 |

|

RU2652529C1 |

| ПРИЕМНОЕ УСТРОЙСТВО ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1983 |

|

SU1840292A1 |

| Устройство формирования и обработки широкополосных сигналов | 2018 |

|

RU2691733C1 |

| ЦИФРОВАЯ АКТИВНАЯ ФАЗИРОВАННАЯ АНТЕННАЯ РЕШЕТКА | 2015 |

|

RU2608637C1 |

| Способ передачи информации в системе связи с широкополосными сигналами | 2019 |

|

RU2696021C1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА ШИРОКОПОЛОСНЫХ СИГНАЛОВ НА РАЗНЕСЕННЫЕ АНТЕННЫ | 2000 |

|

RU2189112C2 |

| ЦИФРОВОЙ ПРИЕМНЫЙ МОДУЛЬ АКТИВНОЙ ФАЗИРОВАННОЙ АНТЕННОЙ РЕШЕТКИ | 2019 |

|

RU2722408C1 |

| Приёмное устройство широкополосных сигналов | 2018 |

|

RU2691731C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРИЕМНЫЙ МОДУЛЬ АКТИВНОЙ ФАЗИРОВАННОЙ АНТЕННОЙ РЕШЕТКИ | 2017 |

|

RU2692417C2 |

| УСТРОЙСТВО ПЕРЕДАЧИ И ПРИЕМА ДЛЯ ШИРОКОПОЛОСНОЙ РАДИОСВЯЗИ | 1980 |

|

SU1840131A1 |

Изобретение относится к радиотехнике и может использоваться для приёма широкополосных сигналов, например, в системе сбора телеметрической информации от бортовой аппаратуры космических аппаратов. Раскрыты способ обработки широкополосных сигналов и устройство фазирования антенн приёма широкополосных сигналов, преимущественно для антенн неэквидистантной решётки. Технический результат состоит в обеспечении повышения быстродействия устройства фазирования антенн антенного поля при приёме от антенного поля широкополосных сигналов, несущих, например, телеметрическую информацию о состоянии бортовых систем космических аппаратов. Последовательности импульсов запуска АЦП для дискретизации сигналов различных антенн решётки после полосового фильтра усилителя промежуточной частоты сдвигаются каждая в своём блоке задержки на свою долю периода дискретизации, которая равна остатку от деления разности времён хода сигналов от фазовых центров ведомых и опорной антенн до соответствующих входов в свои устройства аналого-цифрового преобразования. Длина фидеров подбирается так, чтобы время хода от опорной антенны до входа в свой АЦП было меньше времени хода от любой другой антенны решётки до входа в её АЦП на разность хода сигналов в свободном пространстве между наиболее удалёнными антеннами в решётке. С задержкой, достаточной для прихода сигнала от антенны с наибольшей положительной разностью времён хода сигналов от фазовых центров ведомой и опорной антенн до соответствующих входов в свои устройства аналого-цифрового преобразования, в каждый такт дискретизации из каждого массива памяти выбирают из соответствующих массивов и суммируют в блоке формирования диаграммы направленности дискретные отсчёты по одному от каждой антенны с индексами, относящимися к одному фронту волны сигнала. 2 н. и 3 з.п. ф-лы, 3 ил.

1. Способ обработки широкополосных сигналов, предусматривающий прием сигнала антеннами, являющимися частью антенной решетки, и формирование дискретных отсчетов принятого сигнала с последующим суммированием дискретных отсчетов от антенн решетки

при контроле времени хода сигнала от опорной антенны и от остальных ведомых антенн антенной решетки до соответствующих устройств аналого-цифрового преобразования, отличающийся тем, что

сигналы, принятые указанными антеннами, задерживают на доли периода дискретизации, равные соответствующим остаткам от деления на период дискретизации разностей времен хода сигналов от фазовых центров ведомых и опорной антенн антенной решетки до входов в соответствующие устройства аналого-цифрового преобразования,

сформированные дискретные отсчеты принятых сигналов от соответствующих антенн записывают в соответствующие индексированные массивы памяти, причем запись выполняют

в ячейки с соответствующими индексами, которые относятся к текущему фронту волны принимаемого сигнала и

с задержкой, достаточной для прихода сигнала от антенны с наибольшей положительной разностью времен хода сигналов от фазовых центров ведомой и опорной антенн до соответствующих входов в свои устройства аналого-цифрового преобразования, после записи дискретных отсчетов выбирают из соответствующих массивов и суммируют дискретные отсчеты по одному от каждой антенны с индексами, относящимися к одному фронту волны сигнала.

2. Устройство фазирования антенн приема широкополосных сигналов, содержащее совокупность трактов приема сигналов от антенн, являющихся частью антенной решетки, причем

каждый из трактов приема сигналов связан с шиной данных и включает аналого-цифровой преобразователь, связанный с генератором тактовых импульсов и через дешифратор адресного сигнала с устройством управления,

при этом устройство управления, дешифратор адресного сигнала и генератор тактовых импульсов являются общими для каждого из трактов приема сигналов, отличающееся тем, что

каждый из трактов приема сигналов включает блок задержки, у которого

выход задержанных импульсов дискретизации соединен со входом импульсов запуска соответствующего аналого-цифрового преобразователя,

вход данных соединен с соответствующим выходом на блок задержки шины данных,

адресный вход соединен с соответствующим выходом дешифратора адресного сигнала,

вход импульсов фазирования соединен с выходом генератора тактовых импульсов,

вход импульсов дискретизации соединен с выходом счетчика-делителя, причем

вход счетчика-делителя соединен с выходом генератора тактовых импульсов,

с выходом счетчика-делителя соединен вход синхронизации устройства управления.

3. Устройство фазирования антенн приема широкополосных сигналов по п. 2, отличающееся тем, что блок задержки содержит

буферный регистр доли периода дискретизации, регистр доли периода дискретизации, схему сравнения, счетчик, схему И, триггер, причем

вход данных буферного регистра доли периода дискретизации соединен со входом данных блока задержки, вход записи буферного регистра доли периода дискретизации соединен с адресным входом блока задержки, выход буферного регистра доли периода дискретизации соединен со входом данных регистра доли периода дискретизации, выход буферного регистра доли периода дискретизации соединен с первым входом схемы сравнения,

второй вход схемы сравнения соединен с выходом счетчика, выход схемы сравнения соединен с выходом задержанных импульсов дискретизации блока задержки, со входом установки в ноль триггера и со входом обнуления счетчика,

вход импульсов дискретизации блока задержки соединен со входом установки в единицу триггера и со входом записи регистра доли периода дискретизации,

единичный выход триггера соединен с первым входом схемы И, второй вход схемы И соединен со входом импульсов фазирования блока задержки, выход схемы И соединен со счетным входом счетчика.

4. Устройство фазирования антенн приёма широкополосных сигналов по п. 2, отличающееся тем, что включает общие для каждого из трактов приёма сигналов

процессор (блок) формирования диаграммы направленности, запоминающее устройство, приёмник, управляющую ЭВМ, причём

адресный вход аналого-цифрового преобразователя в каждом тракте приёма сигналов соединён с соответствующим выходом дешифратора адресного сигнала,

вход которого соединён с первой адресной шиной устройства управления,

выход данных аналого-цифрового преобразователя в каждом тракте приёма сигналов соединён с соответствующим входом шины данных,

вход данных процессора формирования диаграммы направленности соединён с первым выходом данных запоминающего устройства,

вход управления процессора формирования диаграммы направленности соединён с выходом управления устройства управления,

адресная шина запоминающего устройства соединена со второй адресной шиной устройства управления,

шина данных и адресная шина запоминающего устройства соединена с шиной данных и адресной шиной управляющей ЭВМ,

выход данных процессора формирования диаграммы направленности соединён со входом приёмника,

второй выход данных запоминающего устройства соединён со входом данных от запоминающего устройства шины данных,

выход данных на запоминающее устройство шины данных соединён со входом данных запоминающего устройства.

5. Устройство фазирования антенн приёма широкополосных сигналов по п. 2, отличающееся тем, что каждый из трактов приёма сигналов включает

приёмную антенну, входной малошумящий усилитель с фидерами до смесителя, смеситель, общий для каждого из трактов приёма сигналов гетеродин, усилитель промежуточной частоты с полосовым фильтром, при этом

выход приёмной антенны соединён со входом соответствующего малошумящего усилителя с фидером до смесителя, каждый малошумящий усилитель через фидер соединён с сигнальным входом смесителя, гетеродинный вход которого соединён с выходом гетеродина, выход каждого смесителя соединён со входом соответствующего усилителя промежуточной частоты с полосовым фильтром, а

выход усилителя промежуточной частоты с полосовым фильтром соединён с сигнальным входом аналого-цифрового преобразователя.

| АКТИВНАЯ ФАЗИРОВАННАЯ АНТЕННАЯ РЕШЕТКА | 2007 |

|

RU2338307C1 |

| СПОСОБ МНОГОКАНАЛЬНОГО АДАПТИВНОГО ПРИЕМА РАДИОСИГНАЛОВ И УСТРОЙСТВО, ЕГО РЕАЛИЗУЮЩЕЕ | 2011 |

|

RU2477551C1 |

| СПОСОБ ОПРЕДЕЛЕНИЯ УГЛОВОГО СПЕКТРА | 2011 |

|

RU2452974C1 |

| US 4994813 A1 19.02.1991 | |||

| US 20020171583 A1 21.11.2002 | |||

| Роликоопора рольганга для ориентированной подачи изделий | 1980 |

|

SU901183A1 |

Авторы

Даты

2016-08-20—Публикация

2015-05-25—Подача