1

(21)4694081/21 (22)22.05.89 (46)23.11.91. Бюл. №43 (72) А.И.Панов и А.И.Лепехин (53)621.374(088.8)

(56)Эдукайтис Д.Ю., Орлов Б.В., Попель Л ,М. и др. Измерение параметров цифровых интегральных микросхем. /Под ред. Д.Ю.Эдукайтиса, Б.В.Орлова.- М.: Радио и связь, 1982.

Авторское свидетельство СССР № 1432748,кл. Н 03 К 5/01, 1987. (54) ФОРМИРОВАТЕЛЬ ПРЯМОУГОЛЬНЫХ ИМПУЛЬСОВ

(57)Изобретение относится к импульсной технике и предназначено для использования в контрольно-измерительном оборудовании, в частности в системах контроля интегральных схем (ИС) повышенной степени интеграции, с рабочей частотой до 100 МГц, где формирователь применяется в качестве драйвера-эадатчика входных

2

воздействий на контролируемые И С. Цепь изобретения - расширение фунгц./ онэпь- ных возможностей за счет реализации с режиме Третье состояние проме;куто ных значений выходного сопротивления формирователя между высокоомным значением, характерным для режима Третье состояние, при котором выходная шина находится в отключенном состоянии, и низхломным значением, характерным для режима фор- мирорания импульсов, а также поьышенмс точности формирования. Цель досжгзеточ путем образования новых функциональных сзязей, а также путем введения в блеж 3 задания режимов двух регулируемых никое питания, при этом выходной каскад выполнен в виде моста. Формирова ь содержит гакхе 6ло 1 управления, €лок 2 формирования амплитуды, разнопгяярнмм источники опорных напряжений, входные шины 5 и 6 и выходную шину 7. 2 з.п. ф-лы, 2 ил.

VI

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь прямоугольных импульсов | 1987 |

|

SU1432748A1 |

| Усилитель-формирователь прямоугольныхиМпульСОВ | 1979 |

|

SU847501A1 |

| Формирователь прямоугольных импульсов | 1989 |

|

SU1674356A1 |

| Усилитель-формирователь прямоугольных импульсов | 1976 |

|

SU683001A1 |

| Интегральный формирователь импульсов | 1987 |

|

SU1547044A1 |

| Формирователь высоковольтных прямоугольных импульсов | 1978 |

|

SU771863A1 |

| Формирователь высоковольтных прямоугольных импульсов | 1980 |

|

SU869001A1 |

| Интегральный преобразователь импульсов | 1987 |

|

SU1499449A1 |

| Усилитель-формирователь импульсов | 1980 |

|

SU930617A1 |

| Генератор строчной развертки | 1990 |

|

SU1815805A1 |

1

г

Ч

Л

Изобретение относится к импульсной технике и предназначено для использования в контрольно-измерительном оборудовании, в частности в системах контроля интегральных схем (ИС) повышенной степени интеграции с рабочей частотой до 100 МГц, где предлагаемый формирователь применяется в качестве драйвера-за- датчика входных воздействий на контролируемые ИС.

Цель изобретения - расширение функциональных возможностей формирователя прямоугольных импульсов за счет реализации в режиме Третье состояние промежуточных значений выходного сопротивления между высокоомным, характерным для режима Третье состояние, при котором выходная шина находится в отключенном состоянии, и низкоомным значением, характерным для режима формирования импульсов, а также повышение точности формирования.

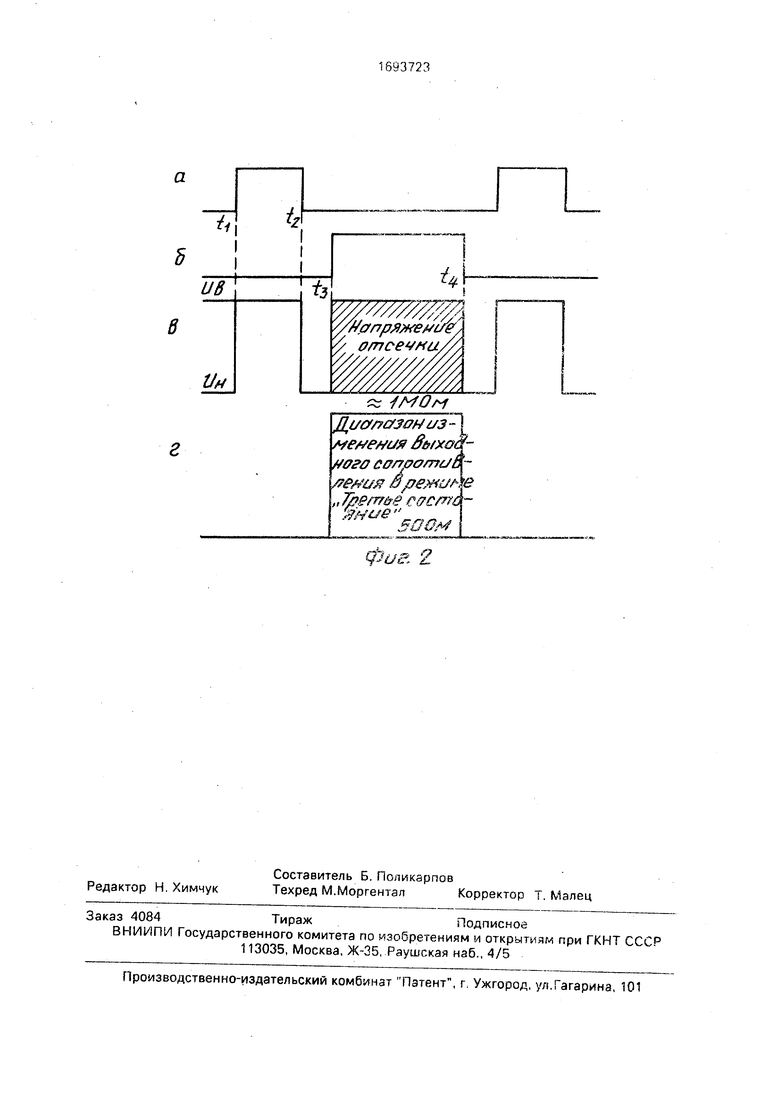

На фиг.1 изображена электрическая схема формирователя прямоугольных импульсов; на фиг.2 - временные диаграммы его работы.

Формирователь прямоугольных импульсов содержит блок 1 управления, блок 2 формирования амплитуды, блок 3 задания режимов, выходной каскад 4, две входные шины 5 и б, выходную шину 7 и разнополяр- ные источники (Ei, E-) опорных напряжений.

блок 1 управления состоит из двух элементов ИЛИ 8 и 9, двух дифференциальных усилителей на транзисторах 10. 11 и 12, 13 соответственно (позициями указаны только активные элементы) и регулируемого источника 14 питания.

Блок 2 формирования амплитуды представляет собой дифференциальный усилитель, выполненный на транзисторах 15 и 16. Блок 3 задания режимов содержит элементы ИЛИ 17 и 18, два дифференциальных усилителя на транзисторах 19. 20 и 21, 22 соответственно, два источники тока на транзисторах 23 и 24 и равнополярные регулируемые источники 25 и 26 питания. Выходной каскад представляет собой мостовую схему на транзисторах 27-30 и резисторах 31 и 32.

Входы элементов ИЛИ 8 и 9 являющиеся первь м и вторым входами блока 1 управ- ления соответственно, раздельно соединены с входными шинами 5 и 6. Прямые выходы элементов ИЛИ 8 и 9 раздельно соединены с базами транзисторов 10 и 12 соответственно, э инверсные выходы - с базами транзисторов 11 и 13. Эмиттеры транзисторов 12 и 13 соединены с регулируемыми источником 14 питания. Коплскгорм транзисторов 10 и 11, образующие первый и второй выходы блока 1 управления, раздельно соединены с базами транзисторов

15 и 16, образующими первый и второй входы блока 2 формирования амплитуды. Коллектор транзистора 13, образующий третий выход блока 1 управления, соединен с эмиттерами транзисторов 15 и 16. Входы элемен0 тов ИЛИ 17 и 18. образующие вход блока 3 задания режимов, соединены с входной шиной 6; прямые выходы элементов ИЛИ 17 и 18 раздельно соединены с базами транзисторов 20 и 21 соответственно, а инверсные

5 - с базами транзисторов 19 и 22. Эмиттеры транзисторов 19 и 20 соединены с регулируемым источником 25 питания, а эмиттеры транзисторов 21 и 22 - с регулируемым источником 26 питания. Коллектор транзисто0 ра 20 соединен с эмиттером транзистора 23, коллектор которого, являющийся первым выходом блока 3 задания режимов, соединен с эмиттерами транзисторов 27 и 29 выходного каскада 4;коллектор транзистора

5 22 соединен с эмиттером транзистора 24, коллектор которого, являющийся вторым выходом блока 3 задания режимов , соединен с эмиттерами транзисторов 28 и 30. Базы транзисторов 27 и 28 соединены с кол0 лектором транзистора 16, являющимся выходом блока 2 формирования амплитуды. Коллекторы транзисторов 29 и 30 соединены с выходной шиной 7 формирователя прямоугольных импульсов. Между базами и

5 коллекторами транзисторов 29 и 30 включены резисторы 31 и 32 соответственно. Источник (Е+) опорного напряжения положительной полярности через резисторы соединен с коллекторами транзисторов

0 15 и 16 блока 2 формирования амплитуды, а источник (Е-) опорного напряжения отрицательной полярности через резистор - с эмиттерами этих же транзисторов.

Блок 1 управления предназначен для

5 приема с входных шин 5 и 6 сигналов данных и сигнала включения режима Третье состояние соответственно и формирования сигналов управления работой транзисторов 15 и 16 блока 2 формирования

0 амплитуды. Элементы ИЛИ 8 и 9 блока 1

управления выполнены на микросхемах К

1500 ЛМ 102, в качестве транзисторов 10-13

применены транзисторы типа КТ363Б.

Блок 2 формирования амплитуды совме5 стно с разнополярными источниками (Е+, Е-) опорных напряжений служит для выработки верхнего UB и нижнего UH уровней напряжения формируемого импульса. В рассматриваемом примере реализации уровня UB, UH задаются в диапазоне от -3 В до +3 В. Блок

2 формирования амплитуды собран на транзисторах КТ 640А. В качестве источников (Е+, Е-) опорных напряжений применены программируемые стабилизированные источники постоянного напряжения с дискретностью задания напряжения 3 мВ.

Блок 3 задания режимов служит для приема с входной шины 6 сигнала включения режима Третье состояние и формирования посредством источников тока на транзисторах 23 и 24 токов высокого и низкого уровней для транзисторного моста выходного каскада 4.

Выходной каскад 4, выполненный в виде транзисторного моста, предназначен для передачи импульсных сигналов заданной амплитуды с уровнями UB, UH на выходную шину 7 формирователя в режиме формирования импульсов, а при работе в качестве эквивалента нагрузки выходной каскад 4 предназначен для переключения токов высокого и низкого уровня при переходе напряжения на выходной шине 7 через пороговое значение напряжения отсечки, которое задается с блока 2 формирования амплитуды. Блок 3 задания режимов и выходной каскад 4 выполнены на транзисторах КТ 363Б, КТ 368Б. Выполнение выходного каскада 4 на транзисторах позволило уменьшить потребляемый ток блока 2 формирования амплитуды и тем самым применить в нем маломощные, но высокочастотные транзисторы. Резисторы 31 и 32 выходного каскада 4 предназначены для устранения насыщения транзисторов 29 и 30, что способствует сохранению высокого быстродействия формирования прямоугольных импульсов.

Формирователь прямоугольных импульсов работает следующим образом.

В режиме формирования импульсов с входной шины 5 на элемент ИЛИ 8 блока 1 управления в момент времени ti поступает сигнал уровня 1 (фиг.2а). С прямого и инверсного выходов элемента ИЛИ 8 сигналы 1 и О соответственно поступают на базы транзисторов 10 и 11, с коллекторов которых сигналы поступают на базы транзисторов 15 и 16 блока 2 формирования амплитуды. С коллекторной нагрузки транзистора 16 сигнал заданной амплитуды поступает на базы транзисторов 27 и 28 выходного каскада 4. На входной шине 6 в режиме формирования импульсов установлен уровень О (фиг.2б). При этом транзистор 12 блока 1 управления открыт, а транзистор 13 закрыт и не влияет на работу транзисторов 15 и 16 блока 2 формирования амплитуды. Транзисторы 20 и 22 блока 3 задания режимов при уровне О на входной

шине 6 также закрыты и не влияют на работу транзисторов 23 и 24 в режиме формирования импульсов, Сигнал заданного уровня Ув, определяемого источником Е+ опорного 5 напряжения, через транзисторный мост выходного каскада 4 поступает на выходную шину 7 формирователя прямоугольных импульсов. Сигнал уровня UH, определяемый источником Е- опорного напряжения, фор0 мируется при установлении уровня О на входной шине 5 описанным образом с той лишь разницей, что полярность выходных сигналов блока 1 управления, блока 2 формирования амплитуды и выходного каскада

5 4 меняется на противоположную вследствие переключения транзисторов перечисленных блоков. В режиме Третье состояние на входной шине 5 установлен уровень О, а на шине 6 - уровень 1

0 (фиг.26, момент времени ts). При этом транзистор 13 блока 1 управления откры и через него от регулируемого источника 14 питания в эмитгерную цепь транзистора 16 блока 2 формирования амплитуды задается допол5 нительный ток, в результате чего напряжение на коллекторе транзистора 16, и следовательно, на базах транзисторов 27 и 28 выходного каскада 4 будет изменяться в диапазоне напряжений от уровня (JH (ниж0 ний уровень) до уровня UB (высокий уровень), как показано на фиг.2в, в зависимости от величины тока, определяемого регулируемым МСТОЧНИКОРЛ 14 питания. В режиме Третье состояние (в интервале времени 1з,

5 ц) транзисторы 20 и 22 блока 3 задания режимов открыты и через них в эмиттеоные цепи соответствующих транзисторов 23 и 24 от регулируемых источников 25 и 26 питания задаются дополнительные токи, в результа0 те чего происходит изменение токов в коллекторных цепях транзисторов 23 и 24, и, следовательно, изменение выходного сопротивления транзисторного моста выходного каскада 4 (фиг.2г). При полностью

5 закрытых транзисторах 23 и 24 выходное сопротивление транзисторного моста составляет около 1 МОм.

При использовании формирователя пря юугольных импульсов в контрольно-из0 мерительном оборудовании для НС с совмещенными входами-выходами он (формирователь) в режиме формирования импульсов является драйвером-задатчпком входных воздействий, передаваемых нэ вы5 воды контролируемой ИС. т.е. обеспечивает входной ток соответствующего вывода, а в. режиме Третье состояние формирователь является эквивалентом нагрузки на соответствующий вывод, т.е. обеспечивает его электрический режим (ток высокого уровня, ток

низкого уровня и пороговое напряжение отсечки, при котором происходит переключение названных токов). Значения токов высокого и низкого уровней определяются выходным сопротивлением транзисторного моста выходного каскада 4, причем задание токов низкого и высокого уровней осуществляется посредством источников тока на транзисторах 23 и 24 блока 3 задания режимов, а уровень напряжения отсечки опреде- ляется коллекторным напряжением транзистора 16 блока 2 формирования амплитуды.

Совмещение в формирователе прямоугольных импульсов функций драйвера-за- датчика и эквивалента нагрузок для контролируемой ИС позволило исключить из контрольно-измерительного оборудования блок эквивалентов нагрузок и вместе с ним - емкость, вносимую в тракт драйвер- контролируемая ИС, следствием чего является уменьшение емкости тракта СТр на 8-10 пФ и повышение быстродействия измерения до 100 МГц.

Формула изобретения 1. Формирователь прямоугольных импульсов, содержащий блок управления, блок формирования амплитуды, разнопо- лярные источники опорных напряжений, блок задания режимов, выходной каскад, две входные и выходную шины, причем входные шины раздельно соединены с входами блока управления, первый и второй выходы которого раздельно соединены с соответствую щи ми входами блока формирования амплитуды, соединенного с разнополярными источниками опорных напряжений, выход блока формирования амплитуды соединен с входом выходного

каскада, подключенного к первому и второму выходам блока задания режимов и выходной шине, отличающийся тем что, с целью расширения функциональных возможностей за счет реализации в режиме Третье состояние промежуточных значений выходного сопротивления формирователя между низкоомным и высокоомным значениями, третий выход блока управления соединен с третьим входом блока формирования амплитуды, вход блока задания режимов соединен с второй входной шиной, блок задания режимов содержит два регулируемых источника питания, а выходной каскад выполнен в виде моста, образованного транзисторами разного типа проводимости, при этом первый вход моста, образованный объединенными базами входных транзисторов разного типа проводимости, соединен с

выходом блока формирования амплитуды, второй и третий входы раздельно соединены с выходами соответствующих регулируемых источникоа питания блока задания режимов, а выход моста - с выходной шиной

и через резисторы - с базами выходных транзисторов моста.

попарно объединенными эмиттерами входных и выходных транзисторов.

Л1/0/70Э0Н U3 меяенмя#0го coffoomejb - яе#{/я a/tewtjf. e

„ТЪет&е C&C/TTQ

5GO&

4МОн

Авторы

Даты

1991-11-23—Публикация

1989-05-22—Подача