со

ND

ф

СХ)

LЯ,i

IUIH.I

Изобретение относится к импульсной технике и предназначено для использования в ко1,трольно-измеритель ом оборудовании, в частности в системах контроля интегральных схем (ИС) различно степени интеграции, и :шжет быть применено в качестве драйвера-задатчика напряжений (входных воздействий) на выводы контролируемых схем.

Цель изобретения - повышение быстродействия посредством уменьшения времени включения режима Третье состояние.

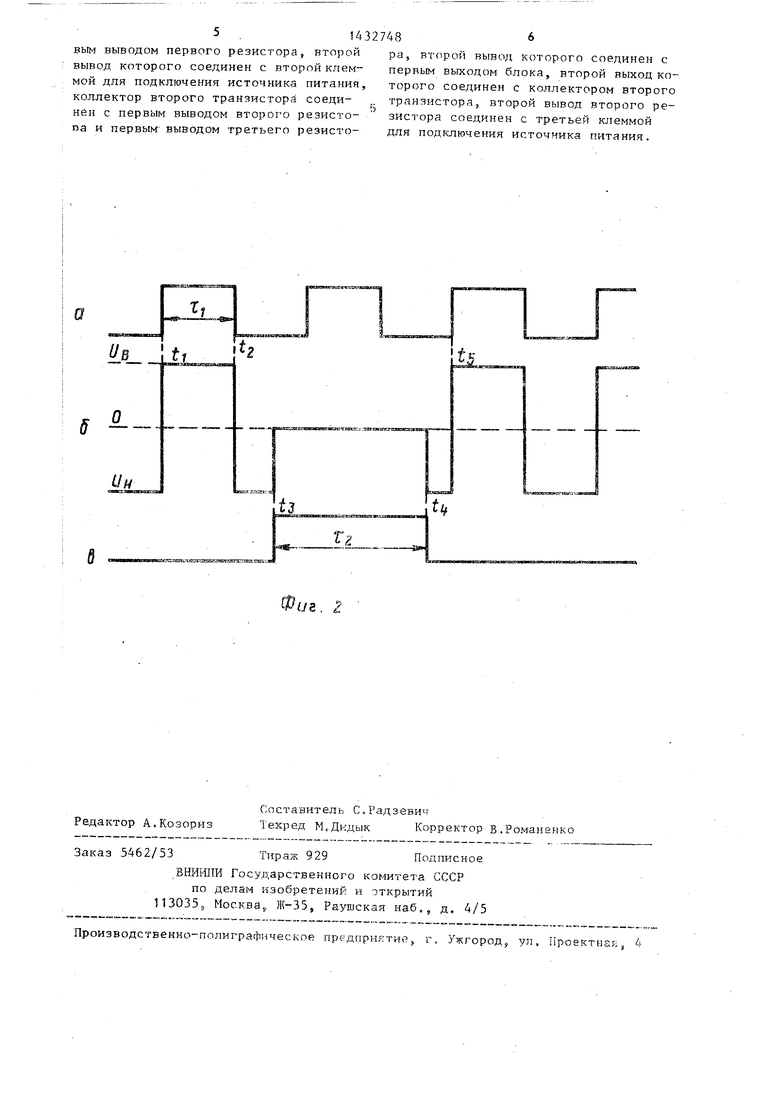

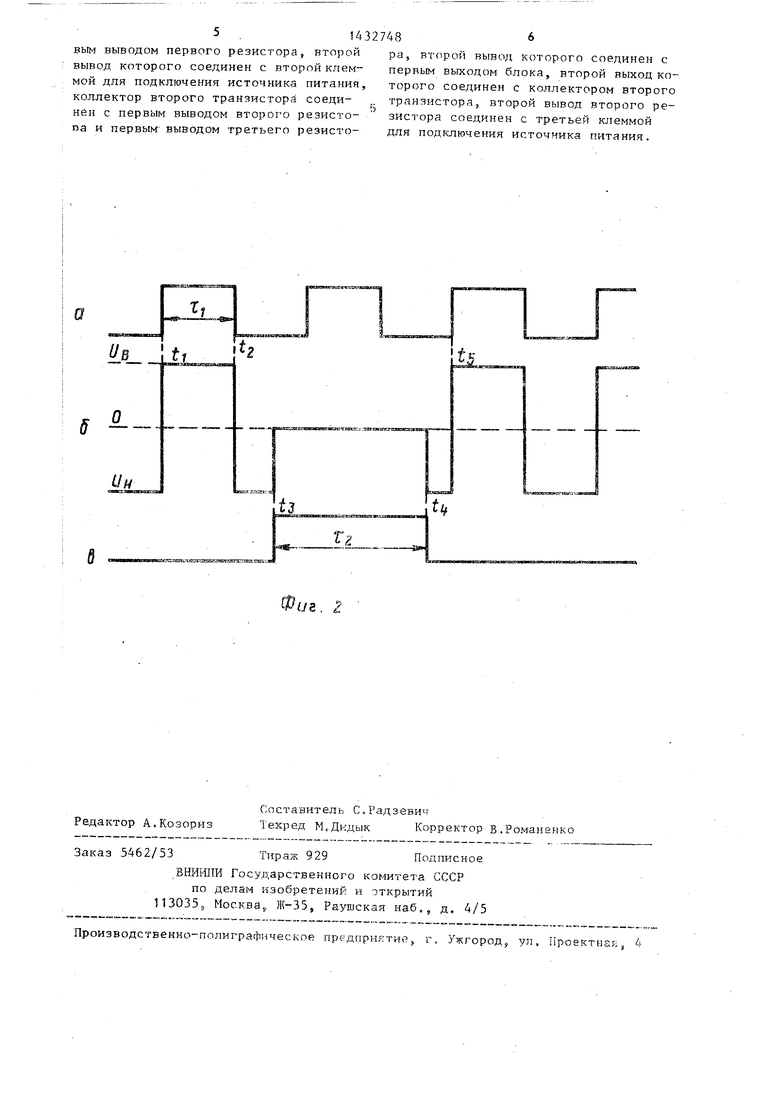

На фиг, 1 изображена электрическая схема формирователя прямоугольных им- Ьульсов; на фиг. 2 - временные диаг- |раммы его работы.

Формирователь прямоугольных импуль |сов содержит блок 1 управления, блок 12 формирования амплитуды, повторитель 3 напряжения, блок 4 задания режимов,, две входные 5 и 6 и выходную 7 шины. I Блок 1. управления состоит из двух 1элементов ИЛИ 8 и 9 и двух дифферен- циальных усилителей на транзисторах ПО и 11 и 12 и 13 соответственно. Блок 2 формирования амплитуды пред- уставляет собой дифференциальный уси- Длитель на транзисторах 14 и 15, пов- |торитель 3 напряжения эмиттерный пов- |торитель на транзисторе 16,а блок 4 {задания режимов - дифференциальный уси- литель на транзисторах 17 и 18 с ре- зисторами 19-21 и клеммами 22 и 23. : Формирователь прямоугольных импульсов содержит также разнополярные источники 24 и 25 опорных напряжений, а повторитель 3 напряжения - клемму 26. Первый вход элемента ИЛИ 8, яв- ляюш;ийся первым входом блока 1 управления, соединен с входной тиной 5, второй вход - с прямым выходом элемента ИЛИ 9, вход которого, являющийся вторым входом блока 1 управления, подключен к входной шине 6 о Прямые выходы элементов. ИЛИ 8 и 9 раздельно соединены с базами транзисторов 10и ,12 соответственно, а инверсные выходы - с базами транзисторов 11 и 13. Коллекторы транзисторов 10 и 11, образующие первый и второй выходы блока 1 управления, раздельно соединены с базами транзисторов 14 и 15, образующими первый и второй входы блока 2 формирования амплитуды.

Коллекторы тра зисторов 12 и 13, образующие третий и четвертый выходы блока 1 управления, раздельно соеди

. ,. j.

0

нены с базами транзисторов 17 и 18 соответственно, образующими первый и второй входы блока 4 задания режима.

Коллектор транзистора 17 через резистор 20, один вывод которого образует первый выход блока 4 задания режима, соединен с коллектором транзистора 14, являющимся выходом блока 2 формирования амплитуды, и с базой транзистора 16, являющейся входом повторителя 3 напряжения, а через резистор 19 - с клеммой 23.

Коллектор транзистора 18, образующий второй выход блока 4 задания режимов, соединен с эмиттером транзистора 16, являющимся выходом повторителя 3 напряжения, и выходной шиной 7. Эмиттеры транзисторов 17 и 18 через резистор 21 соединены с клеммой 22. Источник 24 опорного напряжения положительной полярности через резистор соединен с эмиттерами транзисторов 14 и 15 блока 2 формирования ам- плитуды, а источник 25 опорного напряжения - с коллекторами этих же тран- I

зисторов (через соответствующие резисторы) .

Формирователь прямоугольных импульсов работает следующем образом.

Пусть необходимо сформировать на выходной шине 7 импульсы, длительность которых равна длительности входных импульсов, поступающих на входную шину 5, причем в процессе формирования заданных импульсов необходимо реализовать возможность переключения формирователя в режим Третье состояние по приходу на входную шину 6 управляющего сигнала.

В момент времени t на первьй вход элемента ИЛИ 8 блока 1 управления с входной шины 5 поступает сигнал уровня 1 (фиг.2а). С прямого и инверсного выходов элемента ИЛИ 8 сигналы 1 и О соответственно поступают на базы транзисторов 10 и 11. При этом транзистор 1U открывается, обеспечивая открывание транзистора 14 блока 2 формирования амплитуды и формирование переднего фронта выходного импульса (фиг.26). В течение длительности f, на базу транзистора 16 повторителя 3 напряжения через открытый транзистор 14 поступает высокий уровень напряжения, определяемый протекающим током, задаваемым источником 24 опорного напряжения. При этом, поскольку па входной шине 6 установлен О, транзисто-.

ры 13 и 18 открыты, и результате чего работа трат)зистора 16 осуществляется в линейном режиме за счет задания через него тока транзистором 18 блока 4 задания режима. Высокий уровень напряжения проходит на выходную шину 7, формируя требуемый высокий уровень Ug выходного импульса (фиг.26),

В момент времени-tj на входную. шину 5 поступает сигнал О,, приводя- ций к закрыванию транзисторов Юн 14, в результате чего напряя ение с источ. Формирователь прямоугольных импульсов, содеря аший блок управления, блок формирования амплитудь, источник положительного опорного напряжения.

ника 25 опорного напряжения поступает на базу транзистора 16 повторите- 5 источник отрицательного опорного на- ля 3 напряжения, и на выходной шине 7 пряжения, первую и вторую входные ши формируется низкий уровень напряжения ны,выходную Ш1ну, первая и вторая вход- и вькодного имдульса (фиг.26, момент

времени t, ).

ные шины соединены соответственно с первым и вторым входами блока управления, Цереключение формирователя в режим 2о первый и второй выходы которого сое- Третье состояние осуществляется в. динены соответственно с первым и вто- момент времени t по приходу на вход- рым входами блока формирования ампли- ную щину 6 управлдюи его импульса длительностью t (фиг.2в, момент време-г

туды, третий и четвертый входы которого соединены соответственно с исни tj ), Сигнал 1 с шины 6 поступает25 точник;ами положительного и отрицательна вход элем,ен-та ИЖ 9, с прямого выного опорных напряжений, о т л и ч а- ю ш, и и с я тем, что, с целью повышения быстродействия за счет уменьшения времени включения режима Третье состояние, в него введены повторивторой вход элемента ИЛИ 8,, в ре зуль- тате чего на инверсном выходе элемента ЦЛИ В устанавливается сигнал О, gg обеспечивая закрывание транзисторов и 1-5, Цри этом.транзисторы 10 и 14 (Открываются. Сигналы 1, прямого и инверсного выходов элемента ИЛИ 9 .

ного опорных напряжений, о т л и ч а- ю ш, и и с я тем, что, с целью повышения быстродействия за счет уменьшения времени включения режима Третье состояние, в него введены повторитель напряжения и блок задания режимов, причем первый и второй входы блока задания режимов соединены соответственно с третьим и четвертым вы- поступают на базы транзисторов 12 и . ходами блока управления, первый выход 13 соответственно, в результате чего блока задания режимов соединен с вхо- транзистор 12 открывается, обеспечивая открывание транзистора 17 блока 4

задания режима, а транзистор 13 задом, повторителя напряжения и выходом блока формирования амплитуды, а вто- 1рой выход соединен с выходом повтори- крывается, обеспечивая закрывание Q ,теля напряжения и выходной шиной, транзистора 18. Открытый транзистор 2. Формирователь по п.1, о т л и - 17 обеспечивает протекание дополнительного тока через токоограничиваючающиися тем, что повторитель напряжения содержит транзистор, клемму для подключения источника питания.

щий резистор 20, включенный в каллекописано выше с момента времени t, . Таким образом, происходит формирование прямоугольных импульсов на выходе устройства с переключением его в режим Третье состояние на время действия управляющего импульса, поступающего на входную ишну 6.

Формула изобретения

. Формирователь прямоугольных импульсов, содеря аший блок управления, блок формирования амплитудь, источник положительного опорного напряжения.

источник отрицательного опорного на- пряжения, первую и вторую входные ши ны,выходную Ш1ну, первая и вторая вход-

ные шины соединены соответственно с пер вым и вторым входами блока управления, первый и второй выходы которого сое- динены соответственно с первым и вто- рым входами блока формирования ампли-

туды, третий и четвертый входы которого соединены соответственно с источник;ами положительного и отрицатель

точник;ами положительного и отрицательного опорных напряжений, о т л и ч а- ю ш, и и с я тем, что, с целью повышения быстродействия за счет уменьшения времени включения режима Третье состояние, в него введены повторидом, повторителя напряжения и выходом блока формирования амплитуды, а вто- рой выход соединен с выходом повтори- теля напряжения и выходной шиной, 2. Формирователь по п.1, о т л и -

чающиися тем, что повторитель напряжения содержит транзистор, клемму для подключения источника питания.

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь прямоугольных импульсов | 1989 |

|

SU1693723A1 |

| Формирователь прямоугольных импульсов | 1989 |

|

SU1674356A1 |

| Устройство для контроля цифровых блоков | 1988 |

|

SU1619208A1 |

| Интегральный формирователь импульсов | 1987 |

|

SU1547044A1 |

| Устройство для измерения порогового напряжения полевых транзисторов | 1981 |

|

SU1109685A1 |

| Интегральный преобразователь импульсов | 1987 |

|

SU1499449A1 |

| Способ поиска дефектов в цифровых блоках и устройство для его осуществления | 1985 |

|

SU1260884A1 |

| Устройство для моделирования @ -фазного вентильного электродвигателя | 1990 |

|

SU1797133A1 |

| Формирователь импульсов управления | 1985 |

|

SU1290501A1 |

| Стабилизатор постоянного напряжения | 1988 |

|

SU1539748A1 |

Изобретение относится к импульсной технике и предназначено для использования в контрольно-измерительном оборудовании, в частности в системах контроля интегральных схем. Цель изобретения - повьшение быстродействия посредством уменьшения времени включения режима Третье состояние. Логический сигнал тестовой последовательности поступает на клемму 5 блока 1 управления, посредством которого управляет работой блока 2 формирования амплитуды. Сформированный сигнал с заданными значениями верхнего и нижнего уровней через повторитель 3 напряжения поступает на выходную клемму 7 устройства. Введение в формирователь пря моугольных импульсов повторителя 3 напряжения и блока 4 задания режимов позволяет подавать с клеммы 6 сигнал блокировки через блок 1 управления на транзисторы дифференциального каскада и тем самым с высокой скоростью переключать рабочий ток повторителя 3 напряжения, что обеспечивает малое время включения pe raiMa Третье состояние. В формирователе использованы элементы ИЛИ 8 и 9, транзисторы 10-18, резисторы 19-21, источники 24 . и 25 опорных напряжений, клеммы 22, 23 и 26. 2 з.п. ф-лы, 2 ил. S СЛ

торные цепи транзисторов 14 и 17, в g. причем база транзистора соединена с

результате чего на базе транзистора 16 формируется напряжение вольтодо- бавки, являющееся дополнительным запирающим напряжением для этого транзистора.

Таким образом, до момента времени t т.е. на время длительности f управляющего импульса, транзисторы 16 и 18 закрыты, их токи утечки минимальны, а выходное сопротивление. максимально, чем обеспечивается ре- м Третье состояние.

С момента времени t формирования импульсов повторяется, как

50

55

входом повторителя напряжения, эмитт соединен с выходом повторителя напря жения, а коллектор соединен с клеммо для подключения источника питания.

0

5

входом повторителя напряжения, эмиттер соединен с выходом повторителя напряжения, а коллектор соединен с клеммой для подключения источника питания.

вьгм выводом первого резистора, второй вывод которого соединен с второй клеммой для подключения источника питания, коллектор второго транзистора соединен с первым выводом второго резисто- па и первым выводом третьего резисто;з

ра пе то тр зи дл

5

О

t3

Фик. 2

ра, второй вывод которого соединен с первым выходом блока, второй выход которого соединен с коллектором второго транзистора, второй вывод второго резистора соединен с третьей клеммой для подключения источника питания.

t

| Формирователь прямоугольных импульсов | 1984 |

|

SU1221721A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Эйдукас Д.Ю., Орлов Б.В., Попель Л,М | |||

| и др | |||

| Измерение параметров цифровых интегральных микросхем | |||

| М.: Радио и связь, 1982, с.267, рис.6.21. | |||

Авторы

Даты

1988-10-23—Публикация

1987-03-16—Подача