Изобретение относится к измерительной технике и может быть использовано при создании приборов со световой шкалой, а такжэ в приборах с механическими индика- торами.

Цель изобретения - упрощение устрой- сгпа.

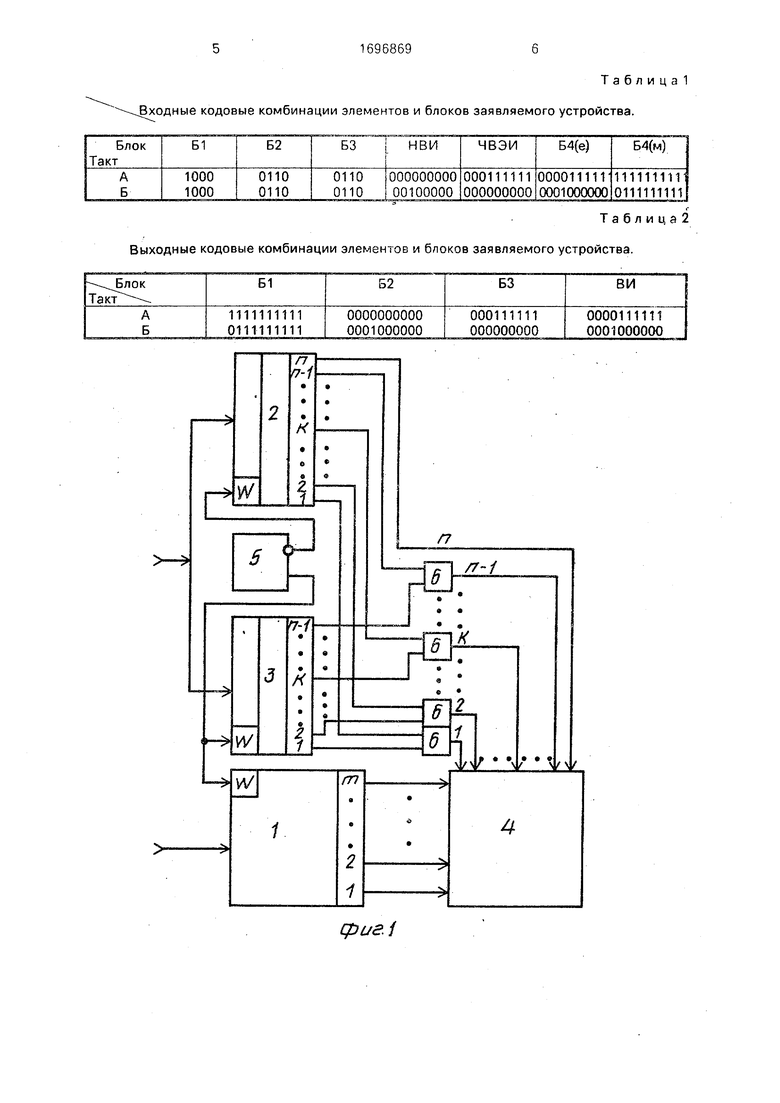

На ,фиг. 1 представлена функциональная схема устройства; на фиг. 2 показан пример реализации блока 1.

Устройство содержит первый, второй и третий блохи 1-3 преобразования кодов, блок 4 регистрации, генератор 5 импульсов, элементы ИЛИ 6, Блок 1 содержит поеобра- зователь 7 кодов и элемент ИЛИ 8

Устройство работает следующим образом. На входы устройства поступает код числа вида NM mN + М. На входы блока 1 поступает код числа младшего разряда М, а на входы блоков 2, 3 - код числа старшего разряда N. Устройство работает в два такта.

Такту А соответствует потенциал логической единицы на прямом выходе генератора 5, а такту Б - потенциал логического нуля. В такт А блок 1 преобразует код числа М в т--разрядную кодовую комбинацию 11...1, где т - количество младших разрядов в блоке 4, Блок 2 трансформирует код числа N в n-рззрядную комбинацию 00...О, а блок 3 - n-1-разрядную кодовую комбинацию ОС..ОИ..1, содержащую N единиц. Стар- шгй бит первой кодовой комбинации поступает на вход старшего разряда блока 4 с номером п, а младшие биты - на первые входы элементов ИЛИ 6. Вторая кодовая комбинация поступает на вторые входы элементов ИЛИ 6, на выходах которых - кодовая комбинация вида 00. .011 ..1 содержашая N единиц. В такт А на входы блока 4 по младшим разрядам подается код 11...1, а по старшим - 00...011...1, содержащий N единиц. В такт В блок 1 преобразует

{ асшй

код числа М в m-разрядную кодовую комбинацию 00,.,Q11...1, содержащую М+1 единиц, блок 2 трансформирует код числа N в п-разрядну О кодовую комбинацию вида 00.,,010.,,О, содержащую здиницу на N+1-ой позиции, а блок 3 - в п-1-разрядную кодовую комбинацию вида ОС...О. Старший бит первой кодовой комбинации пост/лает на вход старшего разряда блока Л г номером п, а младшие биты - на первые Е.ХОДЫ элеаден- то в 6, Вторая кодовая комбинация поступает на вторые входы элементов 6. На выходах элементов 6 формируется п-1-рс13ряднэн кодовая комбинация видя 00 ..010...О, содержащая единицу на N+ 1-oi i пози дим. Сле- довательно, в гакт Е на вхо&ы опока 4 по младшим разрядам подается гп -разрядный шд вида 00,,,011.,,1, содержащий WM зди- чиц, а по старшим разряд;,и - п-разоядный код вида 00.,.010,..0 содержащий единицу ia N+1-ой позиции, В результате зтого ч гакт А возбуждается N полных старших раз- оядов блока 4 из mN элементов, о и такт В - N+1-й неполный старший разряд из М+1 элементов. Част ату импупьсо з тактового re- нератора выбирают таким образом, чтобы оператор воспринимал выходной сигнал в виде непрерывкой кон граем ч о и огмос; 5 ль- но бона линии из mN+M-И озбухды ных элеме -ггов, ч го соответствуй; выводу числа JMM3 + ivS.

Устройство реализовано с И ПОГ ЗОУЗ- мием а качестве основной я-шмепгнои баги микросхем сг;рии К55Б и ссчупано /пя работы с индикатором, выпо иемныгл ь j есно- se 100 светодиодных . Злек.е-ггы были соединены матрицей 10x10.

Работа устройства на г римерс чвод. числа 68 (на индикаторе отображавг-.я ОС значений: от 00 до 99), На влод устрой- стаа поступает код 0110.10СО. Устройство работает в два такта. Тзкгу Л соот в&тс.твует наличие напряжения логическое, ед нмць на прямом выходе генераторе о, а такту 5 -- напряжение логического пуля. Работа уст- ройства описывается картой потенциалов, приведенной в табл. 1, 2, В них использованы следующие обозначения:

ЧВЭИ - четные входы лог и кэских элементов ИЛ И;

НВЭИ - нечетные входы логических элементов ИЛИ;

В И - выходы элементов ИЛИ; Б1 - первый блок преобразования s o- дов

Б2 - второй блок преобразования кедов 53 - третий блок преобразования кодов Б4(с) - входы старших оазрядоз блока 4 Б4(М) - входы младших разрядов блока 4

Б такт А возбуждаются 6 полных старших разрядов .13 60 свегидиодов, «ч в такт Б - седьмой непил- ый старший разряд из 9 светодиодов. Частота импульсов тактового генератора - 100 Гц, В результате оператор наблюдает на шкале светящуюся линию из 69 светодиодов, что соответствует индикации числа 68,

Формула изобретения Устройство для регистрации информации, содержащее три блока преобразования КОДОЕ, блок регистрации, генератор импульсов, информационные входы первого блоке преобразования кодов являются информационными входами мпадших разрядов устройства, информационные входы второго и третьего блоков преобразования ; й1яюгсг, информационными входами старших разоядов устройства, прямой эыхпд генирьгора соединен с управляющие входом nftpt.;o блока преобразованип кодов, выходы которого соединены с инфор- мацитчными входами млг-дших разрядов 5яо,;а регистрации, о т л и дающееся тем, чго, L. целью упрощения, в иего ьведены элементы ИЛИ, управляющий вход третьего блока праобрагованик кодоз соединен с прямым выходом генерс горз импульсоч, инверсный с.ыход которого соединен с управ- ллющим входом второго блока преобразования кодов, выход старшего разряда которого соединен с одним входом старших разрядов блока регистрации, выходы элементов И Л i/I соединены с дружми входами старших разрядов блока регистрации, выходы младших разрядов второго блока преобразования кодов соединены с первыми входами элементов ИЛИ. вторые входы которых соединены с выходами третьего блоча преобразования кодов,

Т а б л и ц а 1 „Входные кодовые комбинации элементов и блоков заявляемого устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для регистрации информации | 1986 |

|

SU1696868A1 |

| Устройство для регистрации информации | 1986 |

|

SU1696870A1 |

| Устройство для регистрации информации | 1986 |

|

SU1696867A1 |

| Устройство для отображения измерительной информации | 1984 |

|

SU1557529A1 |

| СУММИРУЮЩЕЕ УСТРОЙСТВО ПО МОДУЛЮ | 1993 |

|

RU2034328C1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР КОДОВ ФИБОНАЧЧИ | 1993 |

|

RU2047898C1 |

| Преобразователь перемещений в код | 1978 |

|

SU763939A1 |

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код | 1980 |

|

SU943703A1 |

| Генератор символов | 1988 |

|

SU1525724A1 |

| Суммирующее устройство | 1987 |

|

SU1451681A1 |

Изобретение относится к измеритель ной технике и может быть использовано пр л создании приборов со световой шкалой а также s гриборал с механическими индикаторными и регистрирующими устройствами. Изобретение позволяет упростить устройство за счет изменения алгоритма обработки входной информации путем увеличения функциональной нагрузки на блоки преобразования кодов. Устройство содержит три блока преобразователей кодов. блок регистрации, генератор, элементы ИЛИ. Индикация регистрируемой информации происходит в два такта. В начале инди- старшие разряды информации, затем - младшие. Бпагодаря соответственно подобранной частоте генератора индика- иия входной информации представляет собой дпя оператора ряд светящихся линий на матрице индикационных элементов блока регистрации 2 табл. 2 ил.

Выходные кодовые комбинации элементов и блоков заявляемого устройства.

фиа1

Таблица2

x/4 Lf im-/

fcv 70:e3WSSi

Iff. -

f)

1 P I «

:;E W

4,.,.„, f)

г

,77

«4- ;

(Й/5, f

Авторы

Даты

1991-12-07—Публикация

1986-03-25—Подача