Изобретение относится к вычислительной технике и может быть использовано в высокопроизводительных устройствах для обработки множества чисел..

Цель изобретения - сокращение аппаратурных затрат.

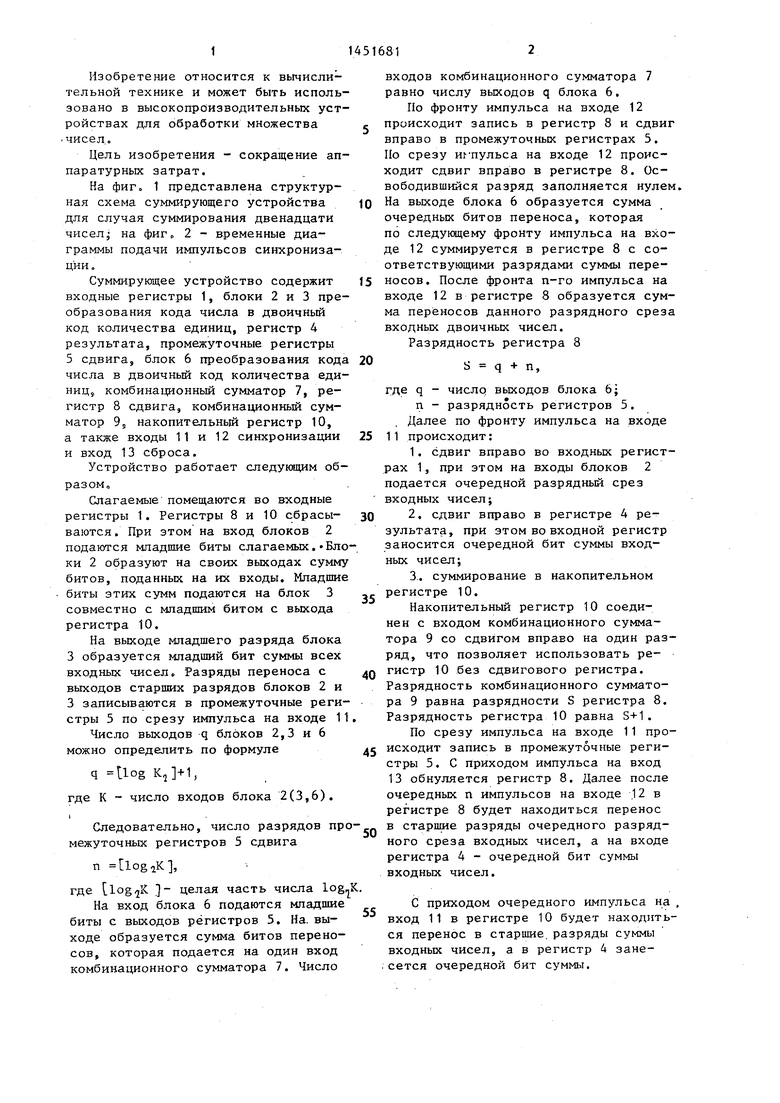

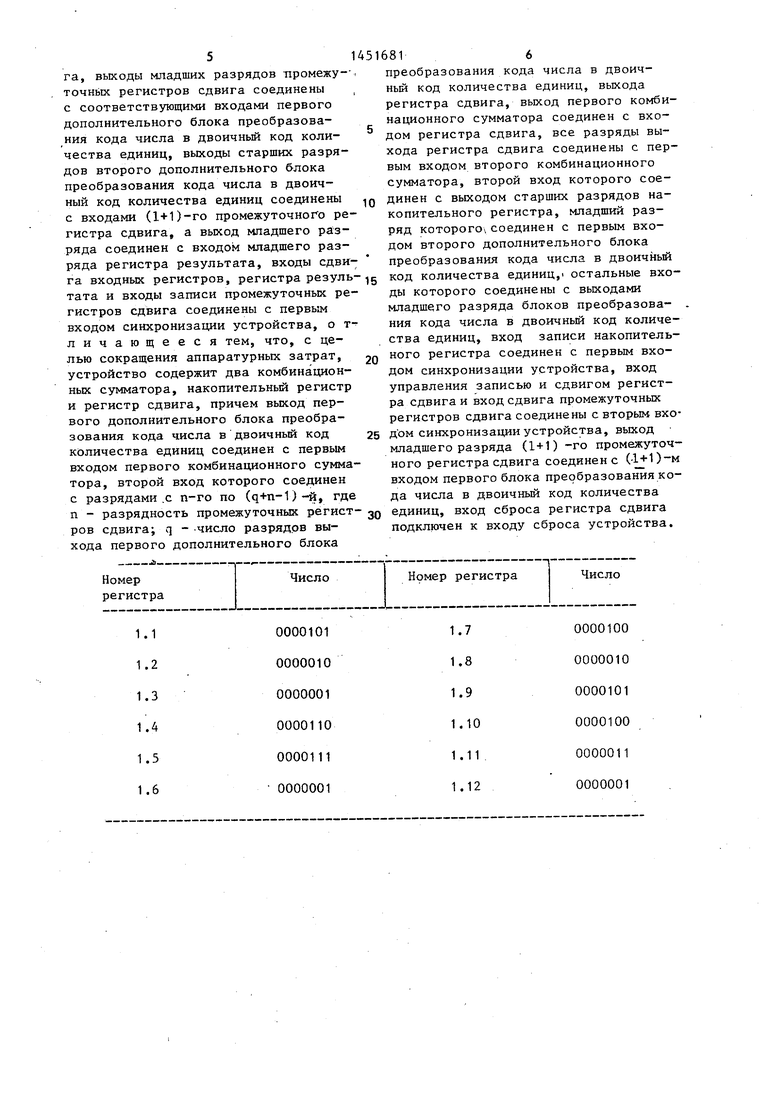

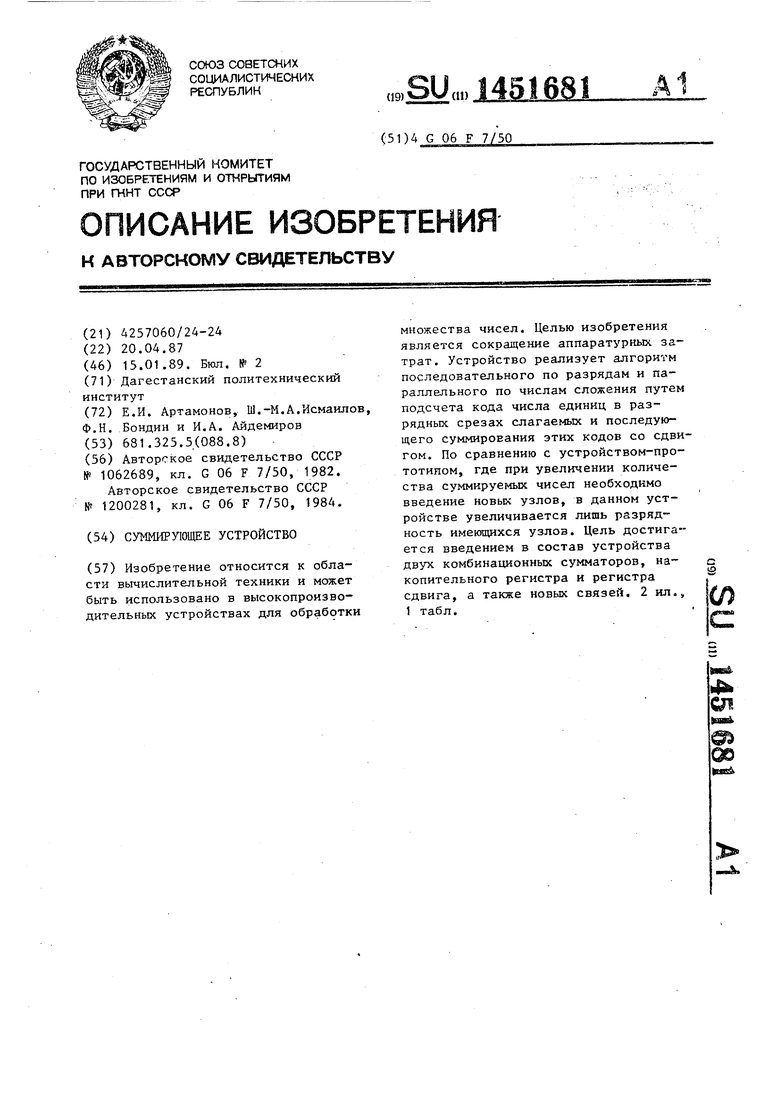

На фиг. 1 представлена структурная схема суммирующего устройства для случая суммирования двенадцати чисел на фиг„ 2 - временные диаграммы подачи импульсов синхронизации .

Суммирующее устройство содержит входные регистры 1, блоки 2 и 3 преобразования кода числа в двоичный код количества единиц, регистр 4 результата, промежуточные регистры 5 сдвига, блок 6 преобразования кода числа в двоичный код количества еди- ниц, комбинационный сумматор 7, регистр 8 сдвига, комбинационный сумматор 9, накопительный регистр 10, а также входы 11 и 12 синхронизации и вход 13 сброса.

Устройство работает следуницим образом.

Слагаемые помещаются во входные регистры 1. Регистры 8 и 10 сбрасы- ваются. При этом на вход блоков 2 подаются младпше биты слагаемых.-Блоки 2 образуют на своих выходах сумму битов, поданных на их входы. Младшие биты этих сумм подаются на блок 3 совместно с мпадшим битом с выхода регистра 10.

На выходе младшего разряда блока 3 образуется младший бит суммы всех входных чисел. Разряды переноса с выходов старших разрядов блоков 2 и 3 записываются в промежуточные регистры 5 по срезу импульса на входе 1

Число выходов q блоков 2,3 и 6 можно определить по формуле

q tlog Kj+1,

где К число входов блока 2(3,6).

1

Следовательно, число разрядов прмежуточных регистров 5 сдвига

п tlogiK,

где log,jK - целая часть числа log

На вход блока 6 подаются мпадшие биты с выходов регистров 5. На. выходе образуется сумма битов переносов, которая подается на один вход комбинационного сумматора 7. Число

0 5

О

0

5

5

входов комбинационного сумматора 7 равно числу выходов q блока 6.

По фронту импульса на входе 12 происходит запись в регистр 8 и сдвиг вправо в промежуточных регистрах 5. По срезу иг пульса на входе 12 происходит сдвиг вправо в регистре 8. Освободившийся разряд заполняется нулем. На выходе блока 6 образуется сумма очередных битов переноса, которая по следукщему фронту импульса на входе 12 суммируется в регистре 8 с соответствующими разрядами суммы переносов. После фронта п-го импульса на входе 12 в регистре 8 образуется сумма переносов данного разрядного среза входных двоичных чисел.

Разрядность регистра 8

S q + п,

где q - число выходов блока 6п - разрядность регистров 5. Далее по фронту импульса на входе 11 происходит:

1.сдвиг вправо во входньк регистрах 1, при этом на входы блоков 2 подается очередной разрядный срез входных чисел;

2.сдвиг вправо в регистре 4 результата, при этом во входной регистр заносится очередной бит суммы входных чисел;

3.. суммирование в накопительном регистре 10.

Накопительный регистр 10 соединен с входом комбинационного сумматора 9 со сдвигом вправо на один разряд, что позволяет использовать регистр 10 без сдвигового регистра. Разрядность комбинационного сумматора 9 равна разрядности S регистра 8. Разрядность регистра 10 равна S+1.

По срезу импульса на входе 11 происходит запись в промежуточные регистры 5. С Приходом импульса на вход 13 обнуляется регистр 8. Далее после очередных п импульсов на входе 12 в регистре 8 будет находиться перенос в старшие разряды очередного разрядного среза входных чисел, а на входе регистра 4 - очередной бит суммы входных чисел.

С приходом очередного импульса на . вход 11 в регистре 10 будет находиться перенос в старшие, разряды суммы входных чисел, а в регистр 4 зане- .сется очередной бит суммы.

После фронта m-ro импульса на входе 1 1 в регистре 4 будет находиться сумма входных чисел.

Таким образом, на вход 11 нужно подать т+1 импульсов, где m - разрядность слагаемых .svHa вход 12 необходимо подавать по п импульсов между каждыми двумя импульсами на входе 11. На вход 13 необходимо подать m импульсов после каждого среза импульса на входе 11.

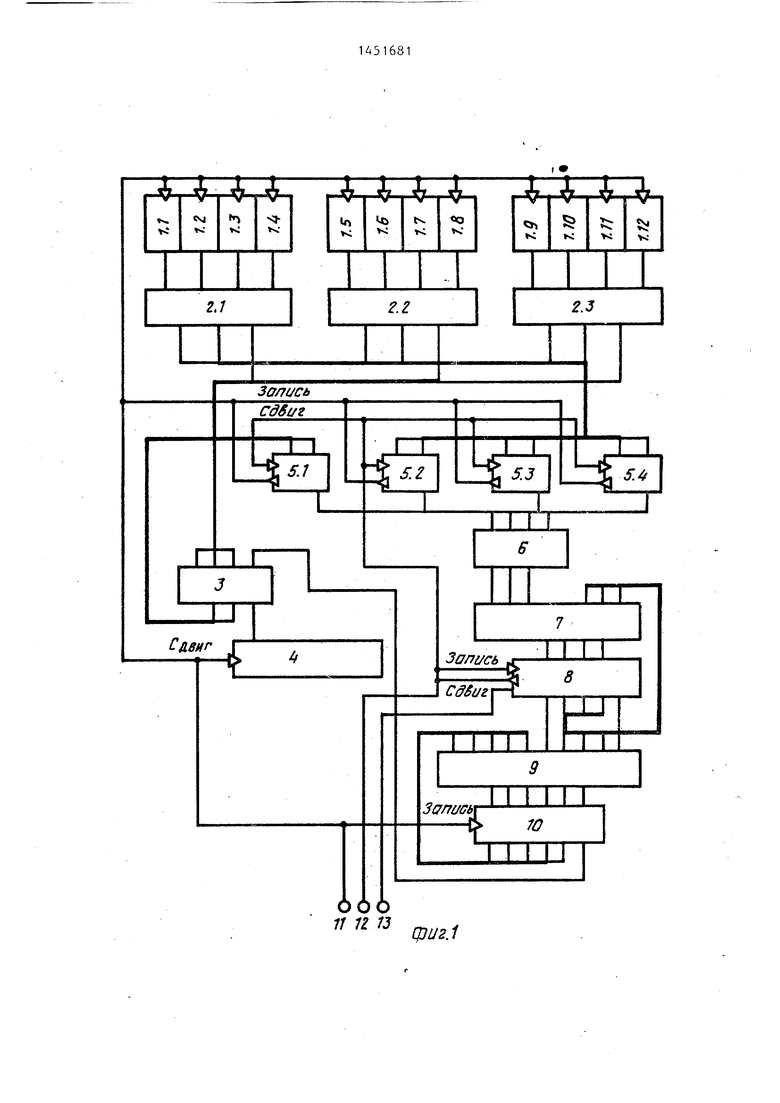

Приме р. Необходимо сложить 12 трехразрядных двоичных чисел.

Слагаемые загружаются в регистры 1 в соответствии с таблицей.

По срезу нулевого импульса на входе 11 происходит запись в регистры 5: Номер регистра Код

5.100

5.201

5.301

5.4 01

На входе блока 6 появляется код 0111, на его выходе - код 011.

По фронту первого импульса на входе 12 происходит суммирование в регистре 8. В рем будет код 00110. Также происходит сдвиг в регистрах 5. На входе блока 6 появляется код 0000, на выходе - код 000.

По срезу первого импульса на входе 12 происходит сдвиг информации в регистре 8. В нем будет код 00011. По фронту второго импульса на входе 12 происходит суммирование в регистре 8.

В нем будет код 00011.

По фронту первого импульса на вхо- де 11 происходит:

1.сдвиг вправо в регистре 4, в нем будет 1 х х х х х х, где х - неопределенный символ;

2.суммирование в -регистре 10, в нем будет код 000011;

3.сдвиг в регистрах 1.

На входах и, соответственно, на выходах блоков 2:

Номер блока

Номер регистра

5.1

5.2

5.3

5.4

На входе блока 6 выходе - код 011.

10

15

25

30

35

Код

01 01 01 00 - код 1110, на

После третьего импульса на входе 12 происходит запись и сдвиг в регистре 8. В нем будет код 00011.

На входе блока 6 будет код 0000, на выходе - код 000. По фронту четвертого импульса на входе 12 в регистре Ъ происходит суммирование, в нем будет 00011, который подается на первый вход сумматора 9, на второй вход подается код 00001. На его выходе - 20 код 000100.

По фронту второго импульса на входе 11 происходит:

1. сдвиг информации в регистре 4, в нем будет 01 х х х х х;

2.запись в регистр 10 кода 000100;

3.сдвиг в регистрах 1.

На входах и выходах блоков 2: Номер блока Код на входе

2.11001

2.21010

2.31100 На

Код на выходе

010

010

010

40

входе регистра 4 будет код 0000, на выходе - код 000.

Продолжая таким образом, после седьмого импульса на входе 11 получим в регистре 4 результата сумму входных слагаемых, т.е. 0101001.

Формула изобретения

2.1 2.2 2.3

Суммирующее устройство, содержащее входные регистры по числу слагаемых, 45 блоки преобразования кода числа в двоичный код количества единиц, промежуточные регистры сдвига, первый и второй дополнительные блоки преобразования кода числа в двоичный

Код на Код на 50 °Д количества единиц,регистр ре- входе выходе зультата, причем входные регистры 0101 010 объединены в 1 групп, выходы млад- 1001 010 ших разрядов входных регистров каж- 0010 001 дои группы соединены с входами соот55 ветствукнцего блока преобразования кода числа в двоичный код количества единиц, выходы старших разрядов которого соединены с входами соответствующего промежуточного регистра сдвиНа входе блока 3 будет код ООП, на выходе - код 010.

По срезу первого импульса на входе 11 происходит запись в регистры 5.

Номер регистра

5.1

5.2

5.3

5.4

На входе блока 6 ыходе - код 011.

Код

01 01 01 00 - код 1110, на

После третьего импульса на входе 12 происходит запись и сдвиг в регистре 8. В нем будет код 00011.

На входе блока 6 будет код 0000, на выходе - код 000. По фронту четвертого импульса на входе 12 в регистре Ъ происходит суммирование, в нем будет 00011, который подается на первый вход сумматора 9, на второй вход подается код 00001. На его выходе - код 000100.

По фронту второго импульса на входе 11 происходит:

1. сдвиг информации в регистре 4, в нем будет 01 х х х х х;

2.запись в регистр 10 кода 000100;

3.сдвиг в регистрах 1.

На входах и выходах блоков 2: Номер блока Код на входе

2.11001

2.21010

2.31100 На

Код на выходе

010

010

010

входе регистра 4 будет код 0000, на выходе - код 000.

Продолжая таким образом, после седьмого импульса на входе 11 получим в регистре 4 результата сумму входных слагаемых, т.е. 0101001.

40

Формула изобретения

га, выходы младших разрядов иромежу- точньк регистров сдвига соединены с соответствующими входами первого дополнительного блока преобразова- ния кода числа в двоичный код количества единиц, выходы старших разрядов второго дополнительного блока преобразования кода числа в двоичный код количества единиц соединены Q с входами (1+1)-го промежуточного регистра сдвига, а выход младшего ра:з- ряда соединен с входом младшего разряда регистра результата, входы сдвига входных регистров, регистра резуль-,5 код количества единиц,, остальные вхо- тата и входы записи промежуточных ре- ды которого соединены с вькодами

преобразования кода числа в двоичный код количества единиц, выхода регистра сдвига, выход первого комбинационного сумматора соединен с входом регистра сдвига, все разряды выхода регистра сдвига соединены с первым входом второго комбинационного сумматора, второй вход которого соединен с выходом старших разрядов накопительного регистра, младший разряд которого соединен с первым входом второго дополнительного блока преобразования кода числа в двоичный

гистров сдвига соединены с первьм входом синхронизации устройства, о т- личающееся тем, что, с целью сокращения аппаратурных затрат, устройство содержит два комбинационных сумматора, накопительньй регистр и регистр сдвига, причем выход первого дополнительного блока преобразования кода числа в двоичный код количества единиц соединен с первым входом первого комбинационного сумматора, второй вход которого соединен с разрядами .с п-го по (q+n-1)-и, где

20

младшего разряда блоков преобразова- ния кода числа в двоичный код количества единиц, вход записи накопительного регистра соединен с первым входом синхронизации устройства, вход управления записью и сдвигом регистра сдвига и вход сдвига промежуточных регистров сдвига соединены с вторым вхо- 25 дом синхронизации устройства, выход младшего разряда (1+1) -го промежуточного регистра сдвига соединен с (-1+1 )-м входом первого блока преобразования кода числа в двоичньш код количества

п - разрядность промежуточных регист- зо единиц, вход сброса регистра сдвига ров сдвига; q --число разрядов вы- подключен к входу сброса устройства, хода первого дополнительного блока

код количества единиц,, остальные вхо- ды которого соединены с вькодами

преобразования кода числа в двоичный код количества единиц, выхода регистра сдвига, выход первого комбинационного сумматора соединен с входом регистра сдвига, все разряды выхода регистра сдвига соединены с первым входом второго комбинационного сумматора, второй вход которого соединен с выходом старших разрядов накопительного регистра, младший разряд которого соединен с первым входом второго дополнительного блока преобразования кода числа в двоичный

код количества единиц,, остальные вхо- ды которого соединены с вькодами

младшего разряда блоков преобразова- . ния кода числа в двоичный код количества единиц, вход записи накопительного регистра соединен с первым входом синхронизации устройства, вход управления записью и сдвигом регистра сдвига и вход сдвига промежуточных регистров сдвига соединены с вторым вхо- дом синхронизации устройства, выход младшего разряда (1+1) -го промежуточного регистра сдвига соединен с (-1+1 )-м входом первого блока преобразования кода числа в двоичньш код количества

;з ; :; :;5гт5; г; ж

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения среднего арифметического значения | 1989 |

|

SU1658169A1 |

| Устройство для поворота вектора | 1983 |

|

SU1132285A1 |

| Коррелятор | 1986 |

|

SU1339584A1 |

| Преобразователь двоично-К-ичного кода в двоичный код | 1983 |

|

SU1126946A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ОСТАТКА ПО МОДУЛЮ ОТ ЧИСЛА | 1996 |

|

RU2110147C1 |

| Цифровое измерительное устройство для обработки сигналов частотных датчиков | 1989 |

|

SU1659891A1 |

| Преобразователь позиционного кода с одним основанием в позиционный код с другим основанием | 1977 |

|

SU734667A1 |

| Преобразователь кодов | 1978 |

|

SU744548A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ В КОДЕ "1 ИЗ 4" | 2003 |

|

RU2251144C1 |

| Преобразователь двоичного кода в двоично-десятичный | 1984 |

|

SU1280702A1 |

Изобретение относится к области вычислительной техники и может быть использовано в высокопроизводительных устройствах для обработки множества чисел. Целью изобретения является сокращение аппаратурных затрат. Устройство реализует алгоритм последовательного по разрядам и параллельного по числам сложения путем подсчета кода числа единиц в разрядных срезах слагаемых и последующего суммирования этих кодов со сдвигом. По сравнению с устройством-прототипом, где при увеличении количества суммируемых чисел необходимо введение новых узлов, в данном устройстве увеличивается лишь разрядность имеющихся узлов. Цель достигается введением в состав устройства двух комбинационных сумматоров, накопительного регистра и регистра сдвига, а также новых связей. 2 ил., 1 табл. lO (Л

«SJ

v:

4h

хГ

0

золись cdSuz

tS

Cusur

нГ

660

7/ П 7J

bv

rc

«о

:

: ь:

к

X

SiJ

х

г. г

5

пг

Ш

5

п

s.

гтгг

Заг7ась

I i М I I

7О

1 I I М

фиг.1

| Суммирующее устройство | 1982 |

|

SU1062689A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для суммирования М чисел | 1984 |

|

SU1200281A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-01-15—Публикация

1987-04-20—Подача