Изобретение относится к вычислительной технике и может быть использовано для сопряжения с вычислительными устройствами, функционирующих в системе остаточных классов (СОК), а также в технике связи для передачи информации кодами СОК.

Известно устройство преобразования двоичного кода в код СОК, содержащее входной регистр, блок умножения на два по соответствующему модулю, коммутатор, входной регистр, промежуточный регистр, группу логических элементов [1]

Недостатки этого устройства: ограниченность функциональных возможностей и небольшое быстродействие при имеющемся объеме оборудования.

Наиболее близким к предлагаемому является суммирующее устройство по модулю, содержащее суммирующий блок, регистр, элемент И, счетчик, постоянный запоминающий блок (ПЗБ), причем выход суммирующего блока соединен с первым входом элемента И, второй вход которого соединен с входом счетчика и является тактовым входом устройства, а выход соединен со входом записи регистра, выходы которого соединены с младшими входами ПЗБ и являются выходами устройства, выходы счетчика соединены со старшими входами ПЗБ, выходы которого соединены с входами регистра [2]

Недостатком этого устройства является большие аппаратурные затраты.

Целью изобретения является уменьшение аппаратурных затрат при сложении n-разрядных N двоичных чисел по соответствующему модулю.

Поставленная цель достигается тем, что в суммирующее устройство по модулю, содержащее первый постоянный запоминающий блок, введены второй постоянный запоминающий блок, группа элементов задержки, группа входных регистров, входы синхронизации которых соединены с тактовыми входами элементов задержки и с входом синхронизации устройства, а выходы соединены с входами второго постоянного запоминающего блока, выходы которого соединены со старшими входами первого постоянного запоминающего блока, младшие входы которого соединены с выходами элементов задержки, входы которых соединены с информационными выходами первого постоянного запоминающего блока, являющимися выходами устройства.

Сопоставительный анализ с прототипом показывает, что заявляемое устройство отличается наличием второго постоянного запоминающего блока, группы элементов задержки, группы входных регистров и новыми связями между элементами.

Таким образом, заявляемое устройство соответствует критерию изобретения "Новизна".

Сравнение заявляемого устройства с другими техническими решениями показывает, что блоки, входящие в структуру устройства известны, но связи между ними создают новые свойства, обеспечивающие сокращение аппаратурных затрат устройства за счет заполнения ячеек ПЗБ устройства кодовыми комбинациями, отличными от кодовых комбинаций в ячейках ПЗБ прототипа, и введения других блоков, что позволяет сделать вывод о соответствии технического решения критерию "Существенные отличия".

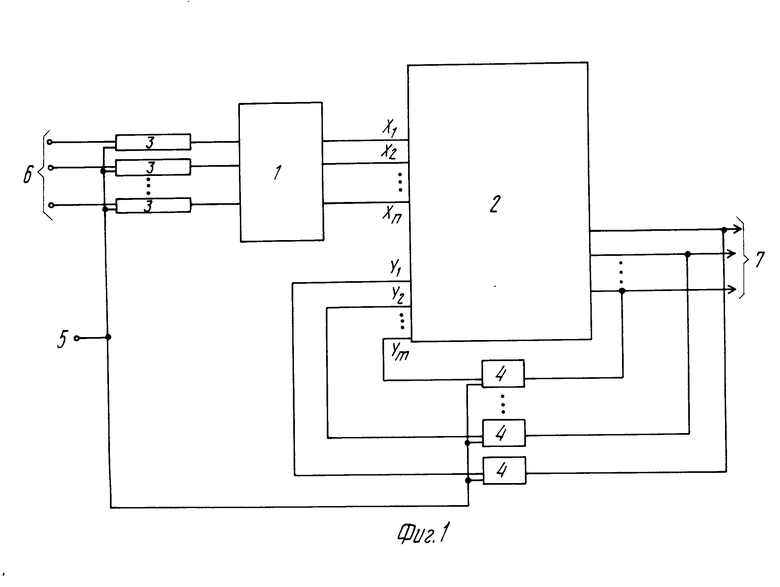

На фиг.1 представлена структурная схема предлагаемого устройства.

Устройство содержит постоянные запоминающие блоки (ПЗБ) 1,2, группу входных регистров 3, группу элементов задержки 4, управляющий вход синхронизации 5, информационные входы 6 и выходы 7.

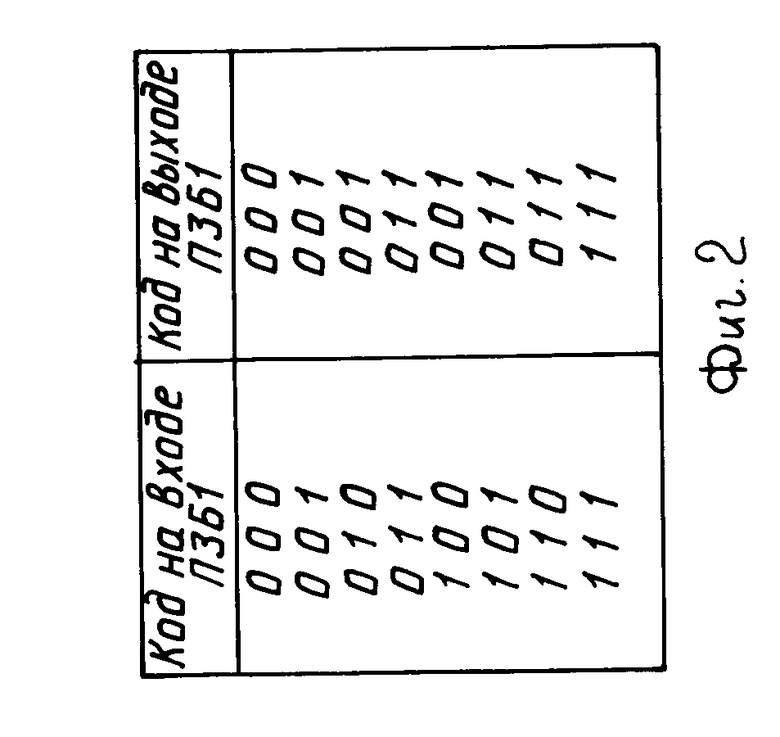

На фиг.2 изображены адреса и записанные по этим адресам слова для ПЗБ 1 при сложении трех n-разрядных двоичных чисел. Блок располагает единицы входного слова подряд в младших разрядах.

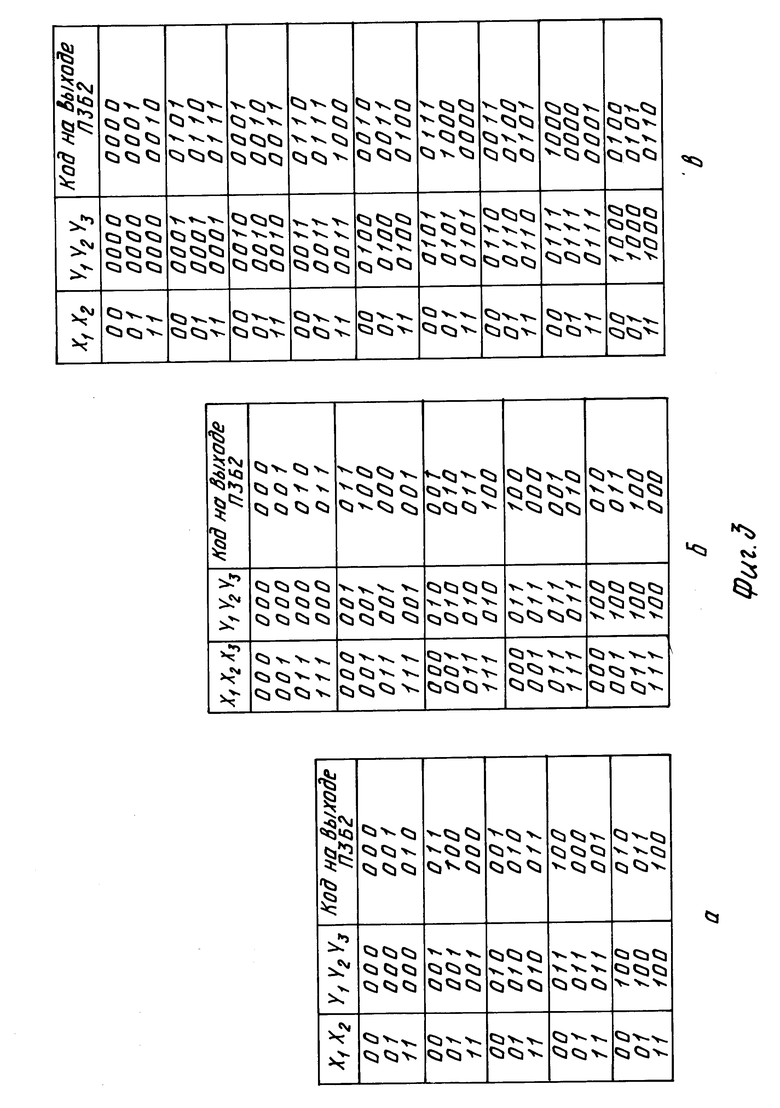

На фиг. 3 показаны адреса и содержащиеся по этим адресам слова ПЗБ 2 в удобной для рассмотрения последовательности: на фиг. 3,а и 3,б при сложении по модулю пять соответственно для двух и трех n-разрядных двоичных чисел; на фиг.3,в при сложении по модулю девять.

Работает устpойство следующим образом. Во входные регистры 3 записываются слагаемые. После прихода первого импульса на вход синхронизации 5 на входы ПЗБ 1 поступают нулевые разряды слагаемых. Преобразованный в ПЗБ 1 код поступает на входы Х1-Хn ПЗБ 2. В том же такте содержимое с выходов элементов задержки 4 поступает на входы Y1-Yn ПЗБ 2. По этому же такту код с выходов ПЗБ 2 поступает на входы элементов задержки. По истечении определенного числа тактов на выходе получается результат суммирования в параллельном коде.

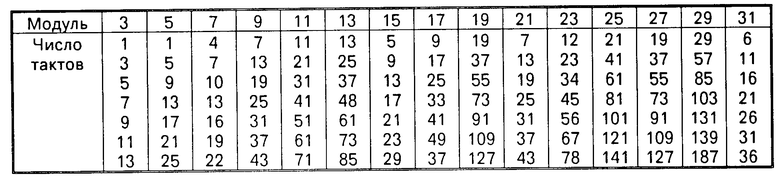

Количество тактов, которые нужно подать для получения результата, зависит от разрядности слагаемых и от модуля, по которому производится сложению двоичных чисел.

Число тактов для различных модулей при различной разрядности слагаемых указано в таблице.

Как видно из таблицы, можно выделить модули с одинаковым числом тактов, например модули 3,5,7,9,13,21 имеют для слагаемых с разрядностью меньше и равной 13, одинаковое число тактов, равное 13.

Число слов ПЗБ 2 определяется по формуле:

K1= Pi (N + 1), где Ki количество слоев ПЗБ 2 для модуля рi;

Рi модуль по которому производится сложение двоичных n-разрядных чисел;

N количество одновременно суммируемых слагаемых в двоичной системе счисления.

Число адресных входов ПЗБ 2 определяется по формуле:

Zi log Pi [ + N,

Zi число адресных входов ПЗБ 2 для модуля рi.

Число выходов ПЗБ2 определяется из равенства

Mi log2 P1[ где Мi число выходов ПЗБ 2 для модуля рi.

Рассмотрим работу устройства для случая суммирования трех операндов по модулю пять. Слагаемые: 1.1101, 2.1001, 3,1110.

В течение первого импульса на входы ПЗБ 1 (фиг.2) поступают нулевые разряды слагаемых, т. е. 110. По указанному адресу с ПЗБ 1 считывается слово 011, которое поступает на входы Х ПЗБ 2 (фиг.3,б). В том же такте с выхода элементов задержки 4, на входы Y ПЗБ 2 поступает слово 000,в результате на входах ПЗБ 2 будет адрес 011000, по указанному адресу с ПЗБ 2 в том же такте считывается слово 010, которое поступает на входы элементов задержки.

В течение второго импульса на входы ПЗБ 1 подаются первые разряды слагаемых 001, по указанному адресу считывается слово 001, которое поступает на входы Х ПЗБ 2. На входы Y через элементы задержки поступает слово 010. По адресу 001010 из ПЗБ 2 считывается слово 010.

В течение третьего импульса на входы ПЗБ 1 подаются вторые разряды слагаемых 101, по указанному адресу считывается слово 011. На входы Х и Y ПЗБ 2 подается кодовая комбинация 011010. По этому адресу считывается слово 011.

В течение четвертого импульса на входы ПЗБ 1 подаются третьи разряды слагаемых 111, по указанному адресу считывается слово 111, которое поступает на входы Х ПЗБ 2. На вход Y через элементы задержки поступает слово 011. По адресу 111011 из ПЗБ 2 считывается слово 010.

Согласно таблице, при суммировании по модулю пять нужно подать пять импульсов для слагаемых, у которых разрядность меньше или равна пяти.

В течение пятого импульса на входы ПЗБ 1 подается слово 000, по указанному адресу из ПЗБ 1 считывается слово 000. На входы Х и Y ПЗБ 2 подается код 000010. По указанному адресу из ПЗБ 2 считывается слово 001, которое и является результатом.

| название | год | авторы | номер документа |

|---|---|---|---|

| Ассоциативное суммирующее устройство @ -разрядных двоичных и двоично-десятичных чисел | 1984 |

|

SU1233134A1 |

| Устройство для суммирования @ -разрядных чисел | 1985 |

|

SU1273917A1 |

| Суммирующее устройство | 1990 |

|

SU1784970A1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР КОДОВ ФИБОНАЧЧИ | 1993 |

|

RU2047898C1 |

| Суммирующее устройство | 1991 |

|

SU1807480A1 |

| Ассоциативное арифметическое устройство | 1986 |

|

SU1363187A1 |

| Суммирующее устройство | 1991 |

|

SU1807479A1 |

| Ассоциативное суммирующее устройство | 1986 |

|

SU1424011A1 |

| Вычислительное устройство | 1990 |

|

SU1784969A1 |

| Суммирующее устройство | 1990 |

|

SU1775722A1 |

Изобретение относится к вычислительной технике и может быть использовано для сопряжения с вычислительными устройствами, функционирующими в системе остаточных классов (СОК), а также в технике связи для передачи информации кодами СОК. Целью изобретения является уменьшение аппаратурных затрат при сложении n-разрядных N двоичных чисел по соответствующему модулю. Устройство содержит постоянные запоминающие блоки, группу входных регистров, группу элементов задержки, управляющий вход синхронизации, информационные входы и выходы. 3 ил., 1 табл.

СУММИРУЮЩЕЕ УСТРОЙСТВО ПО МОДУЛЮ, содержащее первый постоянный запоминающий блок, отличающееся тем, что оно содержит второй постоянный запоминающий блок, группу элементов задержки, группу входных регистров, входы синхронизации которых соединены с тактовыми входами элементов задержки и с входом синхронизации устройства, а выходы с входами второго постоянного запоминающего блока, выходы которого соединены со старшими входами первого постоянного запоминающего блока, младшие входы которого соединены с выходами элементов задержки, входы которых соединены с информационными выходами первого постоянного запоминающего блока, являющимися выходами устройства.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Суммирующее устройство | 1990 |

|

SU1714586A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1995-04-30—Публикация

1993-03-01—Подача