1

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении двоично-десятичных преобразователей угловых величин.

Известны преобразователи двоичного кода в двоично-десятичный код, содержащие сдвиговый регистр и группу блоков коррекции, построенных на основе сумматоров tl и Г21.

Недостаток известных преобразователей состоит в невозможности преобразования угловых величин.

Наиболее близким решением к изобретению по технической сущности и схемному построению является преобразователь двоичного кода в двоичнодесятично-шестидесятиричный код градусов, минут и секунд, содержащий распределитель импульсов, первый регистр, десятичный и шестиричный кор. ректоры D.

Недостаток данного преобразователя состоит в относительно большом

объеме аппаратуры с использованием двоично-десятичных сумматоров.

Цепью изобретения является упрощение преобразователя.

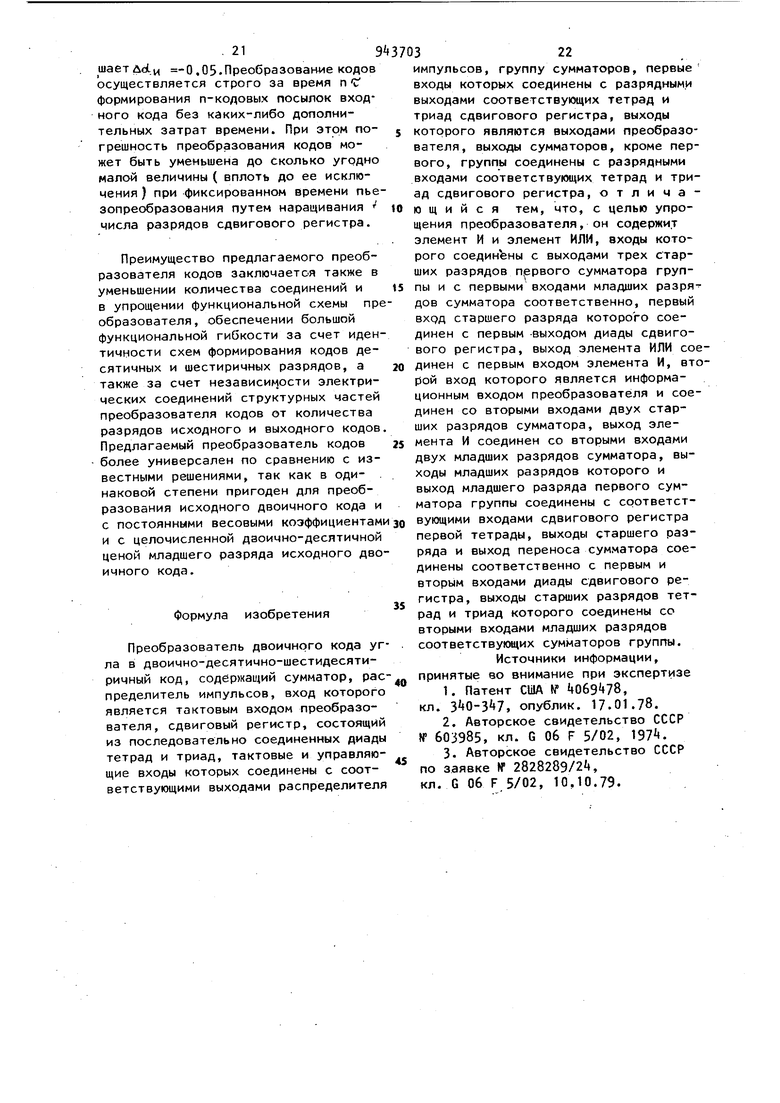

Поставленная цель достигается тем, что преобразователь двоичного кода- угла в двоично-десятично-шестидесятиричный код, содержащий сумматор, распределитель импульсов, вход которого является тактовым

to входом преобразователя, сдвиговый регистр, состоящий из,последовательно соединенных диады, тетрад и триад, тактовые и управляющие входы которых соединены с соответствую15щими выходами распределителя импульсов, группу сумматоров, первые входы которых соединены с разрядными выходами соответствующих тетрад и триад сдвигового регистра, выходы

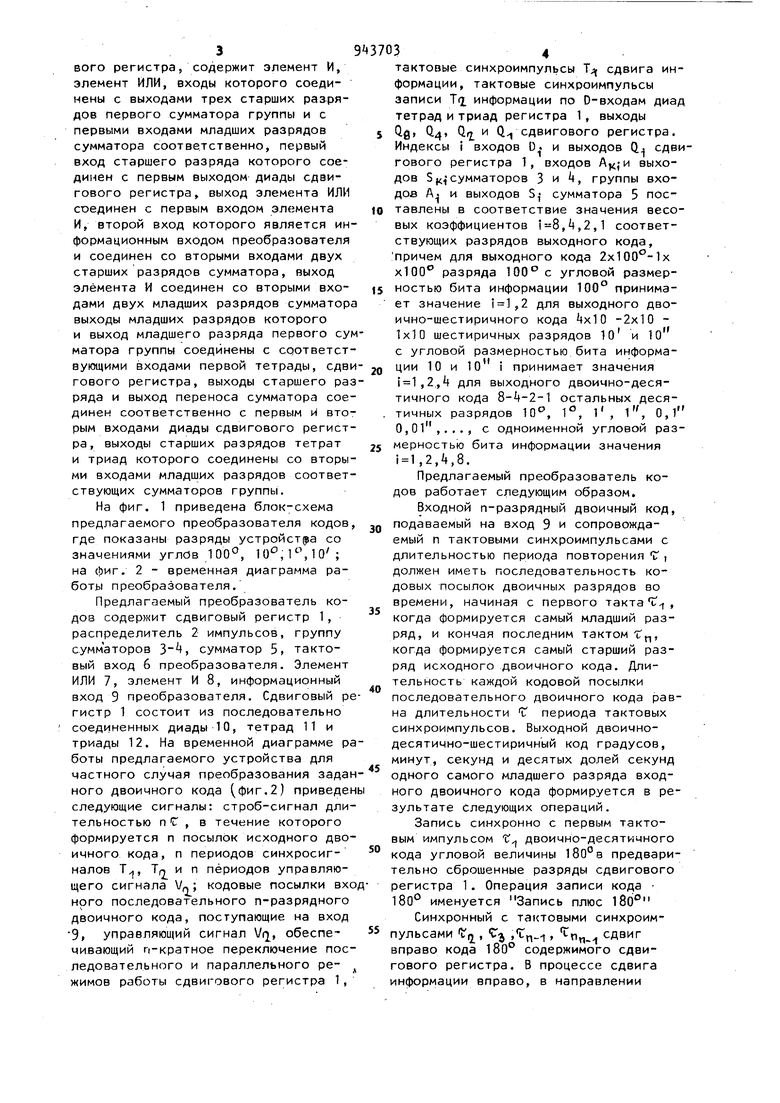

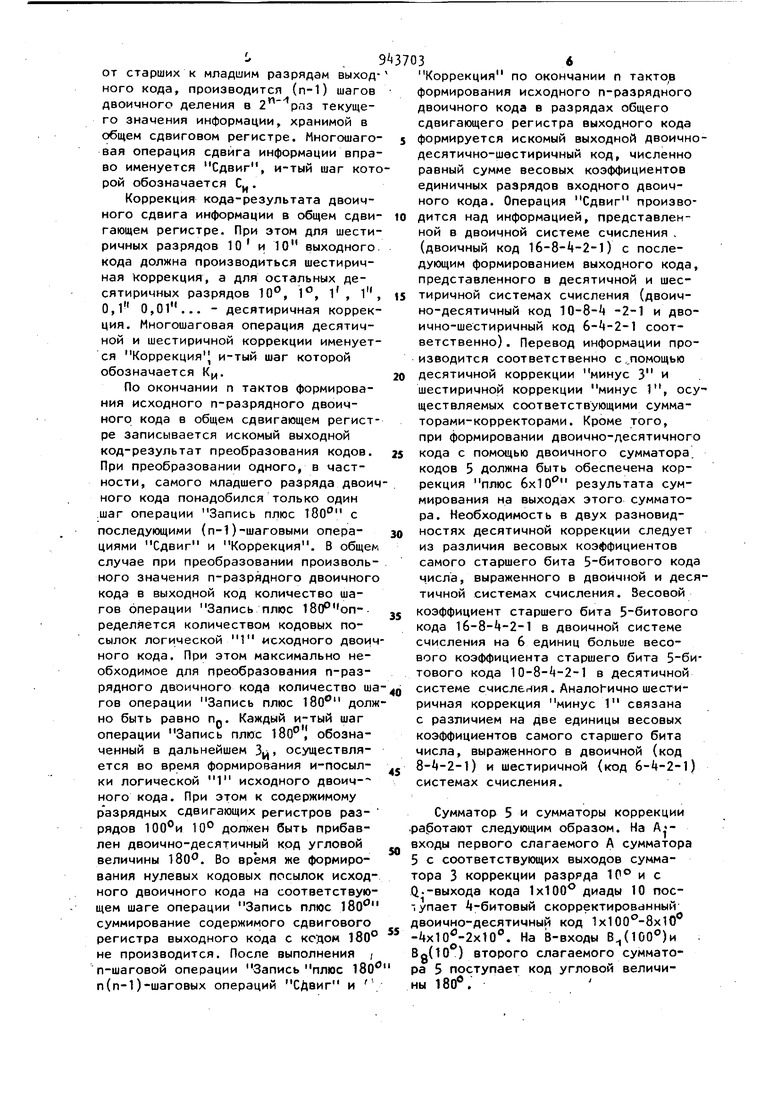

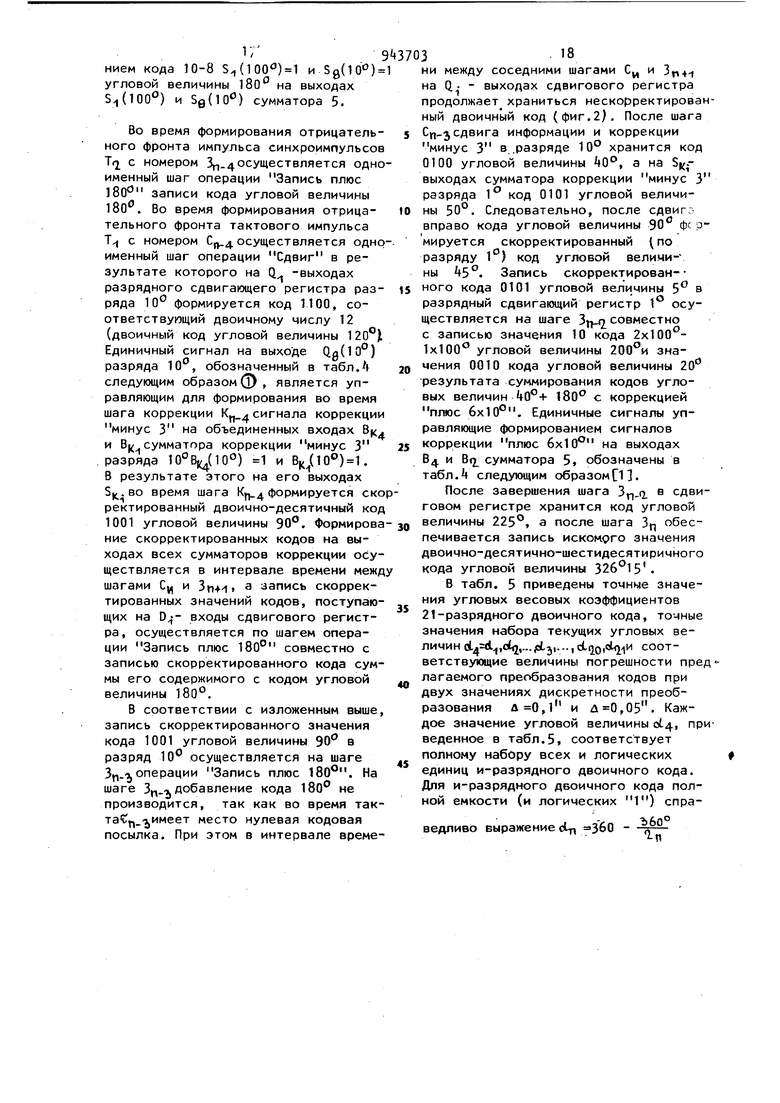

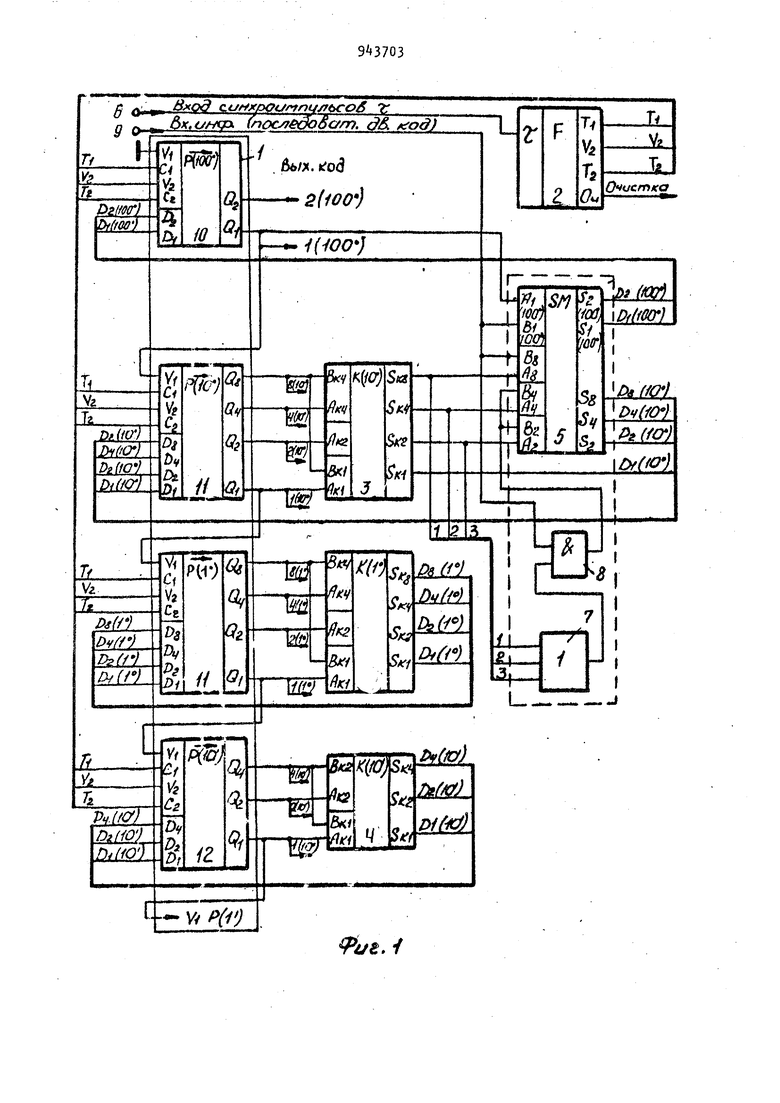

20 которого являются выходами прэобразователя, выходы сумматоров, кроме первого, гpynnы JCoeдинeны с разрядными входами тетрад и Уриад сдвигового регистра, содержит элемент И, элемент ИЛИ, входы которого соединены с выходами трех старших разрядов первого сумматора группы и с первыми входами младших разрядов сумматора соответственно, первый вход старшего разряда которого соединен с первым выходом диады сдвигового регистра, выход элемента ИЛИ соединен с первым входом элемента И, второй вход которого является информационным входом преобразователя и соединен со вторыми входами двух старших разрядов сумматора, выход элемента И соединен со вторыми входами двух младших разрядов сумматора выходы младших разрядов которого и выход младшего разряда первого сум матора группы соединены с соответствующими входами первой тетрады, сдви гового регистра, выходы старшего раз ряда и выход переноса сумматора соединен соответственно с первым И вторым входами диады сдвигового регистра, выходы старших разрядов тетрат и триад которого соединены со вторыми входами младших разрядов соответствующих сумматоров группы. На фиг. 1 приведена блок-схема предлагаемого преобразователя кодов где показаны разряды устройства со значениями углов 100°, 10,1.10; на фиг. 2 - временная диаграмма работы преобразователя. Предлагаемый преобразователь кодов содержит сдвиговый регистр 1 , распределитель 2 импульсов, группу сумматоров 3, сумматор 5, тактовый вход 6 преобразователя. Элемент ИЛИ 7, элемент И 8, информационный вход 9 преобразователя. Сдвиговый ре гистр 1 состоит из последовательно соединенных диады 10, тетрад 11 и триады 12. На временной диаграмме работы предлагаемого устройства для частного случая преобразования заданного двоичного кода (фиг.2) приведены следующие сигналы: строб-сигнал длительностью п С , в течение которого формируется п посылок исходного двоичного кода, п периодов синхроси налов Т, TO и п периодов управляющего сигнала V.; кодовые посылки входнрго последовательного п-разрядного двоичного кода, поступающие на вход 9, управляющий сигнал VQ, обеспе-55 чивающий п-кратное переключение последоватедьного и параллельного режимов работы сдвигового регистра 1, тактовые синхроимпульсы Jj сдвига информации, тактовые синхроимпульсы записи информации по О-входам диад тетрад и триад регистра 1, выходы Qfl 0-4 1 Q сдвигового регистра. Индексы i входов D. и выходов (J, сдвигового регистра 1, входов Ац;и выходов 5ц сумма т о ров 3 и 4, группы входов А и выходов S{ сумматора 5 поставлены в соответствие значения весовых коэффициентов ,,2,1 соответствующих разрядов выходного кода, причем для выходного кода 2х100 -1х разряда 100 с угловой размерностью бита информации 100 принимает значение ,2 для выходного двоично-шестиричного кода -2x10 1x10 шестиричных разрядов 10 и 10 с угловой размерностью бита информа(I ции 10 и 10 i принимает значения ,2,,t для выходного двоично-десятичного кода остальных десятичных разрядов 10, 1°, 1, 1, 0,1 0,01,,,., с одноименной угловой размерностью бита информации значения ,2,k,8. Предлагаемый преобразователь кодов работает следующим образом. Входной п-разрядный двоичный код, подаваемый на вход 9 и сопровождаемый п тактовыми синхроимпульсами с длительностью периода повторения Т, должен иметь последовательность кодовых посылок двоичных разрядов во времени, начиная с первого тактаt., , когда формируется самый младший разряд, и кончая последним тактом tf, когда формируется самый старший разряд исходного двоичного кода. Длительность каждой кодовой посылки последовательного двоичного кода равна длительности Т периода тактовых синхроимпульсов. Выходной двоичнодесятично-шестиричный код градусов, минут, секунд и десятых долей секунд одного самого младшего разряда входнего двоичного кода формируется в результате следующих операций. Запись синхронно с первым тактовым импульсом г двоично-десятичного кода угловой величины 180°в предварительно сброшенные разряды сдвигового регистра 1. Операция записи кода 180° именуется Запись плюс 180° Синхронный с тактовыми синхроим пульсами Q , fj ,, tfi сдвиг вправо кода 180° содержимого сдвигового регистра. В процессе сдвига информации вправо, в направлении от старших к младшим разрядам выходного кода, производится (п-1) шагов двоичного деления в текущего значения информации, хранимой в общем сдвиговом регистре. Многошаговая операция сдвига информации вправо именуется Сдвиг, и-тый шаг кото рой обозначается С... Коррекция кода-результата двоичного сдвига информации в общем сдвигающем регистре. При этом для шестиричных разрядов 10 и 10 выходного кода должна производиться шестиричная коррекция, а для остальных десятиричных разрядов 10, 1°, 1, 1 0,1 0,01... - десятиричная коррекция. Многошаговая операция десятичной и шестиричной коррекции именуется Коррекция и-тый шаг которой обозначается К,. По окончании п тактов формирования исходного п-разрядного двоичного кода в общем сдвигающем регистре записывается искомый выходной код-результат преобразования кодов. При преобразовании одного, в частности, самого младшего разряда двоич ного кода понадобился только один .шаг операции Запись плюс 180 с последующими {п-1)-шаговыми операциями Сдвиг и Коррекция. В общем случае при преобразовании произвольного значения п-разрядного двоичного кода в выходной код количество шагов операции Запись плюс 18(Я определяется количеством кодовых посылок логической 1 исходного двоич ного кода. При этом максимально необходимое для преобразования п-разрядного двоичного кода количество ша гов операции Запись плюс 180 долж но быть равно Пр. Каждый и-тый шаг операции Запись плюс 180) обозначенныи в дальнейшем 3,, осуществляется во время формирования и-посылки логической 1 исходного двоич- ного кода. При этом к содержимому разрядных сдвигающих регистров разрядов 100°и 10° должен быть прибавлен двоично-десятичный код угловой величины . Во время же формирования нулевых кодовых посылок исходного двоичного кода на соответствующем шаге операции Запись плюс суммирование содержимого сдвигового регистра выходного кода с ксдом 180° не производится. После выполнения / п-шаговой операции Запись плюс 180 п(п-1)-шаговых операций СДвиг и Коррекция по окончании п такто,в формирования исходного п-разрядного двоичного кода в разрядах общего сдвигающего регистра выходного кода формируется искомый выходной двоичнодесятично-шестиричный код, численно равный сумме весовых коэффициентов единичных разрядов входного двоичного кода. Операция Сдвиг производится над информацией, представленной в двоичной системе счисления , (двоичный код 1б-8-4-2-) с последующим формированием выходного кода, представленного в десятичной и шестиричной системах счисления (двоично-десятичный код 1Q-8-4 -2-1 и двоично-шестиричный код соответственно) . Перевод информации производится соответственно с,помощью десятичной коррекции минус 3 и шестиричной коррекции минус 1, осуществляемых соответствующими сумматорами-корректорами. Кроме того, при формировании двоично-десятичного кода с помощью двоичного сумматора, кодов 5 должна быть обеспечена коррекция плюс 6x10 результата суммирования на выходах этого сумматора. Необходимость в двух разновидностях десятичной коррекции следует из различия весовых коэффициентов самого старшего бита 5-битового кода ч.исла, выраженного в двоичной и десятичной системах счисления. Весовой коэффициент старшего бита 5 битового кода 16-8-А-2-1 в двоичной системе счисления на 6 единиц больше весового коэффициента старшего бита 5-битового кода 10-8- -2-1 в десятичной системе счисления. Aнaлo ичнo шестиричная коррекция минус 1 связана с различием на две единицы весовых коэффициентов самого старшего бита числа, выраженного в двоичной (код 8-/J-2-1) и шестиричной (код 6-4-2-1) системах счисления. Сумматор 5 и сумматоры коррекции аботают следующим образом. На А«ходы первого слагаемого А сумматора с соответствующих выходов суммаора 3 коррекции разряда 10° и с .-выхода кода 1x100 диады 10 посупает 4-битовый скорректированный воично-десятичный код 1x100 -8x10 4x10 -2x10. На В-входы В(100°)и л(10°) второго слагаемого сумматоа 5 поступает код угловой величиы 180.

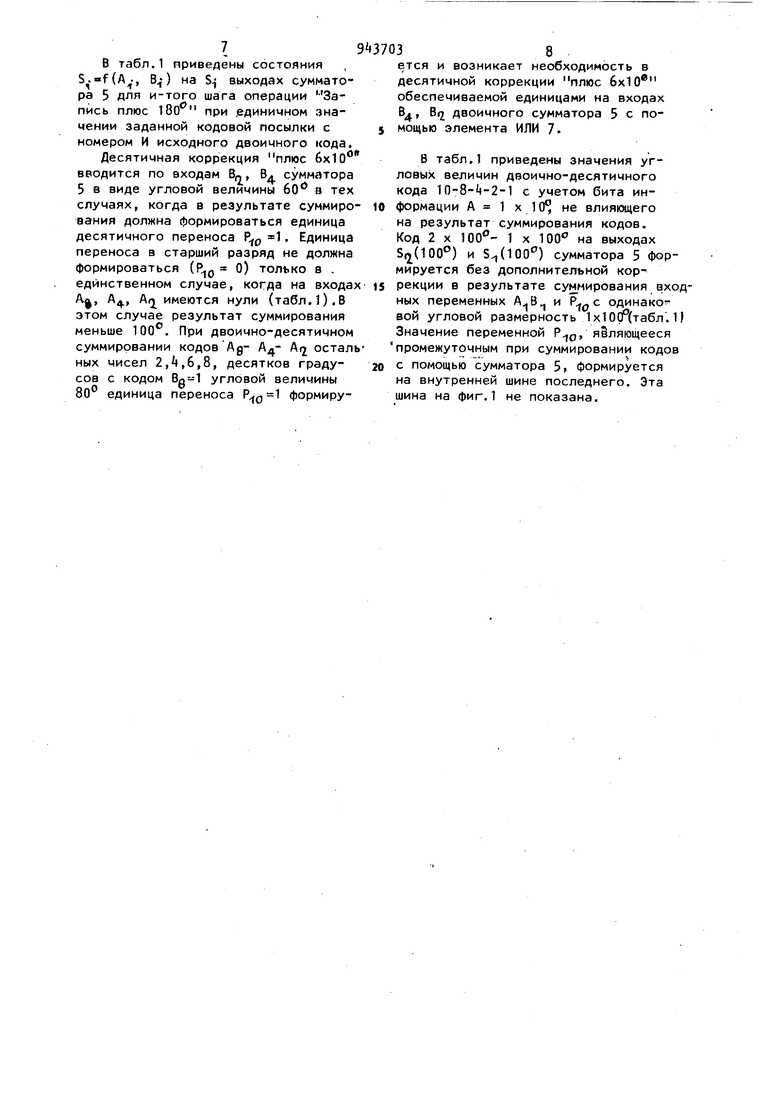

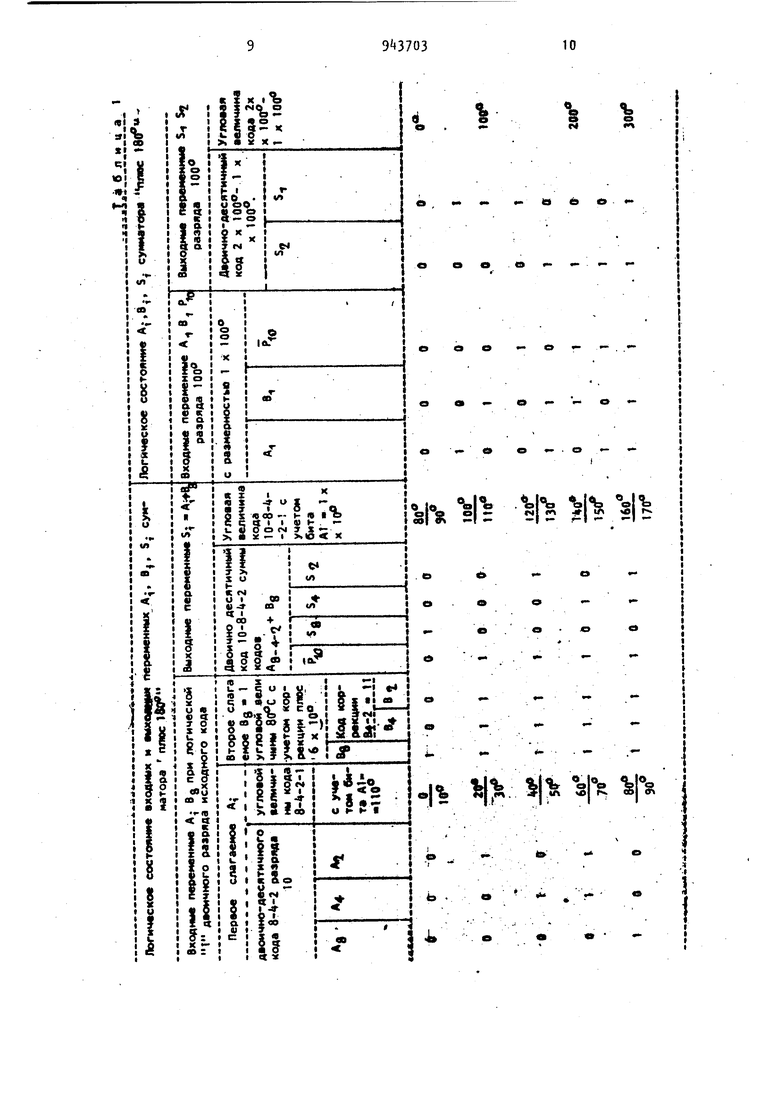

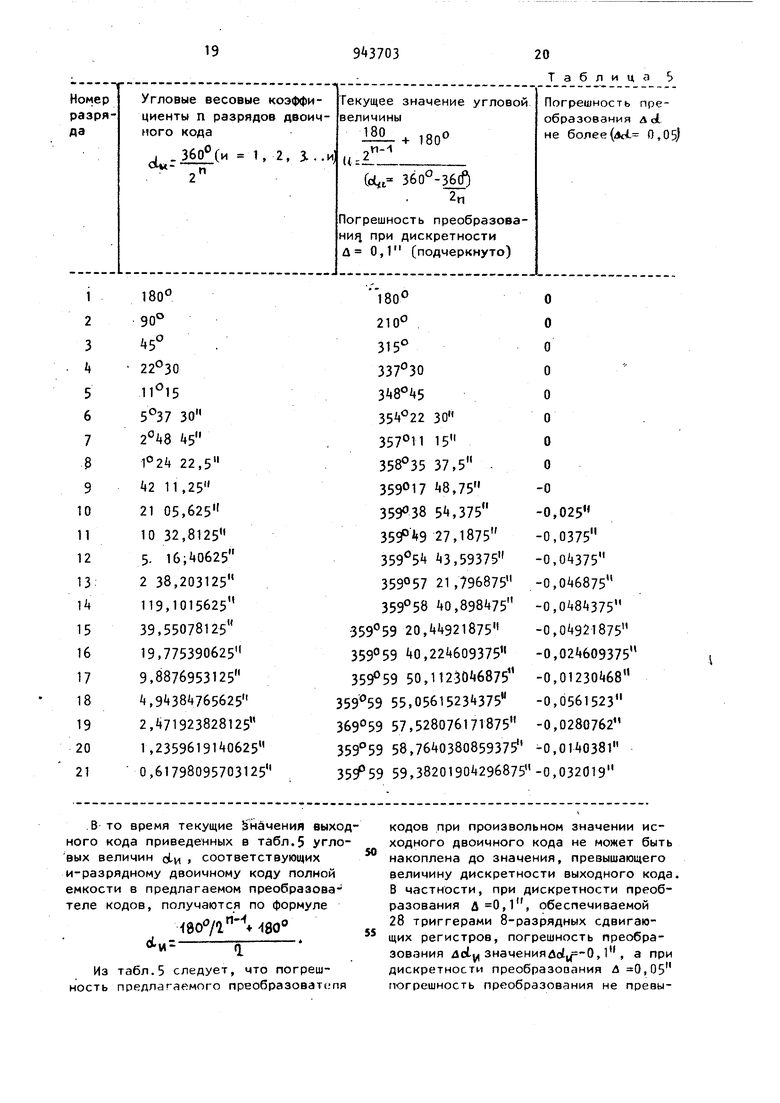

В табл.1 приведены состояния S., ) на S выходах сумматора 5 для и-того шага операции -Запись плюс ТбО при .единичном значении заданной кодовой посылки с номером И исходного двоичного кода.

Десятичная коррекция плюс 6x10 вводится по входам BQ, Вл сумматора 5 в виде угловой величины 60 в тех случаях, когда в результате суммирования должна формироваться единица десятичного переноса Р 1. Единица переноса в старший разряд не должна формироваться (Р.д « О) только в . единственном случае, когда на входах А|, А, Aij имеются нули (табл.1),В этом случае результат суммирования меньше . При двоично-десятичном суммировании кодов Ад- Аг остальных чисел 2,,6,8, десятков градусов с кодом Bg-l угловой величины 80° единица переноса Р 1 формируется и возникает необходимость в десятичной коррекции плюс 6x10 обеспечиваемой единицами на входах В, В(2 двоичного сумматора 5 с помощью элемента ИЛИ 7& табл.1 приведены значения угловых величин двоично-десятичного кода 10-8-4-2-1 с учетом бита информации А 1 не влияющего на результат суммирования кодов. Код 2 X 1 X на выходах 5,() и 5(100) сумматора 5 формируется без дополнительной коррекции в результате суммирования входных переменных и с одинако вой угловой размерность ТхЮО Стабл. 1) Значение переменной , яВляющееся промежуточным при суммировании кодов

с помощью сумматора 5 формируется на внутренней шине последнего. Эта шина на фиг.1 не показана.

Ъ %

ы«

| название | год | авторы | номер документа |

|---|---|---|---|

| Реверсивный преобразователь двоичного кода в двоично-десятичный код | 1978 |

|

SU771661A1 |

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1988 |

|

SU1529457A2 |

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1979 |

|

SU860054A1 |

| Преобразователь двоичного кода в двоично-десятично- шестидесятиричный код | 1982 |

|

SU1051529A1 |

| Преобразователь двоичного кода в двоично-десятичный код градусов и минут | 1979 |

|

SU783787A1 |

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код градусов,минут,секунд | 1980 |

|

SU960791A1 |

| Преобразователь кодов | 1989 |

|

SU1619402A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1984 |

|

SU1280702A1 |

| Устройство для вычитания двоично-десятичных кодов | 1982 |

|

SU1043640A1 |

| Преобразователь двоичного кодаВ дВОичНО-дЕСяТичНый | 1978 |

|

SU809150A1 |

«-о Ь о о

в

. . в ,- -

oil

о 1о N ЧЧ

sIV sir 2j- 5j o| r

.|% %Га Суммирование содержимого разрядов 100 и 10 сдвигового регистра с кодом угловой величины производится только в течение тех тактов t.j преобразования, когда имеется логическая 1 соответствующего п-разряда входного двоичного кода. При наличии же нуля в данном разряде

V. - BK. SK. (при Qg 1)

1

О

О

1

Работа сумматора коррекции минус 3 производится в соответствии ; с табл.2 логических состояний Sj,- f (АО. В ц,) для случая единИ| ного состояния выхода QQ триггера старшей разрядности соответствующей триады 12,

На Ац.- входы сумматора 4 поступает код 4-2-1 с одноименных QJJ- выходов соответствующей триады, а на объединенные его входы Bj, Вц поступает сигнал выхода Qg триггера старшего разряда данной триады. При этом при двоично-десятичный код 4-2-1, поступающий на входы, суммируется с двоично-десятичным кодом числа 5. 9

Таблица 2

о

о

Таким образом осуществляется дес/iтичная коррекция содержимого сдвигового регистра после сдвига информации вправо, когда формированию логической единицы ( на выходе триггера старшего разряда соответствует двоично-десятичный код 0101 (5), а не код 1000(8),

Десятичная коррекция кода минус с помощью сумматора 4, подключенного рассмотренным выше способом, реализуется по правилу минус 8 плюс 5 табл,2),

В табл,3 приведены логические состояния S f ( к.}

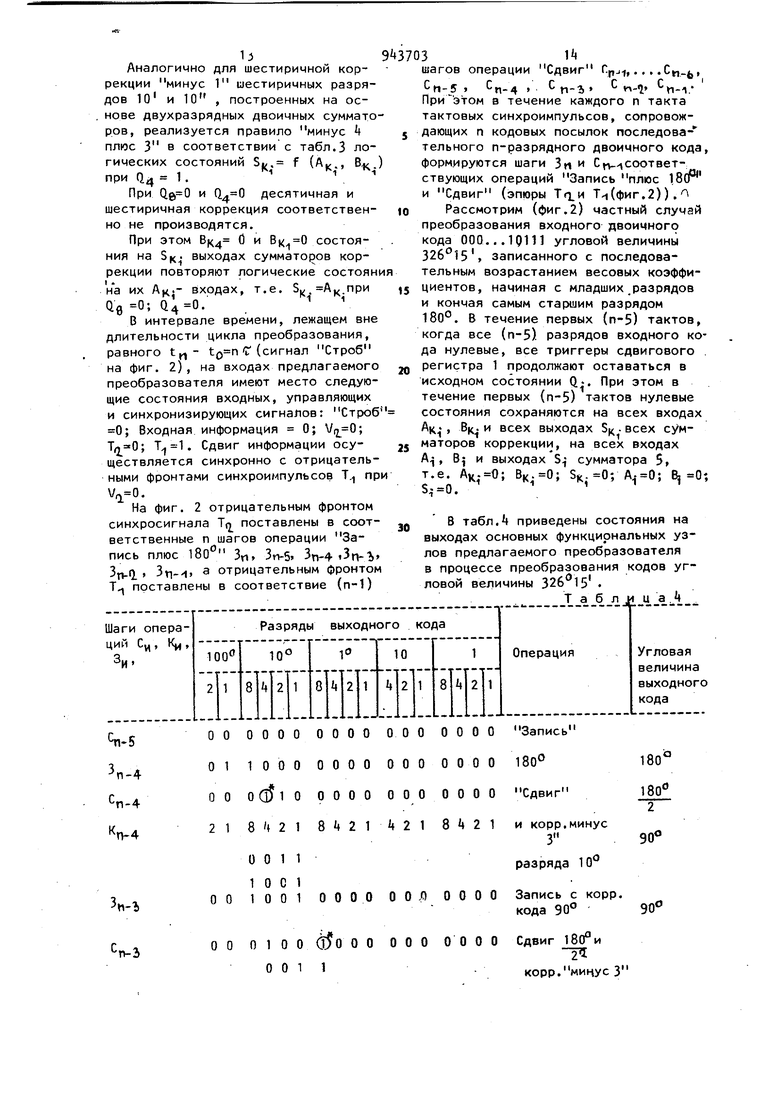

Таблица 3, 3 на В-входах Вд, В, В(100°)сумматора 5 формируются нулевые сигналы и на S: - выходах этого сумматора повторяются состояния входов А, т.е. S, А,- при , В табл. 2 приведены логические состояния f(A Ki КГ Аналогично для шестиричной коррекции минус 1 шестиричных разрядов 10 и 10 , построенных на основе двухразрядных двоичных суммато ров, реализуется правило минус плюс 3 в соответствии с табл.3 логических состояний S|,. f (д., , Btf при (14 1. При и десятичная и шестиричная коррекция соответственно не производятся. При этом В(4 О и состояния на SK- выходах суммато|эов коррекции повторяют логические состоян на их А ц,.- входах, т.е. S,. А Qe 0; интервале времени, лежащем вне длительности цикла преобразования, равного 1„- С (сигнал Строб на фиг. 2), на входах предлагаемого преобразователя имеют место следующие состояния входных, управляющих и синхронизирующих сигналов: Строб 0; Входная информация 0; V,0; . Сдвиг информации осуществляется синхронно с отрицательными фронтами синхроимпульсов Т., пр . На фиг. 2 отрицательным фронтом синхросигнала J( поставлены в соответственные п шагов операции Запись плюс iSo Зп 3rv5 3tT-4 «Зп-Ъ Зп-Ч Зп--1 3 отрицательным фронтом J поставлены в соответствие (п-1) 1001 00 1001 0000 00.Э 0000 00 0100 0 00 000 0000 001

90 3 шагов операции Сдвиг Г.р,.., .Сп, -S t Cn-4 -n-i w-1 -л: При этом в течение каждого п такта тактовых синхроимпульсов, сопровождающих п кодовых посылок последова- тельного п-разрядного двоичного кода, формируются шаги Зи и С vtсоответствующих операций Запись плюс и Сдвиг (эпюры Т-1(фиг.2)) . Рассмотрим (фиг.2) частный случай преобразования входного двоичного кода 000...1011 угловой величины 326 15, записанного с последовательным возрастанием весовых коэффициентов, начиная с младших разрядов и кончая самым старшим разрядом 180°. В течение первых (п-5) тактов, когда все (п-5). разрядов входного кода нулевые, все триггеры сдвигового регистра 1 продолжают оставаться в исходном состоянии Q-. При этом в течение первых (п-5) тактов нулевые состояния сохраняются на всех входах B(q и всех выходах S - всех сумматоров коррекции, на всех входах А, В и выходах S.J сумматора 5, т.е. АК.О; Вц.0; S.0; В, 0; В табл. приведены состояния на выходах основных функциональных узлов предлагаемого преобразователя в процессе преобразования кодов yi ловой величины Запись с корр. кода 90° Сдвиг 180°и Т1 корр.МИНУС 3

+ 1 1 1 1 1 О О О 1 О О 1 О 1 О О О 0.0 О О 01 0001 00106)00 0000 (Т) ГП Кодовые посылки логических 1 исходного кода угловой величины формируются во время тактовых синхроимпульсов с номерами Cj, ,,il,a во время остальных (п-) тактов Т и формируются нулевые кодовые посылки (фиг.2).

После занершения шага операции Сдвиг H.V) выходах всех тригге плюс IbO

с корр.плюс 6

180°

Т 225°

ров сдвигового регистра .сохраняются нулевые состояния.

В рассматриваемом случае преобразования первая единичная кодовая

посылка пятого по старшинству разря40гР

да исходного кода с весом -iSK. фо.ра

мируется в течение такта t. д и является сигналом, управляющим формировлединичные сигналы на выходах Q4 триггеров старших разрядов тетрад и триад, управляющие соответственно десятичной коррекцией минус 3 т и шестиричной коррекцией минус 1 выходных кодов. единичные сигналы на одном из выходов 5|с(), (10°) 5(10 ) сумматора коррекцией разряда 10 выходного кода, управляющие коррекцией плюс 6 при суммировании кода угловой величины 180 с содержанием-сдвигового регистра в разрядах 10 выходного кода. 180 Сдвиг 180 ,р-о -2 + lou и корр; минус 1 разр. 10112°30 нием кода 10-8 S()1 и Sg()1 угловой величины iSo на выходах 5(100) и 50() сумматора 5. Во время формирования отрицательного фронта импульса синхроимпульсов Т(1 с номером 3. одноименный шаг операции Запись плюс 8& записи кода угловой величины 180 . Во время формирования отрицательного фронта тактового импульса Т с номером осуществляется одноименный шаг операции Сдвиг в результате которого на Q -выходах разрядного сдвигающего регистра разряда Ю формируется код 1100, соответствующий двоичному числу 12 (двоичный код угловой величины 120°)1 Единичный сигнал на выходе Qg() разряда Ю, обозначенный в табл.4 следующим образом (3) является управляющим для формирования во время шага коррекции К сигнала коррекции минус 3 на объединенных входах B« и В| сумматора коррекции минус 3 разряда 0°Ъ(Q°) 1 и В,((10°)1. В результате этого на его выходах SIJ.BO время шага K ofiHMftyeTc скор ректированный двоично-десятичный код 1001 угловой величины 90°. Формирование скорректированных кодов на выходах всех сумматоров коррекции осуществляется в интервале времени межд шагами С и Зп-f з запись скорректированных значений кодов, поступающих на входы сдвигового регистра, осуществляется по шагем операции Запись плюс 180 совместно с записью скорректированного кода суммы его содержимого с кодом угловой величины 180°. В соответствии с изложенным выше запись скорректированного значения кода 1001 угловой величины 90 в разряд 10° осуществляется на шаге операции Запись плюс 180°. На шаге добавление кода 180° не производится, так как во время так таС - имеет место нулевая кодовая посылка. При этом в интервале време93 ни между соседними шагами С, и на Q - выходах сдвигового регистра продолжает храниться нескорректированный двоичный код (фиг.2). После шага Сп 5сдвига информации и коррекции минус 3 в .разряде 10° хранится код 0100 угловой величины 0, а на S.выходах сумматора коррекции минус 3 разряда код 0101 угловой величины 50°. Следовательно, после сдвиг;; вправо кода угловой величины 90 фс рмируется скорректированный (по разряду 1°) код угловой велинины 5°. Запись скорректирован-ного кода 0101 угловой величины 5 в разрядный сдвигающий регистр 1° осуществляется на шаге совместно с записью значения 10 кода 2x100 1x100 угловой величины200 и значения 0010 кода угловойвеличины 20 результата суммированиякодов угловых величин tO°+ скоррекцией плюс 6x10°. Единичныесигналы управляющие формированиемсигналов 6x10° на выходах коррекции плюс В и BQ сумматора 5, обозначены в табл. следующим образомС1. После завершения шага З.о. в сдвиговом регистре хранится код угловой величины 225°, а после шага 3 обеспечивается запись искокрго значения двоично-десятично-шестидесятиричного кода угловой величины 32б°15. В табл. 5 приведены точные значения угловых весовых коэффициентов 21-разрядного двоичного кода, точные значения набора текущих угловых величин .,,ol,j,...joL3,...,d( соответствующие величины погрешности пред лагаемого преобразования кодов при двух знамениях дискретности преобразования ,1 и а 0,05. Каждое значение угловой величины cL, приведенное в табл.5, соответствует полному набору всех и логических единиц и-разрядного двоичного кода. Для и-разрядного двоичного кода полной емкости (и логических 1) справедливо выражение с1п 360 Угловые весовые коэффи Номер разряциенты п разрядов двои да ного кода . .(и 1,2, З. -т

180°

90°

5°

. 22°30

5°37 30

1°2t 22,5

2 11,25 21 05,625 10 32,8125

5-

2 38,203125

119,1015625

39,55078125

19,775390625

9,8876953125 359°59 55,05615234375

/,9438 765625 369°59 57,528076171875

2,71923828125 359°59 58,7640380859375

1,23596191 0625

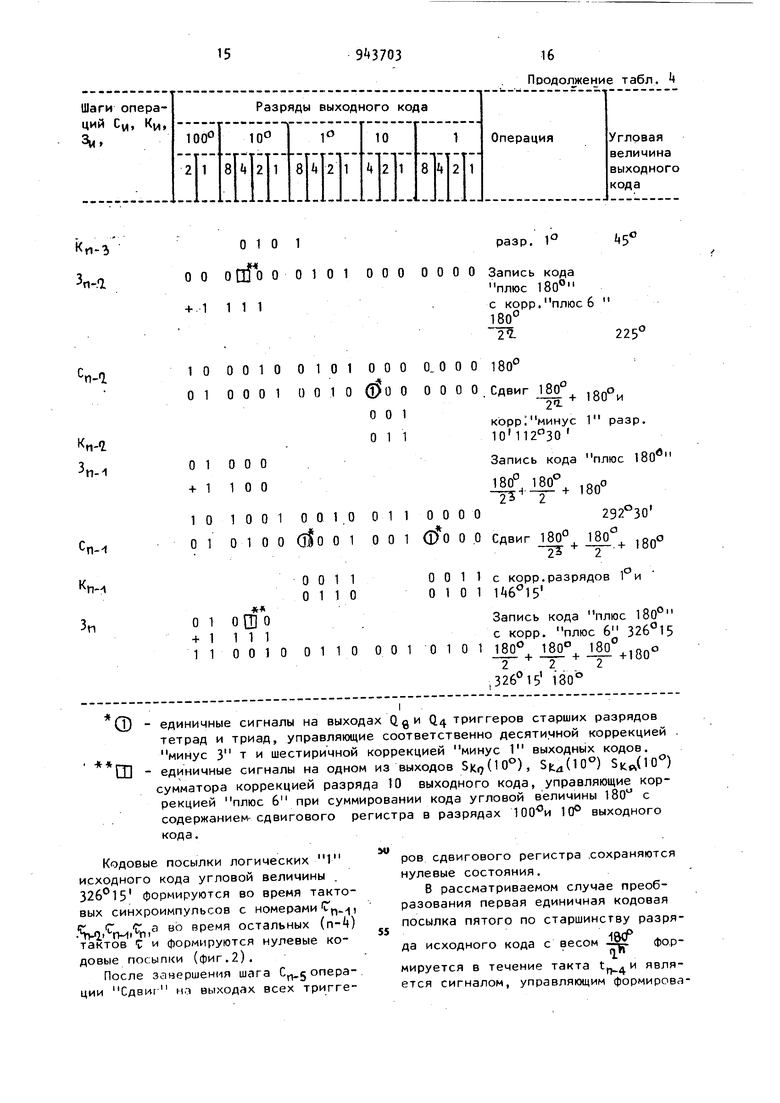

0,61798095703125 59,38201904296875 В то время текущие йнйчения выхо ного кода приведенных в табл.5 угло вых величин сИц , соответствующих и-разрядному двоичному коду полной емкости в предлагаемом преобразователе кодов, получаются по формуле 80°/l % -180 Из табл.5 следует, что погрешность предлагаемого преобразоватопя

l80°

О О 210° 315°

о о о о о о 337°30

3i 8°45 30

357°11 15 358°35 37,5 8,75 -о 5,375

-0,025 27,1875

-0,0375 359V 3,59375

-0,04375

-0,046875 21 ,796875 359°58 ,898475

-0,0484375 20,44921875

-0,04921875

-0,024609375 359°59 40,224609375 359°59 50,1123046875

-0,01230468

-0,0561523

-0,0280762

-0,0140381

-0,032019 Текущее значение угловой величины Погрешность преобразованщ при дискретности Л 0,1 (подчеркнуто) Таблица 5 Погрешность преобразования Adi 180 не более(лс1 0,05) + 180° (ot,, 360°-36rf5 2п КОДОВ при произвольном значении исходного двоичного кода не может быть накоплена до значения, превышающего величину дискретности выходного кода, В частности, при дискретности преобразования ,l, обеспечиваемой 28 триггерами 8-разрядных сдвигающих регистров, погрешность преобразования Д(Ау, значенияйЫ1 -0,1 , а при дискретности преобразопания ,05 погрешность преобразования не превышает -0,05.Преобразование кодов осуществляется строго за время п v формирования п-кодовых посылок входного кода без каких-либо дополнительных затрат времени. При этом погрешность преобразования кодов может быть уменьшена до сколько угодно малой величины ( вплоть до ее исключения ) при фиксированном времени пье зопреобразования путем наращивания числа разрядов сдвигового регистра. Преимущество предлагаемого преобразователя кодов заключается также в уменьшении количества соединений и в упрощении функциональной схемы пре образователя, обеспечении большой функциональной гибкости за счет идентичности схем формирования кодов десятичных и шестиричных разрядов, а также за счет нeзaвиcи 5ocти электрических соединений структурных частей преобразователя кодов от количества разрядов исходного и выходного кодов Предлагаемый преобразователь кодов более универсален по сравнению с известными решениями, так как в оди- . наковой степени пригоден для преобразования исходного двоичного кода и с постоянными весовыми коэффициентами и с целочисленной двоично-десятичной ценой младшего разряда исходного двоичного кода. Формула изобретения Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код, содержащий сумматор, распределитель импульсов, вход которого является тактовым входом преобразователя, сдвиговый регистр, состоящий из последовательно соединенных диады тетрад и триад, тактовые и управляющие входы которых соединены с соответствующими выходами распределителя 9 3 импульсов, группу сумматоров, первые входы которых соединены с разрядными выходами соответствующих тетрад и триад сдвигового регистра, выходы которого являются выходами преобразователя, выходы сумматоров, кроме первого, группы соединены с разрядными входами соответствующих тетрад и триад сдвигового регистра, о т л и ч а ю щ и и с я тем, что, с целью упрощения преобразователя, он содержит элемент И и элемент ИЛИ, входы которого соединены с выходами трех старших разрядов первого сумматора группы и с первыми входами младших разря дов сумматора соответственно, первый вхрд старшего разряда которого соединен с первым -выходом диады сдвигового регистра, выход элемента ИЛИ соединен с первым входом элемента И, второй вход которого является информационным входом преобразователя и соединен со вторыми входами двух старших разрядов сумматора, выход элемента И соединен со вторыми входами двух младших разрядов сумматора, выходы младших разрядов которого и выход младшего разряда первого сумматора группы соединены с соответствующими входами сдвигового регистра первой тетрады, выходы старшего разряда и выход переноса сумматора соединены соответственно с первым и вторым входами диады сдвигового регистра, выходы старших разрядов тетрад и триад которого соединены со вторыми входами младших разрядов соответствующих сумматоров группы. Источники информации. принятые во внимание при экспертизе 1.Патент США М (, кл. , опублик. 17.01.78. 2.Авторское свидетельство СССР № 603985, кл. G 06 F 5/02, 197. 3.Авторское свидетельство СССР по заявке tf 2828289/2, кл. G 06 F 5/02, 10,10.79.

. /

-te

/yfr

-fiz

9

Л.

A

A

rn.

.4lM.

Авторы

Даты

1982-07-15—Публикация

1980-07-03—Подача