+

сг

С

| название | год | авторы | номер документа |

|---|---|---|---|

| РЕЛЯТОРНЫЙ ПРОЦЕССОР ДЛЯ АДРЕСНО-РАНГОВОЙ ОБРАБОТКИ КОРТЕЖЕЙ АНАЛОГОВЫХ СИГНАЛОВ | 1995 |

|

RU2120662C1 |

| ПРОЦЕССОР ДЛЯ АДРЕСНО-РАНГОВОЙ ИДЕНТИФИКАЦИИ И СЕЛЕКЦИИ АНАЛОГОВЫХ СИГНАЛОВ | 1994 |

|

RU2093888C1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ НЕЧЕТКОЙ ИНФОРМАЦИИ | 1998 |

|

RU2158441C2 |

| УСТРОЙСТВО ДЛЯ РАНГОВОЙ ОБРАБОТКИ ДИСКРЕТНО-АНАЛОГОВЫХ СИГНАЛОВ | 1992 |

|

RU2129302C1 |

| Устройство для спектрального анализа | 1985 |

|

SU1249535A2 |

| Цифровой фильтр | 1990 |

|

SU1780089A1 |

| Устройство для вычисления порядковых статистик | 1986 |

|

SU1354210A1 |

| Цифровой фильтр | 1985 |

|

SU1327281A1 |

| УСТРОЙСТВО ДЛЯ РАНГОВОЙ ФИЛЬТРАЦИИ | 1990 |

|

RU2015551C1 |

| УСТРОЙСТВО ДЛЯ РАНГОВОЙ ФИЛЬТРАЦИИ СТРУКТУРНЫХ СИГНАЛОВ | 1991 |

|

RU2101756C1 |

Изобретение относится к радиотехнике и вычислительной технике. Целью изобретения является повышение быстродействия фильтрации. Цифровой ранговый фильтр содержит входной блок памяти 1 , состоящий из (п+1 ) регистров памяти 2; п компараторных

оъ -а

31

ячеек 3, п блоков совпадения k, сумматор 5, выходной умножитель 6, блок памяти коэффициентов 7 и генератор тактовых импульсов 8. Компараторная ячейка 3 состоит из регистра ранговой статистики, двух компараторов, двух арифметико-логических блоков и

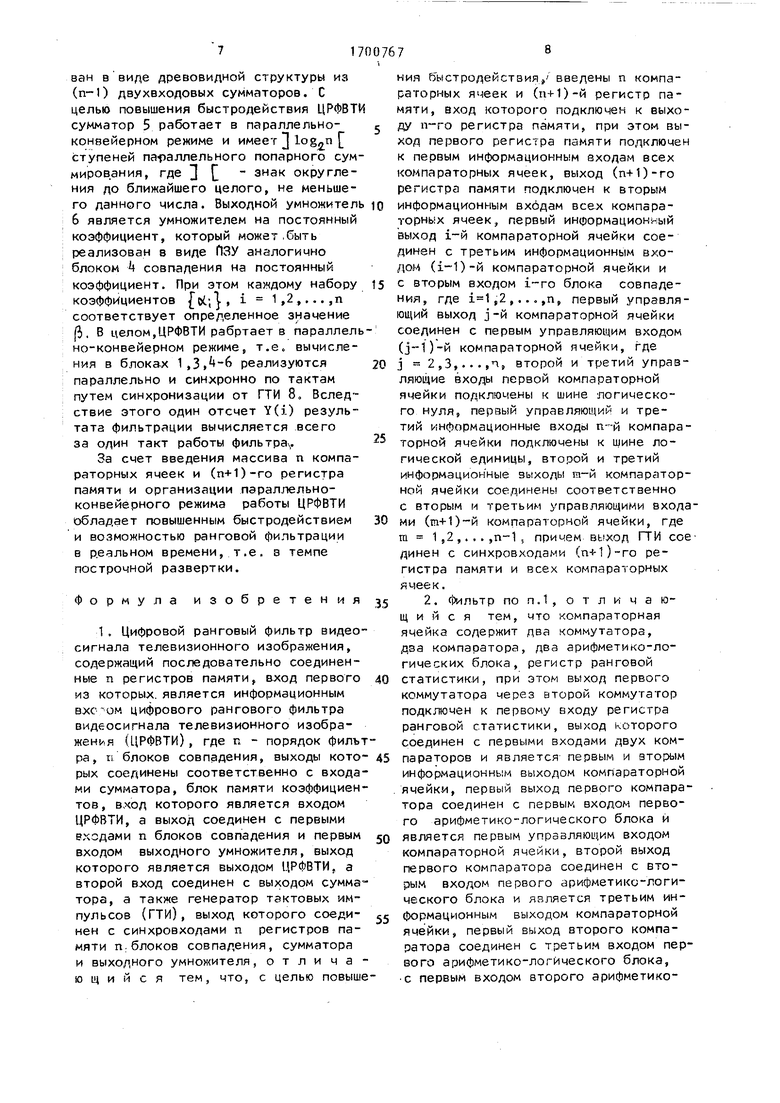

Изобретение относится к радиотехнике и вычислительной технике и может быть использовано для фильтрации видеосигнала телевизионного изображен ия.

Целью изобретения является повышение быстродействия.

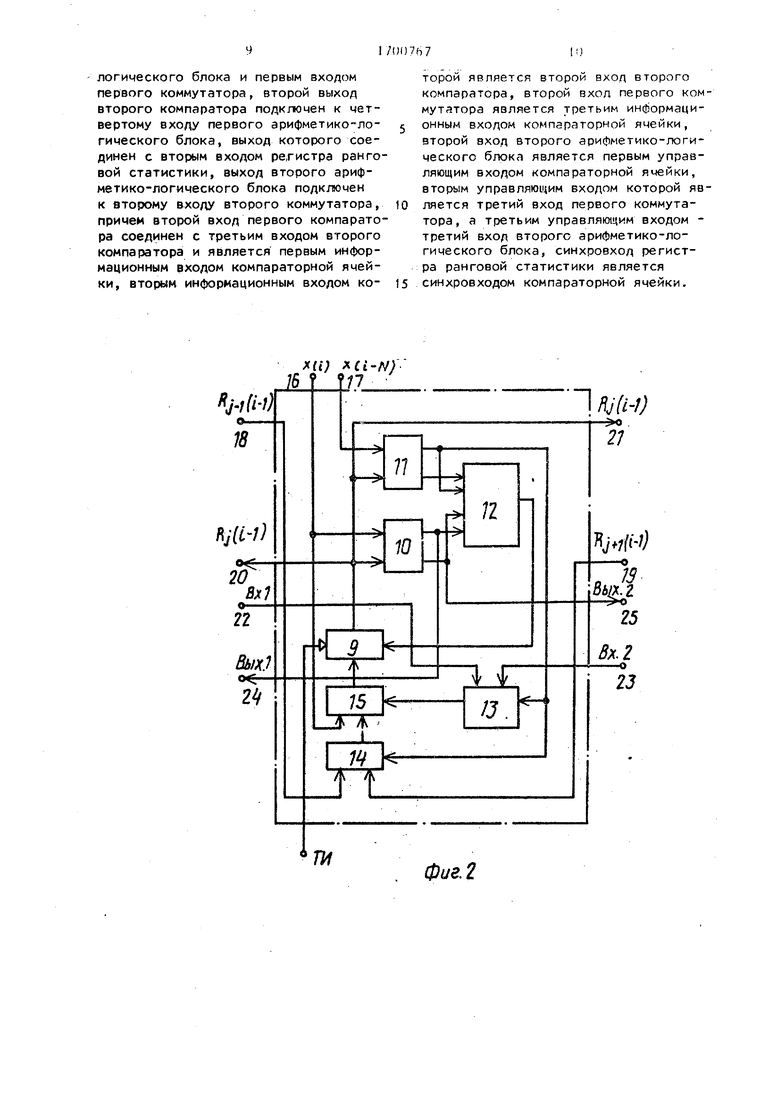

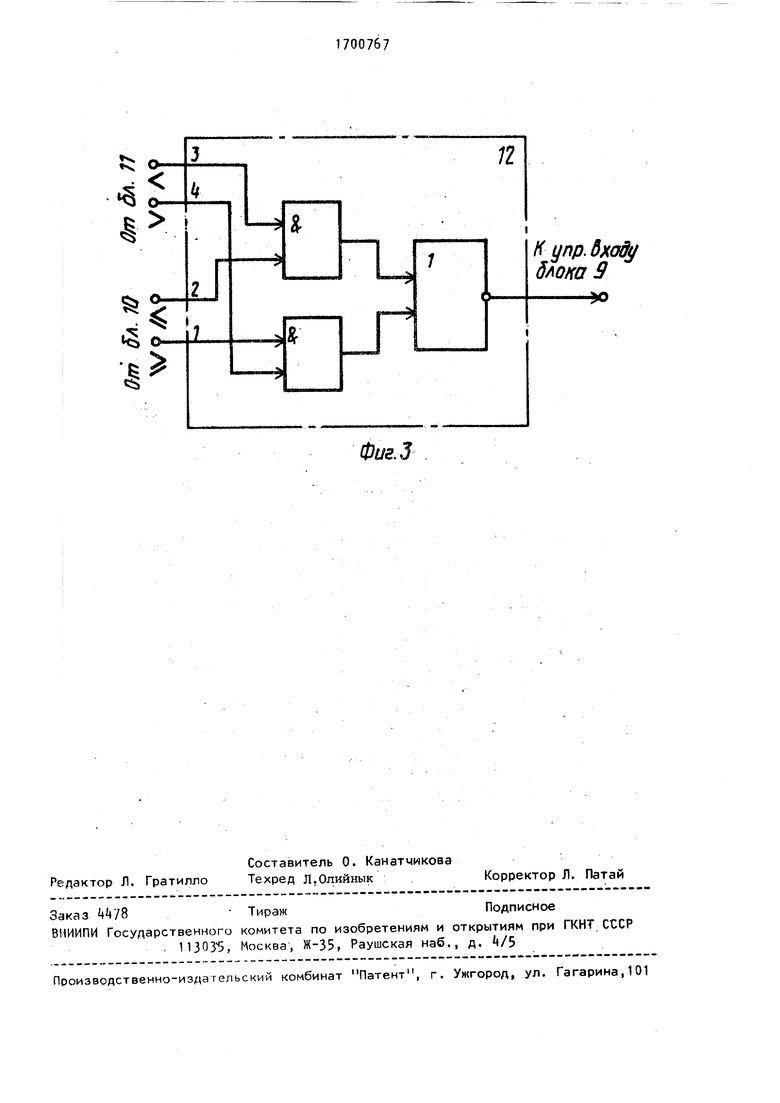

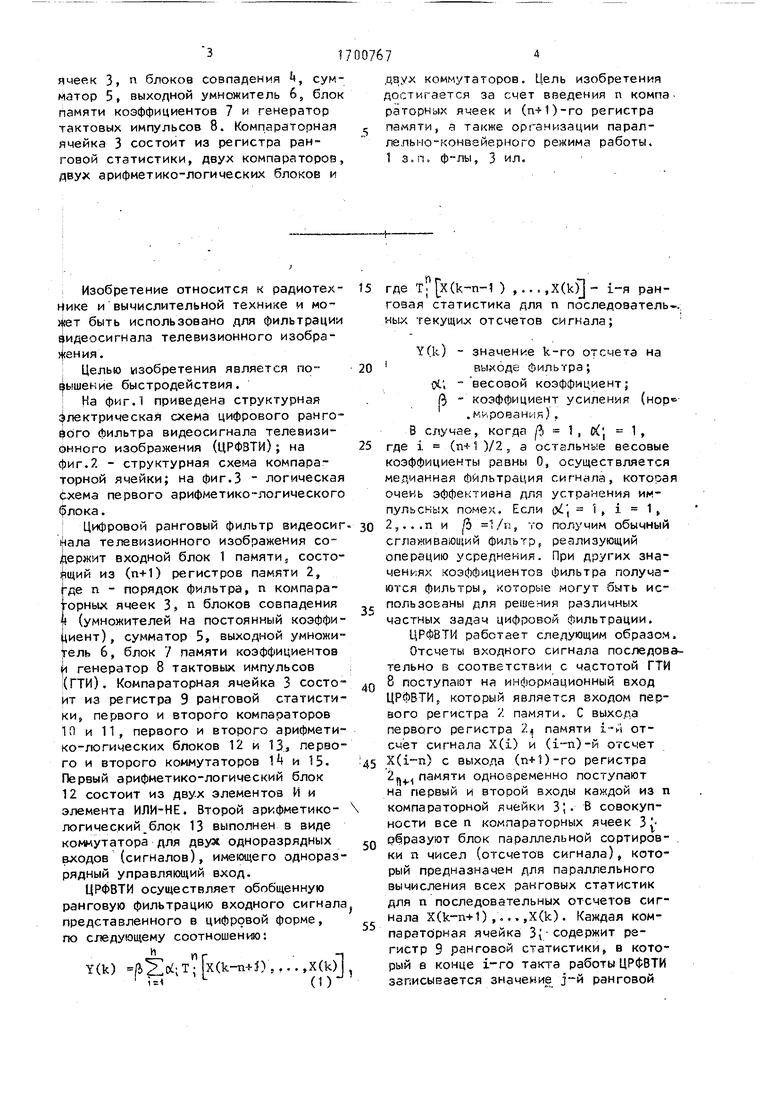

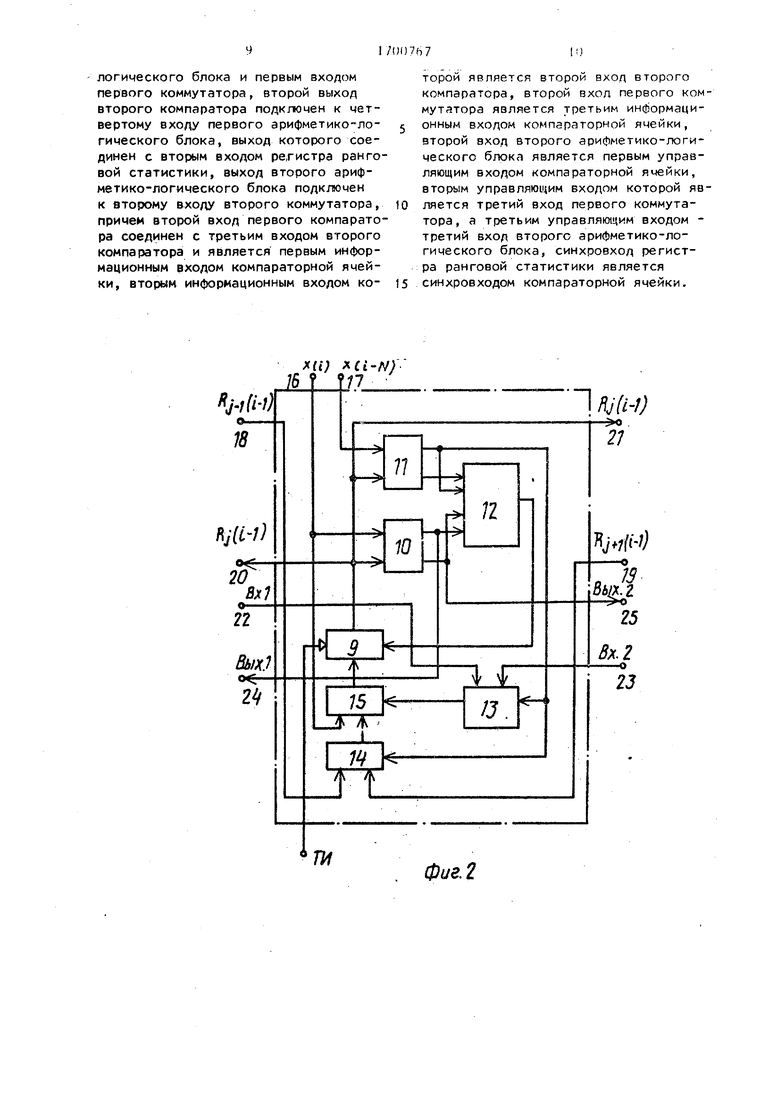

На фиг. приведена структурная электрическая схема цифрового рангового фильтра видеосигнала телевизионного изображения (ЦРФВТИ); на фиг.. - структурная схема компара- торной ячейки; на фиг.З логическая схема первого арифметико-логического блока.

Цифровой ранговый фильтр видеосиг нала телевизионного изображения содержит входной блок 1 памяти, состоящий из (п+1) регистров памяти 2, где п - порядок фильтра, п компараторных ячеек 3, п блоков совпадения k (умножителей на постоянный коэффициент), сумматор 5, выходной умножитель 6, блок 7 памяти коэффициентов и генератор 8 тактовых импульсов (ГТИ). Компараторная ячейка 3 состоит из регистра 9 ранговой статистики, первого и второго компараторов 10 и 11, первого и второго арифметико-логических блоков 12 и 13j первого и второго коммутаторов k и 15. Первый арифметико-логический блок 12 состоит из двух элементов И и элемента ИЛИ-НЕ. Второй арифметике- логический блок 13 выполнен в виде коммутатора для двух одноразрядных входов (сигналов), имеющего одноразрядный управляющий вход.

ЦРФВТИ осуществляет обобщенную ранговую фильтрацию входного сигнала представленного в цифровой форме, по следующему соотношению:

Y(k) (k-n+J),,..,X(k)

1 ы L d)J

двух коммутаторов. Цель изобретения достигается за счет введения п компа раторных ячеек и (п-М)-го регистра памяти, а также организации параллельно-конвейерного режима работы. 1 з.п. ф-лы, 3 ил.

s

0

5

0

5

0

5

0

5

где Т; x(k-n-1 ) , ...fx(k)- i-я ранговая статистика для п последователь-, ных текущих отсчетов сигнала;

Y(k) - значение k-ro отсчета на 1 выходе фильтра;

Otl весовой коэффициент; А - коэффициент усиления (нор .м рования).

В случае, когда ft 1 , tfj 1 , где i (п+1 )/2, а остальные весовые коэффициенты равны 0, осуществляется медианная фильтрация сигнала, которая очень эффективна для устоанения импульсных помех. Если 0ij 1, i 1, 2,...п и fb 1/п, то получим обычный сглаживающий фильтр, реализующий операцию усреднения. При других значениях коэффициентов фильтра получаются фильтры, которые могут быть использованы для решения различных частных задач цифровой фильтрации.

ЦРФВТИ работает следующим образом.

Отсчеты входного сигнала последовательно в соответствии с частотой ГТИ 8 поступают на информационный вход ЦРФВТИ, котооый является входом первого регистра } памяти. С выхода первого регистра 2 памяти i-и отсчет сигнала X(i) и (1-п)-й отсчет X(i-n) с выхода (п+1)-го регистра 2 памяти одновременно поступают на первый и второй входы каждой из п компараторной ячейки 3;. В совокупности все п компараторных ячеек 3 образуют блок параллельной сортировки п чисел (отсчетов сигнала), который предназначен для параллельного вычисления всех ранговых статистик для п последовательных отсчетов сигнала X(k-n+1),...,X(k). Каждая ком- параторная ячейка 3{ содержит регистр 9 ранговой статистики, в который в конце 1-го такта работы ЦРФВТИ записывается значение j-й ранговой

статистики iR (i) Т : fX(i-n+1),..., X(i)J. Компараторные ячейки З; реализуют параллельный алгоритм рекурсивного вычисления всех ранговых статистик последовательности п отсчетов

Rj(i-l), при X(i)5 Rj(i-l) X(i-n);

Rj(i-l), при X(i)Ј Rj(i-l)x(i-n);

мин (x(i)j RJH(i-1)j, при X(i) R/(i-1)bX(i-n);

макс x(i) ; Rj-1(i-1)j, при X(i)jЈ F,/(i-1) Ј X(i-n) .

Посредством первого и второго компараторов 1 Г1 и 11 реализуется сравне- ние Rj(i-l) с X(i )и X(i-n) соответственно. При этом значение Rj(i-1) хранится в регистре 9 ранговой статистики. Посредством первого арифметико-логического блока 12 вырэбатыва- ется управляющий сигнал для разрешения записи в регистр 9 ранговой статистики очередного значения j-й ранговой статистики. В случае, когда на выходе арифметико-логического блока 12 имеется единичный управляющий сигнал, в регистр 9 ранговой статистики записывается одно из трех значений X(i) , Rj(i-1), R;f1() как новое значение Rj(i) согласно соотношения (2). j-й компараторной ячейки 3 результат сравнения X(i) с Rj-jd-l) поступает с третьего информационного выхода (j-1)n ячейки 3 на третий управляю- щий вход ячейки в виде сигнала ВХ1, а результат сравнения X(i.) с Rj+1(i+1) с управляющего выхода (j + O-й ячейки 3 на управляющий вход в виде сигнала ВХ2. Эти сигналы одновременно подаются на второй и третий одноразрядные входы второго арифметико-логического . блока 13, которые являются информационными входами одноразрядного коммутатора. На первый вход второ- го арифметико-логического блока 13 поступает выходной сигнал Меньше с первого выхода второго компаратора 11 . Этот сигнал также подается на пер-- вый вход первого компаратора 1. В случае, когда этот сигнал является логической единицей, то на выходе первого коммутатора 1 имеется значение (двоичный код числа Rj, (i-1). В противоположном случае на его вы- ходе присутствует значение Rj+(i-1) В зависимости от выходного сигнала второго арифметико-логического блока 13 на выходе второго коммутатора

сигнала, в котором j-я ячейка вычисляет значение j-й ранговой статистики Rl(i) в 1-м такте работы ЦРФВТИ относительно входного отсчета 4(1)

(2)

15 присутствует или значение X(i) или выходное значение первого коммутатора 14. При поступлении тактового импульса на вход синхронизации регистра 9 ранговой статистики происходит запись в нем выходного значения коммутатора 15- Поскольку вычислния во всех ячейках 3 происходит одновременно, то за один факт работы фильтра в п регистрах 9 ранговой статистики имеется отсортированная последовательность чисел X(k-n+0

X(k), т.е. значения всех п ранговых статистик относительно k-ro отсчета сигнала. Эти значения затем параллельно поступают на вторые входы п блоков k совпадения. Каждый из блоков k совпадения реализован в виде постоянного запоминающего устройства (ПЗУ), в котором М-разрядный адресный вход является первым и вторым входами. При этом первые К разрядов адресного входа ПЗУ составляют первый вход, а остальные (М-К) разрядов являются вторым входом блока совпадения, где 2К М, например , а . На первый вход всех блоков k совпадения подается одинаковый код (номер) набора коэффициентов (V;. где ,2,...п, на которые таблично умножаются выходные значения компара- торных ячеек 3, т.е. процесс умножения является процессом выборки информации (результата умножения) из ПЗУ. В блоке 7 памяти коэффициентов записаны коды (номера) наборов постоянных коэффициентов, на которые таблично умножаются вычисленные ранговые статистики в блоках 4 совпадения. Конкретный набор коэффициентов в зависимости от решаемой задачи фильтрации задается с управляющего входа (ЦРФВТИ, который является адресным входом блока 7 памяти коэффициентов. Сумматор 5 предназначен для суммирования п чисел и может быть реалиэован в виде древовидной структуры из (п-1) двухвходовых сумматоров. С целью повышения быстродействия ЦРФВТИ сумматор 5 работает в параллельно- конвейерном режиме и имеет Ј ступеней параллельного попарного суммирования, где 3 С знак округления до ближайшего целого, не меньшего данного числа. Выходной умножитель 6 является умножителем на постоянный коэффициент, который может .быть реализован в виде ПЗУ аналогично блоком 4 совпадения на постоянный коэффициент. При этом каждому набору коэффициентов {&( , i 1,2,...,п соответствует определенное значение ($. В целом,ЦРФВТИ рабртает в параллель но-конвейерном режиме, т.е. вычисления в блоках 1,3,-6 реализуются параллельно и синхронно по тактам путем синхронизации от ГТИ 8. Вследствие этого один отсчет Y(i) результата фильтрации вычисляется всего за один такт работы фильтрач.

За счет введения массива п компа- раторных ячеек и (п+1)-го регистра памяти и организации параллельно- конвейерного режима работы ЦРФВТИ обладает повышенным быстродействием и возможностью ранговой фильтрации в реальном времени, т.е. в темпе построчной развертки.

Формула изобретения

0

5

0 5 0 5

ния быстродействия, введены п компа- раторных ячеек и (п+1)-й регистр памяти, вход которого подключен к выходу n-го регистра памяти, при этом выход первого регистра памяти подключен к первым информационным входам всех компараторных ячеек, выход (п+1)-го регистра памяти подключен к вторым информационным вхбдам всех компзра- торных ячеек, первый информационный выход i-й компараторной ячейки соединен с третьим информационным входом (1-1)-й компараторной ячейки и с вторым входом 1-го блока совпадения, где ,2,...,п, первый управляющий выход j-й компараторной ячейки соединен с первым управляющим входом (j-1)-u компараторной ячейки, где j 2,3,...,n, второй и третий управляющие входы первой компараторной ячейки подключены к шине логического нуля, первый управляющий и третий информационные входы компараторной ячейки подключены к шине логической единицы, второй и третий информационные выходы m-й компараторной ячейки соединены соответственно с вторым и третьим управляющими входами (т-И)-й компараторной ячейки, где m 1,2,...,п-1, примем выход ГТИ соединен с синхровходами (п-Н)-го регистра памяти и всех компараторных ячеек.

торой является второй вход второго компаратора, второй вход первого коммутатора является третьим информационным входом компараторной ячейки, второй вход второго арифметико-логического блока является первым управляющим входом компараторной ячейки, вторым управляющим входом которой является третий вход первого коммутатора, а третьим управляющим входом - третий вход второго арифметико-логического блока, синхровход регистра ранговой статистики является синхровходом компараторной ячейки.

Фиг. 2

Фиг.З

| Цифровой фильтр | 1985 |

|

SU1327281A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-12-23—Публикация

1989-07-04—Подача