Изобретение относится к области автоматики и аналоговой вычислительной техники и может быть использовано для ранговой идентификации входных сигналов x1,...,xn, для выделения сигнала заданного ранга из множества сигналов x1,...,xn с идентификацией и без идентификации адреса входа, на который воздействует выделенный сигнал, для параллельного аналого-цифрового преобразования n аналоговых сигналов x1,...,xn, в качестве ранговых распределителей сигналов, для ранжирования аналоговых сигналов, для воспроизведения изломных и разрывных функций и др.

Известны реляторные модули, осуществляющие адресно-ранговую обработку одного из n=3 аналоговых сигналов (см., например, а.с. N 1541636 или статью "Реляторный модуль для рангово-адресной идентификации и селекции выходных сигналов датчиков" в сборнике тезисов V-й Российской научно-технической конференции "Оптические, радиоволновые, тепловые методы и средства контроля качества материалов, изделий окружающей среды". - Ульяновск: Госкомитет по высшему образованию, 1993, рис. 1). Указанные модули обладают ограниченными функциональными возможностями, так как предназначены для обработки трех аналоговых сигналов.

Известен также аналоговый ранговый процессор (а. с. 1571627, G 06 G 7/12). Данный процессор выделяет один из n сигналов заданного ранга, а для выделения сигнала другого заданного ранга процессор требует перестройки, что также ограничивает его функциональные возможности. Здесь для параллельной обработки всего массива переменных требуется n процессоров, предложенных в а. с. 1571627, настроенных на различные ранги r = 1,2,...,n. Но при этом увеличивается расход оборудования в n раз.

Наиболее близким к предлагаемому схемному решению является многопороговый функциональный преобразователь (а.с. 1689972, G 06 G 7/25).

Прототип по сравнению с предлагаемым схемным решением также обладает ограниченными функциональными возможностями, так как не позволяет воспроизводить операции адресно-ранговых совпадений, выделения медианных значений при четном числе переменных и др.

Целью изобретения является расширение функциональных возможностей.

Поставленная цель достигается тем, что в устройстве, содержащем ранговый квантователь, n-1 источников задающих напряжений U1,...,Un-1, источник квантующего напряжения E, управляющий вход i-го позиционного коммутатора соединен i-м выходом Ui рангового квантователя, где i = 1,2,...,n, i-е задающее входы всех позиционных коммутаторов объединены и присоединены к i-му источнику задающего напряжения Ui=(0,5+i)E, выходы n позиционных коммутаторов образуют n групп адресных идентифицирующих выходных каналов, i-е выходы всех позиционных коммутаторов объединены и образуют n групп ранговых идентифицирующих каналов, а первый выход первого, второй выход второго и т.д. до n-го выхода последнего позиционного коммутатора образуют группу выходных шин, идентифицирующих адресно-ранговые совпадения номеров входов и рангов сигналов.

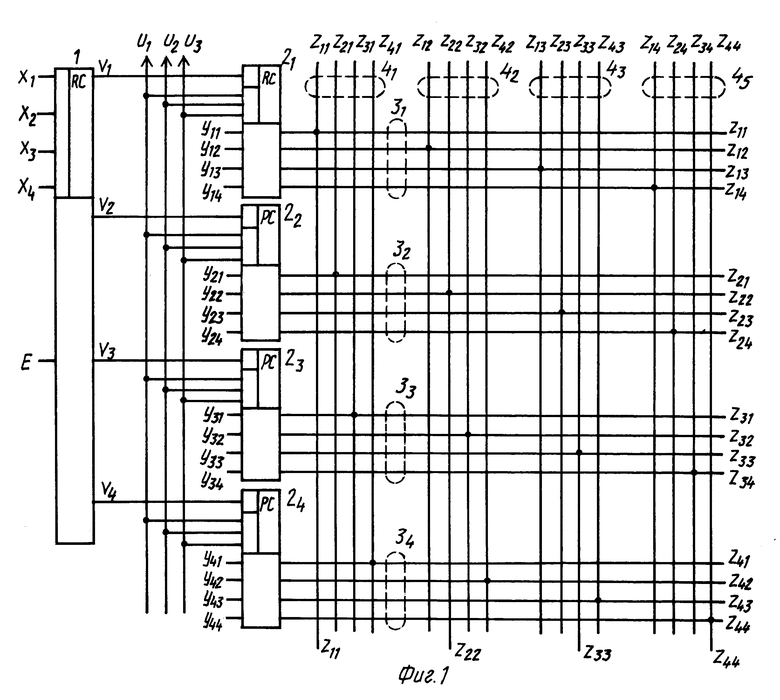

На фиг. 1 представлена схема рангового нейропроцессора при n=4.

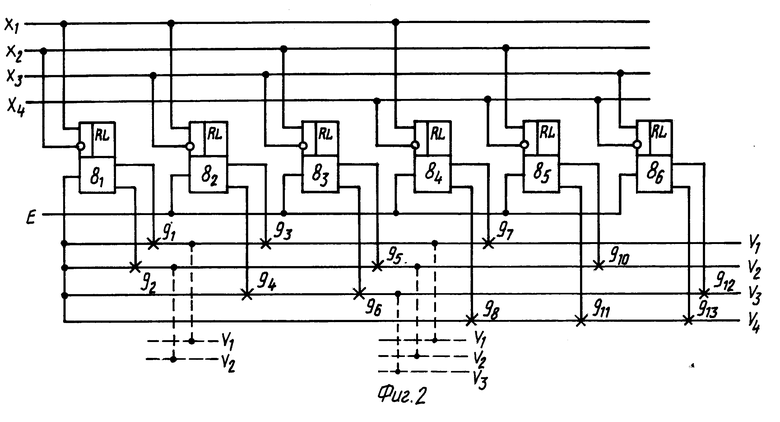

На фиг. 2 представлена схема рангового квантователя при n=4 (патент РФ N 2060550).

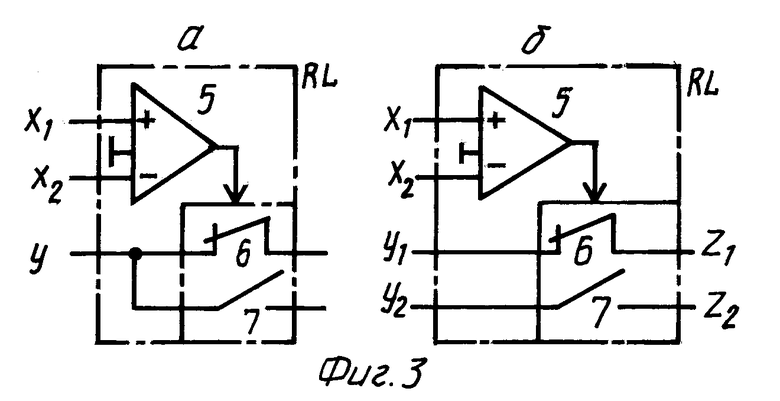

На фиг. 3 представлены схемы нейронных логических элементов (реляторов), на которых построены функциональные узлы нейропроцессора.

На фиг. 4 представлена схема позиционного коммутатора при n=4 (а.с. 1679507).

На фиг. 5 - 8 изображены схемы включения (межсоединений) выводов процессора для воспроизведения различных операций и функций.

Нейропроцессор содержит ранговый квантователь 1, n-позиционных коммутаторов 2i (по числу входных сигналов x1,...,xn), n групп (Zi1,...,Zin) выходных шин ранговой идентификации сигналов 3i, n групп (Zij, Z2j,...,Znj) выходных шин адресной идентификации ранговых сигналов 4i (i=1, 2,...,n; j = 1, 2, . ..,n), одну группу выходных шин (Z11, Z22,...,Znn) идентификации адресно-ранговых совпадений.

Ранговый квантователь 1 (фиг. 2) содержит 0,5 (n-1) реляторов 8 с обращенном включении, схема которых показана на фиг. 3, а. На фиг. 3 цифрой 5 обозначен компаратор, 6 и 7 есть соответственно замыкающий и размыкающий ключи, состоянием которых управляется полярность выходного напряжения компаратора 5 (положение ключей 6 и 7 на фиг. 3 соответствует ситуации, когда напряжение на неивертирующем выходе компаратора больше напряжения на его инвертирующем входе).

Ранговый квантователь (PK) содержит n входных шин, на которые подаются входные сигналы x1,...,xn суммирующих выходных шин 9i, с которых снимаются выходные сигналы V1, ...,Vn, и источник квантующего напряжения E. Компараторные входы реляторов 8i соединены с входными шинами по принципу "каждый со всеми". На переключательные входы реляторов 8i и на входы суммирующих выходных шин подается квантующее напряжение E. На первый вход каждого последующего сумматора 9i подается напряжение с выхода предыдущего сумматора. Вторые входы сумматоров 9i соединены с соответствующими выходами реляторов 8i. В каждую выходную шину включено n-1 сумматоров 9i.

Наращивание размерности квантователя 1 осуществляется без разрушения его исходной схемы.

Выходные напряжения V1,...,Vn рангового квантователя 1 подаются соответственно на управляющие входы позиционных коммутаторов 21,...,2n. Каждый позиционный коммутатор 2i содержит n-1 реляторов 10i, схема которых представлена на фиг. 3,б. На переключательные входы каждого позиционного коммутатора 2i подаются идентифицирующие сигналы yi1, yi2,...,yin (в частном случае yi1= yi2= . . .=yin=yi). Инвертирующие компараторные входы реляторов 10i в каждом позиционном коммутаторе объединены и образуют его управляющий вход, на который подается выходной сигнал Vi с i-го выхода рангового квантователя 1. Каждый позиционный коммутатор имеет n выходов (Zi1, Zi2,...,Zin), которые являются выходами нейропроцессора.

На неинвентирующие компараторные входы реляторов 10i в порядке возрастания от входного до выходного релятора подаются задающие напряжения U1<U2<... <Un-1.

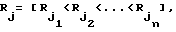

Выходы позиционных коммутаторов (Zi1, Zi2,...,Zin) образуют n групп 3i выходных шин ранговой идентификации сигналов x1,...,xn, выходы (Z1j, Z2j,... ,Znj) образуют n групп шин 4j адресной идентификации ранговых сигналов x(1), x(2), . ..,x(n), где j=ri есть ранг сигнала xi=x(ri), воздействующего на i-й вход нейропроцессора. Последовательность x(1),..., x(n) получена ранжированием переменных x1,...,xn в порядке их неубывания.

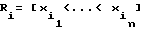

В основу построения процессора положен используемый в моделях нейронных сетей принцип кодирования заданных признаков номеров канала (параллельное пространственное кодирование). Воспроизводимая ранговым квантователем 1 функция определяется отображением (x1,...,xn) ---> (V1,...,Vn), где Vi=riE. Здесь индекс i в индексации выходных напряжений Vi рангового квантователя 1 совпадает с нумерацией входов процессора (с нумерацией входных переменных xi). Для n сигналов x1, ...,xn возможны n! ранговых отношений (ситуаций)  .

.

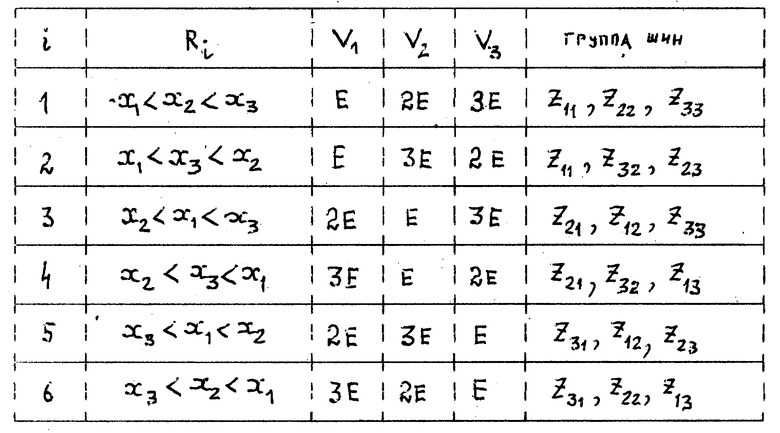

В таблицу сведены все n!=1•2•3=6 ситуаций Ri при n=3. Ранговый квантователь нормирует по амплитуде компоненты xi входного кортежа (x1,...,xn) с сохранением их ранговых отношений. По каждому фиксированному выходу Vi ранговый квантователь является рангово-аналоговым преобразователем, воспроизводящим функцию Vi=riE, где ri есть ранг i-го сигнала  (см. таблицу).

(см. таблицу).

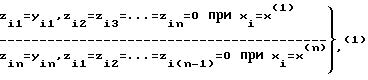

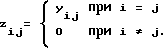

Позиционный коммутатор 2i (i-й коммутатор) воспроизводит функцию ранговой идентификации i-го сигнала

где индексы i,j∈{1,2,...,n} в индексации ij сигналов Zij и yij есть соответственно номер (адрес) переменной и ранг (j=ri) этой переменной. Здесь ранговая идентификация заданного сигнала xi=x(ri) осуществляется номером j= ri возбужденного канала zij∈{zi1,...,zin}. а адресная идентификация осуществляется номером i выходной группы шин 3i.

Путем различных группировок выходных шин (Zi1,...,Zin) 3i процессор воспроизводит ряд других функций и операций адресной и ранговой идентификации сигналов.

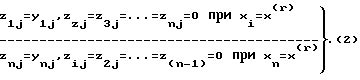

По группам выходных шин 4 воспроизводится операция адресной идентификации сигналов заданных рангов:

Здесь по номеру i возбужденного канала Zij осуществляется адресная идентификация рангового сигнала x(j) j-го ранга.

Дальнейшее расширение номенклатуры воспроизводимых операций возможно путем различных межсоединений выводов процессора.

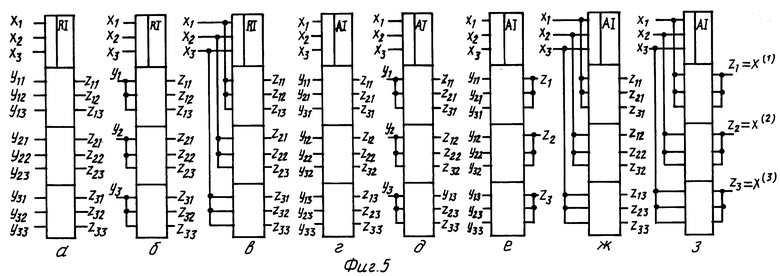

На фиг. 5,а представлено условное изображение процессора (фиг. 1) при n= 3 по горизонтальным группам выходных шин (ранговая идентификация RI). Функция преобразования процессора (фиг. 5,б) определяется выражением (1) при i=1,2,...,n.

При объединении в каждой группе переключательных входов от схемы по фиг. 5, а приходим к схеме по фиг. 5,б, которая при равномерной шкале задающих напряжений U1, U2,...,Un-1 и y1=y2=...=yn=y является n-канальным аналого-цифровым преобразователем (АЦП) с выходным параллельным кодом типа "продвижение единицы".

При соединении каждого i-го входа процессора с i-й группой переключательных входов проходим к схеме n-канального рангового распределителя (фиг. 5, в). Здесь в каждой i-й группе управляющий (идентифицируемый) сигнал xi проходит на тот выход Zij, номер которого j совпадает с рангом сигнала xi= x(j).

На фиг. 5,г представлено условное изображение процессора при n=3 по вертикальным группам выходных шин (адресная идентификация Al). Процессор по фиг. 5,г воспроизводит полный набор операций адресной идентификации ранговых сигналов. Здесь на j-й группе шин (j=1,...,n) выделяются сигналы Zij=x(j) j-го ранга, а номер i возбужденной шины в группе идентифицирует номер входной переменной xi. Функция преобразования схемы по фиг. 5,г определяется выражением (2) при j = 1, 2,...,n.

На фиг. 5,д изображено демультиплексорное включение процессора по фиг. 5,г, воспроизводящего операцию (2) при y1j=y2j=...=ynj=yj, j=1,2,...,n.

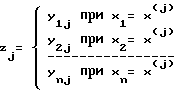

На фиг. 5,е представлено мультиплексорное включение процессора. В мультиплексорном включении процессор (фиг. 5,е) путем различных межсоединений входных (компараторных) и переключательных входов и соответствующей фиксации идентифицирующих сигналов yij воспроизводит полные наборы предикатных, предикатно-аргументных, аргументных и непрерывно-логических функций. При этом полное количество аргументных функций от n переменных равно N=nn!, то есть N=729 при n=3. Операции, воспроизводимые схемой по фиг. 5,е, определяется выражением

При включении входных выводов в схеме по фиг. 5,д в соответствии с фиг. 5, ж воспроизводится операция ранжирования входных сигналов x1,...,xn с идентификацией входов, на которые воздействуют выделенные сигналы. Воспроизводимая фиг. 5,ж операция определяется выражением (2) при y1j=...ynj=xj, то есть на j-й группе выходов выделяется сигнал xi=x(j) j-го ранга, воздействующий на i-й вход.

Схема, изображенная на фиг. 5, з воспроизводит операцию ранжирования (x1,...,xn) _→ (x(1),...,x(n)) множества входных сигналов x1,...,xn. При n=3 (фиг. 5, з) осуществляется параллельное выделение (селекция) минимального, медианного и максимального сигналов: Z1=x(1)=min(x1,x2,x3), Z2=x(m)=med(x1, x2,x3), Z3=x(3)=max(x1,x2,xn).

По группе выходов (Z11,Z22,...,Znn), для которых воспроизводится операция адресно-ранговых совпадений

Здесь возбуждаются те выходы, для которых идентифицируемый адрес (ранг) сигнала совпадает с его рангом (адресом).

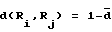

Выбор выходных шин (Z11, . ..,Znn) с индексацией i=j задает эталонную ситуацию R1= [x1<. . .<xn], при наличии которой все выходы Z11,...,Znn возбуждены. Количество  возбужденных выходов в кортеже (Z11,...,Znn) является мерой близости текущей ситуации с эталонной. Количество невозбужденных выходов

возбужденных выходов в кортеже (Z11,...,Znn) является мерой близости текущей ситуации с эталонной. Количество невозбужденных выходов  есть хемминговое расстояние между текущей Ri и эталонной Rj ситуациями.

есть хемминговое расстояние между текущей Ri и эталонной Rj ситуациями.

В качестве эталонной может быть выбрана любая из n! ситуация  что позволяет осуществлять ситуационную идентификацию сигналов x1,...,xn.

что позволяет осуществлять ситуационную идентификацию сигналов x1,...,xn.

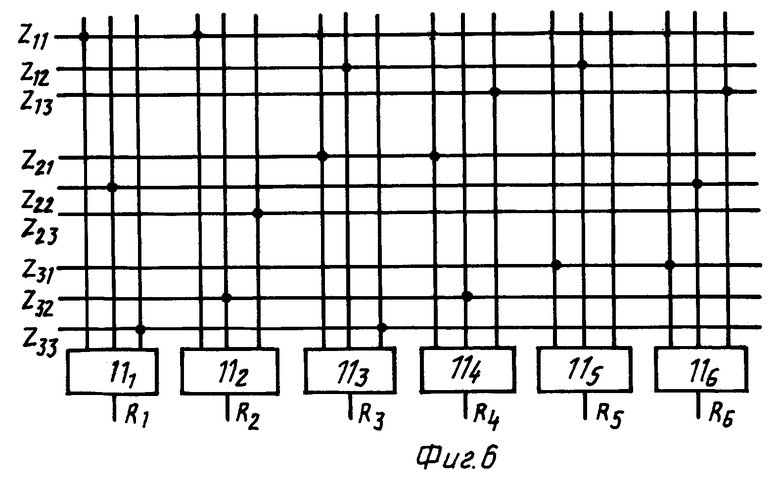

На фиг. 6 представлена схема межсоединений горизонтальных и вертикальных шин при работе процессора в режиме ситуационной идентификации сигналов x1,.. . , xn при n=3 (см. таблицу), где 11i есть логические схемы И (конъюктурны). Здесь возбуждается один из n=6 выходных каналов. Номер возбужденного канала идентифицирует соответствующую ситуацию Ri, указанную в таблице. Соответствующей перегруппировкой входных сигналов по входам процессора всегда может быть обеспечено условие Ri=1.

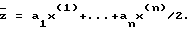

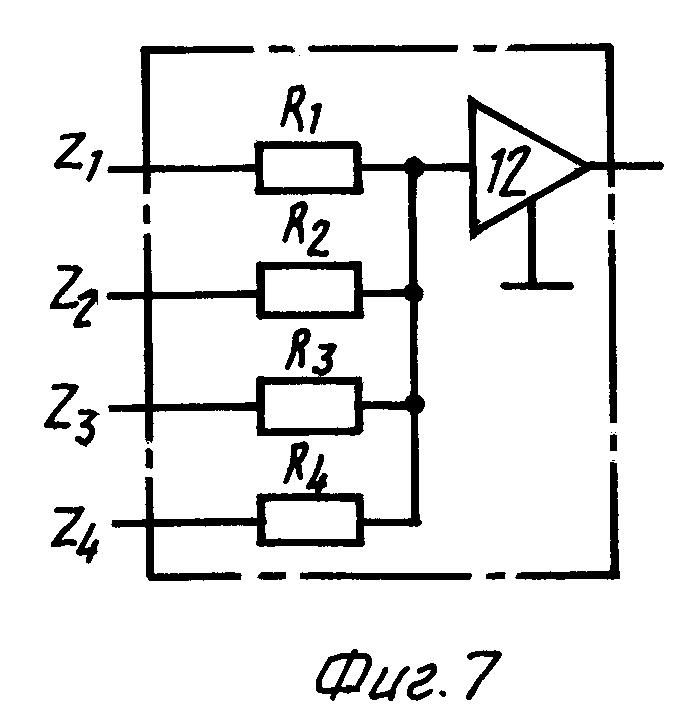

При подаче выходных сигналов с выходов ранжирующей схемы (фиг. 5,з) на вход взвешивающего устройства (фиг. 7) воспроизводится операция рангового взвешивания  . На фиг. 7 R1, R2, R3, R4 есть взвешивающие резисторы, 12 - управляемый током источник напряжения (при достаточно малой нагрузке он может отсутствовать). При равных сопротивлениях воспроизводится операция формирования среднеарифметического значения ранговых сигналов x(1),...,x(n): Z=(x(1)+...+x(n))/2.

. На фиг. 7 R1, R2, R3, R4 есть взвешивающие резисторы, 12 - управляемый током источник напряжения (при достаточно малой нагрузке он может отсутствовать). При равных сопротивлениях воспроизводится операция формирования среднеарифметического значения ранговых сигналов x(1),...,x(n): Z=(x(1)+...+x(n))/2.

В приведенных схемах выходные сигналы снимаются между соответствующей выходной шиной и шиной заземления ("землей"). При снятии выходных сигналов между двумя заданными i-й и k-й выходными шинами в ранжирующих схемах (фиг. 5,з) воспроизводится операция вычитания ранговых сигналов x(i) и x(k): Zi,k= x(i)-x(k). В частности, при i=1 и k=n воспроизводится операция определения размаха выборки x1,...,xn:Z1,n=max(x1, ...,xn)-min(x1,...,xn).

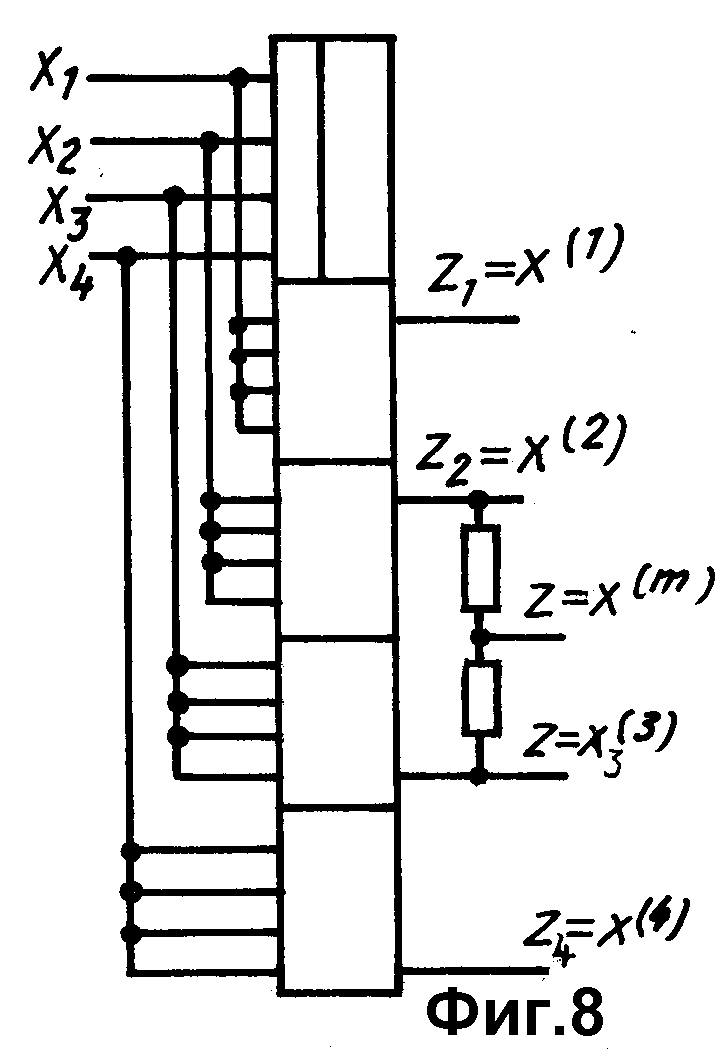

В статистике медианное значение x(m) при четных n определяется как полусумма субмедианной  и супрамедианной

и супрамедианной  переменных, где m1=0,5n,

переменных, где m1=0,5n,  На фиг. 8 представлена схема включения процессора (фиг. 5, з) для воспроизведения операции выделения медианного сигнала при n=4. Здесь между субмедианным Z2=x(2) и супрамедианным Z3=x(3) выходами включен делитель напряжения, содержащий равные сопротивления R1 и R2 (R1= R2). С выхода делителя напряжения снимается медианное значение Z= x(m)= (x(2)+x(3))/2 выборки x1,...,xn. Аналогично в ранжирующем процессоре любой размерности включение такого делителя между субмедианным

На фиг. 8 представлена схема включения процессора (фиг. 5, з) для воспроизведения операции выделения медианного сигнала при n=4. Здесь между субмедианным Z2=x(2) и супрамедианным Z3=x(3) выходами включен делитель напряжения, содержащий равные сопротивления R1 и R2 (R1= R2). С выхода делителя напряжения снимается медианное значение Z= x(m)= (x(2)+x(3))/2 выборки x1,...,xn. Аналогично в ранжирующем процессоре любой размерности включение такого делителя между субмедианным  и супрамедианным x(m2) выходом формирует медианное значение.

и супрамедианным x(m2) выходом формирует медианное значение.

Таким образом, предлагаемое решение обладает широкими функциональными возможностями, часть которых отсутствует у прототипа.

В общем случае процессор по каждой группе выходных шин может воспроизводить различные операции, что также расширяет его функциональные возможности.

Процессор осуществляет параллельную обработку сигналов, то есть обладает максимально возможным быстродействием, недостижимым при использовании традиционных процессоров, реализующих структуру "аналого-цифровой преобразователь - цифровая обработка сигналов - цифроаналоговый преобразователь".

Изобретение относится к автоматике и может быть использовано для ранговой идентификации входных сигналов. Целью изобретения является расширение функциональных возможностей. Процессор содержит ранговый квантователь, источник квантующего напряжения, источники задающих напряжений и позиционные коммутаторы. 8 ил., 1 табл.

Регуляторный процессор для адресно-ранговой обработки кортежей аналоговых сигналов, содержащий ранговый квантователь с n выходами по числу входных сигналов, источник квантующего напряжения E, n-1 источников задающих напряжений U1,...Un-1, n позиционных коммутаторов с одним управляющим и n-1 задающими входами и n выходами, отличающийся тем, что управляющий вход i-го позиционного коммутатора соединен с i-м выходом Vi рангового квантователя, где i=1,2,...n, i-е задающие входы всех позиционных коммутаторов объединения и присоединены к i-му источнику задающего напряжения Ui=(i+0,5) E, i-е выходы всех позиционных коммутаторов объединены и образуют n групп ранговых идентифицирующих каналов, а первые выходы первого, второй выход второго и т. д. до n-го выхода последнего позиционного коммутатора образуют группу выходных шин.

| Многопороговый функциональный преобразователь | 1989 |

|

SU1689972A2 |

| Аналоговый ранговый процессор | 1988 |

|

SU1571627A1 |

Авторы

Даты

1998-10-20—Публикация

1995-01-31—Подача