Изобретение относится к вычислительной технике и предназначено для выполнения следующих операций над расплывчатыми переменными: инверсии, дизъюнкции, конъюнкции, импликации и эквивалентности, а также для преобразования нечетких множеств второго рода в нечеткие множества первого рода. Оно может применяться в системах управления в качестве спецвычислителя с целью принятия решений в условиях неопределенности экспертной информации, а также при оперативном управлении технологическими процессами по нечетким алгоритмам.

Известно устройство для сравнения двух нечетких величин [1], содержащее генератор импульсов, счетчик, два генератора линейного напряжения, первый и второй генераторы пилообразного напряжения, первый, второй и третий аналого-цифровые преобразователи, первый и второй цифроаналоговые преобразователи, первый и второй аналоговые компараторы, сумматор, два ключа, элемент сборки, два регистра, два блока сравнения, два вычитателя, умножитель, элемент ИЛИ, первую и вторую группу из n элементов И, где n - количество разрядов сравниваемых величин, группу из n элементов задержки, первый, второй и третий элементы задержки, причем выход генератора импульсов соединен со счетным входом счетчика, выход переполнения которого через первый элемент задержки соединен с входом останова генератора импульсов, выход первого генератора пилообразного напряжения соединен с входом первого аналого-цифрового преобразователя, выход первого цифроаналогового преобразователя соединен с первым входом первого аналогового компаратора, вход запуска устройства соединен с входами запуска первого генератора линейного напряжения, первого генератора пилообразного напряжения и генератора импульсов, выход которого соединен с тактовыми входами первого и второго аналого-цифровых преобразователей и через второй элемент задержки с входами запуска второго генератора линейного напряжения и второго генератора пилообразного напряжения, выход первого генератора линейного напряжения соединен с информационным входом второго аналого-цифрового преобразователя, выход которого соединен с первым входом сумматора, выход которого соединен с входом первого цифроаналогового преобразователя, выход второго генератора линейного напряжения соединен со вторым входом первого аналогового компаратора, выходы "Меньше" и "Не меньше" которого соединены с первыми входами элементов И соответственно первой и второй групп, выход первого аналого-цифрового преобразователя соединен с входом второго цифроаналогового преобразователя, выход которого соединен с первым входом второго аналогового компаратора и информационным входом первого ключа, выход второго генератора пилообразного напряжения соединен с информационным входом второго ключа и вторым входом второго аналогового компаратора, выходы "Меньше" и "Не меньше" которого соединены с управляющими входами соответственно первого и второго ключей, выходы которых соединены соответственно с первым и вторым входами элемента сборки, выход которого соединен с информационным входом третьего аналого-цифрового преобразователя, выход i-го разряда которого, где i = 1, 2,... n, соединен со вторыми входами i-х элементов И первой и второй групп и через i-й элемент задержки группы с i-ми информационными входами первого и второго регистров, выходы i-x разрядов которых соединены с i-ми входами первой группы соответственно первого и второго блоков сравнения и с i-ми входами соответственно первой и второй групп первого вычитателя, выход которого соединен с первым входом умножителя, выход которого соединен с первым входом второго вычитателя, выход которого является выходом устройства, выходы i-x элементов И первой и второй групп соединены с i-ми входами второй группы соответственно первого и второго блоков сравнения, выходы которых соединены с входами разрешения записи соответственно первого и второго регистров, входы разрешения считывания которых подключены к выходу элемента ИЛИ, первый и второй входы которого подключены соответственно к тактовому выходу третьего аналого-цифрового преобразователя и к выходу третьего элемента задержки, вход которого подключен к выходу переполнения счетчика, вход задания величины разности минимально возможных значений сравниваемых величин устройства соединен со вторым входом сумматора, вход задания величины 1/2 устройства соединен со вторыми входами умножителя и второго вычитателя.

Известен процессор для реализации операций над элементами расплывчатых множеств [2], содержащий первый, второй и третий регистры, схему сравнения, первый и второй коммутаторы, группу элементов И, управляющую память, счетчик, элемент И, входы исходных значений процессора подключены к информационным входам первого и второго регистров, прямой выход первого регистра подключен к первому информационному входу первого коммутатора, первый информационный выход первого коммутатора подключен к первому информационному входу второго коммутатора и первому входу схемы сравнения, выходы кода операции управляющей памяти подключены к первому управляющему входу второго коммутатора, выходы признака адреса первого операнда адреса первого разряда, признака адреса второго операнда, адреса второго операнда управляющей памяти подключены к управляющему входу первого коммутатора, выходы адреса результата управляющей памяти подключены к входам записи первого, второго и третьего регистров, выход признака конца операции управляющей памяти подключен к первым входам элементов И группы и элемента И, второй вход которого подключен к тактовому входу процессора, а выход - к счетному входу счетчика, выход которого подключен к адресным входам управляющей памяти, входы записи счетчика и управляющей памяти подключены к входу задания режима работы процессора, информационный вход управляющей памяти подключен к входу загрузки программы процессора, информационные входы счетчика подключены к входам адреса микрокоманды процессора, инверсный выход первого регистра подключен к второму информационному входу первого коммутатора, прямой и инверсный выходы второго регистра - к третьему и четвертому информационным входам первого коммутатора, прямой и инверсный выходы третьего регистра - к пятому и шестому информационным входам первого коммутатора, второй информационный выход которого подключен к второму информационному входу второго коммутатора и второму входу схемы сравнения, выход которой подключен к второму управляющему входу второго коммутатора, выход которого подключен к вторым входам элементов И группы, к информационным входам второго и третьего регистров, выходы элементов И группы подключены к группе выходов результата процессора.

Наиболее близким по технической сущности и функциональным возможностям к заявляемому устройству для обработки нечеткой информации является устройство для выполнения операций над расплывчатыми операндами [3], содержащее пять регистров, два коммутатора, арифметико-логический блок, два дешифратора, два шинных формирователя, блок памяти, элемент И, группу элементов И, причем информационные входы первого, второго, третьего регистров и первые входы элементов И группы подключены к информационным входам устройства и к выходам первого и второго шинных формирователей, выход первого регистра соединен с первым информационным входом второго коммутатора, инверсный выход первого регистра соединен со вторым информационным входом второго коммутатора, выход второго регистра соединен с третьим информационным входом второго коммутатора, инверсный выход второго регистра соединен с четвертым информационным входом второго коммутатора, выход третьего регистра соединен с пятым информационный входом второго коммутатора, инверсный выход третьего регистра соединен с шестым информационным входом второго коммутатора, первый и второй выходы которого соединены с первым и вторым информационными входами арифметико-логического блока и с первым и вторым информационными входами первого коммутатора соответственно, управляющий вход второго коммутатора соединен с выходом пятого регистра, информационный вход которого соединен с выходом блока памяти, адресный вход которого соединен с выходом четвертого регистра, первый информационный вход которого соединен с входом разрешения записи пятого регистра и с выходом элемента И, первый вход которого соединен со вторым информационным входом четвертого регистра и входом синхронизации устройства, выход пятого регистра соединен с входами разрешения записи первого, второго, третьего регистров, со вторыми входами элементов И, информационным входом первого дешифратора и с первым информационным входом второго дешифратора, первый выход первого дешифратора соединен с входом кода операции арифметико-логического блока, а второй выход соединен с входом синхронизации первого шинного формирователя, информационный вход которого соединен с выходом результата арифметико-логического блока, выход признака равенства операндов которого соединен со вторым информационным входом второго дешифратора, первый выход которого соединен с управляющим входом первого коммутатора, а второй выход второго дешифратора соединен с входом синхронизации второго шинного формирователя, информационный вход которого соединен с выходом первого коммутатора, выходы элементов И группы являются информационными выходами устройства.

Недостатком устройства для выполнения операций над расплывчатыми операндами является узость его функциональных возможностей, выражающаяся в способности к выполнению над расплывчатыми переменными только операций: инверсии, дизъюнкции, конъюнкции, импликации и эквивалентности.

Целью предлагаемого изобретения является расширение функциональных возможностей устройства для выполнения операций над расплывчатыми операндами путем обеспечения ему способности выполнять по сравнению с прототипом операцию преобразования нечеткого множества второго рода в нечеткое множество первого рода.

Поставленная цель достигается тем, что устройство для обработки нечеткой информации, содержащее десять регистров, два регистра признаков, пять коммутаторов, арифметико-логический блок, два дешифратора, три шинных формирователя, блок памяти, элемент И, группу элементов И, интерполятор, причем информационные входы первого, второго, третьего, шестого, седьмого, восьмого, девятого и десятого регистров, первого и второго регистров признаков и первые входы элементов И группы подключены к информационным входам устройства и к выходам первого, второго и третьего шинных формирователей, выходы первого, второго, третьего, шестого и седьмого регистров соединены соответственно с первым, третьим, пятым, седьмым и девятым информационными входами второго коммутатора, второй, четвертый, шестой, восьмой и десятый информационные входы которого соединены соответственно с инверсными выходами первого, второго, третьего, шестого и седьмого регистров, первый и второй выходы второго коммутатора соединены с первым и вторым информационными входами арифметико-логического блока и с первым и вторым информационными входами первого коммутатора соответственно, управляющий вход второго коммутатора соединен с выходом пятого регистра, информационный вход которого соединен с выходом блока памяти, адресный вход которого соединен с выходом четвертого регистра, первый информационный вход которого соединен с входом разрешения записи пятого регистра и с выходом элемента И, первый вход которого соединен с входом синхронизации устройства, второй информационный вход четвертого регистра предназначен для записи адресов микрокоманд, выход пятого регистра соединен с входами разрешения записи первого, второго, третьего, шестого, седьмого, восьмого, девятого и десятого регистров, первого и второго регистров признаков, со вторыми входами элементов И группы, со вторым входом элемента И, с управляющими входами третьего, четвертого и пятого коммутаторов, с входом синхронизации третьего шинного формирователя с информационным входом первого дешифратора и с первым информационным входом второго дешифратора, первый выход первого дешифратора соединен с входом кода операции арифметико-логического блока, а второй выход соединен с входом синхронизации первого шинного формирователя, информационный вход которого соединен с выходом результата арифметико-логического блока, выход признака равенства операндов которого соединен со вторым информационным входом второго дешифратора, первый выход которого соединен с управляющим входом первого коммутатора, а второй выход второго дешифратора соединен с входом синхронизации второго шинного формирователя, информационный вход которого соединен с выходом первого коммутатора, выходы элементов И группы являются информационными выходами устройства, выход первого регистра признаков соединен с информационным входом третьего коммутатора, выход которого соединен с третьим информационным входом четвертого регистра, выходы восьмого и девятого регистров и инверсный выход десятого регистра соединены соответственно с первым, вторым и третьим информационными входами пятого коммутатора, первый, второй и третий выходы которого соединены соответственно с первым, вторым и третьим входами интерполятора, выход второго регистра признаков соединен с информационным входом четвертого коммутатора, выход которого соединен с информационным входом устройства, информационный вход третьего шинного формирователя соединен с выходом интерполятора.

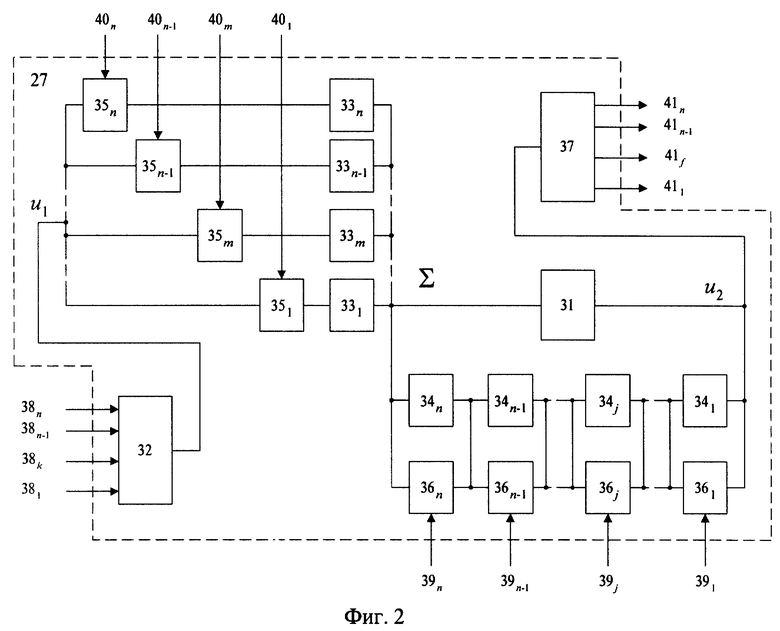

Структурная схема устройства для обработки нечеткой информации представлена на фиг. 1. На фиг. 2 представлена структурная схема интерполятора.

Устройство для обработки нечеткой информации (фиг. 1) содержит первый 1, второй 2, третий 3, четвертый 4, пятый 5, шестой 6, седьмой 7, восьмой 8, девятый 9 и десятый 10 регистры, первый 11 и второй 12 регистры признаков, первый 13, второй 14, третий 15, четвертый 16, пятый 17 коммутаторы, арифметико-логический блок 18, первый 19 и второй 20 дешифраторы, первый 21, второй 22 и третий 23 шинные формирователи, блок памяти 24, элемент И 25, группу 26 элементов И, интерполятор 27, информационный вход 28, адресный вход 29, вход синхронизации 29' и информационный выход 30.

В устройстве для обработки нечеткой информации информационные входы первого 1, второго 2, третьего 3, шестого 6, седьмого 7, восьмого 8, девятого 9 и десятого 10 регистров, первого 11 и второго 12 регистров признаков и первые входы элементов И группы 26 подключены к информационным входам 28 устройства и к выходам первого 21, второго 22 и третьего 23 шинных формирователей, выходы первого 1, второго 2, третьего 3, шестого 6 и седьмого 7 регистров соединены соответственно с первым, третьим, пятым, седьмым и девятым информационными входами второго 14 коммутатора, второй, четвертый, шестой, восьмой и десятый информационные входы которого соединены соответственно с инверсными выходами первого 1, второго 2, третьего 3, шестого 6 и седьмого 7 регистров, первый и второй выходы второго 14 коммутатора соединены с первым и вторым информационными входами арифметико-логического блока 18 и с первым и вторым информационными входами первого 13 коммутатора соответственно, управляющий вход второго 14 коммутатора соединен с выходом пятого 5 регистра, информационный вход которого соединен с выходом блока памяти 24, адресный вход которого соединен с выходом четвертого 4 регистра, первый информационный вход которого соединен с входом разрешения записи пятого 5 регистра и с выходом элемента И 25, первый вход которого соединен с входом синхронизации 29' устройства, второй информационный вход 29 четвертого 4 регистра предназначен для записи адресов микрокоманд, выход пятого 5 регистра соединен с входами разрешения записи первого 1, второго 2, третьего 3, шестого 6, седьмого 7, восьмого 8, девятого 9 и десятого 10 регистров, первого 11 и второго 12 регистров признаков, со вторыми входами элементов И группы 26, со вторым входом элемента И 25, с управляющими входами третьего 15, четвертого 16 и пятого 17 коммутаторов, с входом синхронизации третьего 23 шинного формирователя, с информационным входом первого 19 дешифратора и с первым информационным входом второго 20 дешифратора, первый выход первого 19 дешифратора соединен с входом кода операции арифметико-логического блока 18, а второй выход соединен с входом синхронизации первого 21 шинного формирователя, информационный вход которого соединен с выходом результата арифметико-логического блока 18, выход признака равенства операндов которого соединен со вторым информационным входом второго 20 дешифратора, первый выход которого соединен с управляющим входом первого 13 коммутатора, а второй выход второго 20 дешифратора соединен с входом синхронизации второго 22 шинного формирователя, информационный вход которого соединен с выходом первого 13 коммутатора, выходы элементов И группы 26 являются информационными выходами 30 устройства, выход первого 11 регистра признаков соединен с информационным входом третьего 15 коммутатора, выход которого соединен с третьим информационным входом четвертого 4 регистра, выходы восьмого 8 и девятого 9 регистров и инверсный выход десятого 10 регистра соединены соответственно с первым, вторым и третьим информационными входами пятого 17 коммутатора, первый, второй и третий выходы которого соединены соответственно с первым, вторым и третьим входами интерполятора 27, выход второго 12 регистра признаков соединен с информационным входом четвертого 16 коммутатора, выход которого соединен с информационным входом 28 устройства, информационный вход третьего 23 шинного формирователя соединен с выходом интерполятора 27.

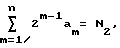

Интерполятор 27 (фиг. 2) содержит операционный усилитель 31, цифроаналоговый преобразователь 32, n входных сопротивлений 331...33n, каждое из которых имеет номер m (m = 1,..., n), величины которых в зависимости от номера m выбраны равными Rm = R02m-1, где n - разрядность обрабатываемых интерполятором двоичных чисел, n сопротивлений цепи отрицательной обратной связи 341. ..34n, каждое из которых имеет номер j (j = 1,..., n), величины которых в зависимости от номера j выбраны равными Rj=R02j-1, n входных аналоговых ключей 351...35n, каждый из которых имеет номер m, n аналоговых ключей цепи отрицательной обратной связи 361. . .36n, каждый из которых имеет номер j аналого-цифровой преобразователь 37, второй вход 38, объединяющий n входов 381. . . 38n для подачи множимого (n-разрядного двоичного числа), каждый из которых имеет номер k (k = 1,..., n) и служит для подачи k-го разряда множимого, третий вход 39, объединяющий n входов 391...39n для подачи множителя (n-разрядного двоичного числа), каждый из которых имеет номер j и служит для подачи j-го разряда множителя, первый вход 40, объединяющий n входов 401... 40n для подачи делителя (n-разрядного двоичного числа), каждый из которых имеет номер m и служит для подачи m-го разряда делителя, выход 41, объединяющий n выходов 411...41n аналого-цифрового блока 37, каждый из которых имеет номер f и служит для выдачи f-го разряда результата.

В интерполяторе 27 n входов цифроаналогового преобразователя 32 являются вторым 38 входом интерполятора, выход цифроаналогового преобразователя 32 соединен с входом каждого m-го входного аналогового ключа 35m, управляющий вход которого является m-м входом 40m интерполятора, выход каждого m-го входного аналогового ключа 35m соединен с вводом m-го входного сопротивления 33m, вывод которого соединен с входом операционного усилителя 31, выход которого соединен с входом аналого-цифрового блока 37 и с входом первого (j = 1) аналогового ключа 361 цепи отрицательной обратной связи, выход j-го (j = 1, . ..,n-1) аналогового ключа 36j цепи отрицательной обратной связи соединен с входом (j+1)-го аналогового ключа 36j+1 цепи отрицательной обратной связи, выход n-го аналогового ключа 36n цепи отрицательной обратной связи соединен с входом операционного усилителя 31, выводы j-го сопротивления 34j цепи отрицательной обратной связи соединены соответственно с входом и выходом j-го аналогового ключа 36j цепи отрицательной обратной связи, управляющий вход которого является j-м входом 39j интерполятора, n выходов аналого-цифрового блока 37 являются n-разрядным выходом 41 интерполятора.

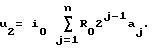

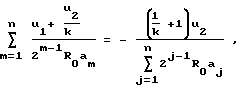

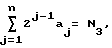

Интерполятор 27 работает следующим образом. Цифроаналоговый преобразователь 32 преобразует множимое N1 (n-разрядное двоичное число), поданное на его входы 381...38n, в напряжение u1, значение которого пропорционально значению N1. Состояние m-го аналогового ключа 35m (m = 1,..., n) определяется значением m-го разряда делителя N2 (n-разрядного двоичного числа), поданного на входы 401...40n интерполятора. При am = 1 аналоговый ключ 35m находится в открытом состоянии, поэтому величина тока, протекающего через m-ое входное сопротивление 33m величиной Rm = R02m-1, вызванного падением напряжения u1-uΣ, равна

При am = 0 аналоговый ключ 35m находится в закрытом состоянии, поэтому ток, протекающий через m-ое входное сопротивление 33m, равен нулю. Операционный усилитель 31 с большим коэффициентом усиления отрицательной обратной связи поддерживает в точке Σ нулевое значение напряжения uΣ. В точке Σ токи im (m = 1,..., n) суммируются. Состояние j-го аналогового ключа 36j (j = 1,. .., n) определяется значением j-го разряда множителя N3 (n-разрядного двоичного числа), поданного на входы 391...39n интерполятора в инверсном коде. При aj = 1 на входе 39j аналогового ключа 36j присутствует  = 0, поэтому он находится в закрытом состоянии и сопротивление j-й ячейки, образованной включенными параллельно друг другу j-м сопротивлением цепи отрицательной обратной связи 34j и j-м аналоговым ключом 36j определяется сопротивлением 34j, величина которого равна Rj=R02j-1. При aj = 0 на входе 39j аналогового ключа 36j присутствует сигнал

= 0, поэтому он находится в закрытом состоянии и сопротивление j-й ячейки, образованной включенными параллельно друг другу j-м сопротивлением цепи отрицательной обратной связи 34j и j-м аналоговым ключом 36j определяется сопротивлением 34j, величина которого равна Rj=R02j-1. При aj = 0 на входе 39j аналогового ключа 36j присутствует сигнал  = 1, который определяет открытое состояние аналогового ключа 36j и нулевое сопротивление j-й ячейки, образованной включенными параллельно друг другу j-м сопротивлением цепи отрицательной обратной связи и j-м аналоговым ключом 36j. Таким образом, сопротивление цепи отрицательной обратной связи, состоящей из n включенных последовательно ячеек, равно сумме их сопротивлений:

= 1, который определяет открытое состояние аналогового ключа 36j и нулевое сопротивление j-й ячейки, образованной включенными параллельно друг другу j-м сопротивлением цепи отрицательной обратной связи и j-м аналоговым ключом 36j. Таким образом, сопротивление цепи отрицательной обратной связи, состоящей из n включенных последовательно ячеек, равно сумме их сопротивлений:

Поэтому напряжение u2 на выходе операционного усилителя определяется соотношением

Аналого-цифровой преобразователь 37 преобразует напряжение u2 в n-разрядное двоичное число N, которое выдается на выходы 411...41n.

Исходя из вышесказанного, определим конкретный вид зависимости значения N, снимаемого с выходов 411...41n от значений двоичных чисел, подаваемых на входы 381. ..38n, 391...39n и 401...40n интерполятора. Функционирование интерполятора описывается следующей системой уравнений:

где N1 - множимое (n-разрядное двоичное число), подаваемое на входы 381. ..38n интерполятора;

λ1 - коэффициент преобразования цифроаналогового преобразователя 32;

u1 - напряжение на выходе цифроаналогового преобразователя 32;

uΣ - напряжение на входе операционного усилителя 31 (в точке Σ );

R0 - сопротивление, определяемое для схемы как минимальное;

am - значение m-го разряда делителя N2 (n-разрядного двоичного числа), подаваемого на входы 401...40n интерполятора;

im - ток, протекающий через m-ое входное сопротивление 33m (m= 1,...,n);

u2 - напряжение на выходе операционного усилителя 31;

aj - значение j-го разряда множителя N3 (n-разрядного двоичного числа), подаваемого на входы 391...39n интерполятора в инверсном коде;

Rо - ток цепи отрицательной обратной связи;

k - коэффициент усиления операционного усилителя 31;

N - результат (n-разрядное двоичное число), снимаемое с 411...41n интерполятора;

λ2 - коэффициент преобразования аналого-цифрового преобразователя 37.

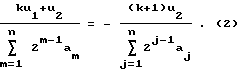

Подставляя значения токов i0 и im (m = 1,...,n) в четвертое уравнение системы (1), с учетом ее пятого уравнения получаем

после упрощения

Учитывая, что

а также первое и шестое уравнения системы (1) имеем

откуда

При использовании операционного усилителя 31 с большим значением коэффициента усиления (k = ∞) первый сомножитель выражения (3) стремится к единице. Выбирая параметры цифроаналогового преобразователя 32 и аналого-цифрового преобразователя 37 таким образом, чтобы отношение их коэффициентов преобразования (λ1/λ2) было равным единице, получим следующую зависимость выходного значения N от входных значений N1, N2 и N3:

Работа устройства для обработки нечеткой информации при выполнении над расплывчатыми переменными операций инверсии, дизъюнкции, конъюнкции, импликации и эквивалентности аналогична работе прототипа.

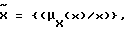

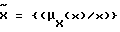

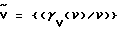

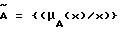

Рассмотрим работу устройства при преобразовании нечеткого множества второго рода в нечеткое множество первого рода. Под нечетким множеством первого рода понимается обычное нечеткое множество  , где μX:x _→ [0;1] - отображение базовых значений x нечеткого множества

, где μX:x _→ [0;1] - отображение базовых значений x нечеткого множества  в единичный отрезок [0;1], которое называется функцией принадлежности нечеткого множества

в единичный отрезок [0;1], которое называется функцией принадлежности нечеткого множества  . Значение функции принадлежности μX(x) для элемента x∈X называется степенью принадлежности. Интерпретацией степени принадлежности является субъективная мера того, насколько элемент x∈X соответствует понятию, смысл которого формализуется нечетким множеством

. Значение функции принадлежности μX(x) для элемента x∈X называется степенью принадлежности. Интерпретацией степени принадлежности является субъективная мера того, насколько элемент x∈X соответствует понятию, смысл которого формализуется нечетким множеством  . Под нечетким множеством второго рода понимается нечеткое множество вида

. Под нечетким множеством второго рода понимается нечеткое множество вида

где  - базовое нечеткое значение для нечеткого множества второго рода

- базовое нечеткое значение для нечеткого множества второго рода  ;

; - нечеткое значение принадлежности базового нечеткого значения

- нечеткое значение принадлежности базового нечеткого значения  нечеткому множеству второго рода

нечеткому множеству второго рода  .

.

Нечеткие множества  и

и  являются нечеткими множествами первого рода. Нечеткие множества второго рода используются при формализации экспертной информации высокой степени неопределенности, описываемой вложенными высказываниями.

являются нечеткими множествами первого рода. Нечеткие множества второго рода используются при формализации экспертной информации высокой степени неопределенности, описываемой вложенными высказываниями.

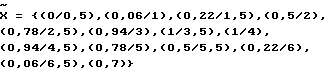

В качестве примера рассмотрим нечеткое множество  , соответствующее, в рамках конкретной задачи, высказыванию эксперта: "ВЕРОЯТНО НОРМА". При этом будем полагать, что нечеткое множество

, соответствующее, в рамках конкретной задачи, высказыванию эксперта: "ВЕРОЯТНО НОРМА". При этом будем полагать, что нечеткое множество

формализует понятие "НОРМА", а нечеткое множество

формализует понятие "ВЕРОЯТНО".

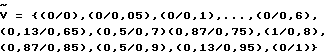

Рассмотрим алгоритм преобразования нечеткого множества второго рода  в нечеткое множество первого рода

в нечеткое множество первого рода  . В нечетком множестве

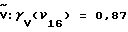

. В нечетком множестве  фиксируется некоторое значение μX(xi)/xi, пусть, например, i = 10, тогда x10 = 5 и μX(x10) = 78. Значение νj принимается равным μX(xi) = μX(x10) = μX(5) = 0,78. Далее определяется γV(νj) = γV(0,78), которое и считается i-м (десятым) значением принадлежности μA(x10) нечеткому множеству

фиксируется некоторое значение μX(xi)/xi, пусть, например, i = 10, тогда x10 = 5 и μX(x10) = 78. Значение νj принимается равным μX(xi) = μX(x10) = μX(5) = 0,78. Далее определяется γV(νj) = γV(0,78), которое и считается i-м (десятым) значением принадлежности μA(x10) нечеткому множеству  . Так как в нечетком множестве

. Так как в нечетком множестве  отсутствует базовое значение νj, равное μX(5) = 0,78, и соответствующее ему значение принадлежности γV(0,78), то необходимо произвести интерполирование. Для этого определяются ближайшие слева и справа базовые значения ν к значению νj = 0,78. В данном случае это значения ν16 = 0,75 и ν17 = 0,8. Соответствующие им значения принадлежности нечеткому множеству

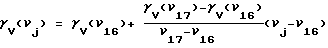

отсутствует базовое значение νj, равное μX(5) = 0,78, и соответствующее ему значение принадлежности γV(0,78), то необходимо произвести интерполирование. Для этого определяются ближайшие слева и справа базовые значения ν к значению νj = 0,78. В данном случае это значения ν16 = 0,75 и ν17 = 0,8. Соответствующие им значения принадлежности нечеткому множеству  и γV(ν17) = 1 . Воспользовавшись интерполяционным многочленом первой степени

и γV(ν17) = 1 . Воспользовавшись интерполяционным многочленом первой степени

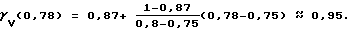

получаем, округляя с точностью до второго знака после запятой:

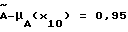

Таким образом, значению x10 = 5 соответствует значение принадлежности нечеткому множеству первого рода  .

.

Рассмотрим работу устройства обработки нечеткой информации при реализации описанного алгоритма преобразования нечеткого множества второго рода в нечеткое множество первого рода.

Выполнение операции начинается с того, что на информационные входы регистра 4 поступает адрес первой микрокоманды операции "Преобразование нечеткого множества второго рода в нечеткое множество первого рода", и по сигналу "Запись" он записывается в регистр 4. С выхода регистра 4 адрес первой микрокоманды подается на адресный вход блока памяти 24. Через время, определяемое типом блока памяти 24, на его выходе появляется первая микрокоманда микропрограммы, реализующей операцию "Преобразование нечеткого множества второго рода в нечеткое множество первого рода". По переднему фронту первого тактового импульса от внешнего генератора синхроимпульсов (ГСИ) первая микрокоманда записывается в регистр 5, с этого момента начинается реализация микропрограммы.

Управляющее поле первой микрокоманды разрешает запись в третий 3 регистр базового значения ν1 нечеткого множества  со входа 28. Одновременно поле "Конец операции" этой микрокоманды поступает на вход элемента И 25 и разрешает прохождение сигналов от ГСИ. Тактовая частота ГСИ подобрана таким образом, чтобы за его период смогла выполниться любая микрокоманда микропрограммы. По отрицательному фронту первого синхроимпульса (СИ) происходит наращивание содержимого регистра адреса 4. Таким образом, пока выполняется первая микрокоманда, на выходе блока памяти 24 появляется вторая микрокоманда.

со входа 28. Одновременно поле "Конец операции" этой микрокоманды поступает на вход элемента И 25 и разрешает прохождение сигналов от ГСИ. Тактовая частота ГСИ подобрана таким образом, чтобы за его период смогла выполниться любая микрокоманда микропрограммы. По отрицательному фронту первого синхроимпульса (СИ) происходит наращивание содержимого регистра адреса 4. Таким образом, пока выполняется первая микрокоманда, на выходе блока памяти 24 появляется вторая микрокоманда.

С приходом второго СИ от ГСИ в регистр 5 записывается вторая микрокоманда, выполнение которой аналогично выполнению первой, только базовое значение ν2 записывается с информационного входа 28 устройства во второй 2 регистр. По отрицательному фронту второго СИ от ГСИ происходит наращивание содержимого регистра 4, вследствие чего на выходе блока памяти 24 появляется третья микрокоманда, которая по переднему фронту третьего СИ записывается в регистр 5, и ее поля поступают на управляющий вход второго 14 коммутатора.

В соответствии с микропрограммой операции "Преобразование нечеткого множества второго рода в нечеткое множество первого рода" на первом выходе коммутатора 14 появляется значение ν1, а на его втором выходе - значение ν2. С выходов коммутатора 14 значения ν1 и ν2 поступают на информационные входы арифметико-логического блока (АЛБ) 18 и первого коммутатора 13. В результате выполнения третьей микрокоманды на выходе АЛБ 18 будет результат операции d21= ν2-ν1.

С приходом четвертого СИ в регистр 5 записывается пятая микрокоманда, по которой абсолютный результат  записывается в восьмой 8 регистр (регистр делителя).

записывается в восьмой 8 регистр (регистр делителя).

В результате выполнения пятой микрокоманды первое значение принадлежности μX(xi) (далее по тексту просто μ1 ) нечеткому множеству  с информационного входа 28 устройства записывается в первый 1 регистр.

с информационного входа 28 устройства записывается в первый 1 регистр.

В результате выполнения шестой микрокоманды на выходе АЛБ 18 появится результат операции δ11= μ1-ν1, знаковый разряд которого седьмой микрокомандой записывается во второй разряд первого 11 регистра признаков, абсолютное значение результата  - в девятый 9 регистр (регистр множимого).

- в девятый 9 регистр (регистр множимого).

В результате выполнения восьмой микрокоманды на выходе АЛБ 18 появится результат операции δ12= μ1-ν2, знаковый разряд которого девятой микрокомандой записывается в первый разряд первого 11 регистра признаков.

В ходе выполнения десятой микрокоманды выдается сигнал на управляющий вход третьего коммутатора 15, с выхода которого на третий информационный вход четвертого 4 регистра поступает адрес первой микрокоманды одной из трех подмикропрограмм, в зависимости от содержимого первого 11 регистра признаков. Если его содержимое "00", то выбирается первая подмикропрограмма - "Выбор следующих базовых значений ν нечеткого множества  ". Если содержимое первого 11 регистра признаков "11", то выбирается вторая подмикропрограмма - "Выбор предыдущих базовых значений ν нечеткого множества

". Если содержимое первого 11 регистра признаков "11", то выбирается вторая подмикропрограмма - "Выбор предыдущих базовых значений ν нечеткого множества  ". При содержимом первого 11 регистра признаков "01" выбирается третья подмикропрограмма - "Интерполяция". Содержимое первого 11 регистра признаков "10" невозможно, так как значение μ1 не может одновременно быть меньше меньшего ν1 и больше большего ν2.

". При содержимом первого 11 регистра признаков "01" выбирается третья подмикропрограмма - "Интерполяция". Содержимое первого 11 регистра признаков "10" невозможно, так как значение μ1 не может одновременно быть меньше меньшего ν1 и больше большего ν2.

Так как базовые значения ν∈V заданы на интервале [0; 1] и ν1 всегда равно нулю, то при первом анализе содержимое первого 11 регистра признаков не может быть "11".

Пусть содержимое первого 11 регистра признаков - "00". Тогда по переднему фронту одиннадцатого СИ от ГСИ первая микрокоманда подмикропрограммы "Выбор следующих базовых значений ν нечеткого множества  " записывается в пятый 5 регистр, и с этого момента начинается реализация подмикропрограммы.

" записывается в пятый 5 регистр, и с этого момента начинается реализация подмикропрограммы.

По первой микрокоманде первой подмикропрограммы содержимое второго 2 регистра νj (в данном случае ν2) переписывается в третий 3 регистр.

По второй микрокоманде первой подмикропрограммы во второй 2 регистр с информационного входа 28 устройства записывается очередное базовое значение νj+1 (в данном случае ν3).

В результате выполнения третьей микрокоманды первой подмикропрограммы на выходе АЛБ 18 будет результат операции dj+1,j= νj+1-νj(d32= ν3-ν2), абсолютное значение которого  записывается четвертой микрокомандой первой подмикропрограммы в регистр 8 делителя.

записывается четвертой микрокомандой первой подмикропрограммы в регистр 8 делителя.

В результате выполнения пятой микрокоманды первой подмикропрограммы на выходе АЛБ 18 появится результат операции нахождения разности между содержимым первого 1 регистра μi (в данном случае μ1) и содержимым третьего 3 регистра νj (в данном случае ν2 ): δi,j= μi-νj(δ12= μ1-ν2).

По шестой микрокоманде первой подмикропрограммы знаковый разряд значения δi,j(δ12) заносится во второй разряд первого 11 регистра признаков, а абсолютное значение  - в регистр 9 множимого.

- в регистр 9 множимого.

В результате выполнения седьмой микрокоманды первой подмикропрограммы на выходе АЛБ 18 появится результат операции нахождения разности между содержимым первого 1 регистра - μi (в данном случае μ1) и содержимым второго 2 регистра νj+1 (в данном случае ν3) : δi,j+1= μi-νj+1(δ13= μ1-ν3) , знаковый разряд которого по восьмой микрокоманде записывается в первый разряд первого 11 регистра признаков.

По девятой микрокоманде первой подмикропрограммы анализируется содержимое первого 11 регистра признаков и в зависимости от результата выбирается одно из трех возможных продолжений микропрограммы.

Вторая подмикропрограмма - "Выбор предыдущих базовых значений ν нечеткого множества  " полностью идентична первой подмикропрограмме с той лишь разницей, что по ее первой микрокоманде содержимое третьего 3 регистра νj+1/ переписывается во второй 2 регистр, а по ее второй микрокоманде в третий 3 регистр с информационного входа 28 устройства записывается предыдущее базовое значение νj нечеткого множества

" полностью идентична первой подмикропрограмме с той лишь разницей, что по ее первой микрокоманде содержимое третьего 3 регистра νj+1/ переписывается во второй 2 регистр, а по ее второй микрокоманде в третий 3 регистр с информационного входа 28 устройства записывается предыдущее базовое значение νj нечеткого множества  .

.

Пусть при очередном анализе содержимое первого 11 регистра признаков оказалось "01". В этом случае по переднему фронту очередного СИ от ГСИ первая микрокоманда подмикропрограммы - "Интерполяция" записывается в регистр 5 и начинается ее выполнение.

По первой микрокоманде третьей подмикропрограммы значение принадлежности γj нечеткому множеству  , соответствующее базовому значению νj, содержащемуся в третьем 3 регистре, записывается в седьмой 7 регистр.

, соответствующее базовому значению νj, содержащемуся в третьем 3 регистре, записывается в седьмой 7 регистр.

По второй микрокоманде третьей подмикропрограммы значение принадлежности γj+1 нечеткому множеству  , соответствующее базовому значению νj+1, содержащемуся во втором 2 регистре, записывается в шестой 6 регистр.

, соответствующее базовому значению νj+1, содержащемуся во втором 2 регистре, записывается в шестой 6 регистр.

В результате выполнения третьей микрокоманды третьей подмикропрограммы на выходе АЛБ 18 будет результат операции нахождения разности между содержимым шестого 6 и седьмого 7 регистров: ρj+1,j= γj+1-γj, знаковый разряд которого по четвертой микрокоманде третьей подмикропрограммы записывается во второй 12 регистр признаков, а абсолютное значение результата  - в регистр 10 множителя.

- в регистр 10 множителя.

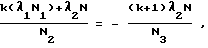

В результате выполнения пятой микрокоманды третьей подмикропрограммы выдается сигнал на управляющий вход пятого коммутатора 17, и значения  и

и  соответственно из восьмого 8, девятого 9 и десятого 10 регистров через пятый коммутатор 17 поступают соответственно на первый 40, второй 38 и третий 39 входы интерполятора 27. В интерполяторе 27 осуществляется операция

соответственно из восьмого 8, девятого 9 и десятого 10 регистров через пятый коммутатор 17 поступают соответственно на первый 40, второй 38 и третий 39 входы интерполятора 27. В интерполяторе 27 осуществляется операция

результат которой hi появляется на выходе интерполятора, и по шестой микрокоманде записывается в шестой 6 регистр.

В результате выполнения седьмой микрокоманды третьей подмикропрограммы содержимое второго 12 регистра признаков через четвертый коммутатор 16 записывается в знаковый разряд шестого 6 регистра.

В результате выполнения восьмой микрокоманды третьей подмикропрограммы на выходе АЛБ 18 будет результат операции суммирования содержимого шестого 6 и седьмого 7 регистров: ωi= γj+hi, (ωi - искомое значение принадлежности базового значения xi нечеткому множеству первого рода  .

.

По девятой микрокоманде третьей подмикропрограммы значения ωi принадлежности нечеткому множеству первого рода  базового значения xi выдается через блок 26 элементов И на информационный выход 30 устройства для записи по соответствующему адресу.

базового значения xi выдается через блок 26 элементов И на информационный выход 30 устройства для записи по соответствующему адресу.

В результате выполнения десятой микрокоманды третьей подмикропрограммы через информационный вход 28 устройства в первый 1 регистр записывается следующее значение μi+1 принадлежности нечеткому множеству  .

.

В результате выполнения одиннадцатой микрокоманды третьей подмикропрограммы на выходе АЛБ 18 появится результат операции нахождения разности между содержимым первого 1 регистра μi+1 и содержимым третьего 3 регистра νj:δi+1,j= μi+1-νj, знаковый разряд которого по двенадцатой микрокоманде третьей подмикропрограммы заносится во второй разряд первого 11 регистра признаков, а абсолютное значение  - в регистр 9 множимого.

- в регистр 9 множимого.

В результате выполнения тринадцатой микрокоманды третьей подмикропрограммы на выходе АЛБ 18 будет результат операции нахождения разности между содержимым первого 1 регистра μi+1 и содержимым второго 2 регистра νj+1:δj+1,j+1= μi+1-νj+1 , знаковый разряд которого по четырнадцатой микрокоманде записывается в первый разряд первого 11 регистра признаков.

По пятнадцатой микрокоманде третьей микропрограммы анализируется содержимое первого 11 регистра признаков и в зависимости от результата выбирается одно из трех возможных продолжений микропрограммы.

Таким образом находятся значения принадлежности ω для всех базовых значений xi∈X (i = 1,...,I) и формируется нечеткое множество первого рода  .

.

Преимуществом устройства для обработки нечеткой информации по сравнению с прототипом является способность в дополнение к операциям, реализуемым прототипом (инверсия, дизъюнкция, конъюнкция, импликация и эквивалентность), осуществлять преобразование нечетких множеств второго рода в нечеткие множества первого рода, что позволяет ему обрабатывать экспертную информацию высокой степени неопределенности.

ИСТОЧНИКИ ИНФОРМАЦИИ:

1. Авторское свидетельство СССР N 1442989.

2. Авторское свидетельство СССР N 1256010.

3. Авторское свидетельство СССР N 1451677.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ СИСТЕМЫ РАДИОСВЯЗИ | 1998 |

|

RU2156032C2 |

| УСТРОЙСТВО СВЕРТКИ ПО ПЕРЕМЕННОМУ МОДУЛЮ | 1991 |

|

RU2051408C1 |

| УСТРОЙСТВО РЕЗЕРВИРОВАНИЯ АКСЕЛЕРОМЕТРОВ В СИСТЕМЕ УПРАВЛЕНИЯ ЛЕТАТЕЛЬНЫМ АППАРАТОМ | 1996 |

|

RU2142645C1 |

| РЕТРАНСЛЯТОР | 1991 |

|

RU2010431C1 |

| УНИВЕРСАЛЬНЫЙ ПАРАЛЛЕЛЬНЫЙ СЧЕТЧИК ПО МОДУЛЮ M - ДЕШИФРАТОР КОЛИЧЕСТВА ЕДИНИЦ В N-РАЗРЯДНОМ ДВОИЧНОМ КОДЕ | 1991 |

|

RU2020744C1 |

| ДЕКОДИРУЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2037272C1 |

| УСТРОЙСТВО ДЛЯ РЕКОНФИГУРАЦИИ МНОГОМАШИННОГО ВЫЧИСЛИТЕЛЬНОГО КОМПЛЕКСА | 1991 |

|

RU2022342C1 |

| АССОЦИАТИВНЫЙ ВЫЧИСЛИТЕЛЬ СМЕЩЕНИЯ ЦЕНТРА ТЕКУЩЕГО ИЗОБРАЖЕНИЯ ОТ ЦЕНТРА ЭТАЛОННОГО | 1991 |

|

RU2029358C1 |

| УСТРОЙСТВО ЗАЩИТЫ ПАМЯТИ | 1990 |

|

RU2022343C1 |

| УСТРОЙСТВО ДЛЯ ОТСЛЕЖИВАНИЯ КОНТУРОВ ДВУМЕРНЫХ ОБЪЕКТОВ | 1991 |

|

RU2050594C1 |

Изобретение относится к вычислительной технике и может применяться в системах управления в качестве спецвычислителя с целью принятия решений в условиях неопределенности, а также при оперативном управлении технологическими процессами по нечетким алгоритмам. Технический результат изобретения заключается в возможности выполнения устройством преобразований нечеткого множества второго рода в нечеткое множество первого рода. Устройство для обработки нечеткой информации содержит десять регистров 1, ..., 10, два регистра признаков 11, 12, пять коммутаторов 13, ..., 17, арифметико-логический блок 18, два дешифратора 19, 20, три шинных формирователя 21, ..., 23, блок памяти 24, элемент 25 И, группу 26 элементов И, интерполятор 27. 2 ил.

Устройство для обработки нечеткой информации, содержащее пять регистров, два коммутатора, арифметико-логический блок, два дешифратора, два шинных формирователя, блок памяти, элемент И, группу элементов И, причем информационные входы первого, второго, третьего регистров и первые входы элементов И группы подключены к информационным входам устройства и выходам первого и второго шинных формирователей, выход первого регистра соединен с первым информационным входом второго коммутатора, инверсный выход первого регистра соединен со вторым информационным входом второго коммутатора, выход второго регистра соединен с третьим информационным входом второго коммутатора, инверсный выход второго регистра соединен с четвертым информационным входом второго коммутатора, выход третьего регистра соединен с пятым информационным входом второго коммутатора, инверсный выход третьего регистра соединен с шестым информационным входом второго коммутатора, первый и второй выходы которого соединены с первым и вторым информационными входами арифметико-логического блока и первым и вторым информационными входами первого коммутатора соответственно, управляющий вход второго коммутатора соединен с выходом пятого регистра, информационный вход которого соединен с выходом блока памяти, адресный вход которого соединен с выходом четвертого регистра, первый информационный вход которого соединен с входом разрешения записи пятого регистра и выходом элемента И, первый вход которого соединен с входом синхронизации устройства, второй информационный вход четвертого регистра предназначен для записи адресов микрокоманд, выход пятого регистра соединен с входами разрешения записи первого, второго, третьего регистров, вторыми входами элементов И группы, вторым входом элемента И, информационным входом первого дешифратора и первым информационным входом второго дешифратора, первый выход первого дешифратора соединен с входом кода операции арифметико-логического блока, а второй выход соединен с входом синхронизации первого шинного формирователя, информационный вход которого соединен с выходом результата арифметико-логического блока, выход признака равенства операндов которого соединен со вторым информационным входом второго дешифратора, первый выход которого соединен с управляющим входом первого коммутатора, а второй выход второго дешифратора соединен с входом синхронизации второго шинного формирователя, информационный вход которого соединен с выходом первого коммутатора, выходы элементов И группы являются информационными выходами устройства, отличающееся тем, что оно дополнительно содержит пять регистров, два регистра признаков, три коммутатора, интерполятор, шинный формирователь, причем информационные входы шестого, седьмого, восьмого, девятого и десятого регистров, первого и второго регистров признака, выход третьего шинного формирователя, выход четвертого коммутатора подключены к информационным входам устройства, выход шестого регистра соединен с седьмым информационным входом второго коммутатора, инверсный выход шестого регистра соединен с восьмым информационным входом второго коммутатора, выход седьмого регистра соединен с девятым информационным входом второго коммутатора, инверсный выход седьмого регистра соединен с десятым информационным входом второго коммутатора, выход первого регистра признаков соединен с информационным входом третьего коммутатора, выход которого соединен с третьим информационным входом четвертого регистра, управляющий вход третьего коммутатора соединен с выходом пятого регистра, управляющим входом четвертого коммутатора и управляющим входом пятого коммутатора, выход восьмого регистра соединен с первым информационным входом пятого коммутатора, выход девятого регистра соединен со вторым информационным входом пятого коммутатора, инверсный выход десятого регистра соединен с третьим информационным входом пятого коммутатора, первый, второй и третий выходы которого соединены с первым, вторым и третьим входами интерполятора соответственно, выход которого соединен с входом третьего шинного формирователя, вход синхронизации которого соединен с входами разрешения записи шестого, седьмого, восьмого, девятого и десятого регистров, первого и второго регистров признака и с выходом пятого регистра, информационный вход четвертого коммутатора соединен с выходом второго регистра признаков.

| Устройство для выполнения операций над расплывчатыми операндами | 1986 |

|

SU1451677A1 |

| Устройство для сравнения двух нечетких величин | 1986 |

|

SU1442989A1 |

| US 4192010 A, 04.03.1980 | |||

| US 5262968 A, 16.11.1993. | |||

Авторы

Даты

2000-10-27—Публикация

1998-06-22—Подача