Процессор относится к области аналоговой вычислительной технике и автоматике. Сущность изобретения: процессор содержит N-разрядный буферный регистр, n сумматоров кодовых единиц (по количеству входных информационных каналов), n цифровых компараторов и ключей, N=0,5(n-1)n аналоговых компараторов, входы которых соединены с информационными входами процессора по принципу "каждый со всеми", а выходы соединены с входами буферного регистра, инвертирующие и неинвертирующие выходы регистра сгруппированы в n групп, выходы каждой группы соединены с входами соответствующего сумматора кодовых единиц.

Изобретение относится к области аналоговой вычислительной техники и автоматики и может быть использовано для рангового мультиплексирования и демультиплексирования сигналов, для адресной идентификации сигнала заданного ранга, для селекции аналогового сигнала заданного ранга с идентификацией входа, на который воздействует выделенный сигнал, для воспроизведения полных классов предикатных, аргументных и непрерывно-логических функций, для селекции минимального, медианного или максимального сигналов из нескольких переменных и др. ( авт. св. СССР N 637810, кл. G 06 F 7/08, 1978 прототип)

Цель изобретения повышение нагрузочной способности процессора при сохранении функциональных возможностей прототипа.

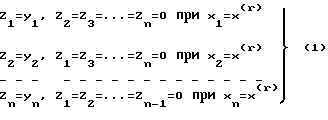

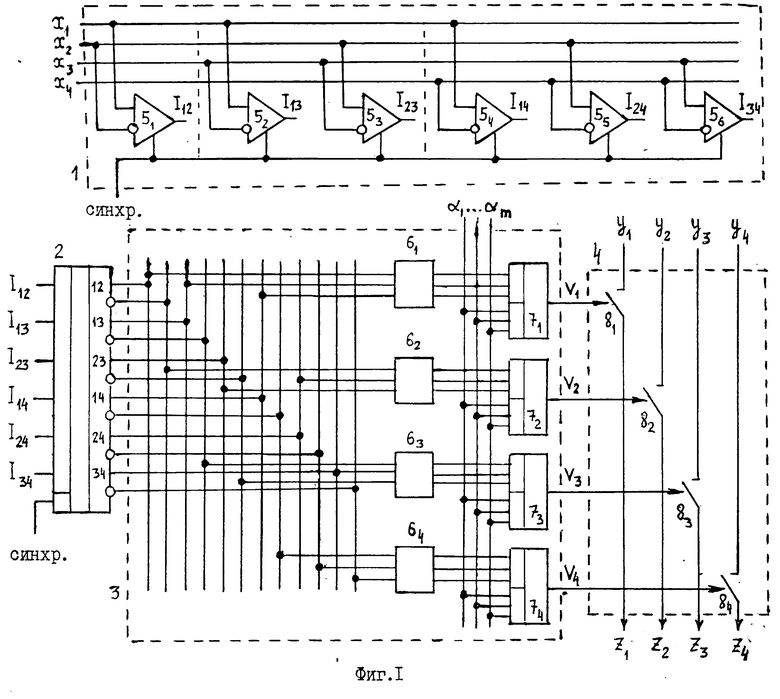

Схема процессора при n=4 приведена на фиг.1. Процессор содержит компараторный блок 1, буферный регистр 2, блок цифровой обработки 3 и коммутационный блок 4. Компараторный блок содержит N=0,5(n-1)n стробируемых аналоговых компараторов 51-5n, входы которых присоединены к входным шинам процессора по принципу сравнения входных сигналов x1,xn, подаваемых на входные шины, по принципу "каждый со всеми". Компараторный блок преобразует множество аналоговых входных сигналов x1,xn во множество бинарных сигналов I12, I13, I(n-1)n (выходные сигналы аналоговых компараторов), где Iij=I(xi-xj) есть единичная функция равная нулю при xi<xj и единице при xi>xj. Множество бинарных сигналов Iij запоминается в N-разрядном буферном регистре 2, который имеет N неинвертирующих Iij и N инвертирующих  выходов, где

выходов, где  1-Iij= I(xj-xi).

1-Iij= I(xj-xi).

Все 2N=(n-1)n выходов регистра 2 группируются в n групп, каждая из которых включает в себя n-1 выходных выводов регистра. Группы формируются следующим образом. Каждой i-й (i= 1,2,n) группе выводов соответствует i-я входная шина процессора (нумерация входных шин совпадает с индексацией входных переменных xi).

При построении компараторного блока 1 по принципу "каждый со всеми" к каждой i-й входной шине процессора присоединено n-1 входов различных компараторов 5, количество которых равно n-1 (i-я адресная группа компараторов). Группировка выходов регистра 2 осуществляется по признаку их принадлежности к i-й адресной группе компараторов. При этом неинверсным и инверсным входам адресных групп компараторов соответствуют неинвертирующие и инвертирующие в соответствующей группе выходов регистра 2.

Кодовая комбинация сигналов с каждой i-й группы выходов регистра 2 подается на i-й сумматор единиц 6i (i=1,2,n), который воспроизводит операции взвешивания кода (подсчет числа единиц в двоичном параллельном коде) и представления этого числа в двоичном параллельном коде.

Выходные коды сумматоров единиц 61-6n подаются на первые входы цифровых компараторов 71-7n, на вторые входы которых поступает код задания ранга r ∈ 1,2, n} где r есть порядковый номер входного сигнала xi=x(r) в последовательности x(1), x(2),x(n), полученной ранжированием входных переменных x1, x2,xn в порядке их неубывания.

Код ранга r задается кодированием числа r-1, представленного в двоичной системе счисления α1...αm. Равенство кодов, подаваемых на входы цифрового компаратора 7i, индицируется наличием на его выходе логической единицы Vi, воздействующей на управляющий вход аналогового ключа 8i в коммутационном блоке 4.

Коммутационный блок 4 содержит n выходных шин, в каждую из которых включен один аналоговый ключ 8i (i=1,2,n).

При равенстве кода, подаваемого на цифровые компараторы 7i с выходов сумматора единиц 6i и кода  , задающего ранг r, на управляющий вход i-го ключа 8i с выхода цифрового компаратора 7i поступает логическая единица Vi=1, ключ 8i замыкается (при этом для остальных ключей Vj=0, т. е. они остаются разомкнутыми) и идентифицирующий сигнал yi проходит на i-й выход Zi процессора.

, задающего ранг r, на управляющий вход i-го ключа 8i с выхода цифрового компаратора 7i поступает логическая единица Vi=1, ключ 8i замыкается (при этом для остальных ключей Vj=0, т. е. они остаются разомкнутыми) и идентифицирующий сигнал yi проходит на i-й выход Zi процессора.

Процессор построен на стандартной цифровой элементной базе, выпускаемой отечественной промышленностью в виде логических микросхем.

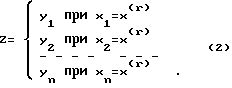

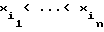

Таким образом, процессор воспроизводит функцию идентификации

и селекции (при y1=x1,yn=xn) аналоговых сигналов xi ∈x1,xn} заданного ранга r с идентификацией адреса этого сигнала xi=x(r) в кортеже (x1,xn) входных сигналов (с идентификацией входа, на который воздействует выделенный сигнал).

Путем коммутационного программирования процессор воспроизводит ряд операций и функций более низкой функциональной иерархии.

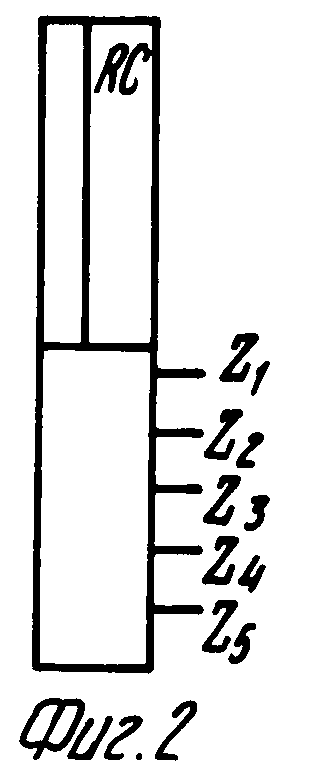

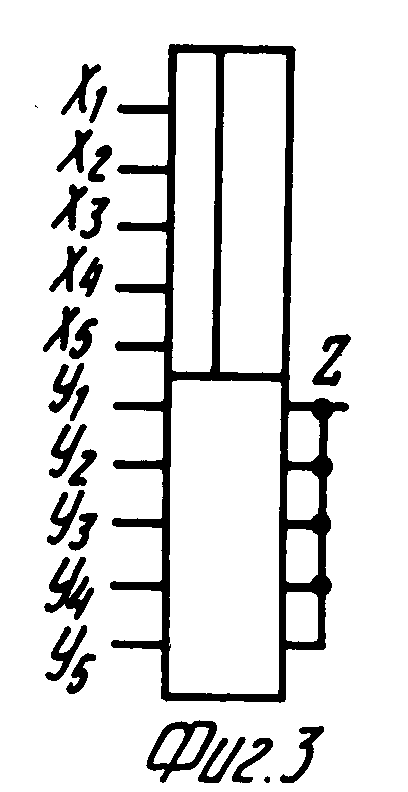

На фиг.2 представлено условное изображение базовой схемы процессора при n= 5, которая является ранговым коммутатором (класс RC). При объединении в базовой схеме (фиг.2) выходных выводов приходим к схеме рангового мультиплексора, изображенного на фиг.3, для которой

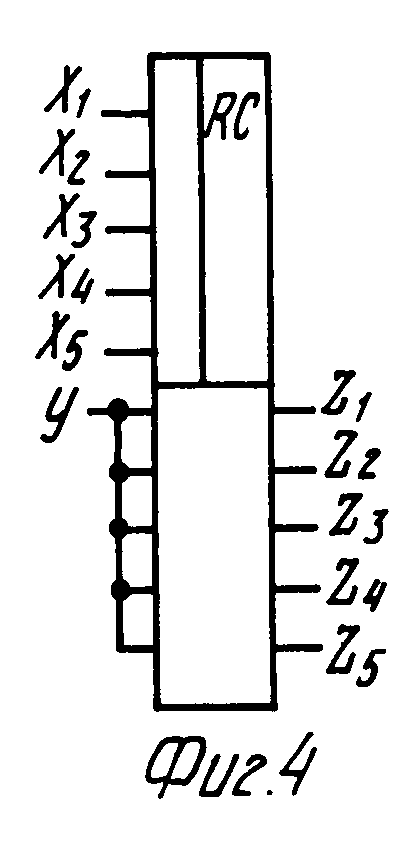

При включении входных переключательных выводов процессора в соответствии с фиг. 4 приходим к схеме адресного идентификатора (ранговый демультиплексор), для которой функция преобразования определяется выражением (1) при y1= y2=yn=y.

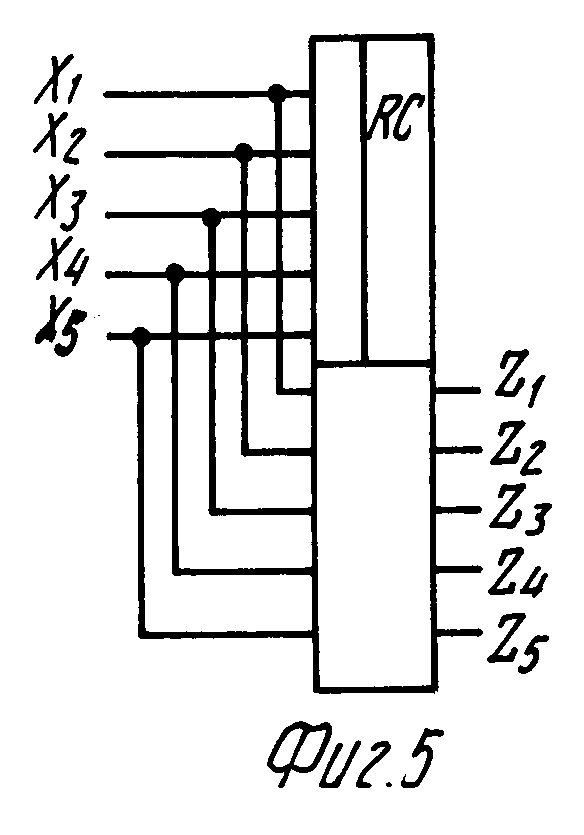

При отождествлении входных переменных xi с идентифицирующими сигналами yi приходим к схеме рангового селектора (фиг.5) с идентификацией входа, на который воздействует выделенный сигнал xi=x(r), для которой воспроизводимая функция определяется выражением (1) при y1=x1, yn=xn.

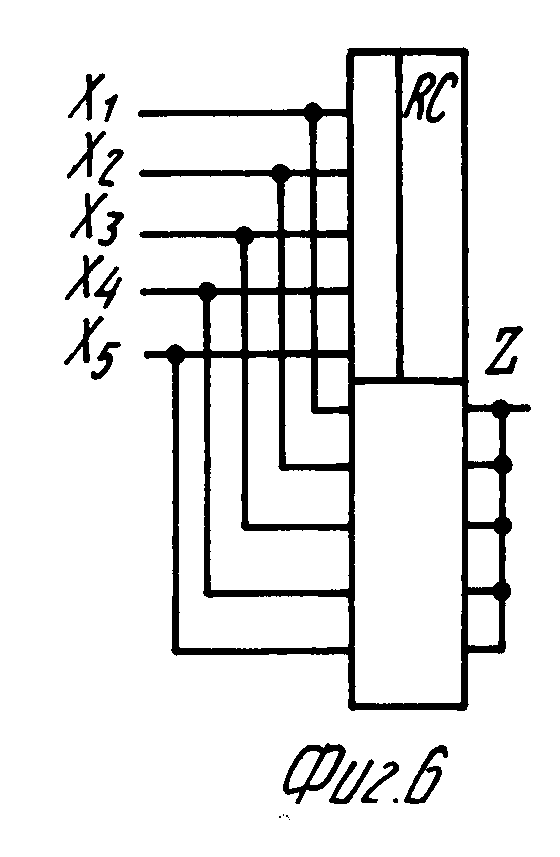

При объединении в схеме по фиг.5 выходных приходим к схеме рангового селектора по фиг.6, воспроизводящего функции Z=x(r), r=1,2,n. При r=1, r=m, r= n ранговый селектор соответственно воспроизводит многоместные операции непрерывной логики: Z=x(1)=min(x1,xn), Z=x(m)=med(x1,xn), Z=x(n)=max(x1,xn селектирования (выбора) минимального, медианного и максимального сигнала из n переменных.

Процессор в мультиплексорном включении (фиг.3) путем коммутационного программирования, фиксацией и отождествлением заданных переменных воспроизводит полные классы предикатных, аргументных, предикатно-аргументных и непрерывно-логических функций, являющихся подклассом аргументных функций.

В предложенной схеме искомая функция воспроизводится за один такт, задаваемый по синхронизирующим входам процессора.

Выходное сопротивление в отличие от прототипа для любых ситуационных отношений переменных  определяется сопротивлением одного замкнутого ключа 8i, что повышает его нагрузочную способность и увеличивает быстродействие (задержка, вносимая сопротивлением ключа зашунтированного паразитной емкостью, равна одной единице).

определяется сопротивлением одного замкнутого ключа 8i, что повышает его нагрузочную способность и увеличивает быстродействие (задержка, вносимая сопротивлением ключа зашунтированного паразитной емкостью, равна одной единице).

Изобретение относится к аналоговой вычислительной технике и автоматике и может быть использовано для рангового мультиплексирования и демультиплексирования, для адресной идентификации сигналов заданного ранга, для селекции сигналов заданного ранга и др. Целью изобретения является повышение нагрузочной способности. Процессор содержит буферный регистр, цифровые компараторы, ключи, сумматоры и компараторный блок, состоящий из аналоговых компараторов. 6 ил.

Процессор для адресно-ранговой идентификации и селекции аналоговых сигналов, содержащий N-разрядный буферный регистр, n цифровых компараторов и ключи, управляющие входы которых соединены с выходами одноименных цифровых компараторов, отличающийся тем, что в него введены n сумматоров и компараторный блок, состоящий из N аналоговых компараторов, где N 0,5 (n-1)n, причем инвертирующие и неинвертирующие входы аналоговых компараторов соединены соответственно с информационными входами процессора, выходы аналоговых компараторов подключены к соответствующим входам буферного регистра, i-я группа  инвертирующих и неинвертирующих выходов буферного регистра соединена с входами i-го сумматора, выходы которого подключены к первым входам i-го цифрового компаратора, вторые входы цифровых компараторов являются входами задания значения ранга процессора, входы задания идентифицирующих переменных процессора соединены с информационными входами ключей, выходы которых являются выходами процессора.

инвертирующих и неинвертирующих выходов буферного регистра соединена с входами i-го сумматора, выходы которого подключены к первым входам i-го цифрового компаратора, вторые входы цифровых компараторов являются входами задания значения ранга процессора, входы задания идентифицирующих переменных процессора соединены с информационными входами ключей, выходы которых являются выходами процессора.

| Устройство для питания нагрузки | 1976 |

|

SU637910A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1997-10-20—Публикация

1994-03-14—Подача