U12.1 Ug®Uio Не при 0 t Т/4 и Т/2 t ЗТ/4 ;

U 12.2 XlAX2

Ul2.3 XlftX2

О при и Ue при Т/4 t Т/2 ; О при 0 t Т/4 и Т/2 t Т ; Ue при 3T/4t T; |0 при 0 t ЗТ/4.

| название | год | авторы | номер документа |

|---|---|---|---|

| Регулятор статического компенсирующего устройства | 1988 |

|

SU1584032A1 |

| Автоматический регулятор компенсирующего устройства | 1990 |

|

SU1704145A1 |

| Устройство для измерения скорости изменения переменного напряжения | 1990 |

|

SU1780030A1 |

| Широтно-импульсный модулятор для управления усилителем мощности | 1989 |

|

SU1718375A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ АКТИВНОЙ И РЕАКТИВНОЙ СОСТАВЛЯЮЩИХ ТОКА | 1990 |

|

RU2018138C1 |

| Устройство регулирования компенсатора реактивной мощности | 1990 |

|

SU1830524A1 |

| Измерительный преобразователь составляющих основной гармоники переменного тока | 1989 |

|

SU1689862A2 |

| Цифровой измеритель мощности переменного тока | 1988 |

|

SU1511702A1 |

| Устройство для управления весовым дозатором | 1984 |

|

SU1272313A1 |

| Корреляционный измеритель фазовой постоянной цепи | 1988 |

|

SU1624348A1 |

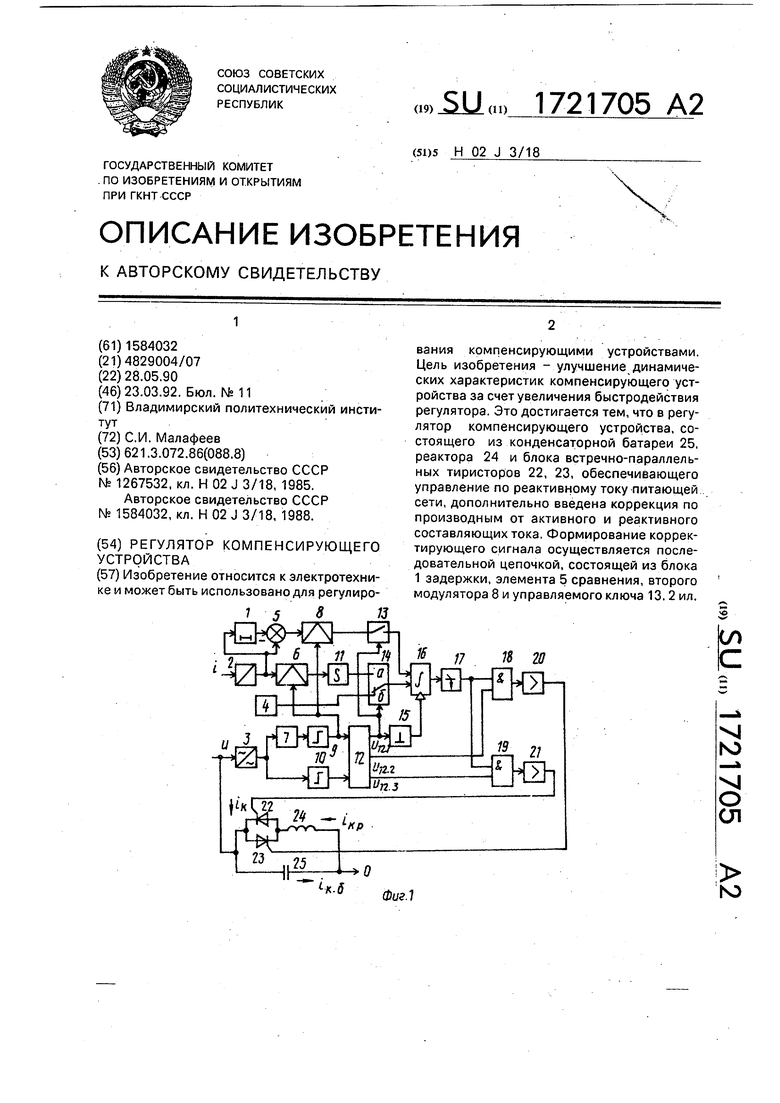

Изобретение относится к электротехнике и может быть использовано для регулирования компенсирующими устройствами. Цель изобретения - улучшение динамических характеристик компенсирующего устройства за счет увеличения быстродействия регулятора. Это достигается тем, что в регулятор компенсирующего устройства, состоящего из конденсаторной батареи 25, реактора 24 и блока встречно-параллельных тиристоров 22, 23, обеспечивающего управление по реактивному току питающей сети, дополнительно введена коррекция по производным от активного и реактивного составляющих тока, Формирование корректирующего сигнала осуществляется последовательной цепочкой, состоящей из блока 1 задержки, элемента 5 сравнения, второго модулятора 8 и управляемого ключа 13. 2 ил.

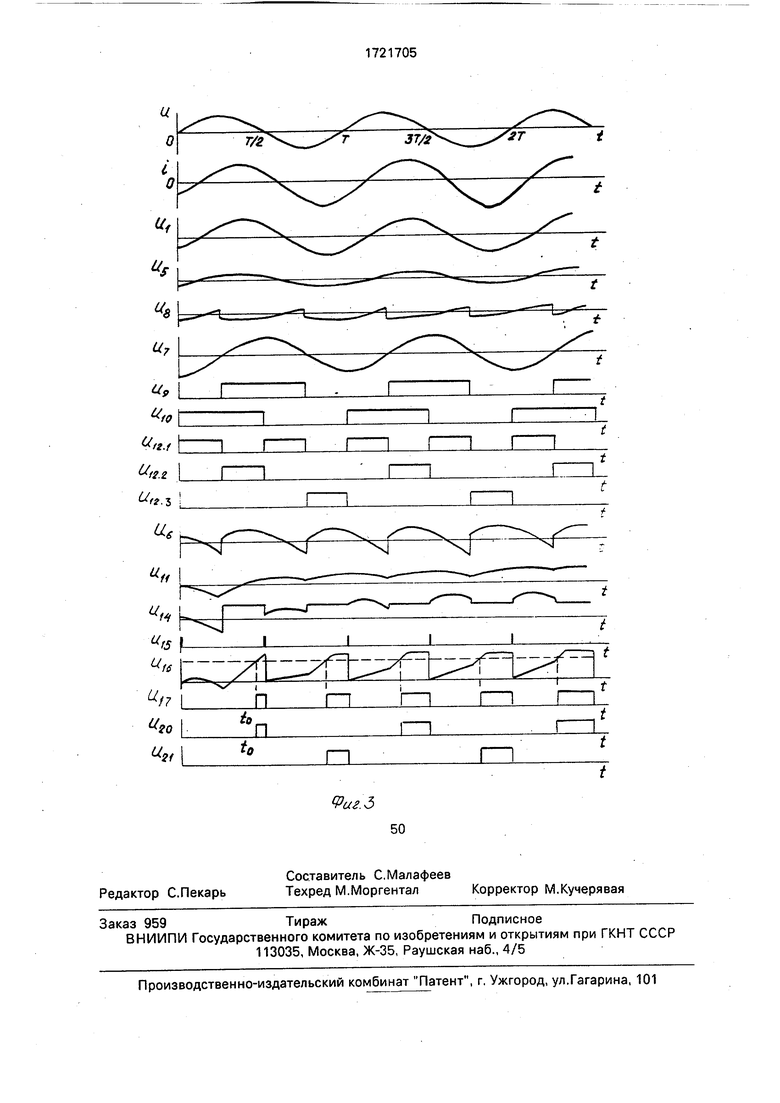

Импульсы U12.1 с первого выхода логического блока 12 поступают на вход формирователя 16 импульсов сброса, на выходе которого действуют короткие импульсы Uis в моменты, соответствующие положительным фронтам импульсов U12.1, т.е. в моменты и .

Выходной сигнал Ug первого релейного элемента управляет первым 6 и вторым 8 модуляторами. При 1) коэффициенты передачи первого 6 и второго 8 модуляторов равны , а при они равны

.

Импульсы IJ12.1 с первого выхода логического блока 12 управляют коммутатором 14 и управляемым ключом 13. При Ui2. переключающий элемент коммутатора 14 находится в положении а, а управляемый ключ 13 разомкнут. При Ui2. переключающий элемент коммутатора 14 находится в положении б, а управляемый ключ 13 замкнут.

Импульсы U 12.2 и U12.3 с второго и третьего выходов логического блока 12 поступают на вторые вход ментов И 18 и 19 обеспечивается разре ние тиристора 23 т 25 , а тиристора .

Ток питающей элект 30 i lMSin (yt+t/0.

где IM-амплитуда;

1/) - фазовый сдвиг напряжения,

35 преобразуется с помощ образователя 1 тока в н

где К2 -коэффициент п 40 преобразователя 1 тока

Напряжение U2 пос вого модулятора 6, кото риодический сигнал

Ue

fclM sin(ftrt + V) при Ug Ue(T/4 t 3T/4) ;

- sin (tot + V) при Ug 0 (0 t Т/4 и ЗТ/4 t Т) ,

пают на вторые входы логических элементов И 18 и 19. Таким образом, обеспечивается разрешение на включение тиристора 23 только в интервале , а тиристора 22 - в интервале .

Ток питающей электрической сети i lMSin (yt+t/0.0)

где IM-амплитуда;

1/) - фазовый сдвиг тока относительно напряжения,

преобразуется с помощью первичного преобразователя 1 тока в напряжение

,

где К2 -коэффициент передачи первичного преобразователя 1 тока.

Напряжение U2 поступает на вход первого модулятора 6, который формирует периодический сигнал

с периодом Т/2. Среднее значение выходного сигнала первого модулятора б за период его повторения Т/2 равно

9 ЗТ/4о 1м K-J

/ iMSinuHdt Sin V . Т т/4п

(2)

Таким образом, постоянная составляющая выходного сигнала первого модулятора 6 пропорциональна реактивной составляющей тока сети.

Сигнал Ue с выхода первого модулятора 6 поступает на вход интегратора 11, который формирует сигнал

I Ue(t)dt.

Так как напряжение Ue(t) представляет собой сумму постоянной „составляющей Deep (2) и высших гармоник Ue, то выходной сигнал интегратора 11 также можно представить в виде суммы постоянной составля- ющей Uii (0), отражающей начальные условия линейно изменяющегося напряжения

Uiicp(t) KnUecpt 2КгКз1м

п

,

и высших гармоник

/ U6(t)dt. о

При этом амплитуды высших гармонических составляющих на выходе интегратора 11 ослабляются в число раз, пропорциональное номеру гармоники.

Следовательно, при наличии реактивной составляющей тока напряжение на выходе интегратора 11 возрастает со скоростью, пропорциональной величине этой составляющей. Знак выходного сигнала интегратора 11 определяется знаком реактивного тока, При гр 0 среднее значение импульсов на входе интегратора 11 равно 0 и, следовательно, среднее значение его выходного сигнала не изменяется.

Коммутатор 14 подключает попеременно к второму входу второго интегратора 16 со сбросом выходной сигнал интегратора 11

U8

К2 Л IM (t) sin (ал - V) при Ub Ue (Т/4 t 3T/4) ;

- К2 A IM (t) sin (col -гр) при Ub 0 (0 t Т/4 и 3t/4 t Т),

0

5

0

и опорное напряжение Uo. При 0 и на первом выходе логического блока 12 действует сигнал Ui2., который устанавливает переключающий элемент коммутатора 14 в положение а. Поэтому в указанные интервалы времени к второму входу второго интегратора 16 подключен выход первого интегратора 11. При и сигнал на первом выходе логического блока 12 Ui2., переключающий элемент коммутатора 14 находится в положении б и к второму входу второго интегратора 16 подключен выход источника 4 опорного напряжения Uo.

Выходной сигнал IJ2 первичного преобразователя тока поступает на вход блока 1 задержки, который выполняет задержку сигнала U2, пропорционального тока i, на период Т.

Сигнал 1Н с выхода блока 1 задержки поступает на вычитающий вход элемента 5 сравнения, на суммирующем входе которо- го действует сигнал U2(t). При этом на выходе элемента 5 сравнения формируется сигнал

U5 U2-Ul K2lM(t)sin()-K2IM( t-T)sln(u t- (t)-lM(t-T) sin(ftj t- t/)K2 A lMSin( an- /).

Таким образом, на выходе элемента 5 сравнения формируется напряжение, пропорциональное разности сигналов, пропорциональных току сети, задержанному на период. Если амплитуда тока постоянна, то сигнал на выходе элемента 5 сравнения равен 0. Если амплитуда тока линейно возрастает, то на выходе элемента 5 формируется переменное напряжение, амплитуда которого пропорциональна скорости изменения тока, а фаза совпадает с фазой тока. Если амплитуда тока линейно уменьшается, то на выходе элемента 5 сравнения формируется напряжение, амплитуда которого пропорциональна скорости изменения тока, а фаза сдвинута на 180 эл.град. относительно сигнала переменного тока. Выходной, сигнал элемента 5 сравнения поступает на информационный вход второго модулятора 8, который формирует периодический сигнал

Сигнал с выхода второго модулятора 8 через управляемый ключ 13 поступает на первый вход второго интегратора 16 со сбросом. Так как управляемый ключ 13 замкнут в интервалы времени 0 t Т/4 и Т/2 , а в интервалах времени и разомкнут, то выходной сигнал Us второго модулятора 8 подключается к входу второго интегратора 16 со сбросом в интервалах времени и .

На второй вход второго интегратора 16 со сбросом поступает выходное напряжение коммутатора 14.

Формирование импульсов управления тиристорами происходит в каждом полупериоде следующим образом. В начале каждого полупериода ( и t Т/2) второй интегратор 16 со сбросом устанавливается выходным импульсом формирователя 15 импульсов сброса в исходное состояние, соответствующее U . В интервале времени переключающий элемент коммутатора 14 установлен в положение а, так как сигнал Ui2.. Следовательно, к первому и второму входам второго интегратора 16 со сбросом подключены выходы соответственно первого и второго модуляторов. В результате на выходе второго интегратора 16 со сбросом формируется сигнал

Uie(t)Ki6/ Un(t)+ Un(0)+Ue(t)dt

Ki6/ Uiicp(t)+Un(0)dt+

о

+ KnKi6 // U6(t)dt+ о о

+ K2Ki6 / Aliyisin(wt-)dt,

где Kie - коэффициент передачи второго интегратора 16 со сбросом.

При выходное напряжение второ- го интегратора 16 со сбросом достигает значения

-гТ/4

Ui6 (7)K16 / UncpW 4о

+ Un(0)dt+KnKi6 / / U6(t)dt+ о о

Т Д1м COS If) К2К1бТ Д1|у| Sin t/

2312n

Второе слагаемое в правой части выра- жения (3) представляет собой двойной интеграл от переменной составляющей напряжения на выходе модулятора за четверть периода. Так как при прохождении переменного сигнала через два интегратора

амплитуды высших гармоник уменьшаются в число раз, пропорциональное квадрату частоты (например, пятая гармоника ослабляется в 25 раз, а седьмая - в 49 раз), то вторым слагаемым в правой части (3) можно пренебречь и записать уравнение (3) в виде

и16ф

Т/4

Kie / UiicP(t)+Un(0)dt+

K2Ki6 Т А1м cos ip K2Ki6 T Д IM sin t/) 2л2л

(4)

Первое слагаемое в выражении (4) представляет собой интеграл от реактивной составляющей тока электрической сети, второе слагаемое пропорционально скорости изменения активной составляющей тока сети, а третье слагаемое пропорционально скорости изменения реактивной составляющей тока.

Следовательно, в момент времени на выходе второго интегратора со сбросом формируется управляющий сигнал, представляющий собой сумму напряжений, пропорциональных интегралу от реактивного тока сети и производным от активной и реактивной составляющих тока.

При происходит изменение сигнала на первом выходе логического блока 12 с Ue до 0. В интервале на первом выходе логического блока 12 действует сигнал Ui2.. При этом переключающий элемент коммутатора 14 находится в положении б и к входу второго интегратора 16 со сбросом подключен источник опорного напряжения Do. В результате выходной сигнал второго интегратора 16 со сбросом линейно возрастает от значения Ui6(T/4) в соответствии с выражением

Т/4

Ui6(t)Ki6 / UiicP(t)+Un(0)dt+

foKie Т A IM cos V К2К16 Т Д IM sin p

2л

+

2л

+

50

+ Ki6Uo(t- |).

(5)

При достижении выходным напряжением второго интегратора 16 со сбросом в момент времени to напряжения Un переключения порогового элемента 17 происходит срабатывание последнего, т.е. его выходной сигнал скачком изменяется от 0 до Ue. Сигнал поступает на объединенные первые входы первого 18 и второго 19 логических элементов И, на вторых входах которых действуют сигналы с второго и третьего выходов логического блока 12 соответственно Ui2. (на втором входе логического элемента И 18) и Ui2. (на втором входе второго логического элемента И 19). Следовательно, высокий потенциал повторяется на выходе первого элемента И 18. Импульс с выхода первого элемента И 18 через первый формирователь 20 импульсов управления поступает на управляющий вход второго тиристора 23, потенциал на аноде которого при 0 t T/2 положительный.

При работа устройства проис- ходит аналогично, но импульс управления с выхода порогового элемента 17 через второй логический элемент И 19 и второй формирователь 21 импульсов управления поступает на управляющий вход первого ти- ристора 22, потенциал на аноде которого положительный.

Статическая характеристика устройства при постоянной амплитуде тока, т.е. Л , имеет вид

а п Г1 - (6)

Из уравнения (6) следует, что угол вклю- чения тиристоров изменяется от п при Un( до л 12 при Un(0) Do.

Компенсация реактивной составляющей тока нагрузки происходит следующим образом. Основную гармонику тока питаю- щей электрической сети (1) можно представить в виде суммы трех составляющих

i ia+ip+iK,

где ia - активная составляющая, la livicos slrmn;

ip - реактивная составляющая основной гармоники, ip li /isin ч/ cos аи;

IK - ток компенсирующего устройства.

Ток компенсирующего устройства в свою очередь является суммой двух составляющих: нерегулируемого тока конденсаторной батареи 25, опережающего напряжение на 90 эл.град.

к.б. U.6COSW t,

и регулируемого тиристорами тока реактора 24, основная гармоника которого равна

к.р I к.р COS Urt.

В исходном состоянии в установившем- ся режиме при t/ 0 напряжение на выходе первого интегратора 11 содержит постоянную составляющую Un(0), за счет которой формируются импульсы управления с такой фазой, при которой ток компенсирующего

устройства по модулю равен, а по фазе противоположен реактивной составляющей тока нагрузки. При этом обеспечивается полная компенсация реактивного тока нагрузки.

При изменении, например при увеличении индуктивного тока нагрузки ( ifxG), происходит уменьшение постоянной составляющей Uiicp на выходе первого интегратора 11. В результате- уменьшается управляющий сигнал на втором входе второго интегратора 16 со сбросом. Кроме того, в течение переходного процесса на первом входе второго интегратора 16 со сбросом в интервалах времени и действует сигнал, интеграл от которого пропорционален сумме производных от активной и реактивной составляющих тока.

Уменьшение сигнала на выходе второго интегратора 16 со сбросом приводит в соответствии с уравнением (6) к увеличению угла включения тиристоров 22 и 23 и, следовательно, уменьшению индуктивного тока iK.p, протекающего через реактор 24. Так как емкостной ток к.б, протекающий через конденсаторую батарею 25, остается неизменным, а ток к.р через реактор уменьшается, то, следовательно, возрастает емкостной ток U компенсирующего устройства. Это приводит к уменьшению реактивного тока питающей сети. Уменьшение постоянной составляющей на выходе первого интегратора 11 происходит до момента полной компенсации реактивного тока нагрузки. При этом на выходе первого интегратора устанавливается новое значение постоянной составляющей Un(0), которая определяет углы включения тиристоров 22 и 23, при которых достигается полная компенсация реактивного тока нагрузки.

В случае перекомпенсации ( 1/кО) происходит увеличение постоянной составляющей Uiic.p на выходе первого интегратора 11, уменьшение углов включения тиристоров 22 и 23 и, следовательно, увеличение индуктивного тока через реактор 24. В результате емкостной ток iK компенсирующего устройства уменьшается. Уменьшение этого тока происходит до тех пор, пока в сети не установится режим полной компенсации реактивного тока нагрузки. Таким образом, обеспечивается астатическое регулирование реактивного тока в узле нагрузки.

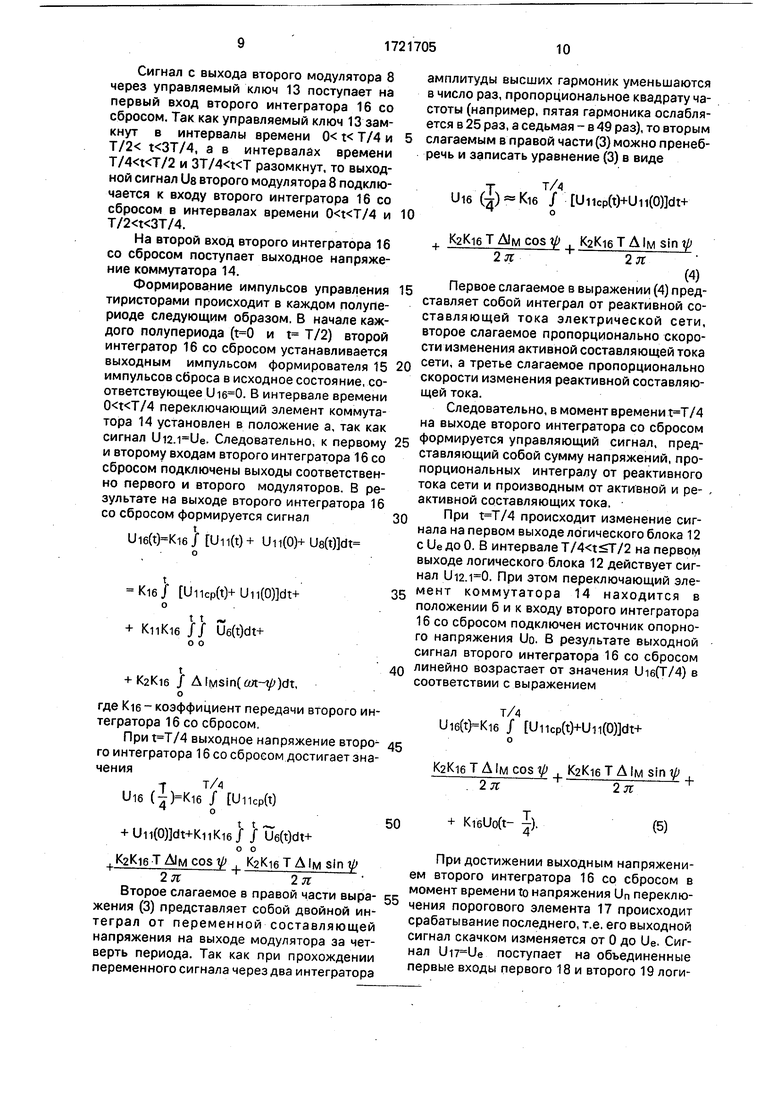

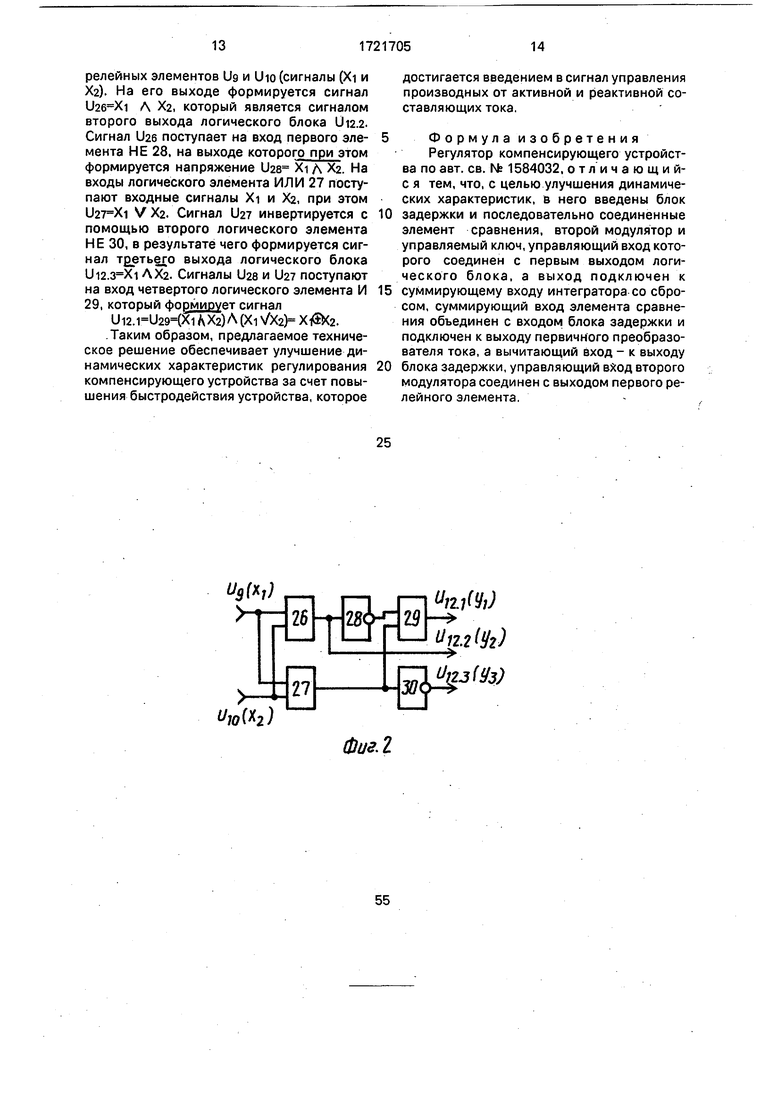

Логический блок 12 (фиг. 2) работает следующим образом. На входы третьего логического элемента И 26 поступают выходные сигналы первого 9 и второго 10

релейных элементов Ug и Uio (сигналы (Xi и Х2). На его выходе формируется сигнал Л Х2, который является сигналом второго выхода логического блока Ui2.2. Сигнал U26 поступает на вход первого эле- мента НЕ 28, на выходе которого при этом формируется напряжение U28 Xi Д Х2. На входы логического элемента ИЛИ 27 поступают входные сигналы Хч и Х2, при этом V X2. Сигнал U27 инвертируется с помощью второго логического элемента НЕ 30, в результате чего формируется сигнал третьего выхода логического блока Ui2. AX2. Сигналы U28 и U27 поступают на вход четвертого логического элемента И 29, который Формирует сигнал

Ui2.(Xi AX2)A (Xi VX2) XiSX2. .Таким образом, предлагаемое техническое решение обеспечивает улучшение динамических характеристик регулирования компенсирующего устройства за счет повышения быстродействия устройства, которое

)

%(Х2)

Фиг. 2

достигается введением в сигнал управления производных от активной и реактивной составляющих тока.

Формула изобретения Регулятор компенсирующего устройства по авт. св. № 1584032, отличающий- с я тем, что, с целью улучшения динамических характеристик, в него введены блок задержки и последовательно соединенные элемент сравнения, второй модулятор и управляемый ключ, управляющий вход которого соединен с первым выходом логического блока, а выход подключен к суммирующему входу интегратора со сбросом, суммирующий вход элемента сравнения объединен с входом блока задержки и подключен к выходу первичного преобразователя тока, а вычитающий вход - к выходу блока задержки, управляющий вход второго модулятора соединен с выходом первого релейного элемента.

%;W Unith)

U 123 (Уз)

U

11

«го tt

П

| Устройство для управления источником реактивной мощности | 1985 |

|

SU1267532A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Регулятор статического компенсирующего устройства | 1988 |

|

SU1584032A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1992-03-23—Публикация

1990-05-28—Подача