Изобретение относится к измерительной технике и может быть использовано для измерения среднего значения сдвига фаз между двумя гармоническими колебаниями известной частоты.

Цель изобретения - повышение быстродействия при сохранении точности измерения.

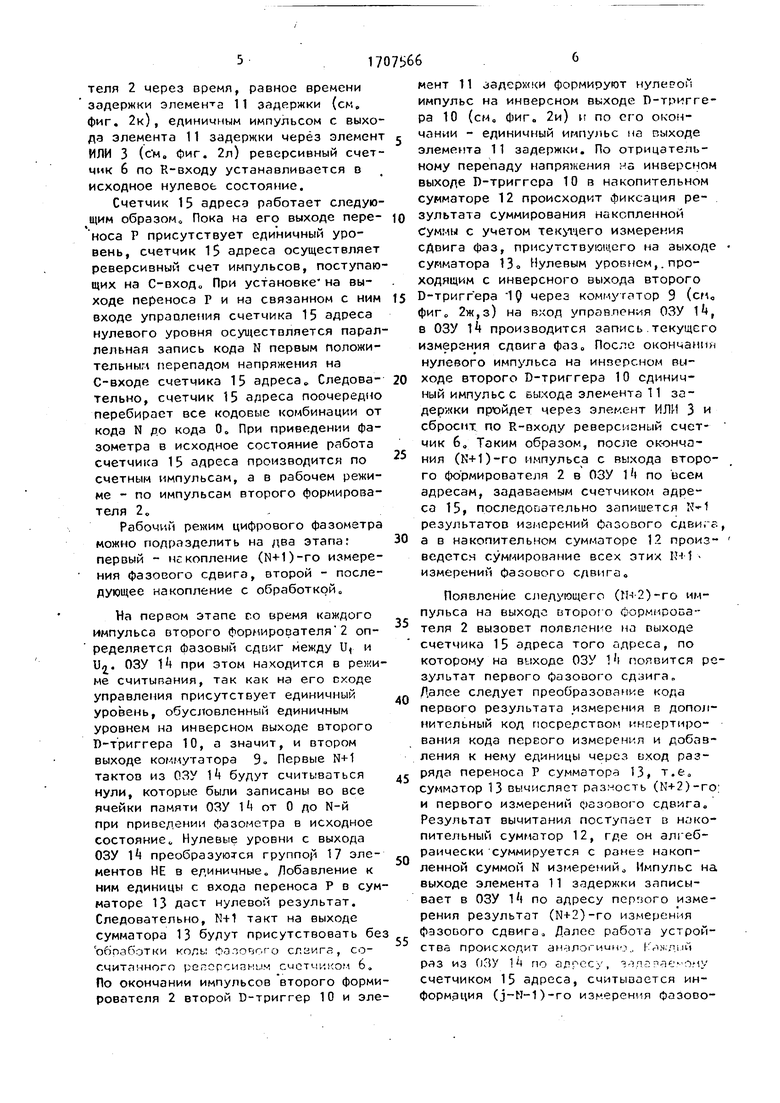

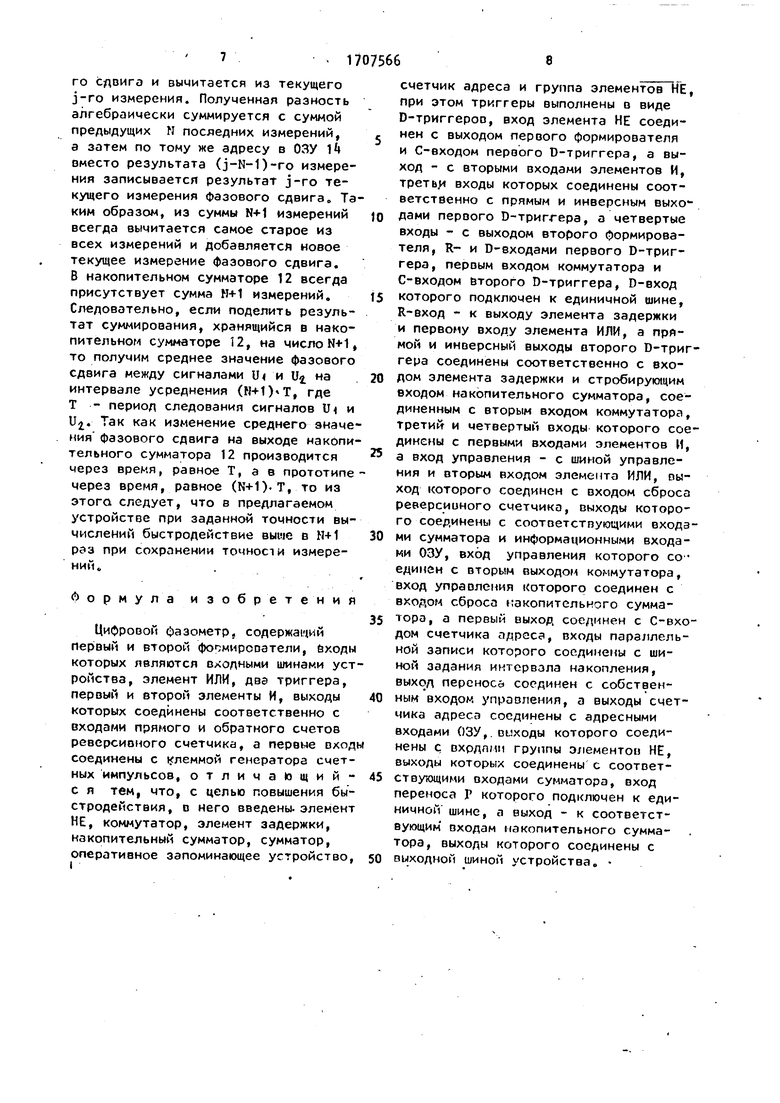

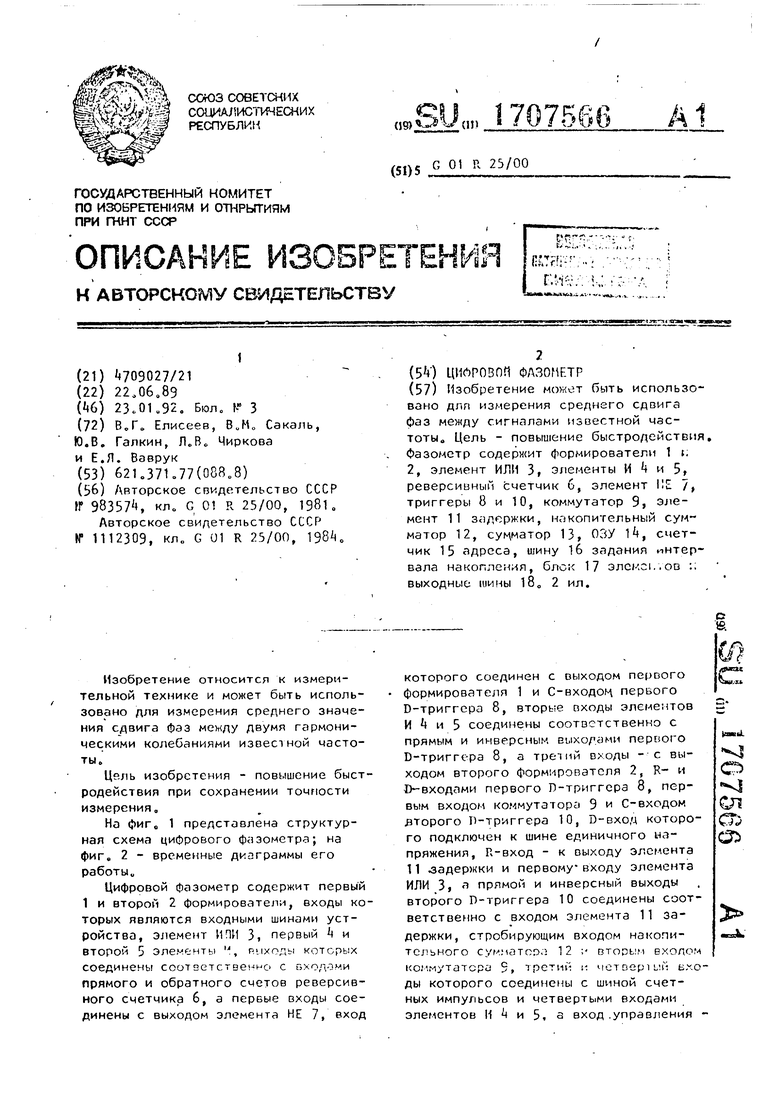

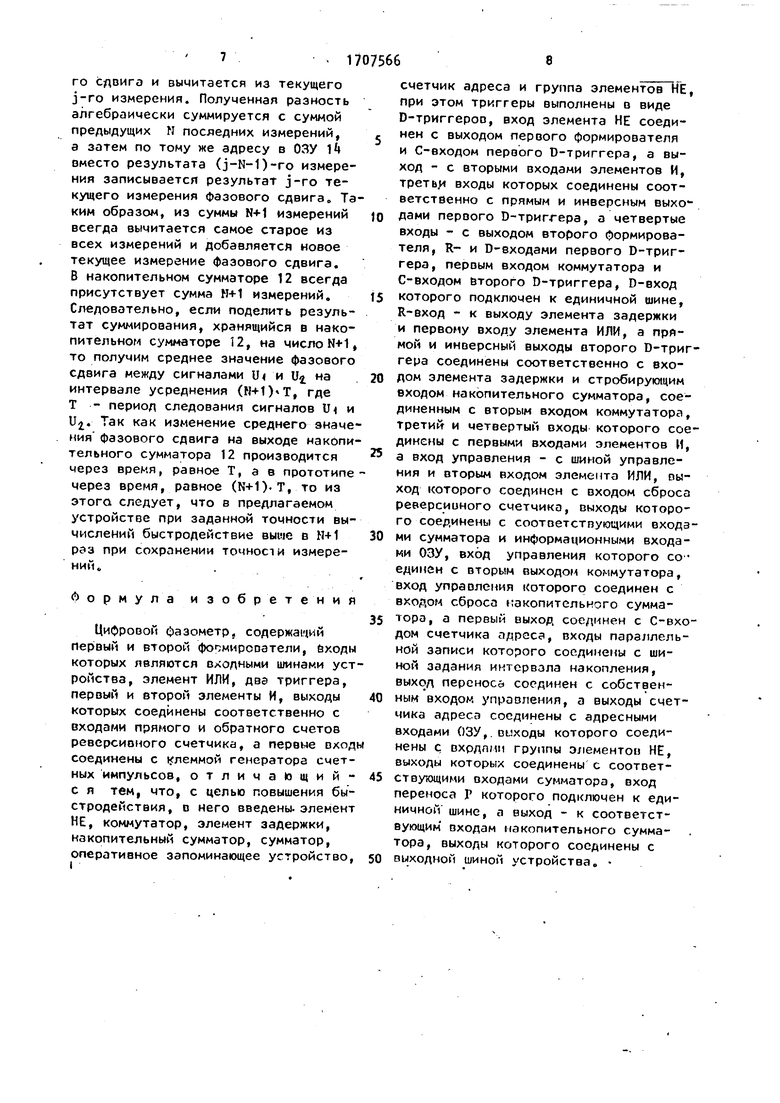

На фиг. 1 представлена структурная схема цифрового фазометра; на фиг. 2 - временные диаграммы его работы.

Цифровой фазометр содержит первый 1 и второй 2 формирователи, входы которых являются входными шинами устройства, элемент ИЛИ 3, первый Ц и второй 5 элементы , Р.ЫХОДЫ которых соединены соответственно с входами прямого и обратного счетов реверсивного счетчика 6, а первые входы соединены с выходом элемента НЕ 7, вход

которого соединен с выходом первого формирователя 1 и С-входом. первого D-триггера 8, вторые входы элементов И Ц и 5 соединены соответственно с прямым и инверсным выходами перЕЮГО D-триггера 8, а третий входы - с выходом второго Формирователя 2, R- и D-входами первого D-триггера 8, первым входом коммутатора 9 и С-входом второго D-триггера 10, D-вход которого подключен к шине единичного напряжения, R-вход - к выходу элемента 11 .задержки и первому входу элемента ИЛИ 3| а прямой и инверсный выходы второго П-триггера 10 соединены соответственно с входом элемента 11 задержки, стробирующим входом накопительного сумматор.) 12 ; вторым входом коммутатора S, третий .: четвертый ьхо- ды которого соединены с шиной счетных импульсов и четвертыми входами элементов И k и 5, а вход .управления V.

Г

Wu.

|OH|JL

О

ел

о о

с шиной сигнала управления, входом сброса накопительного сумматора 12 и вторым входом элемента ИЛИ 3 выход которого соединен с входом сброса ре- версивного счетчика 6, выходы которого соединены с соответствующими входами сумматора 13 и информационными входами оперативного запоминающего устройства (ОЗУ) 14, вход управления которого соединен с вторым выходом коммутатора 9, первый выход которого соединен с С-входом счетчика адреса 15, выходы параллельной записи которого соединены с шиной задания интервала накопления 16, выход переноса соединен с собственным входом управления, а выходы счетчика адреса 15 соединены с адресными входами ОЗУ 1, выходы которого соединены с группой 17 элементов НЕ, выходы которых соединены с соответствующими входами сумматора 13f вход переноса Р которого подключен к шине единичного напряжения, а выходы - к соответствующим входам накопительного сумматора 12, выходы которого соединены с выходной шиной устройства 18„

Цифровой фазометр работает следующим образом.

В исходное состояние устройство приводится единичным импульсом по .шине управления, длительность которого для полного обнуления ОЗУ I должна, превышать цикл работы счетчика адреса 15 при подаче на его С-вход счетных импульсов. В этом случае единичный уровень на шине управления через элемент ИЛИ 3 обнуляет реверсивный счетчик 6, а-счетчик 15 адреса считывает пропускаемые на его С-вход коммутатором 9 счетные импульсы, принимая все значения от 0 до N, в результате чего в ОЗУ I по всем адресам от 0 до N запишутся нули. Коммутатор 9 при единичном уровне на его входе управления пропускает на оба выхода счетные импульсы с третьего и четвертого входов, а при нулевом уровне - информацию с первого входа на первый выход, а с второго входа - на второй выход. На входы параллельной записи счетчика 15 адреса по шине 16 задания интервала накопления подается кед N, ,ел. м; с г о . jwpcmir , у;з- счаусщих в формировании среднего значения фазового сдвига. Код N устанавливается на шине 16 задания интер

5

5

0

0

5

0

5

0

55

вала накопления до приведения фазометра в исходное состояние.

По окончании единичного импульса v на шине управления фазометр переходит в рабочий режим. В это время на С-вход счетчика адреса 15 поступают через коммутатор 9 импульсы с выхода второго формирователя 2, а на вход управления ОЗУ И - импульсы с выхода второго D-триггера 10. Второй D-триг- гер 10 по задним фронтам импульсов второго формирователя 2 формирует импульсы, длительность которых равна времени задержки элемента 11 задержки, так как единичным уровнем с выхода элемента 11 задержки второй D-триггер 1Q по R-входу устанавливается в нулевое состояние.

Реверсивный счетчик 6 служит для определения фазового сдвига между двумя входными гармоническими колебаниями 1Г,| и Иг (см0 фмг. 2) относительно U4. Элементы И t и 5 пропускают счетные импульсы тогда, когда на выходе первого формирователя 1 (гм. фиг. 2а) нулевой уровень (на выходе элемента НЕ 7 единичный уро- . вень), а на выходе второго формирователя 2 - РДИНИЧНЫЙ уровень. В случае, когда U2 опережает U, по заднему фронту импульса первого формирователя 1 первый D-триггер 8 устанавливается в единичное состояние (см, фиг. 2г), и счетные импульсы проходят- через первый элемент И (см. фиг 2д) н-э вход прямого счета реверсивного счетчика 6. По окончании единичного импульса на выходе второго формирователя 2 (см0 фиг.26) первый D-триггер 8 устанавливается по R-входу в нулевое исходное состояние. В случае t когда 11 отстает от U., первый D-триггер 8 (см. фиг„2в) не устанавливается в единичное состояние по заднему фронту импульса первого формирователя 1, остается в нулевом состоянии, и с появлением единичного уровня на выходе второго формироватеь/ 2 счетные импульсы про- ходят через второй элемент И 5 (см. фиг. 2е) на вход обратного счета реверсивного счетчика 6. Таким образом; реверсивный счетчик 6 осуществляет прямой счет счетных импульсов при опережении сигнала Ь г и обратный счет (реверсивный) - при отставании сигнала Ua относительно сигнала U. После окончания импульса второго формирователя 2 через время, равное времени задержки элемента И задержки (см„ фиг. 2к), единичным импульсом с выхода элемента 11 задержки через элемент ИЛИ 3 (с м. фиг. 2л) реверсивный счетчик 6 по R-входу устанавливается в исходное нулевое состояние.

Счетчик 15 адреса работает следующим образом Пока на его выходе пере- носа Р присутствует единичный уровень, счетчик 15 адреса осуществляет реверсивный счет импульсов, поступающих на С-вход0 При установке на выходе переноса Г и на связанном с ним входе упраоления счетчика 15 адреса нулевого уровня осуществляется параллельная запись кода N первым положительным перепадом напряжения на С-входе счетчика 15 адреса. Следова- тельно, счетчик 15 адреса поочередно перебирает все кодовые комбинации от кода N до кода 0„ При приведении фазометра в исходное состояние работа счетчика 15 адреса производится по счетным импульсам, а в рабочем режиме - по импульсам второго формирователя 2 о

Рабочий режим цифрового фазометра можно подразделить на два этапа: первый - накопление (N+1)-ro измерения фазового сдвига, второй - последующее накопление с обработкой„

На первом этапе г.о время каждого

импульса второго Формирователя 2 определяется фазовый сдвиг между U, и Ул. ОЗУ 1 при этом находится в режиме считывания, так как на его сходе управления присутствует единичный уровень, обусловленный единичным уровнем на инверсном выходе второго Т)-т риггера 10, а значит, и втором выходе коммутатора 9. Первые N+1 тактов из ОЗУ I1 будут считываться нули, которые были записаны во все ячейки памяти ОЗУ 1Ц от 0 до N-й при приведении фазометра в исходное состояние Нулевые уровни с выхода ОЗУ И преобразуются группой 17 эле- ментов НЕ в единичные. Лобавление к ним единицы с входа переноса Р в сумматоре 13 даст нулевой результат. Следовательно, N-H такт на выходе сумматора 13 будут присутствовать без обработки коды Оалового сг.нигз, сосчитанного репорсизним счетчиком 6. По окончании импульсов второго формирователя 2 второй D-триггер 10 и эле

5 0

0

5

Q 5

мент 11 задерх ки формируют нулееой импульс на инверсном выходе D-тригге- ра 10 (см. фиг„ 2и) и по его окончании - единичный импульс на выходе элемента 11 задержки. По отрицательному перепаду напряжения на инверсном выходе Р-триггсра 10 в накопительном сумматоре 12 происходит фиксация результата суммирования накопленной суммы с учетом текущего измерения сдвига фаз, присутствующего на выходе сумматора 13о Нулевым уровнем,.проходящим с инверсного выхода второго D-триггера 10 через коммутатор 9 (см, фиг о 2ж,з) на вход управления ОЗУ в ОЗУ 14 производится запись.текущего измерения сдвига фаз„ После окончания нулевого импульса на инверсном выходе второго D-триггерэ 10 единичный импульс с выхода элемента 11 задержки прюйдет через элемент ИЛИ 3 и сбросит по R-входу реверсивный счет- чик 60 Таким образом, после окончания (N+1)-ro импульса с выхода второго формирователя 2 в ОЗУ 1 по всем адресам, задаваемым счетчиком адреса 15, последовательно запишется N«-1 результатов измерений фазового сдвига, а в накопительном сумматоре 12 произ- ведется суммирование всех этих ГЛ-1 - измерений фазового сдвига.

Появление следующего ()-ro импульса на выходе второго формирователя 2 вызовет появление но выходе счетчика 15 адреса того адреса, по которому на выходе ОЗУ 1( появится результат первого фазового сдзига„ Далее следует преобразование кода первого результата измерения в дополнительный код посредством инвертирования кода первого измерения и добавления к нему единицы через ЕЗХОД разряда переноса Р сумматора 13, т.е„ сумматор 13 вычисляет разность (N+2)-ro; и первого измерений q 330ooro сдвига. Результат вычитания поступает в накопительный сумматор 12, где он алгебраически суммируется с ранеэ накопленной суммой N измерений„ Импульс на выходе элемента 11 задержки записывает в ОЗУ 1 по адресу пергюго измерения результат (N+2)-ro измерения фазового сдвига , Далее работа устройства происходит аналогично., Кг-чждий раз из ОЗУ по адресу, з пзрае- ому счетчиком 15 адреса, считывается информация (j-N-l)-ro измерения фаэового сдвига и вычитается из текущего j-ro измерения. Полученная разность алгебраически суммируется с суммой предыдущих N последних измерений, а затем по тому же адресу в ОЗУ 14 вместо результата (j-N-l)-ro измерения записывается результат j-ro текущего измерения фазового сдвига Таким образом, из суммы N+1 измерений всегда вычитается самое старое из всех измерений и добавляется новое текущее измерение фазового сдвига. В накопительном сумматоре 12 всегда присутствует сумма N4-1 измерений. Следовательно, если поделить результат суммирования, хранящийся в накопительном сумматоре 12, на число N+1, то получим среднее значение фазового сдвига между сигналами 1 и U на интервале усреднения (Н-Н)Т, где Т - период следования сигналов U и U. Так как изменение среднего значения фазового сдвига на выходе накопительного сумматора 12 производится через время, равное Т, а в прототипе через время, равное (N+1).T, то из этого следует, что в предлагаемом устройстве при заданной точности вычислений быстродействие вьиче в Н-Н раз при сохранении точности измерений,,

Формула изобретения

Цифровой фазометр, содержащий первый и второй формирователи, входы которых являются входными шинами устройства, элемент ИЛИ, два триггера, первый и второй элементы И, выходы которых соединены соответственно с входами прямого и обратного счетов реверсивного счетчика, а первые вход соединены с клеммой генератора счетных импульсов, отличающий- с я тем, что, с целью повышения быстродействия, в него введены, элемент НЕ, коммутатор, элемент задержки, накопительный сумматор, сумматор, оперативное запоминающее устройство,

0 0

5

0 5 0

счетчик адреса и группа элементов НЕ, при этом триггеры выполнены в виде D-триггеров, вход элемента НЕ соединен с выходом первого формирователя и С-входом первого D-триггера, а выход - с вторыми входами элементов И, третье входы которых соединены соответственно с прямым и инверсным выходами первого D-триггера, а четвертые входы - с выходом второго формирователя, R- и D-входами первого D-триггера, первым входом коммутатора и С-входом второго D-триггера, D-вход которого подключен к единичной шине, R-вход - к выходу элемента задержки и первому входу элемента ИЛИ, а прямой и инверсный выходы второго D-триггера соединены соответственно с входом элемента задержки и стробирующим входом накопительного сумматора, соединенным с вторым входом коммутатора, третий и четвертый входы которого соединены с первыми входами элементов И, а вход управления - с шиной управления и вторым входом элемента ИЛИ, выход которого соединен с входом сброса реверсииного счетчика, выходы которого соединены с соответствующими входами сумматора и информационными входами ОЗУ, вход управления которого соединен с вторым выходом коммутатора, вход управления которого соединен с входом сброса накопительного сумматора, а первый выход соединен с С-входом счетчика адреса, входы параллельной записи которого соединены с шиной задания интервала накопления, выход переноса соединен с собственным входом управления, а выходы счетчика адреса соединены с адресными входами ОЗУ,.выходы которого соединены с вхрдлми группы элементен НЕ, выходы которых соединены с соответствующими входами сумматора, вход переноса р которого подключен к единичной шине, а выход - к соответствующим входам накопительного сумматора, выходы которого соединены с выходной шиной устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Измерительный двухфазный генератор | 1987 |

|

SU1442931A1 |

| Следящий фазометр (его варианты) | 1981 |

|

SU1029095A1 |

| СПОСОБ ЦИФРОВОГО ИЗМЕРЕНИЯ ФАЗОВОГО СДВИГА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1990 |

|

SU1823625A1 |

| Фазометр | 1991 |

|

SU1817037A1 |

| Цифровой фазометр | 1986 |

|

SU1348744A1 |

| Устройство для приема дискретной информации | 1989 |

|

SU1693735A1 |

| Многоканальный фазометр | 1989 |

|

SU1720028A1 |

| Способ измерения фазового сдвига между двумя гармоническими сигналами и устройство для его осуществления | 1988 |

|

SU1596272A1 |

| Цифровой фазометр | 1986 |

|

SU1323979A1 |

| Устройство для сопряжения цифровой вычислительной машины с каналом связи | 1991 |

|

SU1837301A1 |

Изобретение может быть использовано длп измерения среднего сдвига фаз между сигналами известной частоты. Цель - повышение быстродействия. Фазометр содержит формирователи 1 t; 2, элемент ИЛИ 3, элементы И k и 5, реверсивный счетчик 6, элемент НЕ 1t триггеры 8 и 10, коммутатор 9, элемент 11 задержки, накопительный сумматор 12, сумматор 13, ОЗУ 1, сметчик 15 адреса, шину 16 задания интервала накопления, блок 17 элскс..ов :: выходные шины 18. 2 ил.

VI------l

ЖЛШШВШ -1 ГТ....

| 0 |

|

SU98357A1 | |

| Цифровой фазометр | 1983 |

|

SU1112309A1 |

Авторы

Даты

1992-01-23—Публикация

1989-06-22—Подача