Изобретение относится к радиотехнике и может использоваться в синхронных сетях обмена дискретной информацией, системах навигации,связи и телеуправления.

Цель изобретения - повышение досто- верности ретрансляции путем двунаправленной ретрансляции.

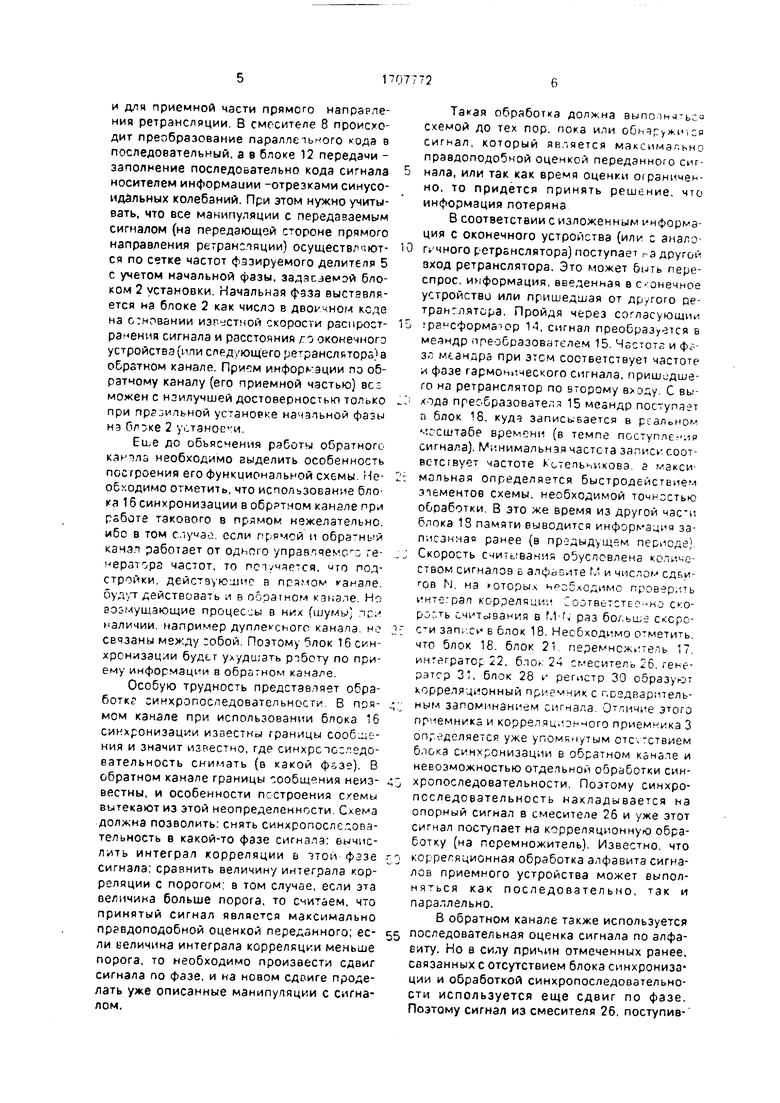

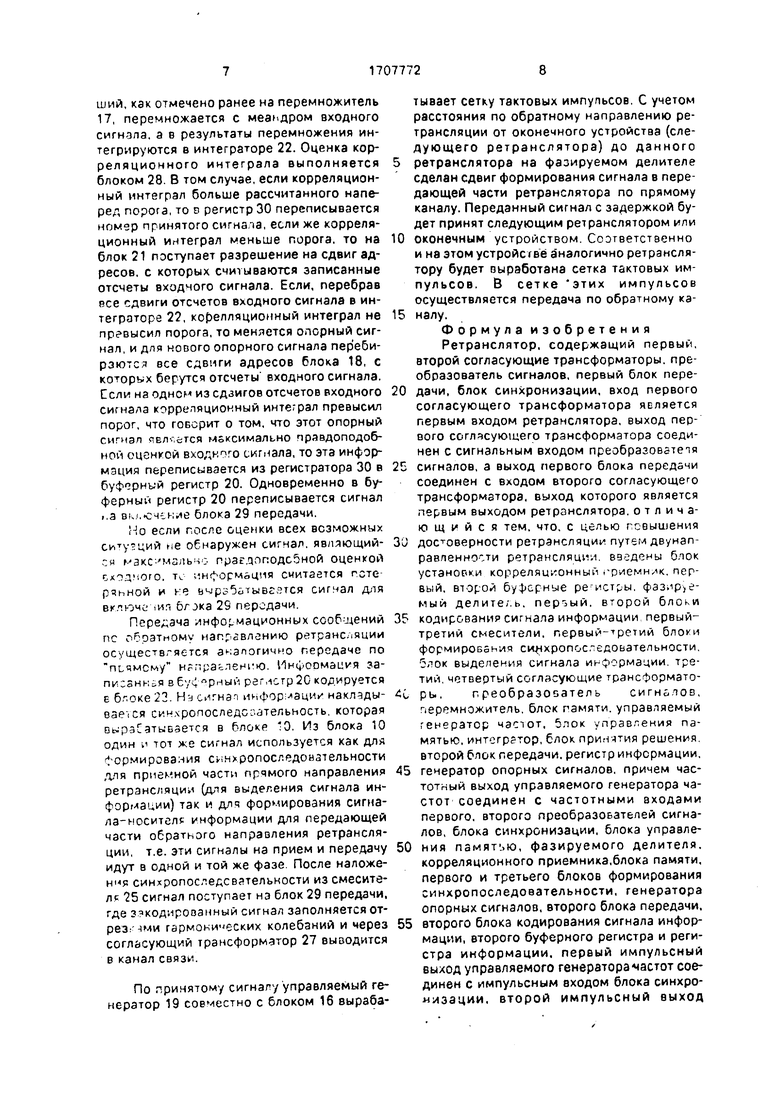

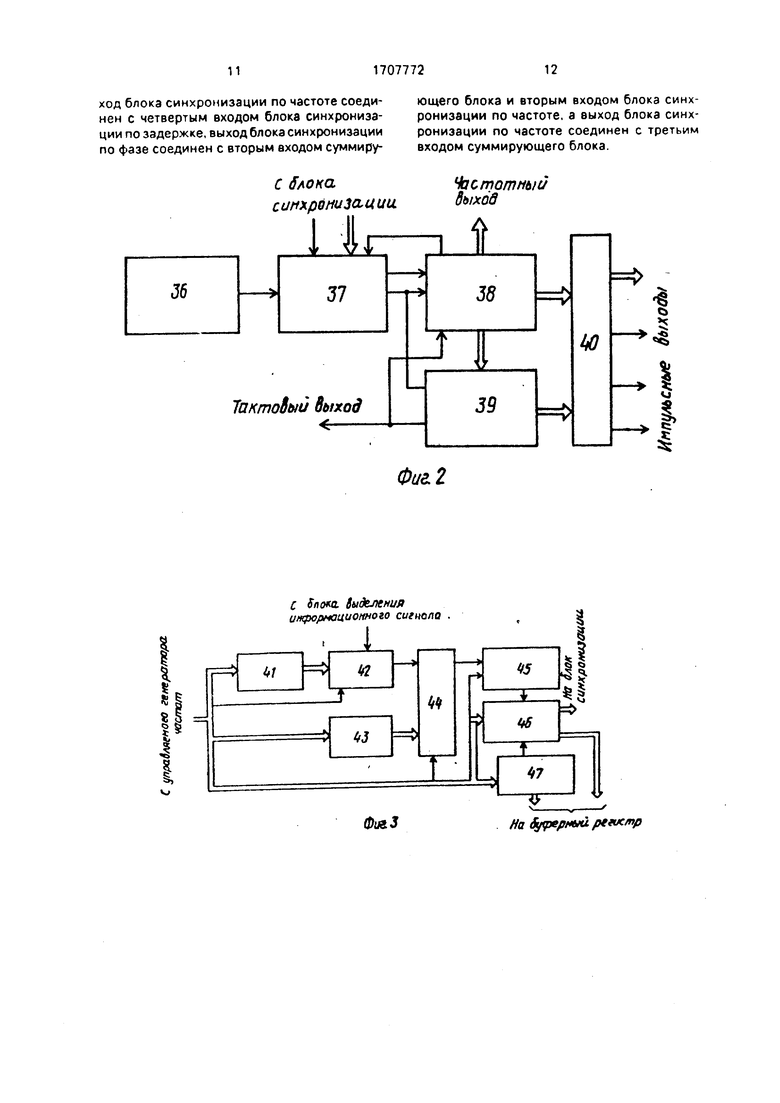

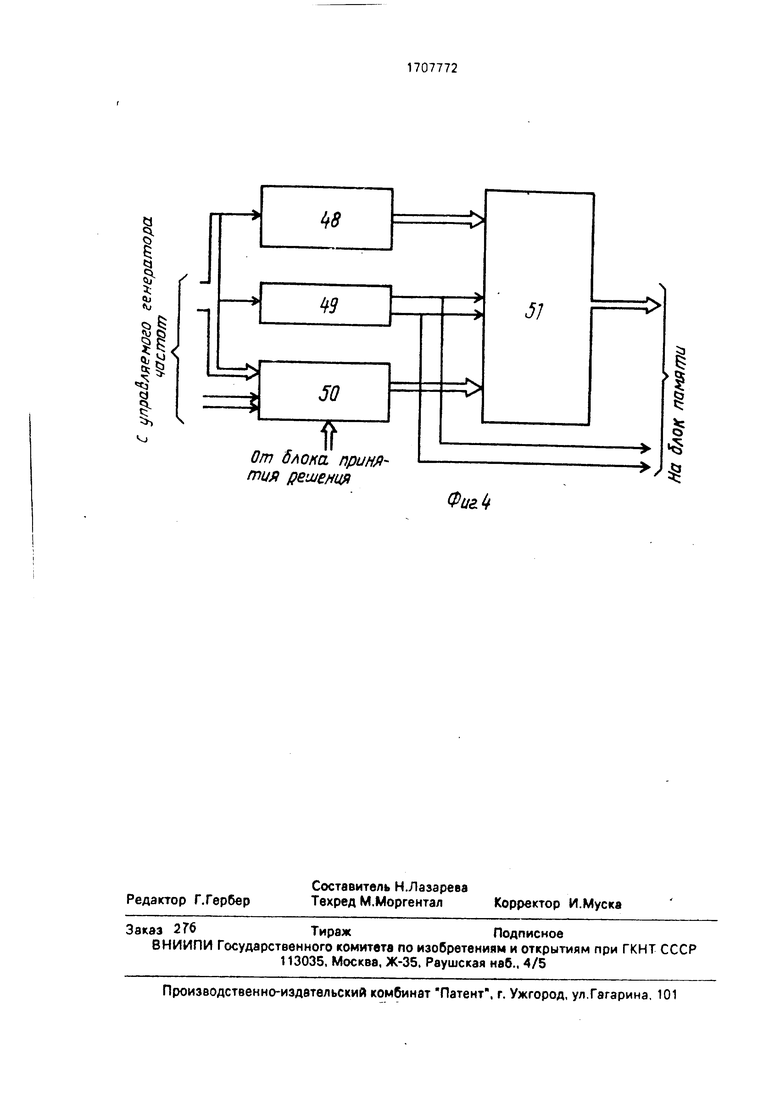

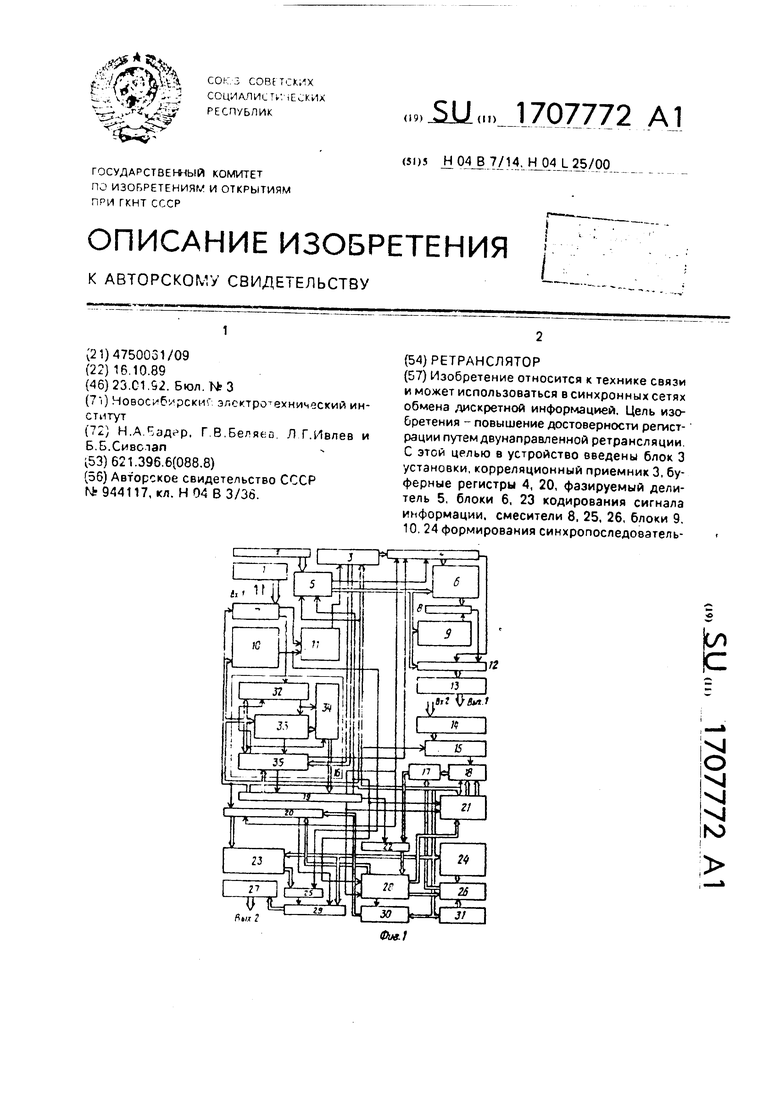

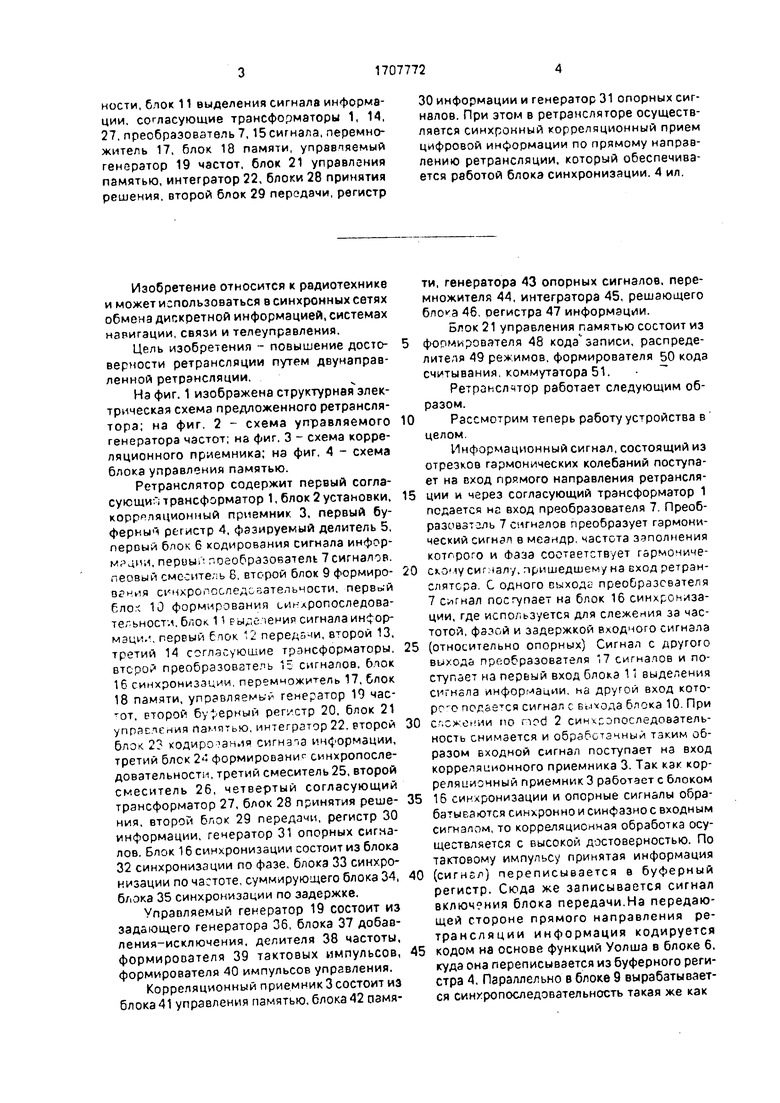

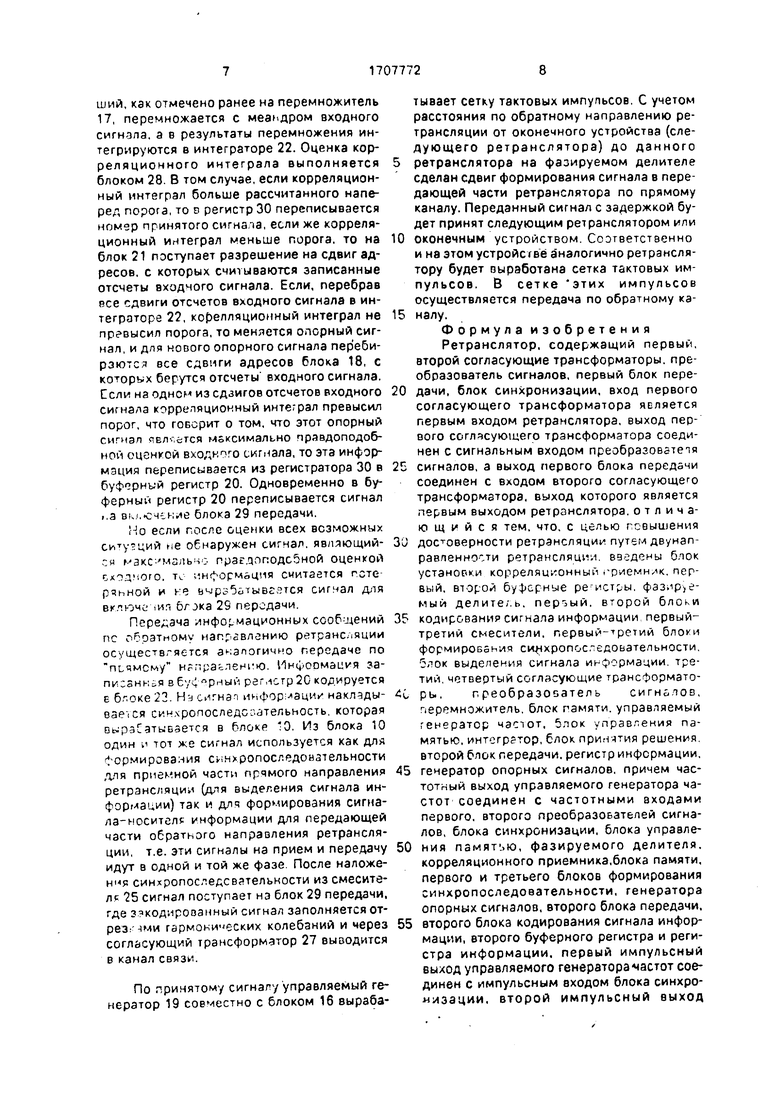

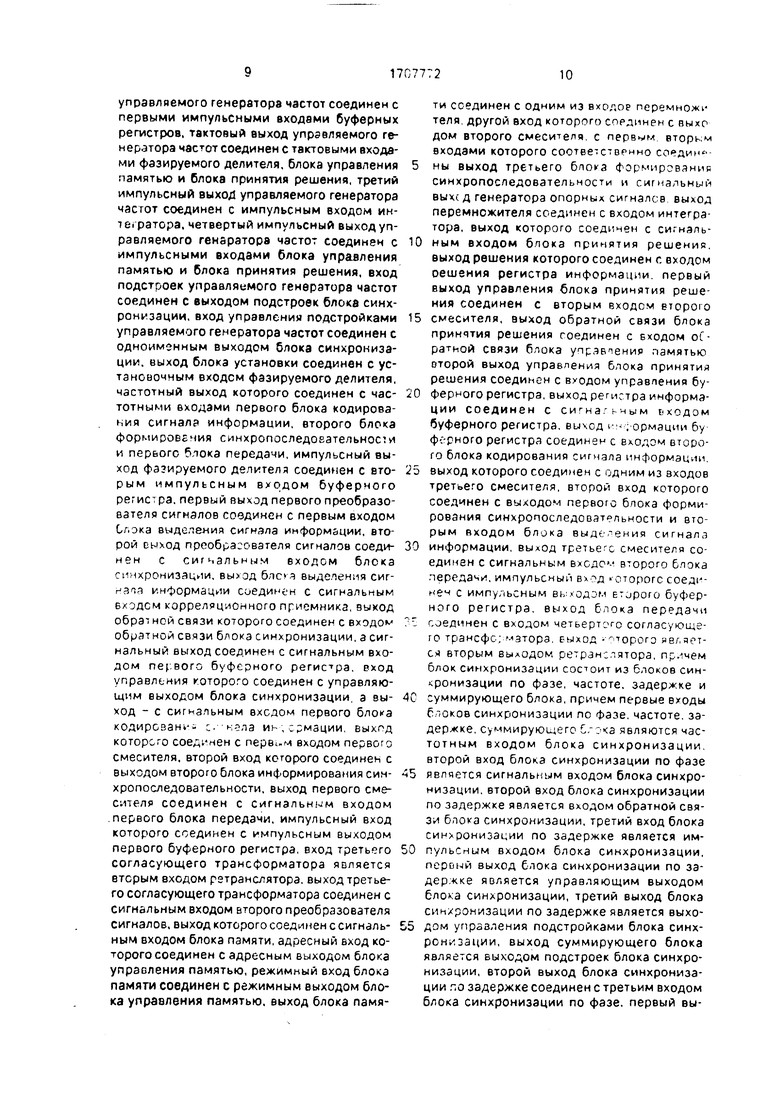

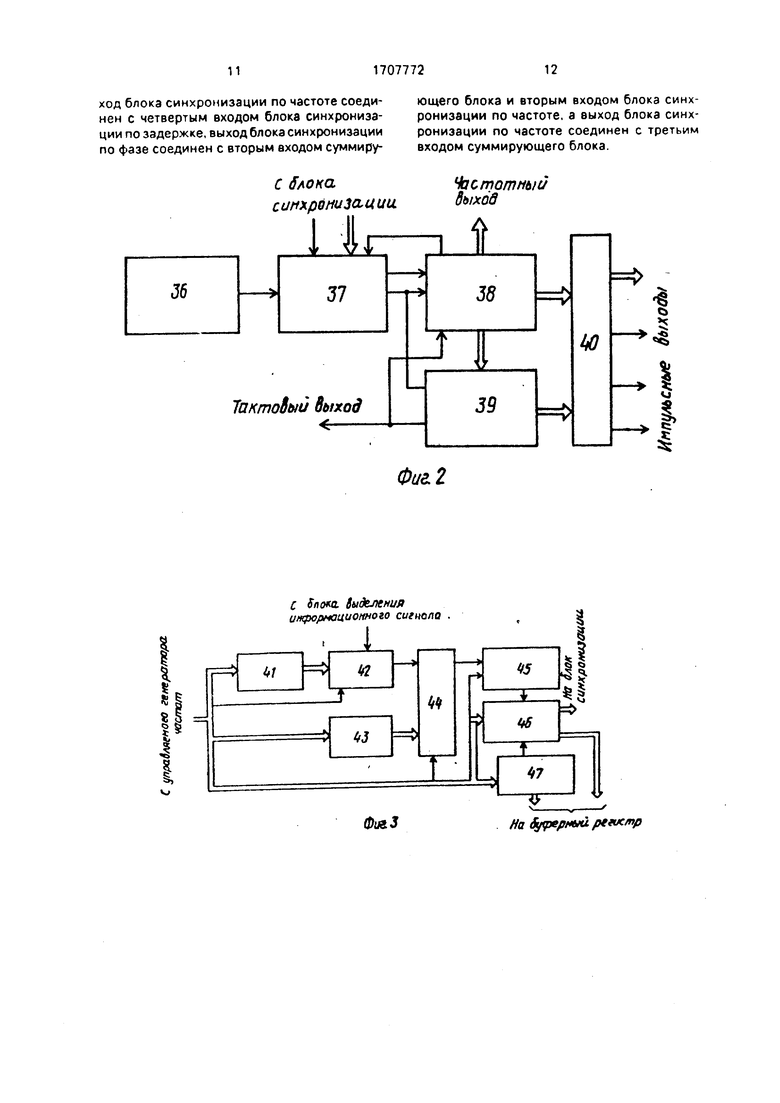

На фиг. 1 изображена структурная электрическая схема предложенного ретранслятора; на фиг. 2 - схема управляемого генератора частот; на фиг. 3 - схема корреляционного приемника; на фиг. 4 - схема блока управления памятью.

Ретранслятор содержит первый согла- сующи- i трансформатор 1, блок 2 установки, корреляционный приемник 3, первый буферный регистр 4, фазируемый делитель 5, первый блок 6 кодирования сигнала инфор- МРЦНИ, периый гюеобразователь 7 сигналов. пеовый смеситель 8, второй блок 9 формиро- вгния синхропоследовательчости. первый бло. 10 формирования синхропоследова- тельности, блок 11 выделения сигнала информации, первый блок 12 передачи, второй 13, третий 14 согласующие трансформаторы, второй преобразователь 15 сигналов, блок 16 синхронизации, перемчожитель 17,блок 18 памяти, управляемый генератор 19 час- тот, второй буферный регистр 20, блок 21 управления памятью, интегратор 22. второй блок 2 кодирования сигнала информации, третий блек 2 формирование1 синхропосле- довэтельности, третий смеситель 25, второй смеситель 26, четвертый согласующий трансформатор 27, блок 28 принятия реше- ния. второй блок 29 передачи, регистр 30 информации, генератор 31 опорных сигналов. Блок 16 синхронизации состоит из блока 32 синхронизации по фазе, блока 33 синхронизации по частоте, суммирующего блока 34, блока 35 синхронизации по задержке.

Управляемый генератор 19 состоит из задающего генератора 36, блока 37 добавления-исключения, делителя 38 частоты, формирователя 39 тактовых импульсов, формирователя 40 импульсов управления.

Корреляционный приемник3 состоит из блока 41 управления памятью, блока 42 памяти, генератора 43 опорных сигналов, перемножителя 44, интегратора 45, решающего 46. регистра 47 информации.

Блок 21 управления памятью состоит из формирователя 48 кода записи, распределителя 49 режимов, формирователя 50 кода считывания, коммутатора 51.

Ретранслятор работает следующим образом.

Рассмотрим теперь работу устройства в целом.

Информационный сигнал, состоящий из отрезков гармонических колебаний поступает на вход прямого направления ретрансляции и через согласующий трансформатор 1 подается на вход преобразователя 7. Преоб- разовзтзль 7 сигналов преобразует гармонический сигнал в меандр, частота заполнения которого и фаза соответствует гармоническому сигналу, пришедшему на вход ретранслятора. С одного выходе преобразователя 7 сигнал посгупает на блок 16 синхронизации, где используется для слежения за частотой, фазой и задержкой входного сигнала (относительно опорных) Сигнал с другого выхода преобразователя 17 сигналов и поступает на первый вход блока 11 выделения сигнала информации, на другой вход кото- подается сигнал с выхода блока 10. При сг.сжонии no nod 2 синхсопоследоаатель- ность снимается и обработанный таким образом входной сигнал поступает на вход корреляционного приемника 3. Так как кор- реляииочный приемник 3 работает с блоком 16 синхронизации и опорные сигналы обрабатываются синхронно и синфазное входным сигналом, то корреляционная обработка осуществляется с высокой достоверностью. По тактовому импульсу принятая информация (сигнал) переписывается в буферный регистр. Сюда же записывается сигнал включения блока передачи.На передающей стороне прямого направления ретрансляции информация кодируется кодом на основе функций Уолша в блоке 6, куда она переписывается из буферного регистра 4, Параллельно в блоке 9 вырабатывается синхропоследовательность такая же как

и для приемной части прямого напрэрле- ния ретрансляции. В смесителе 8 происходит преобразование параллетьного кода в последовательный, а в блоке 12 передачи - заполнение последовательно кода сигнала носителем информации -отрезками синусоидальных колебаний. При этом нужно учитывать, что все манипуляции с передаваемым сигналом (на передающей стороне прямого направления ретрансляции) осуществляют- ся по сетке частот фазируемого делителя 5 с учетом начальной фазы, задзсаемэй блоком 2 установки. Начальная фзза выставляется на блоке 2 как число в двоичном кеде на основании ИЗГ-УСТНОЙ скорости распрост- ранения сигнала и расстояния /то оконечного устройства (или следующего ретранслятора) в обратном канале. Прием информации по обратному каналу (его приемной частью вес можен с нзилучшей достоверностью только при пргзильной установке начальной фазы нэ блоке 2 устзнос и.

Еше до объяснения работы обратного канэлз необходимо выделить особенность построения его функциональной схемы. Не- обходимо отметить, что использование блока 16 синхронизации в обрятном канале при работе такового в прямом нежелательно, ибо в том случае, если прямой и обратный качал работает от одного управляемого ге- нерзтора частот, то пот/чяется, что подстройки, действующие в прямом канале, будут действовать и в обратном канале. Но возмущающие процессы в них (шумы лен наличии, например дуплексного канала, не связаны между собой. Поэтому блок 16 синхронизации будет ухудшать ртботу по приему информации в обратном канале.

Особую трудность представляет обра- боткг синхропоследовательности. В поя- мом канале при использовании блока 16 синхронизации изаестны границы сообщения и значит известно, где синхрспоследовательность снимать (о какой фазе). В обратном канале границы сообщения неиз- вестны, и особенности построения схемы вытекают из этой неопределенности. Схема должна позволить: снять синхропоследова- тельность в какой-то фазе сигнала: вычислить интеграл корреляции в этой фазе сигнала; сравнить величину интеграла корреляции с порогом; в том случае, если эта величина больше порога, то считаем, что принятый сигнал является максимально правдоподобной оценкой переданного; ее- ли величина интеграла корреляции меньше порога, то необходимо произвести сдвиг сигнала по фазе, и на новом сдвиге проделать уже описанные манипуляции с сигналом.

Такая обработка должна выполна-ьса схемой до тех пор. пока или обнаружится сигнал, который является максимально правдоподобной оценкой переданного сигнала, или так как время оценки ограниченно, то придётся принять решение, что информация потеряна

В соответствии с изложенным информация с оконечного устройства (или с аналогичного ретранслятора) поступает га другой вход ретранслятора. Это может быть переспрос, информация, введенная в с-:онечное устройство или пришедшая от другого ретранслятора. Пройдя через согласующий трансформатор 14, сигнал преобразуется в меандр преобразователем 15. Частота и зл меандра при этом соответствует частоте и фазе гармонического сигнала, пришедшего на ретранслятор по второму входу. С выхода преобразователя 15 мезндр поступает о блок 18, кудэ записывается в реальном масштабе времени (в темпе поступление сигнала). Минимальная частота записи соответствует частоте Котелььиковэ. а максимальная определяется быстродействием элементов схемы, необходимой точностью обработки. В это же время из другой блока 18 памяти выводится информация за- писзннао ранее (в предыдущем периоде). Скорость считывания о5услевлена количеством сигналов Е алфавите М и числом сдвигов N. на которых необходимо проверить интеграл корреляции Соответстсс но скорость считывания в М-Г раз больше скорости записи в блок 18. Необходимо отметить, что блок 18, блок 21, перемнсжитель 17, интегратор 22. блок 24 смеситель 26. генератор 31, блок 28 и регистр 30 образуют корреляционный приемник с г.оедварнтель- ным запоминанием сигнала. Отличие этого приемника и корреляционного приемника 3 определяется уже упомянутым отсутствием блока синхронизации в обратном канале и невозможностью отдельной обработки синхропоследовательности. Поэтому синхро- последовательность накладывается на опорный сигнал в смесителе 26 и уже этот сигнал поступает на корреляционную обработку (на перемножитель). Известно, что корреляционная обработка алфавита сигналов приемного устройства может выполняться как последовательно, так и параллельно.

В обратном канале также используется последовательная оценка сигнала по алфавиту. Но в силу причин отмеченных ранее, связанных с отсутствием блока синхрониза ции и обработкой синхропоследовательности используется еще сдвиг по фазе. Поэтому сигнал из смесителя 26, поступивший, как отмечено ранее на перемножитель 17, перемножается с меандром входного сигнала, а в результаты перемножения интегрируются в интеграторе 22. Оценка корреляционного интеграла выполняется блоком 28. В том случае, если корреляционный интеграл больше рассчитанного наперед порога, то в регистр 30 переписывается номер принятого сигнала, если же корреляционный интеграл меньше порога, то на блок 21 поступает разрешение на сдвиг адресов, с которых считываются записанные отсчеты входного сигнала. Если, перебрав все сдвиги отсчетов входного сигнала в интеграторе 22, корелляционный интеграл не превысил порога, то меняется опорный сигнал, и для нового опорного сигнала перебираются все сдвиги адресов блока 18, с которых берутся отсчеты входного сигнала. Сели на одном из сдзигов отсчетов входного сигнала корреляционный интеграл превысил порог, что говорит о том, что этот опорный сигнал является максимально правдоподобной оценкой входного сигнала, то эта информация переписывается из регистратора 30 в буферный регистр 20. Одновременно в буферный регистр 20 переписывается сигнал ..а вк.|.;чекие блока 29 передачи.

Но если после оценки всех возможных ситу ций не обнаружен сигнал, являющийся макс- мзльчо прзедпподс5ной оценкой с,ходмого. TV инс ормйцмя скитается гсте- рчьной и не вчрз5птывгется сигнал для включения блока 2S передачи.

Передача информационных сообщений пс обратному направлению ретрансляции осуществляется аналогично передаче по прямому нрпраьленпю. Информация за- пи;анкая в буерный регистр 20 кодируется Е блоке 23. НУ сигнап информации накладывается син-хропоследсзательность. которая вырабатывается в блоке 0. Из блока 10 один и тот же сигнал используется как для формирования синхропосг.едонательности для приемной части прямого направления ретрансляции (для выделения сигнала информации) так и для формирования сигнала-носителя информации для передающей части обратного направления ретрансляции, т.е. эти сигналы на прием и передачу идут в одной и той же фазе. После наложения синхропоследсвательности из смесителе 25 сигнал поступает нэ блок 29 передачи, где закодированный сигнал заполняется отрезами гармонических колебаний и через согласующий трансформатор 27 выводится в канал связи.

По принятому сигналу управляемый генератор 19 совместно с блоком 16 вырабатывает сетку тактовых импульсов, С учетом расстояния по обратному направлению ретрансляции от оконечного устройства (следующего ретранслятора) до данного

ретранслятора на фазируемом делителе сделан сдвиг формирования сигнала в передающей части ретранслятора по прямому каналу. Переданный сигнал с задержкой будет принят следующим ретранслятором или

0 оконечным устройством. Соответственно и на этом устройстве а налогично ретранслятору будет выработана сетка тактовых импульсов. В сетке этих импульсов осуществляется передача по обратному ка5 налу.

Формула изобретения Ретранслятор, содержащий первый, второй согласующие трансформаторы, преобразователь сигналов, первый блок пере0 дачи, блок синхронизации, вход первого согласующего трансформатора является первым входом ретранслятора, выход первого согласующего трансформатора соединен с сигнальным входом преобразоватетя

Б сигналов, а выход первого блока передачи соединен с входом второго согласующего трансформатора, выход которого является первым выходом ретранслятора, отличающийся тем. что. с целью повышения

0 достоверности ретрансляции путем двунап- равленности ретрансляции, введены блок установки корреляционный гриемник. первый, второй буферные регистры. фазируемый делитель, первый, второй блоки

5 кодирования сигнала информации, первый- третий смесители, первый- ретий блоки формирования синхропоследовзтельности, блок выделений сигнала информации, третий, четвертый согласующие трансформато0 рь, преобразователь сигналов, перемножитель, блок памяти, управляемый генератор частот. 5лок управления памятью, интегратор, блок принятия решения. второй блок передачи, регистр информации,

5 генератор опорных сигналов, причем частотный выход управляемого генератора частот соединен с частотными входами первого, второго преобразователей сигналов, блока синхронизации, блока управле0 ния памятью, фазируемого делителя, корреляционного приемника,блока памяти, первого и третьего блоков формирования синхропоследовательности, генератора опорных сигналов, второго блока передачи.

5 второго блока кодирования сигнала информации, второго буферного регистра и регистра информации, первый импульсный выход управляемого генератора частот соединен с импульсным входом блока синхронизации, второй импульсный выход

управляемого генератора частот соединен с первыми импульсными входами буферных регистров, тактовый выход управляемого генератора частот соединен с тактовыми входами фазируемого делителя, блока управления памятью и блока принятия решения, третий импульсный выход управляемого генератора частот соединен с импульсным входом интегратора, четвертый импульсный выход управляемого генаратора частот соединен с импульсными входами блока управления памятью и блока принятия решения, вход подстроек управляемого генератора частот соединен с выходом подстроек блока синхронизации, вход управления подстройками управляемого генератора частот соединен с одноименным выходом блока синхронизации, выход блока установки соединен с установочным входом фазируемого делителя, частотный выход которого соединен с час- тотными входами первого блока кодирования сигнала информации, второго блока формировгния синхропоследовательности и первого блока передачи, импульсный выход фазируемого делителя соединен с вто- рым импульсным входом буферного регистра, первый выход первого преобразователя сигналов соединен с первым входом Слока выделения сигнала информации, второй сыход преобразователя сигналов соеди- нен с сигнальным входом блока синхронизации, выход блсм выделения сигнала информации соединен с сигнальным входом корреляционного приемника, выход обрат ной связи которого соединен с входом обратной связи блока синхронизации, а сигнальный выход соединен с сигнальным входом первого буферного регистра, вход управления которого соединен с управляющим выходом блока синхронизации, а вы- ход - с сигнальным входом первого блока кодирован с--н5ла информации, выход которого соединен с первом входом первого смесителя, второй вход которого соединен с выходом второго блока информирования син- хропоследовательности, выход первого смесителя соединен с сигнальным входом .первого блока передачи, импульсный вход которого соединен с импульсным выходом первого буферного регистра, вход третьего согласующего трансформатора является вторым входом ретранслятора, выход третьего согласующего трансформатора соединен с сигнальным входом второго преобразователя сигналов, выход которого соединен с сигналь- ным входом блока памяти, адресный вход которого соединен с адресным выходом блока управления памятью, режимный вход блока памяти соединен с режимным выходом блока управления памятью, выход блока памяти соединен с одним из входое перемножь теля, другой вход которого соединен с выхо дом второго смесителя, с первым вторкм входами которого соответственно соедин - ны выход третьего блока формирований синхропоследовательности и сигнальный выхс д генератора опорных сигналов выход перемнсжителя соединен с входом интегратора, выход которого соединен с сигнальным входом блока принятия решения. выход решения которого соединен с входом оешения регистра информации, первый выход управления блока принятия решения соединен с вторым входом второго смесителя, выход обратной связи блока принятия решения соединен с входом of- ратной связи блока упрдвпения памятью оторой выход управления блока принятия решения соединен с входом управления буферного регистра, выход регистра информации соединен с сигнальным ьходом буферного регистра, выход Формации буферного регистра соединен с входом второго блока кодирования сигнала информации, выход которого соединен с одним из входов третьего смесителя, второй вход которого соединен с выходом первого блока формирования синхропоследовательности и вторым входом блока выделения сигнала информации, выход третьего смесителя соединен с сигнальным входом второго блока передачи, импульсный вход «-оторогс соединен с импульсным выходом второго буферного регистра, выход блока передачи соединен с входом четвертого согласующего трансфс;:мэтора. выход второго является вторым вылодом ретранслятора, причем блок синхронизации состоит из блоков синхронизации по фазе, частоте, задержке и суммирующего блока, причем первые входы блоков синхронизации по Фазе, частоте, задержке, суммирующего С.-ока являются частотным входом блока синхронизации, второй вход блока синхронизации по фазе является сигнальным входом блока синхронизации, второй вход блока синхронизации по задержке является входом обратной связи блока синхронизации, третий вход блока синхронизации по задержке является импульсным входом блока синхронизации, пероый выход блока синхронизации по задержке является управляющим выходом блока синхронизации, третий выход блока синхронизации по задержке является выходом управления подстройками блока синхронизации, выход суммирующего блока является выходом подстроек блока синхронизации, второй выход блока синхронизации г.о задержке соединен с третьим входом блока синхронизации по фазе, первый выход блока синхронизации по частоте соединен с четвертым входом блока синхронизации по задержке, выход блока синхронизации по фазе соединен с вторым входом суммируС блока синхронизации

ющего блока и вторым входом блока синхронизации по частоте, а выход блока синхронизации по частоте соединен с третьим входом суммирующего блока.

Частотный выход

| название | год | авторы | номер документа |

|---|---|---|---|

| Система передачи информации | 1986 |

|

SU1354431A1 |

| СПОСОБ СИНХРОНИЗАЦИИ ЧАСОВ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2010 |

|

RU2426167C1 |

| СПОСОБ СИНХРОНИЗАЦИИ ЧАСОВ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2008 |

|

RU2383914C1 |

| СПОСОБ СИНХРОНИЗАЦИИ ЧАСОВ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2013 |

|

RU2539914C1 |

| СПОСОБ СИНХРОНИЗАЦИИ ЧАСОВ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2015 |

|

RU2613865C2 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| СПОСОБ СИНХРОНИЗАЦИИ ЧАСОВ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2015 |

|

RU2612127C2 |

| СИСТЕМА СВЯЗИ С ШИРОКОПОЛОСНЫМИ СИГНАЛАМИ | 2002 |

|

RU2210860C1 |

| СПОСОБ СИНХРОНИЗАЦИИ ЧАСОВ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2007 |

|

RU2337388C1 |

| Система формирования и приема телевизионного сигнала при передаче изображения | 1988 |

|

SU1555909A2 |

Изобретение относится к технике связи и может использоваться в синхронных сетях обмена дискретной информацией. Цель изобретения - повышение достоверности регистрации путем двунаправленной ретрансляции. С этой целью в устройство введены блок 3 установки, корреляционный приемник 3, буферные регистры 4, 20, фазируемый делитель 5, блоки 6, 23 кодирования сигнала информации, смесители 8. 25, 26, блоки 9. 10. 24 формирования синхропоследователь

С fntWL быделснцр информационного сигнала

Г 4

4

Фиг. 2

Фи&З

На fypepnttd ptiuemp

Фаа4

| Регенератор бинарных сигналов | 1980 |

|

SU944117A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1992-01-23—Публикация

1989-10-16—Подача