Изобретение относится к вычислительной технике и может быть использовано для цифровой обработки четных и нечетных последовательностей, выделения четных и нечетных сигналов на основе дискретного четно-нечетного преобразования Уолша, для цифровой фильтрации, сжатия информацйи, для цифрового спектрально-корреляционного анализа случайных процессов и т.д.

Цель изобретения - расширение функциональных возможностей устройства за счет вычисления преобразования УолшаКачмажа и четно-нечетного преобразования Уолша-Качмажа.

Для обработки четных и нечетных последовательностей используется четно-нечетное преобразование Уолша, по коэффициентам которого определяют четные и нечетные последовательности. Матрица четно-нечетного преобразования Уолша W2 в верхней половине представляет четные cal(k,j) функции Уопша, расположенные в порядке увеличения частности, а в нижней половине - нечетные sal(k,j) функции в порядке уменьшения частности. Матрица W2r для п 3 имеет вид:

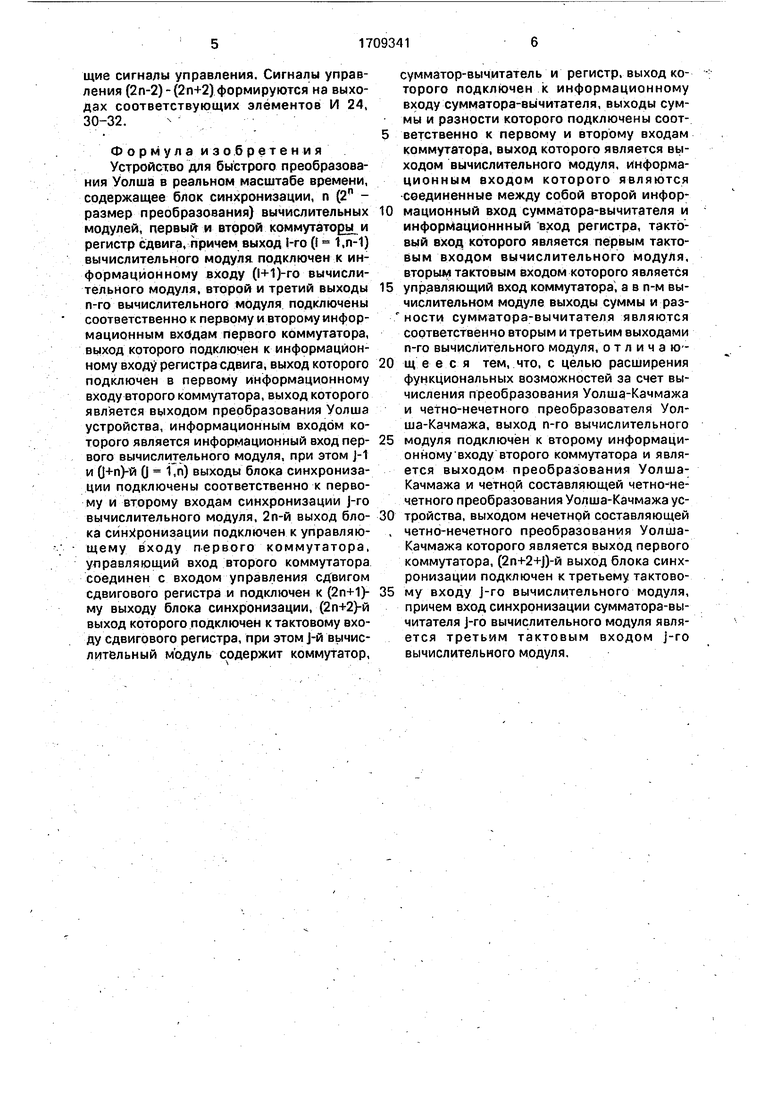

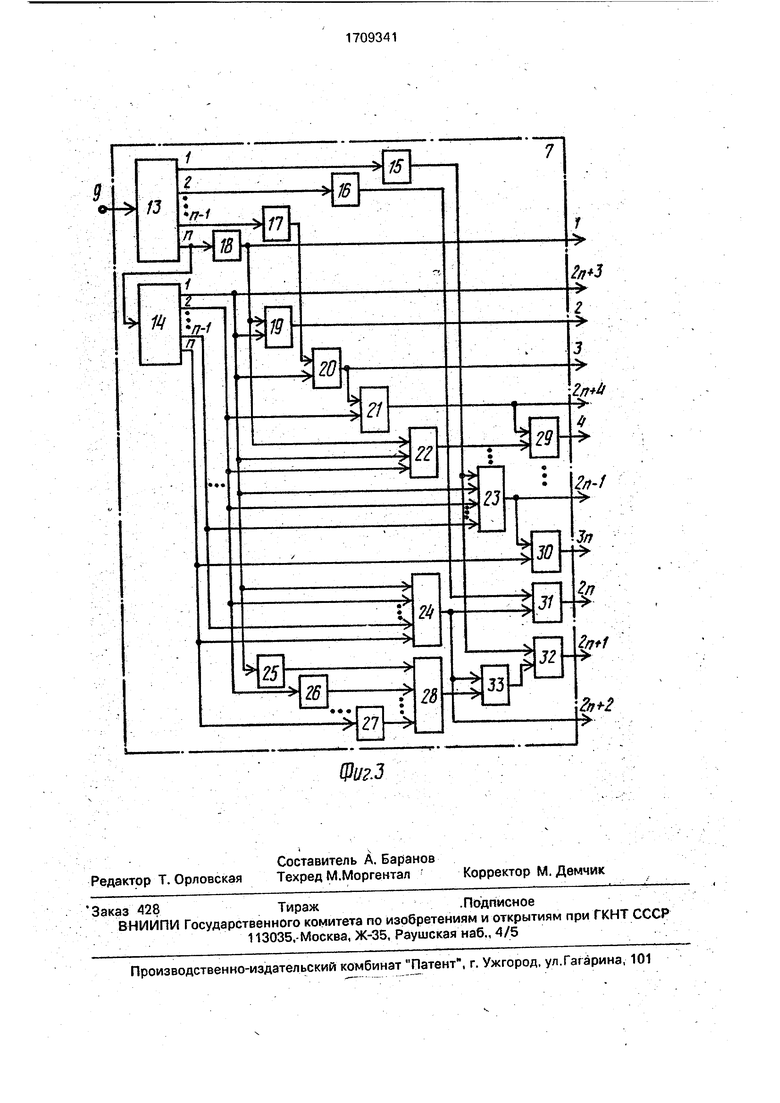

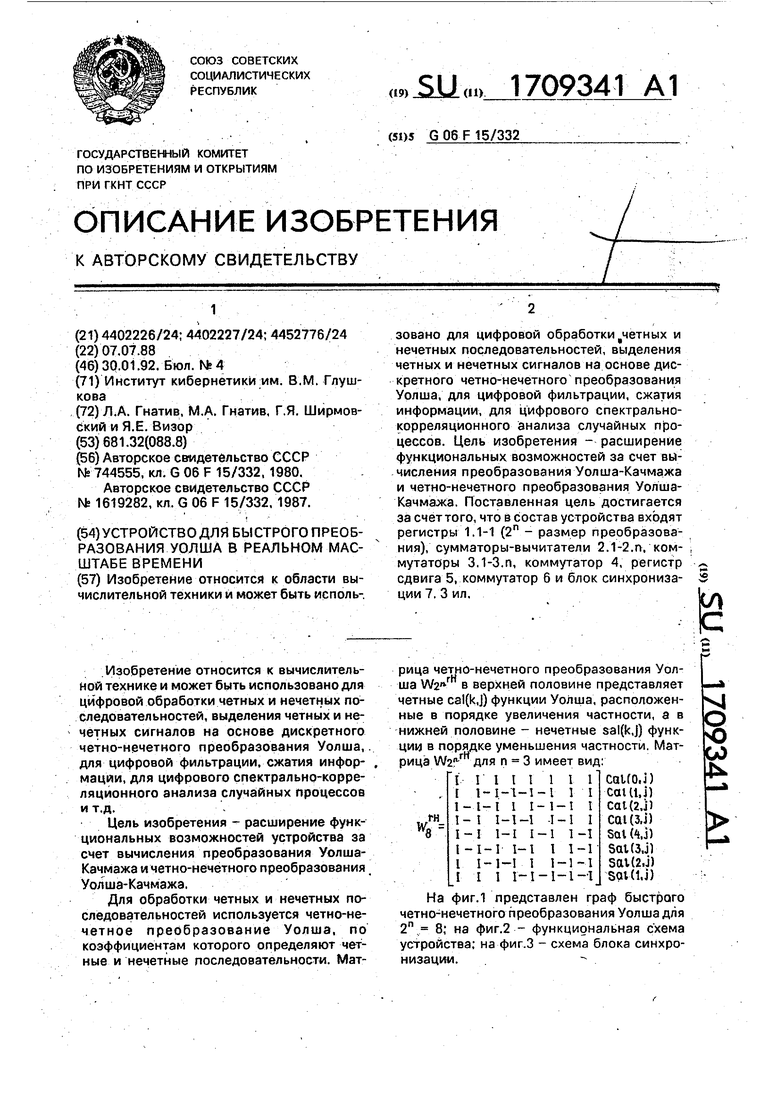

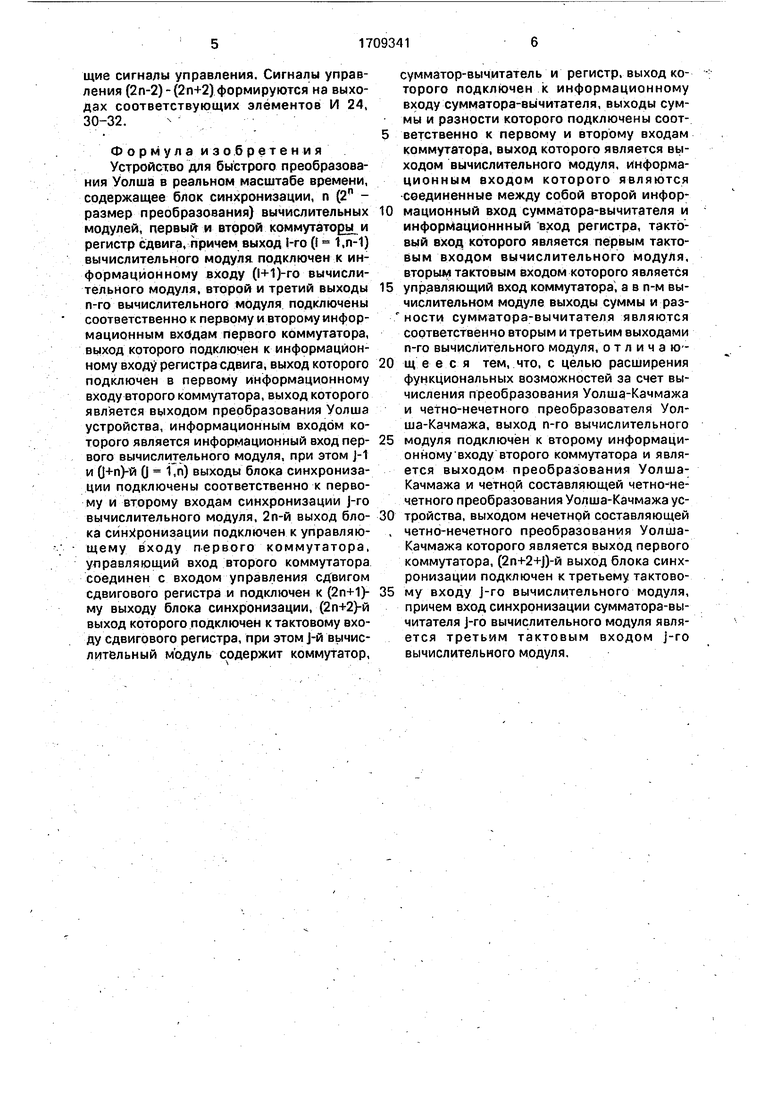

На фиг.1 представлен граф быстрого четно-нечетного преобразования Уолша для 2 8; на фиг.2 - функциональная схема устройства; на фиг.З - схема блока синхронизации. Устройство родержит n регистров 1.11.П, n сумматоров-вычитателей 2.1-2.П, n коммутаторов 3.1-3. п, коммутатор 4, регистр сдвига 5, коммутатор 6 и блок синхронизации 7, информационный вход 8, тактовый вход 9, выход 10 преобразования Уолша, выход 11 преобразования Уолша-Качмажа и частной сбставлягощей четно-нечетного преобразованиЯ;Уолй1а-Качмажа и выход 12 нечетной составляющей четно-нечетного преобразования Уолша-Качмажа. Блок синхронизации (фиг.З) содержит счетчики 13 и 14, элементы НЕ 15-18 и элементы И 19-24, элементы НЕ 25-27, элемент И 28, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 29, элементы И 30-32 ;И элемент ИЛИ 33. Элементы 1,2,3 входят в состав каждого вычислительного модуля 34, а последний модуль содержит дополнительно элементы 4:-6. ... . . ,. , Устройство работает следующим образом. Входная посл едовательность х(1),х(2),,..,, представляющая собой отсчеты дискретного сигнала, с частотой тактовых импульсов поступает на информационный вход регистра 1.1, который управляется тактовым сигналом с выходы 1 блока 7, где задерживается на один такт (в регистре 1.1 хранится один отсчет), и на вычитающий вход сумматОра-вь|читателя 2.1. Срабатывание сумматора-вычитателя 2.1 управляется сигналом с выхода 2п+3 блока 7 и синхронизируется в каждом четном такте. На выход коммутатора 31 в течение каждого такта, начиная сО втОрОго, выводится сначала сумма, а затем разнОсть, сформированные на выходах сумматора-вычитателя 21 в первом каскаде: x(t) + х(2), х(1) - х(2),..., х(2 - 1) + х(2), х(2 - 1)-х(2)ит.д. В 1-М(1 2...П 1) каскаде преобразования последовательность промежуточных /данных, получаемых с выхода коммутатора 3.1-1 предыдущего (1-1)-го каскада, поступает на информационный вход регистра 1.1 и на йычйтающий входсумматора-вычитате ля2.1 ;частотой, в2 . раз большей частоты следования отсчетов входного сигнала. В ;, регистре 1.1 данные задерживаются на 2 тактов. Срабатывание сумматора-вычитателя 2,11-го каскада синхронизируется сигналом с выхода блока 7. На выход : коммутатора 3.1 в течение ка кдого такта работы регистра 1.1 в нечетных тактах выS.. водятся результаты: сумма, а затем разность, а в чет|; ых тактах выводится разность, а затем сумма, сформированные в соответствии с графом преобразования (фиМ) на выходах сумматора-вычитателя 2.1 в t-M каскаде:/ Xia) + xiO + ) + 2-),J 1,3,5.... Х10)-Х1а + 2Лх|0) + + 2Л 2,4,6.... В п-м кас,каде преобразования данные с выхода коммутатора З.п-1 (n-l)-ro каскада поступают на информационный вход регистра 1 .п и на вычитающий вход сумматора-вычитателя 2.n с частотой, в раз большей частоты следования отсчетов входного сигнала. В регистре 1.п данные задерживаются на тактов. В течение каждого TaKta работы регистра 1.h в нечетные такты, через коммутатор З.п на вь1ход {п+2)-го коммутатора 6 выводятся суммы, а в нечетные такты - разности, представляющие собой коэффициенты ) преобразования При четных са1 функциях олша. При этом все коэффициентов преобразования выводятся до прихода ()-го отсчета входного сигнала. Одновременно с этим в нечетные такты через (п+1)-й коммутатор 4 в регистр сдвига 5 заносятся разности, а в четные такты - суммь), которые представляют собой коэффициенты ) преобразования, при нечетных sal функциях Уолша. После прихода ()-го тактового сигнала происходит по сигналу управления сдвигом считывание в обратном порядке коэффициентов ) преобразования с регистра сдвига 5, которые выводятся на выход (п+2)-го коммутатора б с частотой, в раз большей частоты следования отсчетов входного сигнала. Последний коэффициент x(j) преобразования выводится на выход ()-го коммутатора 6 до прихода ()-го отсчета входного сигнала. .В устройстве на интервале дискретизации получаются все Коэффициенты преоб-. разования от 2 отсчетов входного сигнала, что обеспечивает его работы в реальном масштабе времени.. Блок управления 7 работает следующим образом. С приходом импульсов. Поступающих на счетный вход 9 первого счетчика 13, на выходе п-го (старшего) разряда этого счетчика формируется инверсный сигнал управления, который проходит через п-й элемент НЕ 18, а также поступает на счетный вход второго счетчика 14. Сигналы с выходов с первого (младшего) по п-й разрядов первого счетчика 13 через элементы НЕ 15-18 и сигналы с выходов с первого по п-й (старший) разрядов второго счетчика 14 поступают на соответствующие входы элементов И 19-24 и через элементы НЕ 25-27 поступают на входы элемента И 28. При этом на выходе первого разряда второго счетчика 14 формируется сигнал управления 2п+3, а на выходах элементов И 19-21 и первого элемента ИСКЛЮЧАЮЩИЕ ИЛИ 29 формируются соответствующие сигналы управления. Сигналы управления (2п-2)-{2п+2) формируются на выходах соответствующих элементов И 24, 30-32.Формул а изобретения Устройство для быстрого преобразования Уолша в реальном масштабе времени, содержащее блок синхронизации, п (2 размер преобразования) вычислительных модулей, первы и второй коммутаторы и регистр сдвига, причем выход 1-го (( 1,п-1) вычислительного модуля, подключен к информационному входу (1+1 )-го вычислительного модуля, второй и третий выходы п-го вычислительного модуля подключены соответственно к первому и второму информационным вхбдам первого коммутатора, вмход которого подключен к информационному входу регистра сдвига, выход которого подключен в первому информационному входу второго коммутатора, выход которого является выходом преобразования Уолша устройства, информационным входом которого является информационный вход первого вычислительного модуля, при этом J-1 и 0+п)-1й О 1,п) выходы блока синхронизации подключены соответственно к первому и второму входам синхронизации j-ro вычислительного модуля, 2п-й выход блока синхронизации подключен к управляющему входу первого коммутатора, управляющий вход второго коммутатора соединен с входом управления сДвигом сдвигового регистра и подключен к (2п+1)му выходу блока синхронизации, (2п+2}-й выход которого подключен к тактовому входу сдвигового регистра, при этом j-й вьнислитвльный модуль содержит коммутатор.

умматор-вычитатель и регистр, выход которого подключен к информационному входу сумматора-вычитателя, выходы суммы и разности которого подключены соответственно к первому и второму входам коммутатора, выход которого является вь1ходом вычислительного модуля, информационным входом которого являются соединенные между собой второй информационный вход сумматора-вычитателя и информацйоннный вход регистра, тактовый вход которого является первым тактовым входом вычислительного модуля, вторым тактовым входом которого является

управляющий вход коммутатора, а в п-м вычислительном модуле выходы суммы и разности сумматора-вычитателя являются соответственно вторым и третьим выходами п-го вычислительного модуля, отличающ е е с я тем, что, с целью расширения функциональных возможностей за счет вычисления преобразования Уолша-Качмажа и чеТно-нечетного преобразователя Уолша-Качмажа, выход п-го вычислительного

модуля подключён к второму информационномувходу второго коммутатора и является выходом преобразования УолшаКачмажа и четной составляющей четно-нечетного преобразования Уолша-Качмажа устройства, выходом нечетной составляющей четно-нечетного преобразования УолшаКачмажа которого является выход первого коммутатора, (2п+2+)-й выход блока синхронизации подключен к третьему тактовому входу j-ro вычислительного модуля, причем вход синхронизации сумматора-вычитателя j-ro вычислительного модуля является третьим тактовым входом j-ro вычислительного модуля.

.-

Фяг I

I

h

./

(s)

о сложение

БК7атаийв

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для выполнения быстрого преобразования Уолша | 1989 |

|

SU1693612A1 |

| Устройство для выполнения быстрого преобразования Уолша на скользящем интервале | 1990 |

|

SU1789990A1 |

| Устройство для выполнения быстрого преобразования Уолша-Адамара | 1988 |

|

SU1605254A1 |

| Устройство для быстрого преобразования Уолша-Адамара | 1987 |

|

SU1443002A1 |

| Устройство для ортогонального преобразования цифровых сигналов по Уолшу на скользящем интервале | 1987 |

|

SU1619298A1 |

| Устройство для быстрого ортогонального преобразования цифровых сигналов по Уолшу-Адамару | 1989 |

|

SU1615742A1 |

| Процессор быстрого преобразования уолша-адамара | 1989 |

|

SU1795471A1 |

| Устройство для выполнения быстрого преобразования Уолша | 1987 |

|

SU1425707A1 |

| Устройство быстрого преобразования сигналов по Уолшу с упорядочением по Адамару | 1984 |

|

SU1265795A1 |

| Устройство для ортогонального преобразования по Уолшу-Адамару | 1988 |

|

SU1571610A1 |

Изобретение относится к области вычислительной техники и может быть использовано для цифровой обработки ^четных и нечетных последовательностей, выделения четных и нечетных сигналов на основе дискретного четно-нечетного преобразования Уолша, для цифровой фильтрации, сжатия информации, для цифрового спектрально- корреляционного анализа случайных процессов. Цель изобретения - расширение функциональных возможностей за счет вычисления преобразования Уолша-Качмажа и четно-нечетного преобразования Уолша- Качмажа. Поставленная цель достигается за счет того, что в состав устройства входят регистры 1.1-1

J

л

Д

.f

/г-/ S

J/7

г/7

NL

t

/7

L..

//

3i.

7/

ю

I

А/2

ФигЗ

| Устройство для вычисления коэффициентов преобразования по уолшу | 1975 |

|

SU744555A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-01-30—Публикация

1988-04-01—Подача