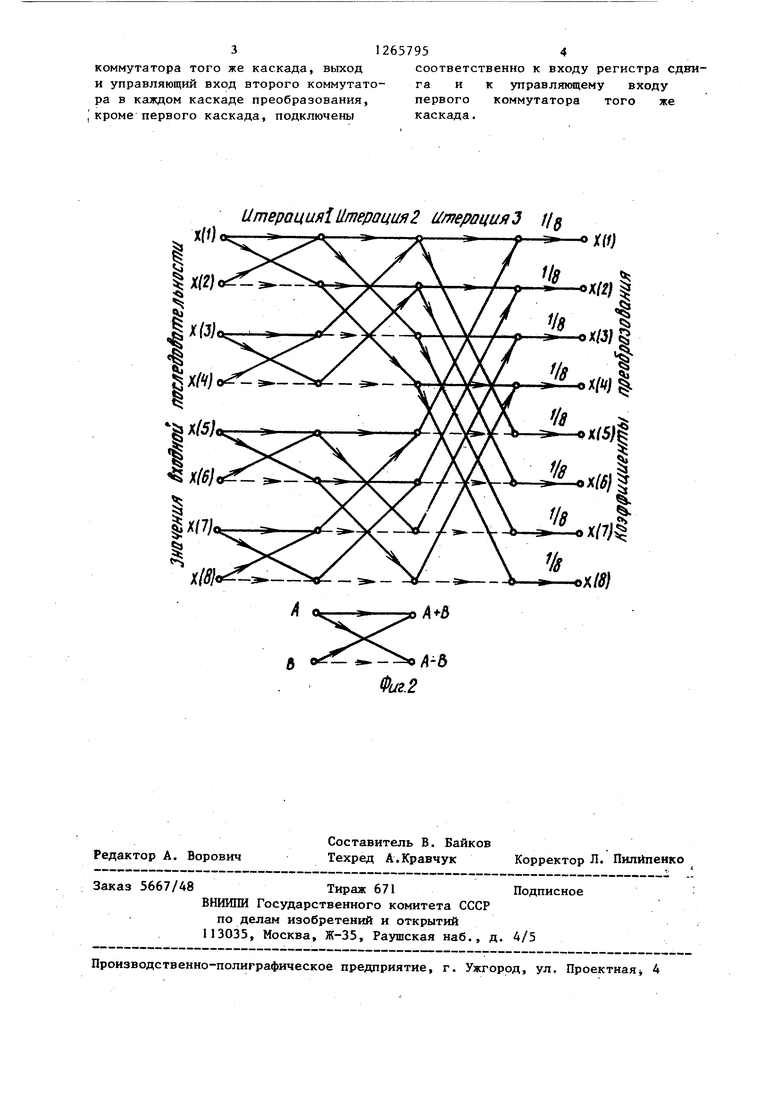

фиг. 1 Изобретение относится к автоматике и вычислительной технике и может быть использовано для спектрального и корреляционного анализа случайных процессов, для цифровой фильтрации, сжатия информации, в технике связи и т.д. Целью изобретения является упрощение устройства. На фиг. 1 представлена функционал ная схема устройства быстрого преобразования сигналов по Уолшу с упорядочением по Адамару; на фиг.2 - граф быстрого преобразования Уолша с упорядочением по Адамару. Устройство содержит коммутаторы 1 регистры 2 сдвига, сумматоры-вычитатели 3, коммутаторы А и счетчик 5 тактовьтх импульсов. Устройство работает следующим образом. . Последовательность х, х , ...,Х(, отсчетов входного сигнала с частотой тактовых импульсов поступает на вход регистра 2 сдвига первого каскада и задерживается в нем на один такт (в разряде регистра сдвига хранится оди отсчет). Срабатьшание сз мматора-вычитателя 3 первого каскада синхронизируется в каждом четном такте с запоминанием результатов (сумма и ра ность) до следующего четного такта. На выход коммутатора 4 первого каска да, управляемого с выхода первого (младшего) разряда счетчика 5 тактовых импульсов, в четных тактах выводятся суммы, а в нечетных - разности сформированные в первом каскаде ,; V V - М-1 X ц и т.д., начиная с второго такта (в первом такте формируется ра.зность последней пары отсчетов из предьщущей выборки). В i-M (, n logjN) -каскаде в соответствии с графом преобразований (фиг.2) последовательность промежуто ных данных задерживается в регистре тактов. Суммы в тече /: сдвига на ние 2 тактов вьшодятся на выход ком мутатора 4, а разности записываются в регистр 2 сдвига через,коммутатор течение следующих 2 тактов 1. В разности из регистра 2 сдвига выводятся на выход коммутатора 4 и одновременно регистр,заполняется очередной группой из 2 данных, поступающих на вход коммутатора 1 из 1-1-го каскада. Управление коммутаторами 1-го каскада осуществляется с выхода 1-го разряда счетчика 5. Последовательность коэффициентов преобразования формируется на выходе коммутатора 4 п-го каскада. Формула изобретения Устройство быстрого преобразования сигналов по Уолшу с упорядочением по Адамару, содержащее п-разрядный счетчик и п каскадов преобразования (п , где N - длина преобразуемой последовательности), каждый из которых содержит первый коммутатор, сумматор-вычитатель и 2-.-; разрядный регистр сдвига (номер каскада преобразования), причем счетный вход счетчика является тактовым входомустройства,выход i-го разряда счетчика подключен к управляющему входу первого коммутатора в 5-м каскаде преобразования, вход регистра сдвига и первый вход сумматора-вычитателя в первом каскаде преобразования подключены к информационному входу устройства, выход регистра сдвига в каждом каскаде преобразования подключен к второму входу сумматоравычитателя, выход суммы которого подключен к первому информационному входу первого коммутатора в том же каскаде преобразования, выход первого коммутатора i-ro каскада преобразования, кроме п-го каскада, подключен к первому входу сумматора-вычитателя (i+i)-ro каскада, выход первого коммутатора fj -го каскада преобразования является выходом устройства, отличающееся тем, что, с целью упрощения, оно содержит второй коммутатор в каждом каскаде пре образования, кроме первого каскада, выход разности сумматора-вычитателя в первом каскаде преобразования подключен к второму информационному входу коммутатора первого каскада, второй информационный вход первого коммутатора и первый информационный вход второго коммутатора в каждом каскаде преобразования, кроме первого каскада, подключены соответств нно к второму и первому входам сумматора-вычитателя того же каскада, выход разности сумматора-вычитателя г каждого каскада преобразования, кроме первого каскада, подключен к второму информационному входу второго

коммутатора того же каскада, выход и управляющий вход второго коммутатора в каждом каскаде преобразования, ,кроме первого каскада, подключены

соответственно к входу регистра сдвига и к управляющему входу первого коммутатора того же каскада.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для быстрого преобразования Уолша-Адамара | 1988 |

|

SU1536398A1 |

| Устройство для выполнения быстрого преобразования Уолша | 1987 |

|

SU1425707A1 |

| Устройство для быстрого преобразования Уолша в реальном масштабе времени | 1988 |

|

SU1709341A1 |

| Устройство для выполнения быстрого преобразования Уолша-Адамара | 1988 |

|

SU1605254A1 |

| Устройство для выполнения быстрого преобразования Уолша | 1989 |

|

SU1693612A1 |

| Устройство для быстрого преобразования Уолша-Адамара | 1987 |

|

SU1443002A1 |

| Устройство для быстрого ортогонального преобразования цифровых сигналов по Уолшу-Адамару | 1989 |

|

SU1615742A1 |

| Устройство быстрого преобразования сигналов по Уолшу с упорядочением по Адамару | 1990 |

|

SU1784996A1 |

| Устройство для ортогонального преобразования цифровых сигналов по Уолшу на скользящем интервале | 1987 |

|

SU1619298A1 |

| ПРОЦЕССОР БЫСТРОГО ПРЕОБРАЗОВАНИЯ СИГНАЛОВ ПО УОЛШУ С УПОРЯДОЧЕНИЕМ ПО АДАМАРУ | 1991 |

|

RU2025772C1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано для спектрального и корреляционного анализа случайных процессов, для цифровой фильтрации, сжатия информации, в технике связи. Целью изобретения является упрощение устройства. Устройство содержит две группы коммутаторов 1,4, регистры 2 сдвига, группу сумматоров -вычитателей 3, счетчик 5 тактовых импульсов. Поставленная цель достигается вышеуказанной сово(Л купностью признаков. 2 ил.

итерация Итерация2 1/терацияЗ //

/ А I ,.S.XZ I

i r$$VVVy

|.«...W, ..«I

i6}

M

| Устройство ортогонального преобразования цифровых сигналов по Уолшу-Адамару | 1980 |

|

SU951320A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Патент США 3792355, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1986-10-23—Публикация

1984-08-02—Подача