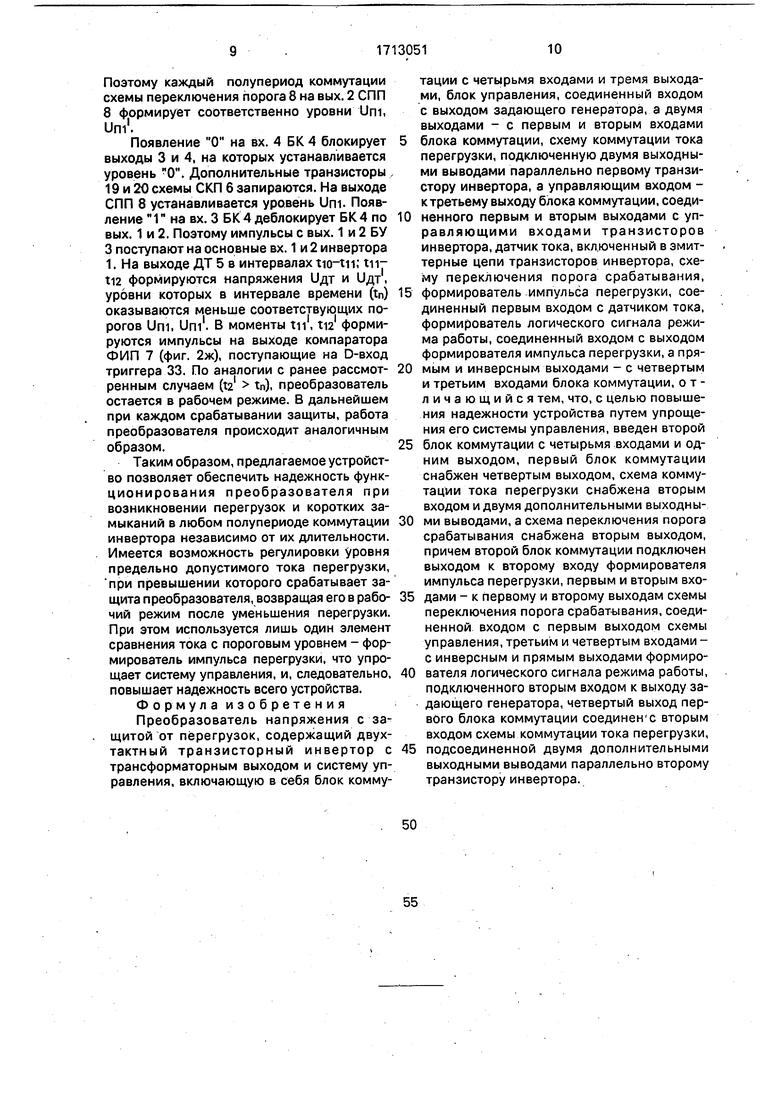

СКОРО сигнала режима работы. Вых. 1 и 2 формирователя 10 соединены с вх. 4 и вх. 3 первого блока 4 коммутации и вх. 4 и 3 второго блока 9 коммутации.

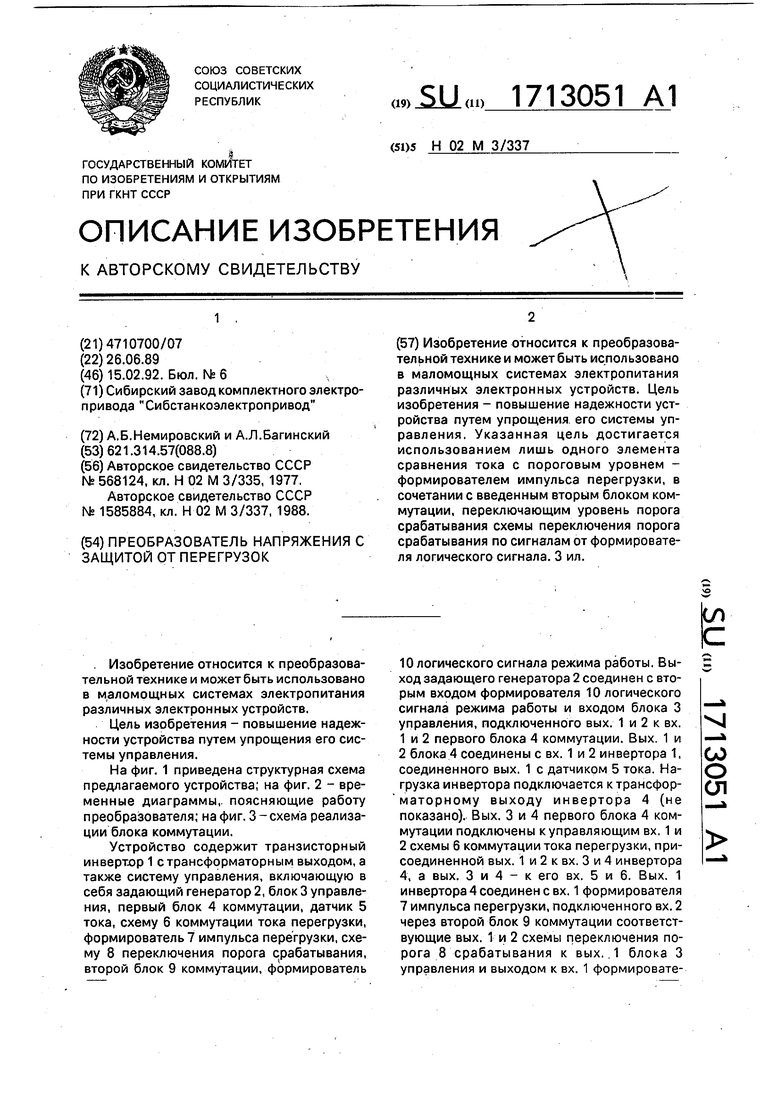

Задающий генератор 2(3.Г.) служит для формирования кратковременных тактовых импульсов. Блок управления 3 (БУ)выполненный на триггере 11, предназначен для формирования входных импульсов двухтактного транзисторного инвертора 1 и управления работой схемы переключения порога 8 срабатывания.

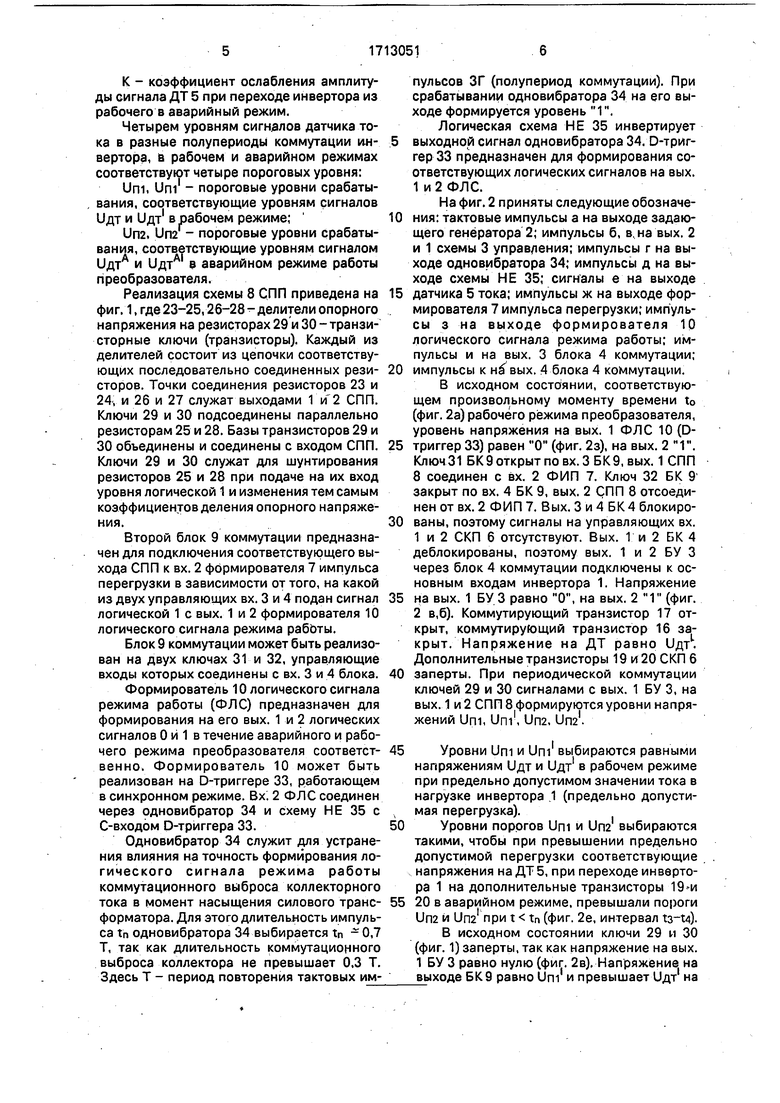

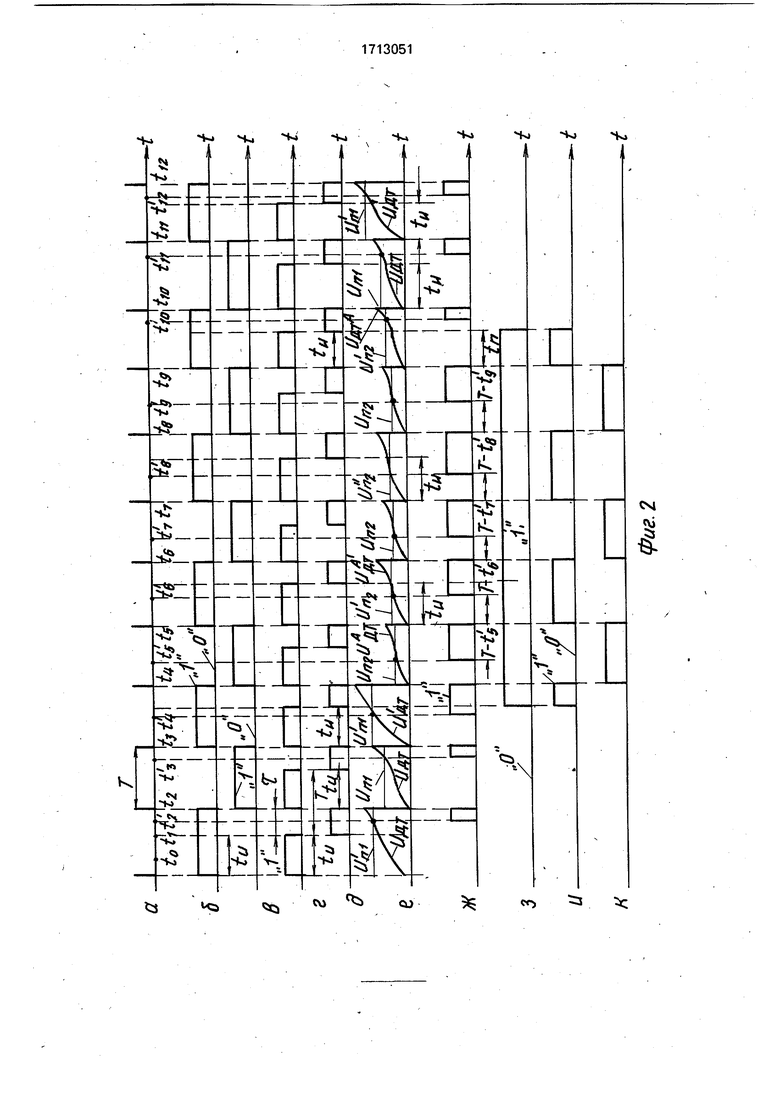

Первый блок 4 коммутации (БК) может быть выполнен на логических элементах И 12-15 и служит для отключения выходов 1 и 2 блока 3 управления от основных вх. 1 и 2 инвертора 1 при возникновении аварийного режима и подключения вых. 1 и 2 БУ к управляющим вх. 1 и 2 схемы 6 коммутации тока перегрузки.

Транзисторный инвертор 4 (ТИ) с трансформаторным выходом служит для преобразования напряжения источника постоянного напряжения в переменное и выполнен по двухтактной схеме с независимым возбуждением и выводом средней точки первичной обмотки трансформатора, к которой подключается один из выводов источника напряжения. В ТИ установлены первый и второй транзисторы 16 и 17, базы которых служат двумя основными входами - вх. 1 и 2. Дополнительными вх. 3-5 и входом 6 служат коллекторы и эмиттеры транзисторов 16 и 17 соответственно.

Датчик 5 тока (ДТ) предназначен для получения напряжения, пропорционального коллекторному току транзисторов 16 и 17 инвертора 4, и выполнен на измерительном резисторе 18, включенном между эмиттерами транзисторов 16 и 17 и общей точкой схемы, к которой подключен другой вывод источника напряжения.

Нагрузка инвертора 4 может быть выполнена, например, в ви.де двухполупериодного выпрямителя с выходным RCфильтром.

Схема 6 коммутации тока перегрузки (СКП) г1редназначена для формирования напряжения на датчике 5 тока во время каждого полупериода коммутации инвертора при работе преобразователя в режиме перегрузки и короткого замыкания. СКП реализована в виде дополнительных транзисторов 19 и 20 той же проводимости, что и коммутирующие транзисторы 16 и 17 инвертора 4. В коллекторных цепях транзисторов 19 и 20 установлены резисторы 21 и 22. При этом транзисторы 19 И 20 работают при отпирании (в ключевом режиме) в области насыщения, что обеспечивает высокую чувствительность датчика 5 тока и температурную стабильность выходного напряжения. Для обеспечения ключевого режима транзисторов 19 и 20 выбираются соответстиующие токи базы. Вторые концы резисторов 21 и 22 и эмиттеры дополнительных транзисторов 19 и 20 являются соответственно вых. 1-4 СКП.

Формирователь 7 импульса перегрузки

(ФИП) служит для формирования на его выходе перепада напряжения при превышении сигналом на выходе ДТ порога срабатывания формирователя. ФИП может быть выполнен по схеме компаратора или

операционного усилителя.

Схема переключения порога 8 срабатывания (СПП) предназначена для изменения порога ррабатывания формирователя 7 импульса перегрузки в каждом полупериоде

коммутации ТИ при рабочем режиме, а также при переходе преобразователя из рабочего в аварийный режим работы. Необходимость в измерении порога каждый полупериод коммутации при рабочем режиме преобразователя объясняется тем, что из-за разброса параметров транзисторов 16 и 17, несимметрии коллекторных полуобмоток трансформатора инвертора на резисторе 18 датчика 5 тока каждый полупериод

формируются напряжения разной амплитуды.

При переходе ТИ в аварийный режим ДТ запитывается коллекторными токами, протекающими через те же полуобмотки

трансформатора, но подключенными к коллекторам транзисторов 19 и 20 через резисторы 21 и 22 соответственно. Поэтому уровни формируемых напряжений на резисторе 18 ДТ каждый полупериод коммутации отличаются друг от друга. При этом они изменяются по сравнению с уровнями сигналов, формируемыми в рабочем режиме. С учетом сказанного формируемые на резисторе 18 ДТ уровни сигналов имеют значения:

идт - сигналы на резисторе 18 ДТ в одном из полупериодов коммутации в рабочем режиме;

идт - сигналы на резисторе 18 ДТ в

смежном полупериоде коммутации в рабочем режиме;

А идт

идГ

сигналы на резисторе 18

К

ДТ в одном из полупериодов коммутации в аварийном режиме;

идт У -сигналы на резисторе 18

14

ДТ в смежном полупериоде коммутации в аварийном режиме;

К - коэффициент ослабления амплитуды сигнала ДТ 5 при переходе инвертора из рабочего в аварийный режим.

Четырем уровням сигналов датчика тока в разные полупериоды коммутации инвертора, 13 рабочем и аварийном режимах соответствуют четыре пороговых уровня;

Uni, Uni - пороговые уровни срабатывания, соответствующие уровням сигналов идт и идт в рабочем режиме;

ип2, ип2 - пороговые уровни срабатывания, соответствующие уровням сигналом идт и в аварийном режиме работы преобразователя.

Реализация схемы 8 СПП приведена на фиг. 1, где 23-25,26-28 - делители опорного напряжения на резисторах29 и30-транзисторные ключи (транзисторы). Каждый из делителей состоит из цепочки соответствующих последовательно соединенных резисторов. Точки соединения резисторов 23 и 24, и 26 и 27 служат выходами 1 и2 СПП. Ключи 29 и 30 подсоединены параллельно резисторам 25 и 28. Базы транзисторов 29 и 30 объединены и соединены с входом СПП. Ключи 29 и 30 служат для шунтирования резисторов 25 и 28 при подаче на их вход уровня логической 1 и изменения тем самым коэффициентов деления опорного напряжения.

Второй блок 9 коммутации предназначен для подключения соответствующего выхода СПП к вх. 2 формирователя 7 импульса перегрузки в зависимости от того, на какой из двух управляющих вх. 3 и 4 подан сигнал логической 1 с вых. 1 и 2 формирователя 10 логического сигнала режима рабЬты.

Блок 9 коммутации может быть реализован на двух ключах 31 и 32, управляющие входы которых соединены с вх. 3 и 4 блока.

Формирователь 10 логического сигнала режима работы (ФЛС) предназначен для формирования на его вых. 1 и 2 логических сигналов О и 1 в течение аварийного и рабочего режима преобразователя соответственно. Формирователь 10 может быть реализован на Ь-триггере 33, работающем в синхронном режиме. Вх. 2 ФЛС соединен через одновибратор 34 и схему НЕ 35 с С-входом Р-триггера 33.

Одновибратор 34 служит для устранения влияния на точность формирования логического сигнала режима работы коммутационного выброса коллекторного тока в момент насыщения силового трансформатора. Для этого длительность импульса tn одновибратора 34 выбирается tn -0,7 Т, так как длительность коммутационного выброса коллектора не превышает 0,3 Т. Здесь Т - период повторения тактовых импульсов ЗГ (полупериод коммутации). При срабатывании одновибратора 34 на его выходе формируется уровень 1.

Логическая схема НЕ 35 инвертирует

выходной сигнал одновибратора 34. D-триггерЗЗ предназначен для формирования соответствующих логических сигналов на вых. 1 и 2 ФЛС.

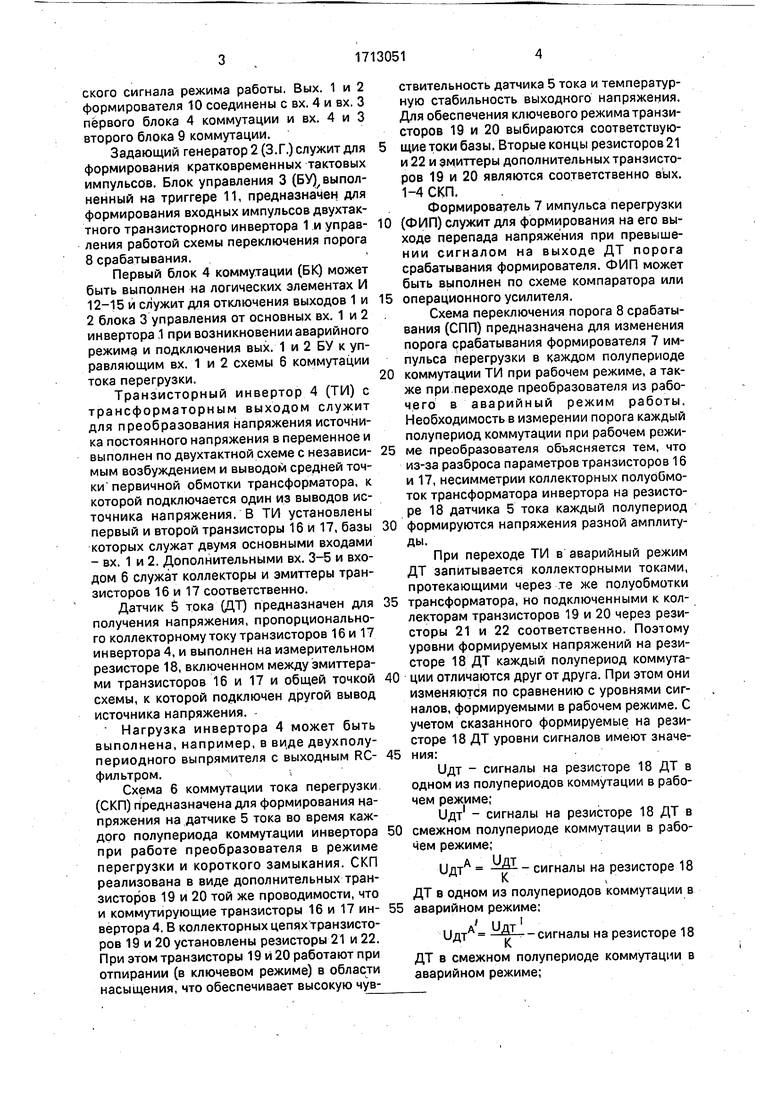

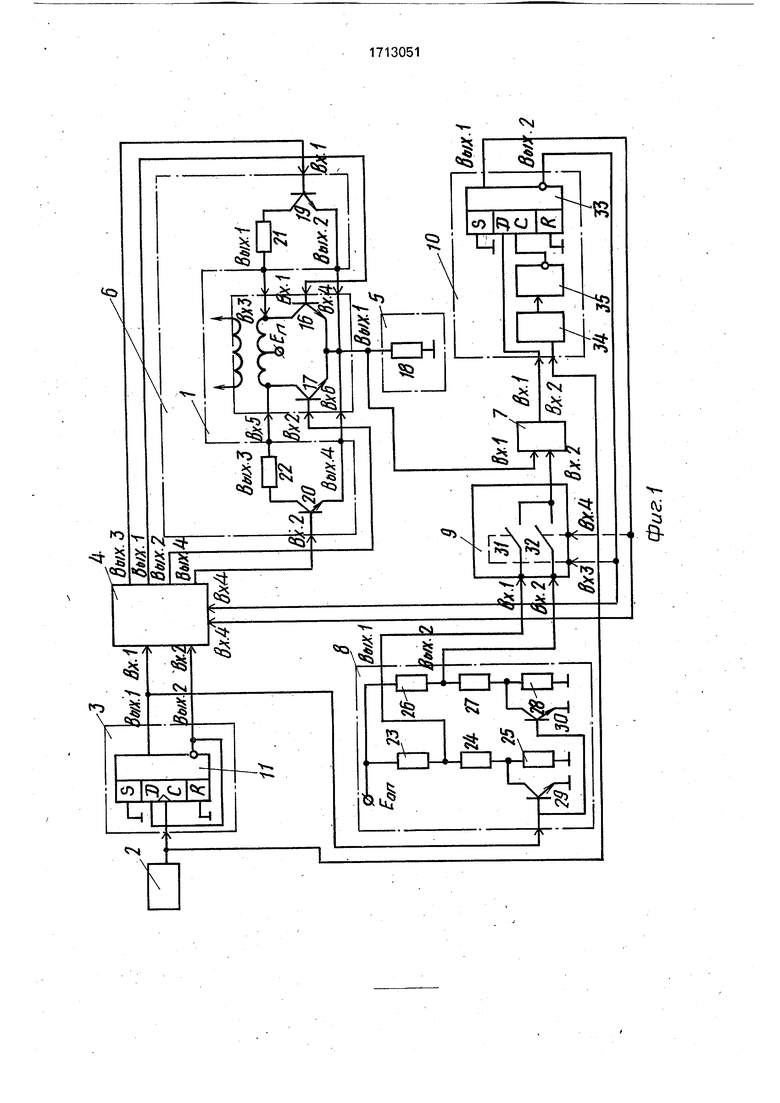

На фиг. 2 приняты следующие обозначения: тактовые импульсы а на выходе задающего генератора 2; импульсы б, в, на вых. 2 и 1 схемы 3 управления; импульсы г на выходе одновибратора 34; импульсы д на выходе схемы НЕ 35; сигналы е на выходе

датчика 5 тока; импульсы ж на выходе формирователя 7 импульса перегрузки; импульсы 3 на выходе формирователя 10 логического сигнала режима работы; импульсы и на вых. 3 блока 4 коммутации;

импульсы к . 4 блока 4 коммутации.

В исходном состоянии, соответствующем произвольному моменту времени to (фиг. 2а) рабочего режима преобразователя, уровень напряжения на вых. 1 ФЛС 10 (Dтриггер 33) равен О (фиг. 2з), на вых. 2 1. Ключ31 БК9открытповх.ЗБК9,вых. 1 СПП 8 соединен с вх. 2 ФИП 7. Ключ 32 БК 9 закрыт по вх. 4 БК 9, вых. 2 СПП 8 отсоединен от вх. 2 ФИП 7. Вых. Зи4 БК4блокированы, поэтому сигналы на управляющих вх.

1и 2 СКП 6 отсутствуют. Вых. 1 и 2 БК 4 деблокированы, поэтому вых. 1 и 2 БУ 3 через блок 4 коммутации подключены к основным входам инвертора 1. Напряжение

на вых. 1 БУ 3 равно О, на вых. 2 1 (фиг.

2в,б). Коммутирующий транзистор 17 открыт, коммутирующий транзистор 16 закрыт. Напряжение на ДТ равно идтН Дополнительные транзисторы 19 и 20 СКП 6

заперты. При периодической коммутации ключей 29 и 30 сигналами с вых. 1 БУ 3, на вых. 1 и 2 СПП 8 формируются уровни напряжений Uni, Uni, Un2, Una.

Уровни Uni и Uni выбираются равными напряжениям идт и идт в рабочем режиме при предельно допустимом значении тока в нагрузке инвертора ,1 (предельно допустимая перегрузка).

Уровни порогов Uni и Una выбираются такими, чтобы при превышении предельно допустимой перегрузки соответствующие напряжения на ДТ 5, при переходе инвертора 1 на дополнительные транзисторы 19-и

20 в аварийном режиме, превышали пороги Un2 и Una при t tn (фиг. 2е, интервал t3-t4). В исходном состоянии ключи 29 и 30 (фиг. 1) заперты, так как напряжение на вых. 1 БУ 3 равно нулю (фиг. 2в). Напряжение на выходе БК9 равно Uni и превышает идт на

ДТ 5 (вх. 1 ФИП 7). На выходе одновибратора 34 формируется уровень 1.

В момент ti-tn на выходе схемы НЕ 35 формируется импульс 1 длительностью г Т - tn, поступающий на С-вход триггера 33 (фиг. 2д). При сравнении Удт с уровнем Uni (фиг. 2е) в момент ta на выходе компаратора ФИП 7 формируется импульс 1 (фиг, 2ж), поступающий на D-вход триггера 33. Так как t2 tn, т.е. сигнал на D-вход триггера 33 поступает позже импульса на С-входе, D-триггер, согласно алгоритму его работы остается в прежнем состоянии (информация в триггер 33 не записывается). Напряжение на вых. 1 ФЛС 10 (триггера 33) равно 0. Поэтому преобразователь остается в рабочем режиме.

В следующем полупериоде коммутации (интервал t2-t3) инвертора при t ta напряжение на вых. 1 БУ 3 остановится равным 1 на вых. 2 - О (фиг. 2в. б). При этом коммутирующий транзистор 17 закрывается, транзистор 16 открывается. Напряжение на ДТ 5 равно Удт (фиг. 2е). Транзисторы 29 и 30 открываются, шунтируя резисторы 25 и 28. На выходах 1 и 2 СПП В устанавливаются соответствующие уровни Uni и Un2. Напряжение на вх. 2 ФИП 7 равно Uni, на вх. 1 идт.

Сопоставляя в данном полупериоде моменты (ts) пересечения Удт с порогом Dm и формирования импульса 1 на выходе НЕ 35 длительностью г Т - tn, видим, что ta tn. Поскольку это соотношение аналогично предыдущему полупериоду (ta tn), D-триггер 33 остается в прежнем состоянии. Поэтому преобразователь продолжает функционировать в рабочем режиме.

Предположим, что в некоторый момент (ts) происходит перегрузка инвертора 1 по току, превышающая предельно допустимую величину - начало аварийного режима. Вследствие этого напряжение Удт на датчике 5 тока (фиг. 2е) превышает пороговый уровень Unr в момент tn.

На выходе ФИП 7 формируется импульс 1 (фиг. 2ж). Так как при этом импульс на О-вход триггера 33 поступает раньше, чем появится уровень 1 на С-входе, на вых. 1 ФЛС 10 формируется 1 (фиг. 2з). На вых. 2 ФЛС 10 устанавливается уровень О. Появление 1 на вх. 4 БК 4 деблокирует выходы 3 и 4 БК 4, появление О на вх. 3 БК 4 блокирует БК 4 по вых. 1 и 2. Кроме того, появление 1 на управляющем вх. 4 БК9 и О на вх. 3 БК9 откоывает ключ 32. который соединяет выхч2 СПП 8 с вх. 2 .ФИП 7. Ключ 31 запирается и отсоединяет вых. 1 СПП 8 от вх. 2 ФИП 7. Каждый полупериод коммутации схемы переключения порога 8 на вых. 2 СПП 8 формируются пороговые уровни ип2 (интервалы t4-t5; te-ty) и Una (интервалы t5-t6: t7-t8, поступающие через ключ 32 на

вх. 2ФИП7.

Деблокирование вых. 3 и 4 БК 4 приводит к тому, что на его вых. 3 и 4 и соединенных с ними управляющих входах 1 и 2 СКП 6 начинают формироваться импульсы, определяемые логическими уровнями сигналов на вх. 1 и вх. 2 БК 4 (фиг. 2 и, к). На основных входах 1 и 2 инвертора 1 устанавливаются нулевые уровни сигналов. Поэтому коммутирующие транзисторы 16 и 17 Запираются.

5 При появлении 1 на управляющем входе транзистора 19 (интервалы времени t4-t5; te-ty) он открывается и на выходе датчика 5 тока формируются импульсы напряжения (фиг. 2е), амплитуда которых оказывается

0 пропорциональной току перегрузки. Аналогичнре происходит при появлении 1 на входе транзистора 20, который открывается в интервалах времени ts-te: ty-ts. При этом на выходе ДТ 5 формируются напряжения

5 .

В ава|)ийном режиме на выходе компаратора ФИП 7 формируются импульсы (фиг. 2ж), возникающие в моменты времени ts, te, ty, te, tg. При этом моменты tz появления

0 передних фронтов соответствующих импульсов на Ь-входе триггера 33 находятся внутри временного интервала tn, т.е. соотношение времени поступления импульсов на вх. 1 и вх. 2 ФЛС 10 остается таким же,

5 как при возникновении аварийного режима. Предположим, что аварийный режим оканчивается в момент времени tg (фиг. 2а). Снижение перегрузки ниже предельно допустимого уровня приводит к уменьшению

0 напряжения на выходе ДТ 5.

Сигнал на вх. 1 ФИП 7 (идт) становится меньше уровня Una на вх. 2 (фиг. 2а). Поэтому момент tio равенства входных напряжений при возникновении на ДТ 5

5 коммутационного выброса тока оказывается вне интервала 0-tn. На выходе ФИП 7 в момент tio формируется импульс 1 (фиг. 2и), поступающий на D-вход триггера 33. Так как tio tn, т.е. сигнал на D-вход

0 поступает позже импульса на С-входе (фиг. 2д), D-триггер 33, согласно алгоритму его работы, меняет состояние и на выходе 1 ФЛС 10 устанавливается уррвень О, на выходе 2 - 1 (фиг. 2з). Происходит переход

5 из аварийного режима работы преобразователя в рабочий режим.

При этом ключ 31 открывается по вх. 3 БК 9, ключ 32 запирается по вх: 4 БК 9. Выход 1 СПП 8 подсоединяется к вх. 1 БК 9, вх. 2 ФИП 7, выход 2 СПП 9 отключается.

Поэтому каждый полупериод коммутации схемы переключения порога 8 на вых. 2 СПП 8 формирует соответственно уровни Uni, Uni.

Появление О на вх. 4 БК 4 блокирует выходы 3 и 4, на которых устанавливается уровень О. Дополнительные транзисторы 19 и 20 схемы СКП 6 запираются. На выходе СПП 8 устанавливается уровень Uni. Появление 1 на вх. 3 БК 4 деблокирует БК4 по вых. 1 и 2. Поэтому импульсы с вых. 1 и 2 БУ 3 поступают на основные вх. 1 и 2 инвертора 1. На выходе ДТ 5 в интервалах tio-tii; tnti2 формируются напряжения идт и идт, уровни которых в интервале времени (tn) оказываются меньше соответствующих порогов Uni, Uni. В моменты tn, 112 формируются импульсы на выходе компаратора ФИП 7 (фиг. 2ж), поступающие на D-вход триггера 33. По аналогии с ранее рассмотренным случаем (t2 tn), преобразователь остается в рабочем режиме. В дальнейшем при каждом срабатывании защиты, работа преобразователя происходит аналогичным образом.

Таким образом, предлагаемое устройство позволяет обеспечить надежность функционирования преобразователя при возникновении перегрузок и коротких замыканий в любом полупериоде коммутации инвертора независимо от их длительности. Имеется возможность регулировки уровня предельно допустимого тока перегрузки, при превышении которого срабатывает защита преобразователя, возвращая его в рабочий режим после уменьшения перегрузки. При этом используется лишь один элемент сравнения тока с пороговым уровнем - формирователь импульса перегрузки, что упрощает систему управления, и, следовательно, повышает надежность всего устройства.

Формула изобретения

Преобразователь напряжения с защитой от перегрузок, содержащий двухтактный транзисторный инвертор с трансформаторным выходом и систему управления, включающую в себя блок коммутации с четырьмя входами и тремя выходами, блок управления, соединенный входом с выходом задающего генератора, а двумя выходами - с первым и вторым входами

блока коммутации, схему коммутации тока перегрузки, подключенную двумя выходными выводами параллельно первому транзистору инвертора, а управляющим входом к третьему выходу блока коммутации, соединенного первым и вторым выходами с управляющими входами транзисторов инвертора, датчик тока, включенный в эмиттерные цепи транзисторов инвертора, схему переключения порога срабатывания,

формирователь импульса перегрузки, соединенный первым входом с датчиком тока, формирователь логического сигнала режима работы, соединенный входом с выходом формирователя импульса перегрузки, а прямым и инверсным выходами - с четвертым и третьим входами блока коммутации, отличающийся тем, что, с целью повышения надежности устройства путем упрощения его системы управления, введен второй

блок коммутации с четырьмя входами и одним выходом, первый блок коммутации снабжен четвертым выходом, схема коммутации тока перегрузки снабжена вторым входом и двумя дополнительными выходными выводами, а схема переключения порога срабатывания снабжена вторым выходом, причем второй блок коммутации подключен выходом к второму входу формирователя импульса перегрузки, первым и вторым входами - к первому и второму выходам схемы переключения порога срабатывания, соединенной входом с первым выходом схемы управления, третьим и четвертым входами с инверсным и прямым выходами формирователя логического сигнала режима работы, подключенного вторым входом к выходу задающего генератора, четвертый выход первого блока коммутации соединенс вторым входом схемы коммутации тока перегрузки,

подсоединенной двумя дополнительными выходными выводами параллельно второму транзистору инвертора.

CVJ

-i

ч

.

Svi

,J

Isi

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь напряжения с защитой от перегрузки | 1990 |

|

SU1713047A2 |

| Преобразователь напряжения с защитой от перегрузок | 1988 |

|

SU1585884A1 |

| Транзисторный конвертор | 1977 |

|

SU731524A1 |

| Стабилизированный транзисторный конвертор | 1977 |

|

SU736289A1 |

| Устройство для передачи телеграфного сигнала | 1980 |

|

SU1202067A1 |

| Самовозбуждающийся преобразователь постоянного напряжения | 1987 |

|

SU1457130A1 |

| Преобразователь постоянного напряжения | 1989 |

|

SU1705982A1 |

| ИМПУЛЬСНЫЙ СТАБИЛИЗАТОР НАПРЯЖЕНИЯ | 1992 |

|

RU2007825C1 |

| ДИСКРЕТНО-АНАЛОГОВЫЙ СИНУС-ГЕНЕРАТОР | 1995 |

|

RU2108657C1 |

| СПОСОБ ЗАЩИТЫ ОТ СБОЕВ И ОТКАЗОВ ЭЛЕКТРОННОГО БЛОКА КОСМИЧЕСКОГО АППАРАТА, ВЫЗЫВАЕМЫХ ВНЕШНИМИ ВОЗДЕЙСТВУЮЩИМИ ФАКТОРАМИ, И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2018 |

|

RU2693296C1 |

Изобретение относится к преобразовательной технике и может быть использовано в маломощных системах электропитания различных электронных устройств. Цель изобретения - повышение надежности устройства путем упрощения его системы управления. Указанная цель достигается использованием лишь одного элемента сравнения тока с пороговым уровнем - формирователем импульса перегрузки, в сочетании с введенным вторым блоком коммутации, переключающим уровень порога срабатывания схемы переключения порога срабатывания по сигналам от формирователя логического сигнала. 3 ил.•ч^'^. Изобретение относится к преобразовательной технике и можетбыть использовано в маломощных системах электропитания различных электронных устройств.Цель изобретения - повышение надежности устройства путем упрощения его системы управления.На фиг. 1 приведена структурная схема предлагаемого устройства; на фиг. 2 - временные диаграммы,, поясняющие работу преобра;зователя; на фиг. 3 -схема реализации блока коммутации.Устройство содержит транзисторный инвертор 1 с трансформаторным выходом, а также систему управления, включающую в себя задающий генератор 2, блок 3 управления, первый блок 4 коммутации, датчик 5 тока, схему 6 коммутации тока перегрузки, формирователь 7 импульса перегрузки, схему 8 переключения порога с^рабатывания, второй блок 9 коммутации, формирователь10 логического сигнала режима работы. Выход задающего генератора 2 соединен с вторым входом формирователя 10 логического сигнала режима работы и входом блока 3 управления, подключенного вых. 1 и 2 к вх.1и 2 первого блока 4 коммутации. Вых. 1 и2блока 4 соединены с вх. 1 и 2 инвертора 1, соединенного вых. 1 с датчиком 5 тока. Нагрузка инвертора подключается к трансформаторному выходу инвертора 4 (не показано). Вых. 3 и 4 первого блока 4 коммутации подключены к управляющим вх. 1 и 2 схемы 6 коммутации тока перегрузки, присоединенной вых. 1 и 2 к вх. 3 и 4 инвертора 4, а вых. 3 и 4 - к его вх. 5 и 6. Вых. 1 инвертора 4 соединен с вх. 1 формирователя 7 импульса перегрузки, подключенного вх. 2 через второй блок 9 коммутации соответствующие вых. 1 и 2 схемы переключения порога 8 срабатывания к вых. .1 блока 3 управления и выходом к вх. 1 формировате-СОо ел

CV4

,

CO

t3

CO

«

Л л 5х.4 5x.J

Фиг.З

| Стабилизированный преобразователь постоянного напряжения | 1976 |

|

SU568124A2 |

| кл | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1992-02-15—Публикация

1989-06-26—Подача