10

15

Изобретение относится к вычислительной технике и может быть использовано для сопряжения мини- и микро- ЭВМ в многомашинный комплекс.

Цель изобретения - повьпиение производительности устройства.

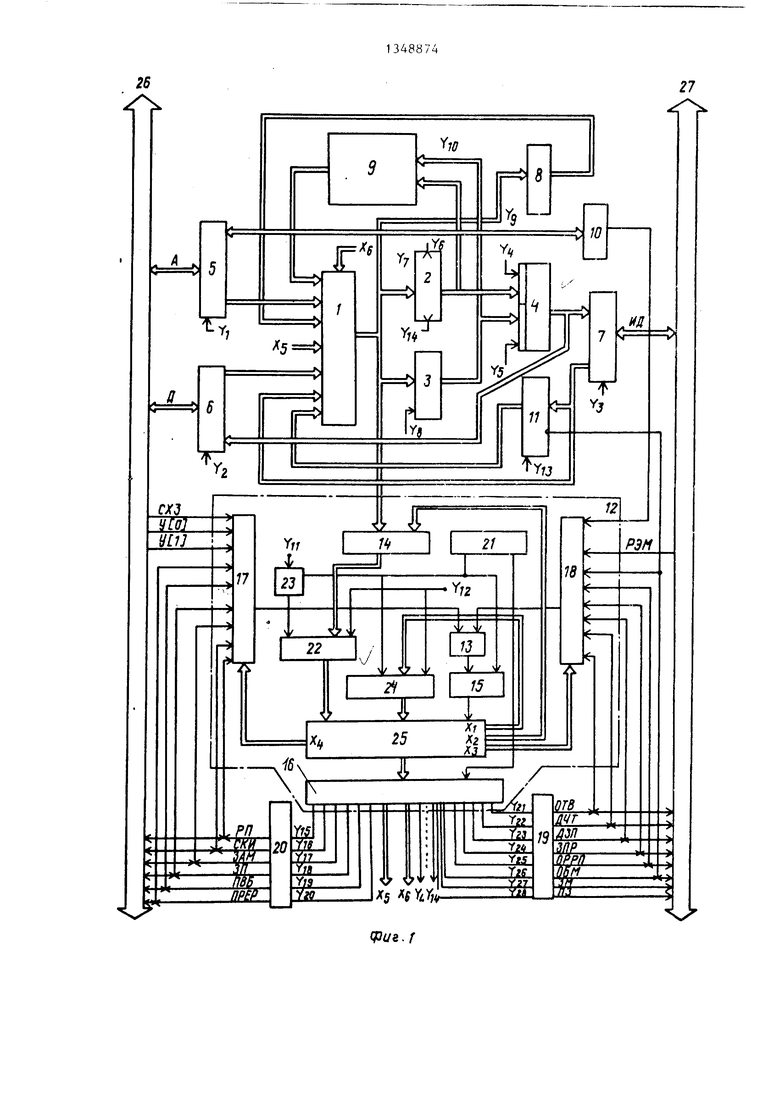

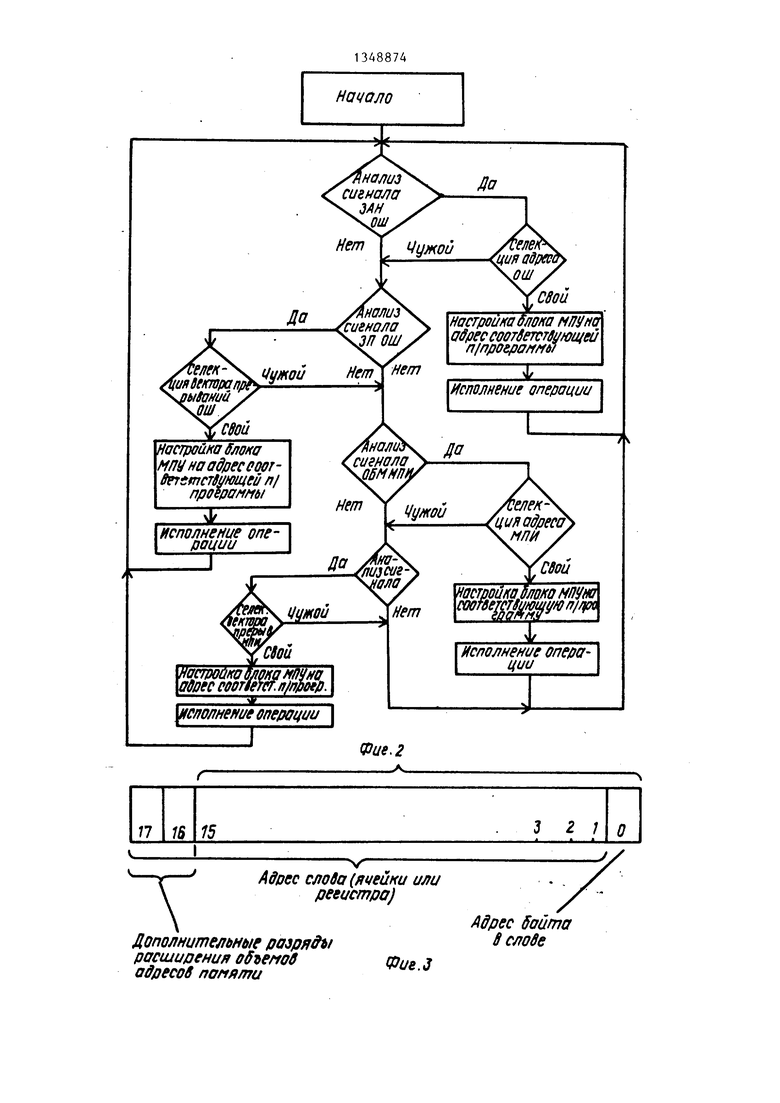

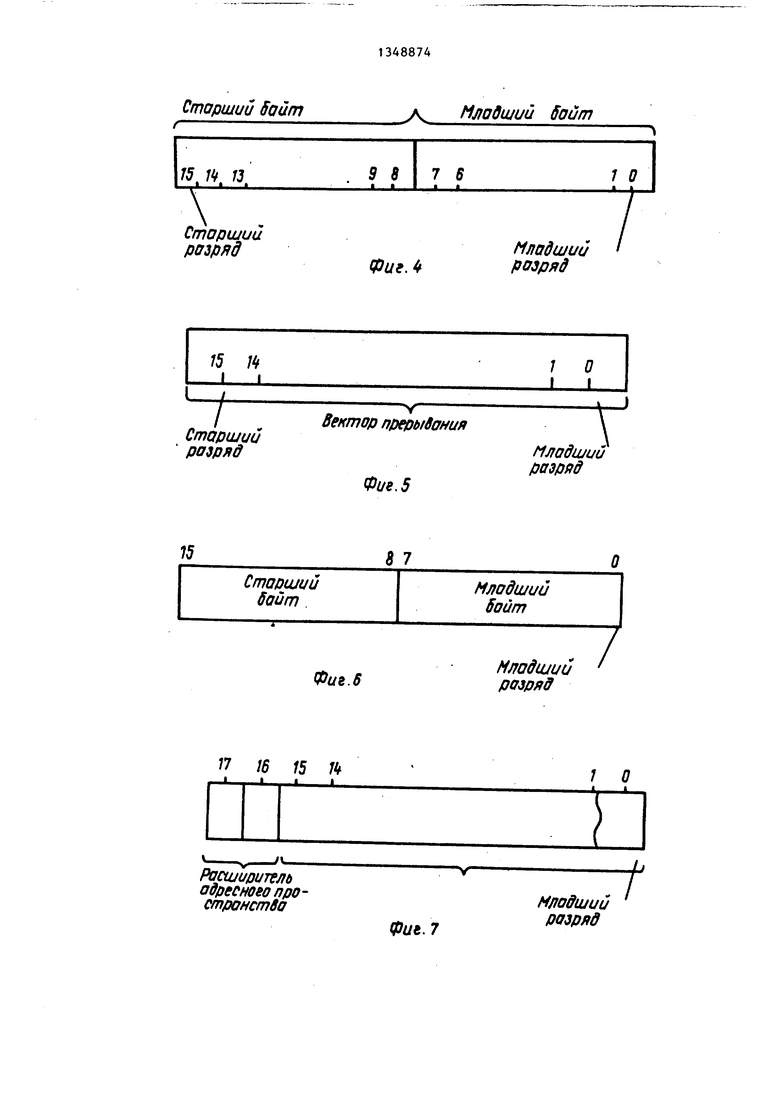

На фиг, 1 представлена блок-схема устройства, на фиг. 2 - обобщенный у

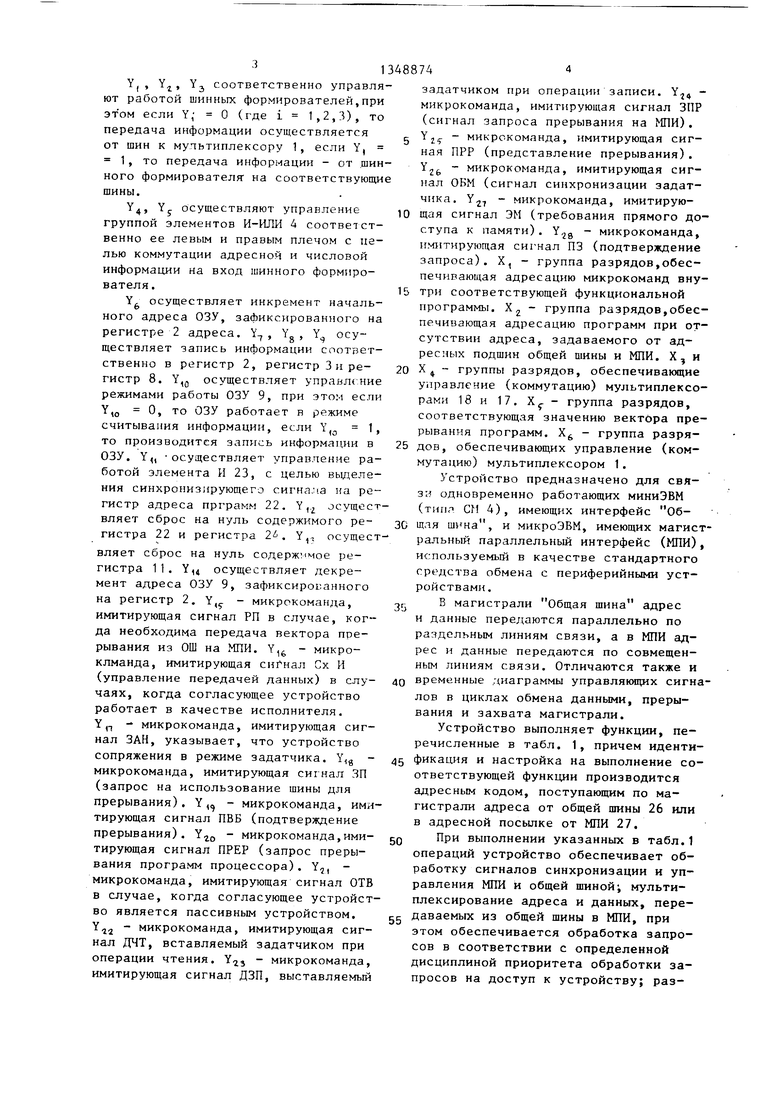

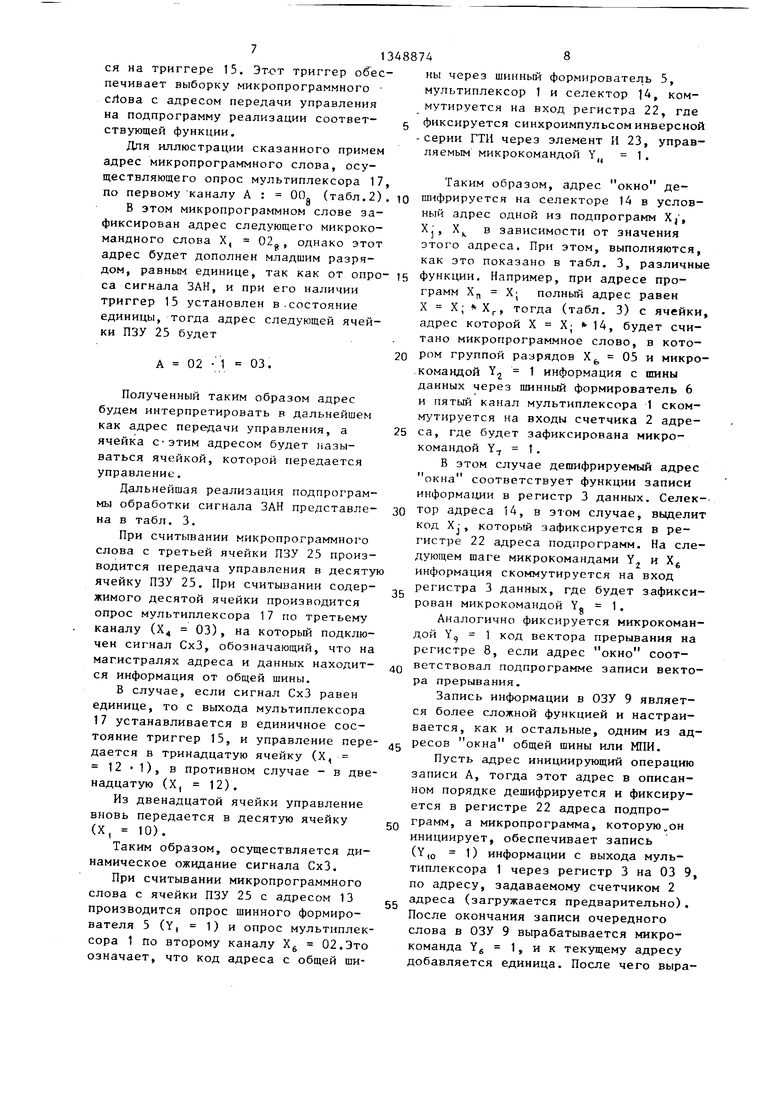

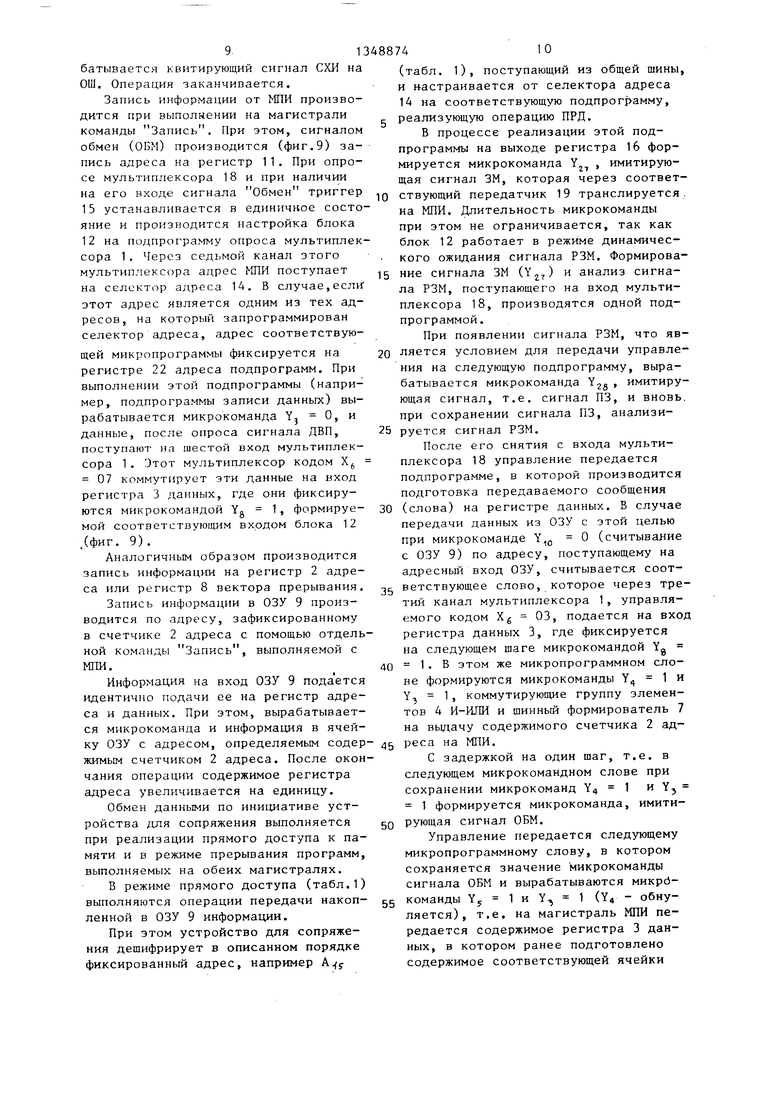

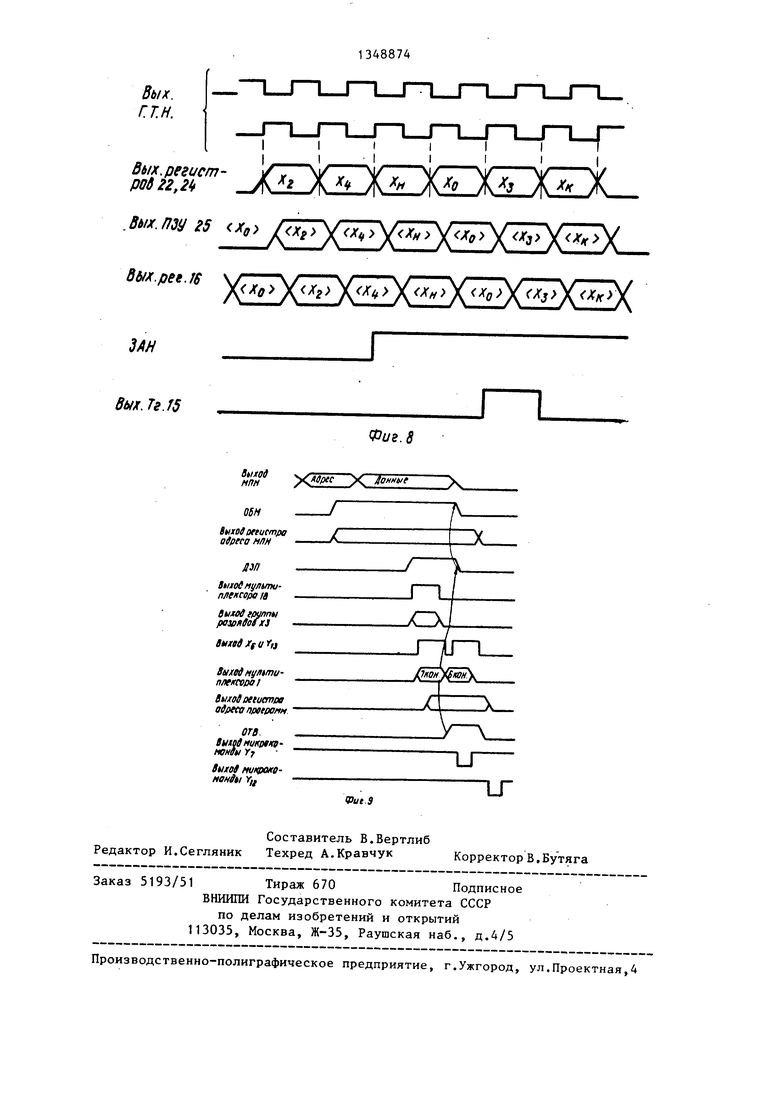

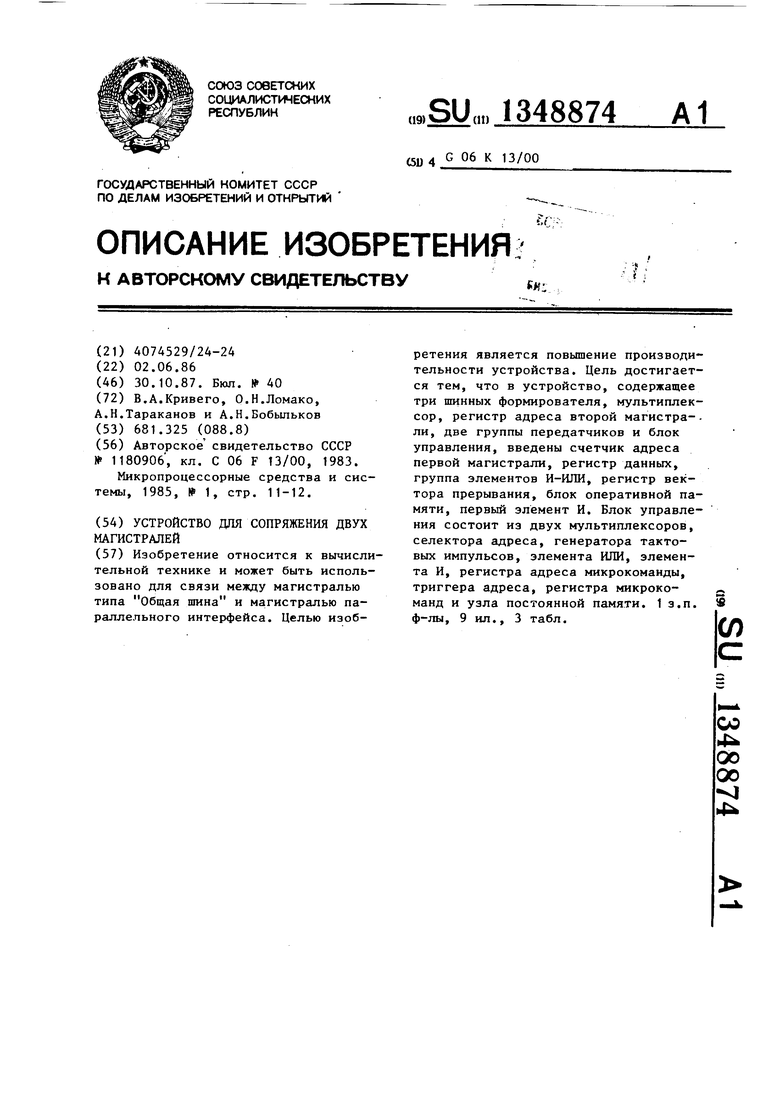

алгоритм работы устройства;на фиг.З и 4 - формат представления адреса и данных на шинах адреса и данных первой магистрали (ОШ); на фиг. 5 - формат представления вектора прерывания программы ОШ; на фиг. 6 - формат представления данных на второй магистрали (М11И) ; на фиг. 7 - формат представления адреса на МПИ;нафиг.8- пример реализации временной диаграммы блока управления; на фиг. 9 - вре- 0 менная диаграмма обмена с МПИ.

Устройство содержит (фиг. 1) мультиплексор 1, счетчик адреса 2 первой магистрали, регистр данных 3, группу элементов И-ИПИ 4, шинные формирователи 5-7, регистр 8 вектора прерывания, блок оперативной памяти (ОЗУ) 9, элемент И 10, регистр 11 адреса второй магистрали блока 12 управления, элемент ИЛИ 13, селектор 14 адреса, триггер 15 адреса, регистр 16 микро- ,команд, второй и первый мультиплексоры 17 и 18, группы передатчиков 19 и 20, генератор 21 тактовых импульсов, генератор 22 адреса программ, элемент И 23, регистр 24 адреса микрокоманд, узел постоянной памяти (ПЗУ) 25.

Устройство также содержит первуюма- гистраль, например, общую шинуОШ 26и

25 30

35

вторую магистраль - шину магистрального 40 согласование магистральных и синхро- параллельй го интерфейса МПИ 27. низирующих сигналов ОШ и МПИ. Регистр

Устройство обеспечивает сопряжение двух одновременно работающих микро и миниЭВМ.

Функциональные элементы устройства 45 4) на время ее использования. Эле- имеют следующие функциональные знача- мент И 23 обеспечивает стробирование

20 адреса программ обеспечивает запоминание адреса подпрограммы, определяемого фиксированным адресом (операния.

Мультиплексор 1 обеспечивает коммутацию адресной и числовой информации на входы счетчика адреса 2, регистров данных 3, вектора прерываний 8 и селектора 14 адреса. Счетчик адреса 2 обеспечивает буферное хранение адресов ОШ и МПИ, а также производит реверсивное суммирование инкремента к содержимому адреса для данных адресации ОЗУ 9. Регистр данных 3 обеспечивает буферное хранение данных с целью записи их в ОЗУ, на магистрали 27

5

0

и 26 МПИ или на ОШ. Шинные формирователи 5-7 обеспечивают соответственно разделение и мультиплексирование адресов и данных при передаче на ОШ или МПИ, а также при приеме адресов и данных от зтих шин. Регистр 8 некто- ра прерывания обеспечивает буферное хранение кода вектора прерывания с целью передачи его на ОШ или МПИ по соответствующей команде. Блок оперативной памяти (ОЗУ) 9 обеспечивает буферное хранение данных для передачи их массивом на МПИ или ОШ в режиме прямого доступа. Элемент И 10 обеспечивает выделение нулевого адреса в области адресных кодов ОЗУ. Регистр 11 адреса обеспечивает оперативную регистрацию адреса с шины МПИ с целью запоминания его во время действия сигнала Обмен. Блок 12 управления обеспечивает синхронизацию работы устройства с ОШ и МПИ, а также вырабатывает управляюш;ие сигналы (микро- 5 команды) с целью реализации заданного алгоритма (операции). Селектор 14 адреса осуществляет дешифрацию фиксированного адреса (кода операции) в код адреса соответствующей программы. 0 Триггер 15 адреса обеспечивает модификацию текущего адреса программы. Регистр 16 микрокоманд обеспечивает буферное хранение микрокоманд на время их отработки в устройстве. Мультиплексоры 17 и 18 обеспечивают коммутацию управляющих и синхронизирующих сигналов в соответствии с программой пользователя устройства. Передачтчики 19 и 20 обеспечивают параметрическое

5

согласование магистральных и синхро- низирующих сигналов ОШ и МПИ. Регистр

20 адреса программ обеспечивает запоминание адреса подпрограммы, определяемого фиксированным адресом (опера0

записи информации в регистр 22. Регистр 24 адреса микрокоманд обеспечивает буферное хранение адреса микрокомандного слова на время его исполнения в течение одного шага (периода частоты). Постоянное запоминающее устройство (ПЗУ) 25 обеспечивает хранение микрокомандных слов и программ, реализующих алгоритмы устройства для сопряжения вычислительных машин.

Назначение микрокоманд, формируемых блоком микропрограммного управления, следующее.

Y( , Y, УЗ соответственно управляют работой шинных формирователей,при эт ом если У; 0 (где i 1,2,3), то передача информации осуществляется от шин к мультиплексору 1, если У, 1, то передача информации - от шинного формирователяг на соответствующие шины,

У, Уу осуществляют управление группой элементов И-ИЛИ 4 соответственно ее левым и правым плечом с пе- лью коммутации адресной и числовой информации на вход шинного формирователя .

У, осуществляет инкремент начальt

ного адреса ОЗУ, зафиксированного на регистре 2 адреса. Y-, , Yg , Y осуществляет запись информации соответственно в регистр 2, регистр 3 и регистр 8. Y,(j осуществляет управление режимами работы ОЗУ 9, при этом если Y,o О, то ОЗУ работает в режиме считывания информации, если Y,,., 1, то производится запись информации в ОЗУ. Y, осуществляет управление работой элемента И 23, с целью вьщеле- ния синхронизирующего сигна.иа на резадатчиком при операции записи. У - микрокоманда, имитирующая сигнал ЗПР (сигнал запроса прерывания на МПИ). с У - микрокоманда, имитирующая сиг- ная ПРР (представление прерывания). У2 - микрокоманда, имитирующая сигнал ОБМ (сигнал синхронизации задат- чика. Yj - микрокоманда, имитирую10 щая сигнал ЭМ (требования прямого доступа к памяти), - микрокоманда, имитирующая сигнал ПЗ (подтверждение запроса). X, - группа разрядов,обеспечивающая адресацию микрокоманд вну15 три соответствующей функциональной программы. Х группа разрядов,обеспечивающая адресацию программ при отсутствии адреса, задаваемого от адресных подшин общей шины и МПИ. X, и

20 Х - группы разрядов, обеспечивающие управление (коммутацию) мультиплексорами 18 и 17, Х - группа разрядов, соответствующая значению вектора прерывания программ. Х - группа разря25 дов, обеспечивающих управление (коммутацию) мультиплексором 1.

Устройство предназначено для связи одновременно работающих миниЭВМ гистр адреса прграмм 22. У ,, осущсст- (типл СМ 4), имеющих интерфейс 06- вляет сброс на нуль содержимого ре- зс щля шина, и микроЭВМ, имеющих магист- гистра 22 и регистра 2. У,- осущест- ральный параллельньй интерфейс (МПИ), вляет сброс на нуль содержммое реиспользуемьш в качестве стандартного средства обмена с периферийными устройствами.

гистра 11. УН осуществляет декремент адреса ОЗУ 9, зафиксированного на регистр 2. У, - микрокоманда, имитирующая сигнал РП в случае, когда необходима передача вектора прерывания из ОШ на МПИ. У, - микро- клманда, имитирующая сигнал Сх И (управление передачей данных) в случаях, когда согласующее устройство работает в качестве исполнителя. У, - микрокоманда, имитирующая сигнал ЗАН, указывает, что устройство сопряжения в режиме задатчика. y,g - микрокоманда, имитирующая сигнал ЗП (запрос на использование шины для прерывания). У - микрокоманда, имитирующая сигнал ПВБ (подтверждение прерывания). - микрокоманда,имитирующая сигнал ПРЕР (запрос прерывания программ процессора). У-;, - микрокоманда, имитирующая сигнал ОТВ в случае, когда согласующее устройство является пассивным устройством. - микрокоманда, имитирующая сигнал ДЧТ, вставляемый задатчиком при операции чтения. У, микрокоманда, имитирующая сигнал ДЗП, выставляемый

задатчиком при операции записи. У - микрокоманда, имитирующая сигнал ЗПР (сигнал запроса прерывания на МПИ). У - микрокоманда, имитирующая сиг- ная ПРР (представление прерывания). У2 - микрокоманда, имитирующая сигнал ОБМ (сигнал синхронизации задат- чика. Yj - микрокоманда, имитирующая сигнал ЭМ (требования прямого доступа к памяти), - микрокоманда, имитирующая сигнал ПЗ (подтверждение запроса). X, - группа разрядов,обеспечивающая адресацию микрокоманд внутри соответствующей функциональной программы. Х группа разрядов,обеспечивающая адресацию программ при отсутствии адреса, задаваемого от адресных подшин общей шины и МПИ. X, и

Х - группы разрядов, обеспечивающие управление (коммутацию) мультиплексорами 18 и 17, Х - группа разрядов, соответствующая значению вектора прерывания программ. Х - группа разрядов, обеспечивающих управление (коммутацию) мультиплексором 1.

Устройство предназначено для связи одновременно работающих миниЭВМ (типл СМ 4), имеющих интерфейс 06- с щля шина, и микроЭВМ, имеющих магист- ральный параллельньй интерфейс (МПИ),

0

используемьш в качестве стандартного средства обмена с периферийными устройствами.

В магистрали Общая щина адрес и данные передаются параллельно по раздельным линиям связи, а в МПИ адрес и данные передаются по совмещенным линиям связи. Отличаются также и временные диаграммы управляющих сигналов в циклах обмена данными, прерывания и захвата магистрали.

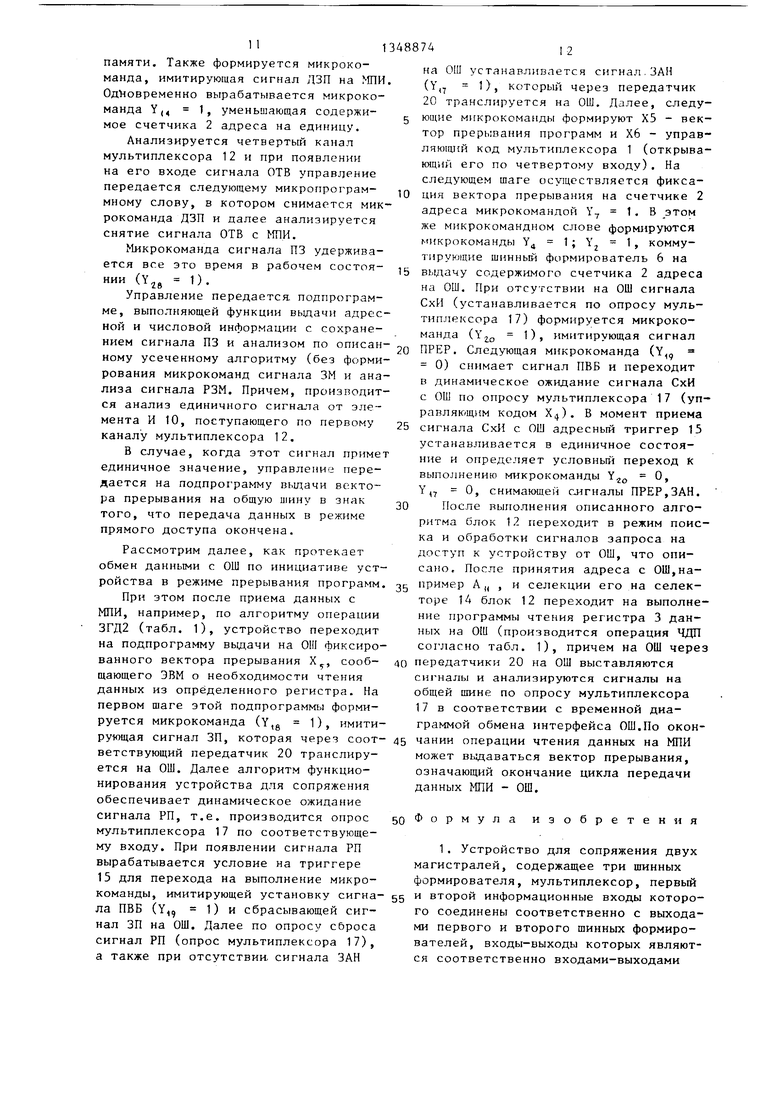

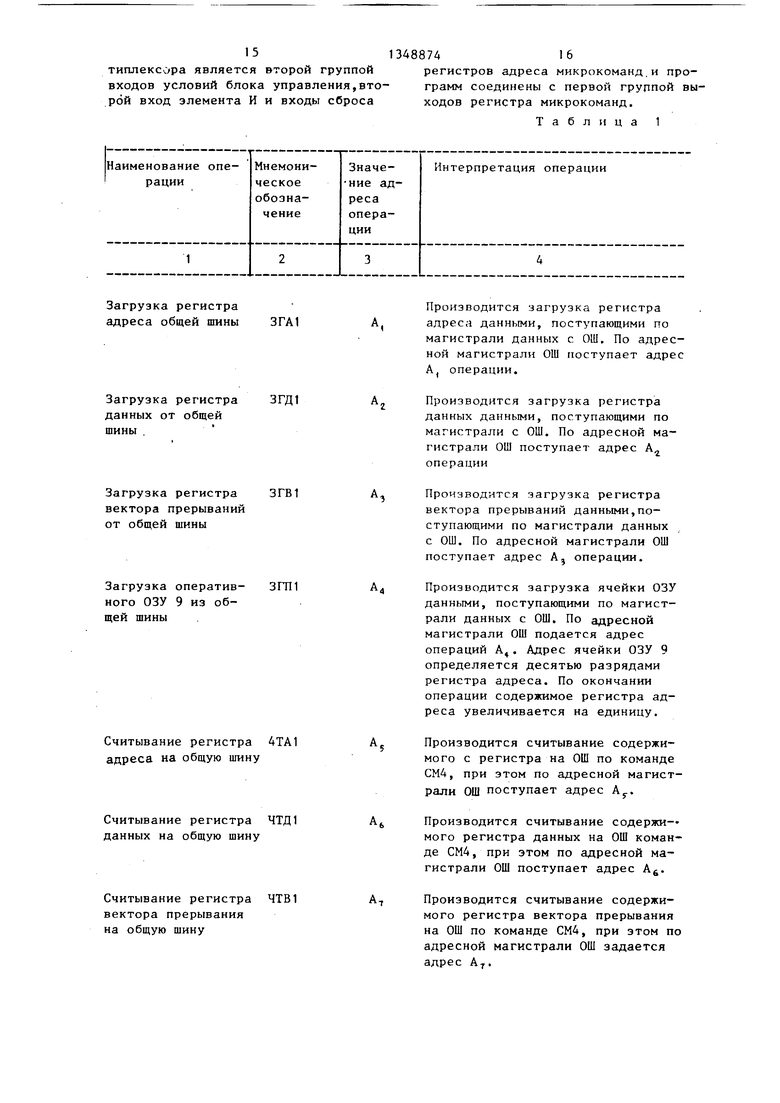

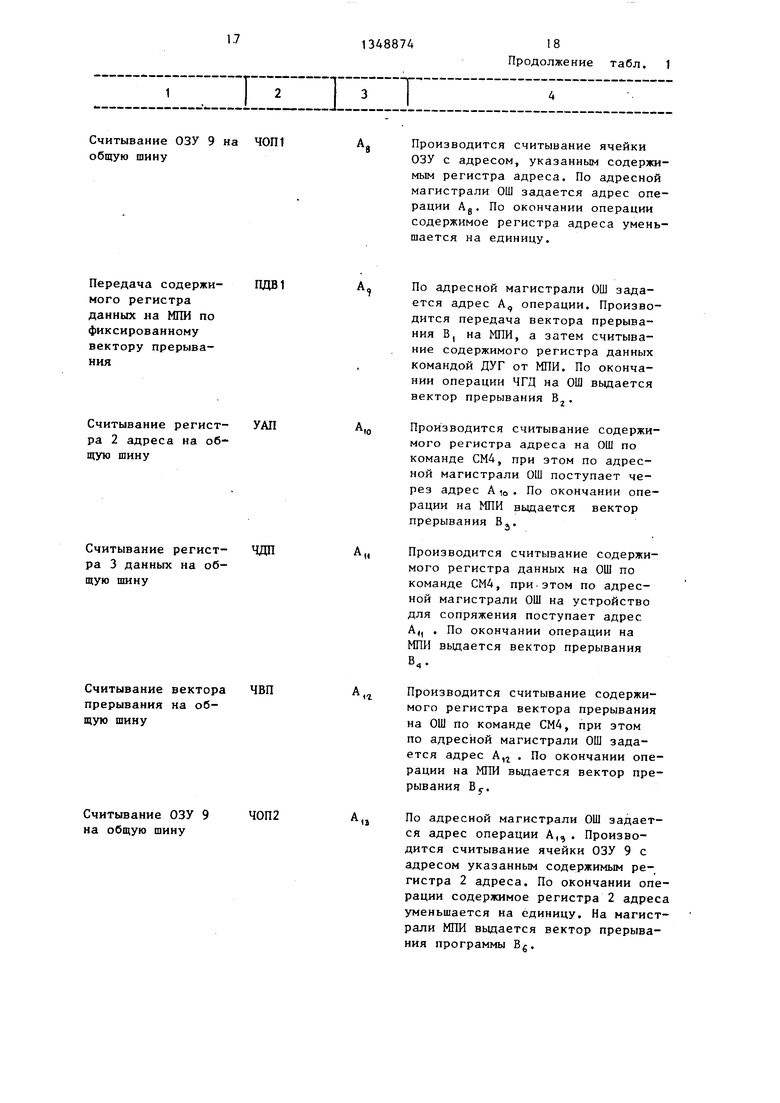

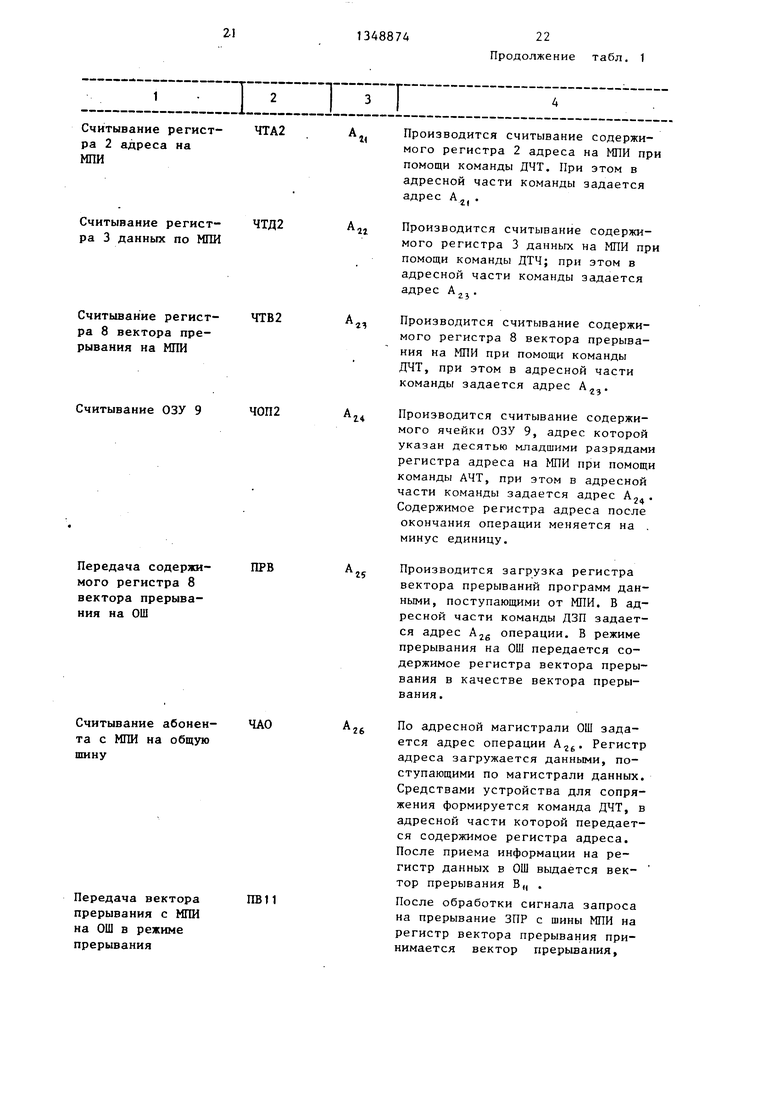

Устройство выполняет функции, перечисленные в табл. 1, причем иденти- 5 фикация и настройка на выполнение соответствующей функции производится адресным кодом, поступающим по магистрали адреса от общей шины 26 или в адресной посылке от МПИ 27.

При выполнении указанных в табл.1 операций устройство обеспечивает обработку сигналов синхронизации и управления МПИ и общей шиной; мультиплексирование адреса и данных, пере- g даваемых из общей шины в МПИ, при этом обеспечивается обработка запросов в соответствии с определенной дисциплиной приоритета обработки запросов на доступ к устройству; раз0

51

деление адреса и данных, передаваемых из М11И в общую шину; прием и обработку векторов прерываний из МПИ и из общей шины, а также формирование фиксированных векторов прерываний на общую шину или МНИ.

Преобразование сигналов синхронизации и управления и аналогичных сигналов МПИ производится блоком 12.

15

Пусть эти сигналы подсоединены на первый и второй входы мультиплексоров 17 и 18, причем на первые входы будут подключены сигналы непосредственно на считывание или запись, а на вторые - сигналы доступа на прерывание .

Последовательность опроса мультиплексоров 17 и 18 определяет дисциплину (порядок) обработки запросов.

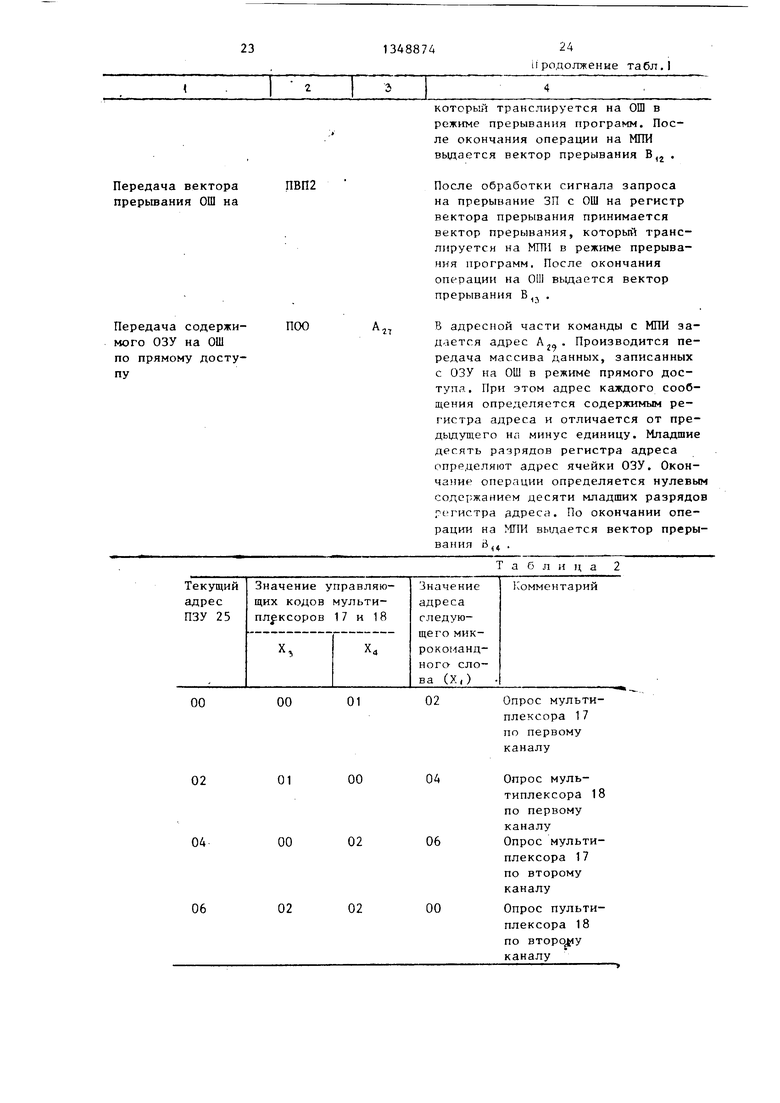

В табл. 2 приведен пример реализаПропесс преобразования сигналов состоит из обнар ткения (опроса этих сигналов, формирование сопутствующих сигналов на пнутре п1их магистралях устройства, т,е. сигналов, обеспечивающих пыпопиение соответствующих микроопорлций, например, регистрации (записи) адреса, данных, вектора прерываний и т.д., формирование ответных JQ ции подпрограммы поиска и обработки сигналов, а также формирование квити- запросов, рующих (ответных) сигналов на приемной (передающей) магистрали.

Как нпдно из табл. 1, команды устройства не носят характер специально выраженного формата, а представляются фиксированными адресами в формате, принятом ;1ля представления адресной информации в СМ4 (фиг.З) общей шины.

В табл. 2 представлен вариант программы поиска запросов, которые рас- 2S ставлены по приоритету следующим образом ЗАН, ЗП, ОБМ, ЗПР.

Как видно, в первых четырех ячейках ПЗУ 25 с четными адресами программируются коды Х, Х, обеспечи- Пер. дача данных на общую шину осу- о вающпе последовательный опрос мультищестилястся диумя операциями: ЧТС и ЗПС.

При ЧТС запрашивается шина для передачи ин|11ормации от исполнителя к задатчику, т.е. от устройства для сопряжения к СМ4 информация передается полным (16-разр.) словом.

Управление выполнением операциями ЧТС и ЗПС. производится согласно временной диаграмме обмена информацией ОШ.

Операция ЗПС используется для передачи информации от задатчика к ис полнителю, т.е. от СМ4 к устройству для сопряжения по адресу, указанному разрядами А 1 7 : 0J. Данные при этом помещаются исполнителем на под- щину Д П 5: 0 1|Э

При вьшол;1еиии некоторых операций устройство выдает на ОШ и МПИ вектора прерывания. При этом,управление обменом ведется стандартным для каждой из шин способом, а вектор прерывания программ размещается в l500

35

40

45

50

плексоров 17 и 18 по соответствующим каналам. Однако, могут быть и другие дисциплины обработки запросов в случае изменения подпрограммы.

Формирование динамических кодов (Х, Х) опроса магистралей (табл.2) производится с ПЗУ 25 из начального состояния регистра 22 адреса программ и регистра 11 адреса микрокоманд, а также триггера 15.

Начальным состоянием блока 12 считается такое состояние, при котором на адресных входах блока ПЗУ 25 - нули. Обнуление блока 12 производится по включению или восстановлению после провала сети электропитания, от блока начальной установки (не показан) ,

Программный порядок установки исходного состояния блока 12 следующий.

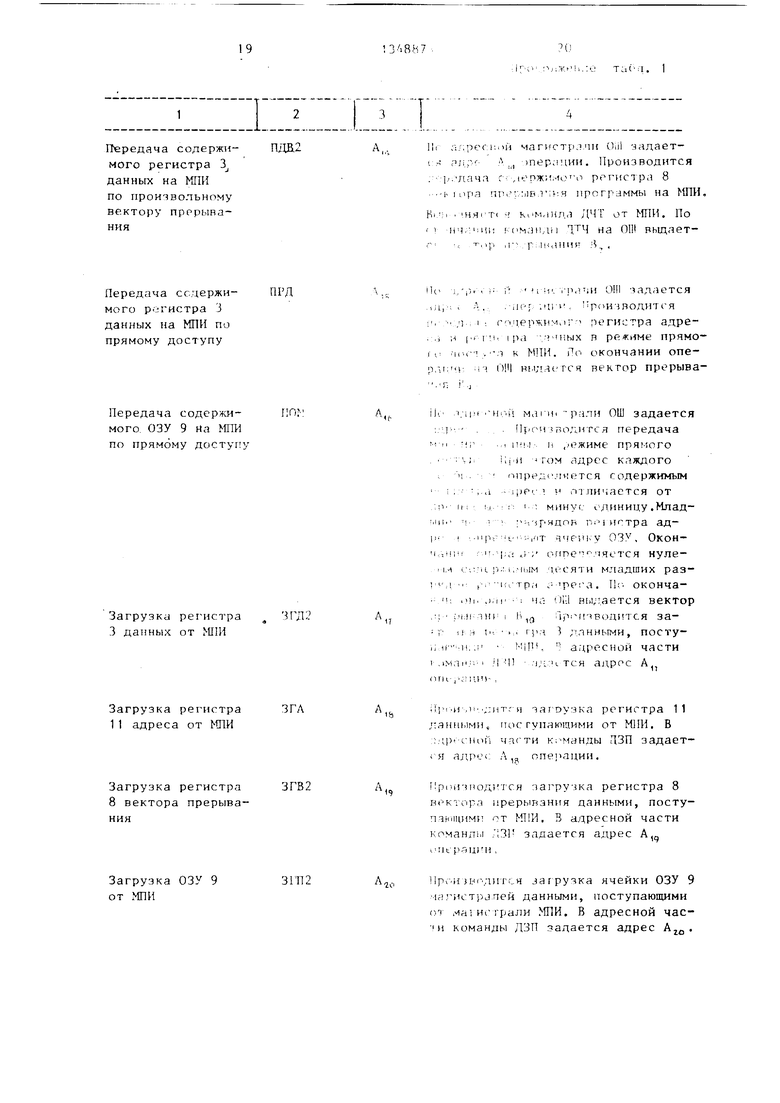

Динамика (темп) работы блока 12 определяется генератором 21 тактовых импульсов (ГТИ) (фиг.8).

Как видно из временной диаграммы

разрядах подшины данных при передаче 55 (Фш -З), при наличии соответствующих

сигналов на входе мультиплексоров 17 и 18, например сигнала ЗАН от ОШ, на выходе мультиплексора 17 снимается единичный сигнал, который фиксируетего на ОШ и разрядах - при передаче его на МПИ.

Форматы представления адресов данных и векторов прерывания программ

по шинам ОШ, МПИ И представление информации на шине МПИ приведены соответственно на фиг.3-7.

Рассмотрим работу блока 12 в режиме поиска и обработки сигналов запроса на доступ к устройству для содержания от общей шины и МПИ.

Пусть эти сигналы подсоединены на первый и второй входы мультиплексоров 17 и 18, причем на первые входы будут подключены сигналы непосредственно на считывание или запись, а на вторые - сигналы доступа на прерывание .

Последовательность опроса мультиплексоров 17 и 18 определяет дисциплину (порядок) обработки запросов.

В табл. 2 приведен пример реализации подпрограммы поиска и обработки запросов,

ции подпрограммы поиска и обработки запросов,

В табл. 2 представлен вариант программы поиска запросов, которые рас- ставлены по приоритету следующим образом ЗАН, ЗП, ОБМ, ЗПР.

Как видно, в первых четырех ячейках ПЗУ 25 с четными адресами про5

0

5

0

плексоров 17 и 18 по соответствующим каналам. Однако, могут быть и другие дисциплины обработки запросов в случае изменения подпрограммы.

Формирование динамических кодов (Х, Х) опроса магистралей (табл.2) производится с ПЗУ 25 из начального состояния регистра 22 адреса программ и регистра 11 адреса микрокоманд, а также триггера 15.

Начальным состоянием блока 12 считается такое состояние, при котором на адресных входах блока ПЗУ 25 - нули. Обнуление блока 12 производится по включению или восстановлению после провала сети электропитания, от блока начальной установки (не показан) ,

Программный порядок установки исходного состояния блока 12 следующий.

Динамика (темп) работы блока 12 определяется генератором 21 тактовых импульсов (ГТИ) (фиг.8).

Как видно из временной диаграммы

713488748

ся на триггере 15. Этот триггер ны через шинный формирователь 5, печивает выборку микропрограммного мультиплексор 1 и селектор 14, ком- сЛова с адресом передачи управления на подпрограмму реализации соответствующей функции.

Для иллюстрации сказанного примем

мутируется на вход регистра 22, гле g фиксируется синхроимпульсам инверсной -серии ГТИ через элемент И 23, управляемым микрокомандой Y

адрес микропрограммного слова, осуществляющего опрос мультиплексора 17,

Таким образом, адрес окно депо первому каналу А : 00 (табл.2), ю шифрируется на селекторе 14 в услов 8

В этом микропрограь1мном слове зафиксирован адрес следующего микроконый адрес одной из подпрограмм , X;, Х| в зависимости от значения этого адреса. При этом, выполняются, как это показано в табл. 3, различные

02

и

однако этот

мандного слова X,

адрес будет дополнен младшим разрядом, равным единице, так как от опро- t6 Функции. Например, при адресе проный адрес одной из подпрограмм , X;, Х| в зависимости от значения этого адреса. При этом, выполняются как это показано в табл. 3, различн

са сигнала ЗАН, и при его наличии триггер 15 установлен в .состояние единицы, тогда адрес следующей ячейки ПЗУ 25 будет

А 02 - 1 03.

Полученный таким образом адрес будем интерпретировать в дальнейшем как адрес передачи управления, а ячейка с-этим адресом будет называться ячейкой, которой передается управление.

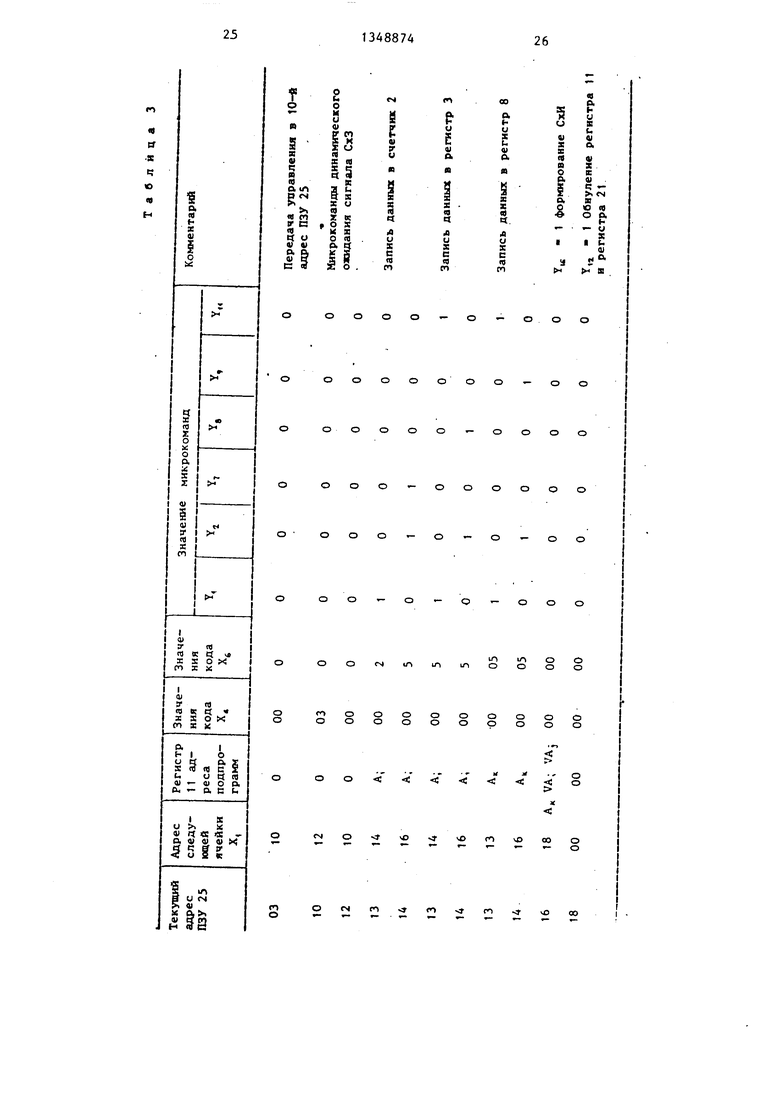

Дальнейшая реализация подпрограммы обработки сигнала ЗАН представлена в табл. 3.

При считывании микропрограммного слова с третьей ячейки ПЗУ 25 производится передача управления в десяту ячейку ПЗУ 25. При считывании содержимого десятой ячейки производится опрос мультиплексора 17 по третьему каналу (Х 03), на который подключен сигнал СхЗ, обозначающий, что на магистралях адреса и данных находится информация от общей шины.

В случае, если сигнал СхЗ равен единице, то с выхода мультиплексора 17 устанавливается в единичное состояние триггер 15, и управление передается в тринадцатую ячейку (X, 12 -1), в противном случае - в двенадцатую (X, 12).

Из двенадцатой ячейки управление вновь передается в десятую ячейку (X, 10).

Таким образом, осуществляется динамическое ожидание сигнала СхЗ.

При считывании микропрограммного слова с ячейки ПЗУ 25 с адресом 13 производится опрос шинного формирователя 5 (Y, 1) и опрос мультиплексора 1 по второму каналу Х 02.Это означает, что код адреса с общей ши ны через шинный формирователь 5, мультиплексор 1 и селектор 14, ком-

мутируется на вход регистра 22, гле g фиксируется синхроимпульсам инверсной -серии ГТИ через элемент И 23, управляемым микрокомандой Y

Таким образом, адрес окно деФункции. Например, при адресе проный адрес одной из подпрограмм , X;, Х| в зависимости от значения этого адреса. При этом, выполняются, как это показано в табл. 3, различные

грамм Хр X; полный адрес равен X X; Х, тогда (табл. 3) с ячейки, адрес которой X Х; 14, будет считано микропрограммное слово, в котором группой разрядов Х 05 и микро- командой Yj 1 информация с шины данных через шинный формирователь 6 и пятый канал мультиплексора 1 ском- м тируется на входы счетчика 2 адреса, где будет зафиксирована микрокомандой Y-J 1.

В этом случае дешифрируемый адрес окна соответствует функции записи информации в регистр 3 данных. Салак-- тор адреса 14, в этом случае, выделит

который зафиксируется в реНа сле22 адреса подпрограмм.

г

шаге микрокомандами Y и Xg

5

0

5

0

5

информация скоммутируется на вход регистра 3 данных, где будет зафиксирован микрокомандой Yg 1.

Аналогично фиксируется микрокомандой Yg 1 код вектора прерывания на регистре 8, если адрес окно соответствовал подпрограмме записи вектора прерывания.

Запись информации в ОЗУ 9 является более сложной функцией и настраивается, как и остальные, одним из адресов окна общей шины или МПИ.

Пусть адрес инициирующий операцию записи А, тогда этот адрес в описанном порядке дещифрируется и фиксируется в регистре 22 адреса подпрограмм, а микропрограмма, которую,он инициирует, обеспечивает запись (Y,o 1) информации с выхода мультиплексора 1 через регистр 3 на 03 9, по адресу, задаваемому счетчиком 2 адреса (загружается предварительно). После окончания записи очередного слова в ОЗУ 9 вьфабатывается микрокоманда YS 1, и к текущему адресу добавляется единица. После чего вырабатывается квитирующий сигнал СХИ на ОШ. Операция заканчивается.

Запись информации от МПИ производится при выполнении на магистрали команды Запись. При этом, сигналом обмен (ОБМ) производится (фиг,9) запись адреса на регистр 11. При опросе мультиплексора 18 и при наличии на его входе сигнала Обмен триггер 15 устанавливается в единичное состояние и производится пастройка блока 12 на подпрограмму опроса мультиплексора 1. Через седьмой канал этого мультиплексора адрес МЕИ поступает на селектор адреса 14. В случае, если этот адрес является одним из тех адресов, на который запрограммирован селектор адреса, адрес соответствующей микропрограммы фиксируется на регистре 22 адреса подпрограмм. При выполнении этой подпрограммы (например, подпрограммы записи данных) вырабатывается микрокоманда Y, 0, и данные, после опроса сигнала ДВП, поступают на шестой вход мультиплексора 1. Этот мультиплексор кодом Х 07 коммутирует эти данные на вход регистра 3 данных, где они фиксируются микрокомандой Yg 1, формируемой соответствующим входом блока 12 /фиг. 9).

Аналогичным образом производится запись информации на регистр 2 адреса или регистр 8 вектора прерывания.

Запись информации в ОЗУ 9 производится по адресу, зафиксированному в счетчике 2 адреса с помощью отдельной команды Запись, выполняемой с МПИ.

Информация на вход ОЗУ 9 пода ется идентично подачи ее на регистр адреса и данных. При зтом, вырабатывается микрокоманда и информация в ячейку ОЗУ с адресом, определяемым содержимым счетчиком 2 адреса. После окончания операции содержимое регистра адреса увеличивается на единицу.

Обмен данными по инициативе устройства для сопряжения выполняется при реализации прямого доступа к памяти и в режиме прерывания программ, выполняемых на обеих магистралях.

В режиме прямого доступа (табл,1) выполняются операции передачи накопленной в ОЗУ 9 информации.

При этом устройство для сопряжения дешифрирует в описанном порядке фиксированный адрес, например

(табл. 1), поступающий из общей шины, и настраивается от селектора адреса 14 на соответствующую подпрограмму, реализующую операцию ПРД.

В процессе реализации этой подпрограммы на выходе регистра 16 формируется микрокоманда Y , имитирующая сигнал ЗМ, которая через соответствующий передатчик 19 транслируется, на МПИ. Длительность микрокоманды при этом не ограничивается, так как блок 12 работает в режиме динамического ожидания сигнала РЗМ. Формирование сигнала ЗМ (Y.,) и анализ сигнала РЗМ, поступающего на вход мультиплексора 18, производятся одной подпрограммой.

При появлении сигнала РЗМ, что является условием для передачи управления на следующую подпрограмму, вырабатывается микрокоманда , имитирующая сигнал, т.е. сигнал ПЗ, и вновь, при сохранении сигнала ПЗ, анализируется сигнал РЗМ.

После его снятия с входа мультиплексора 18 управление передается подпрограмме, в которой производится подготовка передаваемого сообщения

(слова) на регистре данных. В случае передачи данных из ОЗУ с этой целью при микрокоманде Y, О (считывание с ОЗУ 9) по адресу, поступающему на адресньп вход ОЗУ, считывается соответствующее слово, которое через третий канал мультиплексора 1, управляемого кодом Xg 03, подается на вход регистра данных 3, где фиксируется на следующем шаге микрокомандой Yg

1. В этом же микропрограммном слове формируются микрокоманды Y, 1 и Y, 1, коммутирующие группу элементов 4 И-ИЛИ и шинный формирователь 7 на выдачу содержимого счетчика 2 адреса на МПИ.

С задержкой на один шаг, т.е. в следующем микрокомандном слове при сохранении микрокоманд Y, 1 и Y.J 1 формируется микрокоманда, имитиРУЮщая сигнал ОБМ.

Управление передается следующему микропрограммному слову, в котором сохраняется значение микрокоманды сигнала ОБМ и вырабатываются микрйкоманды Y 1 и Y, 1 (Y4 - обнуляется) , т.е. на магистраль МПИ передается содержимое регистра 3 данных, в котором ранее подготовлено содержимое соответствующей ячейки

памяти. Также формируется микрокоманда, имитирующая сигнал ДЗП на МПИ ОдУювременно вырабатывается микрокоманда Y(4 - 1 уменьшающая содержимое счетчика 2 адреса на единицу.

Анализируется четвертый канал мультиплексора 12 и при появлении на его входе сигнала ОТВ управление передается следующему микропрограммному слову, в котором снимается микрокоманда ДЗП и далее анализируется снятие сигнала ОТВ с МПИ.

Микрокоманда сигнала ПЗ удерживается все это время в рабочем состоянии ( 1).

Управление передается подпрограмме, выполняющей функции выдачи адресной и числовой информации с сохранением сигнала ПЗ и анализом по описанному усеченному алгоритму (без формирования микрокоманд сигнала ЗМ и анализа сигнала РЗМ. Причем, производится анализ единичного сигнала от элемента И 10, поступающего по первому каналу мультиплексора 12.

В случае, когда этот сигнал приме единичное значение, управление передается на подпрограмму выдачи вектора прерывания на общую шину в знак того, что передача данных в режиме прямого доступа окончена.

Рассмотрим далее, как протекает обмен данными с ОШ по инициативе устройства в режиме прерывания программ

При этом после приема данных с МПИ, например, по алгоритму операции ЗГД2 (табл. 1), устройство переходит на подпрограмму выдачи на OIII фиксированного вектора прерывания Х, сообщающего ЭВМ о необходимости чтения данных из определенного регистра. На первом шаге этой подпрограммы формируется микрокоманда (Y,g 1), имитирующая сигнал ЗП, которая через соответствующий передатчик 20 транслируется на ОШ. Далее алгоритм функционирования устройства для сопряжения обеспечивает динамическое ожидание сигнала РП, т.е. производится опрос мультиплексора 17 по соответствующему входу. При появлении сигнала РП вырабатывается условие на триггере 15 для перехода на выполнение микрокоманды, имитирующей установку сигнала ПВБ (Y,,j 1) и сбрасывающей сигнал ЗП на ОШ. Далее по опросу сброса сигнал РП (опрос мультиплексора 17), а также при отсутствии, сигнала ЗАН

на ОШ устанавливается сигнал,ЗАН (Y, 1), который через передатчик 20 транслируется на ОШ. Далее, следу- ющие микрокоманды формируют Х5 - вектор прерывания программ и Х6 - управляющий код мультиплексора 1 (открывающий его по четвертому входу). На следующем шаге осу1цествляется фиксадин вектора прерывания на счетчике 2 адреса микрокомандой Y 1. В ртом же микрокомандном слове формируются микрокоманды Y 1; Y 1, коммутирующие шинный формирователь 6 на

выдачу содержимого счетчика 2 адреса на ОШ. При отсутствии на ОШ сигнала СхИ (устанавливается по опросу мультиплексора 17) формируется микрокоманда ( 1), имитирующая сигнал

ПРЕР. Следующая микрокоманда (Y, 0) снимает сигнал ПВБ и переходит в динамическое ожидание сигнала СхИ с ОШ по опросу мультиплексора 17 (управляющим кодом Х). В момент приема

сигнала СхЛ с ОШ адресный триггер 15 устанавливается в единичное состояние и определяет условный переход К выполнению микрокоманды Y О, Y ,7 0 снимающей слгналы ПРЕР,ЗАН.

После выполнения описанного алгоритма блок 12 переходит в режим поиска и обработки сигналов запроса на доступ к устройству от ОШ, что описано. После принятия адреса с ОШ,например А„ , и селекции его на селекторе 14 блок 12 переходит на выполнение программы чтения регистра 3 данных на ОШ (производится операция ЧДП согласно табл. 1), причем на ОШ через

передатчики 20 на ОШ выставляются си1 налы и анализируются сигналы на общей шине по опросу мультиплексора 17 в соответствии с временной диаграммой обмена интерфейса ОШ.По окончании операции чтения данных на МПИ может выдаваться вектор прерывания, означающий окончание цикла передачи данных МПИ - ОШ.

Формула изобретения

1. Устройство для сопряжения двух магистралей, содержащее три шинных формирователя, мультиплексор, первый и второй информационные входы которого соединены соответственно с выходами первого и второго шинных формирователей, входы-выходы которых являются соответственно входами-выходами

ycTpoi icTHa для подключения соответственно шин алреса и данных первой магистрали, регистр адреса второй магистрали, информационный вход которого подключен к выходу третьего шинного формирователя, вход-выход которого является входом-выходом устройства для подключения адресно- информационной шины второй магистрали, две группы передатчиков, выходы которых являются соответствующими выходами устройства для подключения к управляющим шинам второй и первой магистра. гой, и Плок управления, первая группа ных(1лов которого соединена с упраг ляы1цими входами первого, второго н третьего шинных формирова- телс, мультиплексора и регистра адреса второй магистрали, а вторая и третья rpynnfji выходов соединены соответственно с выходами передатчиков второй и nepnoii групп, первая и вторая rpyniii) входов условий блока управления являются соответствующими входами ус;тройства для подключения к шинам .поиия первой и второй магистрале, отличающееся тем, 410, с целью повышения производительности устройства, в него введены блок оперативной памяти, регист вектора прер,1наиия, счетчик адреса первой маг истрали, регистр данных, группа элсме 1тои И-1ПИ и элемент И, причем В111ХОД мультипх ексора соединен с информационными входами регистра вектора 11)ерывания, счетчика адреса первой магистрали, регистра данных и адресным входом блока управления,первая группа выходов которого подключена к адресным входам блока оперативной памяти, порным входам элементов

H-tLlH груцпы, синхровходам регистров вектора прерывания, данных, входам суммирования, записи и вычитания счетчика адреса первой магистрали, третий - седьмой информационные входы мультиплексора соединены соответственно с выходами блока оперативной памяти, регистра вектора прерывания, четвертой группой выходов блока управления, выходом третьего шинного формирователя и выходом регистра адреса второй магистрали, группа разрядных выходов счетчика адреса первой gg реса, груггаа информационных входов

магистрали соединена с группой информационных входов первого шинного формирователя, группой входов элемента И, группой адресных входов блока oneпервого мультиплексора соединена с входом условия и первой группой вхо дов условий блока управления,группа информационных входов второго муль

5

0

ративнои памяти и вторыми входами элементов И-ИЛИ группы, выходы которых соединены с информационными входами второго и третьего шинных формирователей, а третьи входы - с выходом регистра данных и информационным входом блока оперативной памяти, выход элемента И соединен с входом условия блока управления, синхровход регистра адреса второй магистрали соединен с выходом синхронизации задатчика соответствующего цередатчика первой группы.

2, Устройство по П.1, отличающееся тем, что блок управления содержит узел постоянной памяти, селектор адреса, информационный вход которого является адресным входом блока управления, регистр адреса программ, регистр адреса микрокоманд, триггер адреса, регистр микрокоманд, первая - четвертая группы выходов которого являются соответственно 5 первой - четвертой группами выходов блока управления, генератор тактовых импульсов, элемент И, элемент ИЛИ и первый и второй мультиплексоры, причем первая - пятая группы выходов узла постоянной памяти подключены соответственно к информационному вx(Jдy 1)ег истра адреса микрокоманд, управляющему входу селектора адреса, управляющим входам первого и второго мультиплексоров и информационному входу рег истра микрокоманд, синхро- входом соединенного с первым выходом генератора тактовых импульсов, второй ыход которого подключен к первому входу элемента И и синхровходам регистра адреса микрокоманд и триггера адреса, выходы которого соединены с цервой группой адресных входов и входом адреса узла постоянной памяти, вторая группа адресных входов которого соединена с группой выходов регистра адреса программ, синхровходом и информационным входом подключенного к выходам элемента И и селектора адреса, выходы первого и второго мультиплексоров подключены соответственно к первому и второму входам элемента ИЛИ, выходом соединенного с информационным входом триггера йд0

5

0

5

0

первого мультиплексора соединена с входом условия и первой группой входов условий блока управления,группа информационных входов второго муль151348874

типлексора является второй группой входов условий блока управления,второй вход элемента И и входы сброса

рег гра ход

Загрузка регистра адреса общей шины

ЗГА1

Загрузка регистра данных от общей щины .

ЗГД1

Загрузка регистра вектора прерываний от общей шины

ЗГВ1

Загрузка оперативного ОЗУ 9 из общей шины

ЗГП1

Считывание регистра 4ТА1 адреса на общую шину

Считывание регистра ЧТД1 данных на общую шину

Считывание регистра ЧТВ1 вектора прерывания на общую шину

16

регистров адреса микрокоманд,и программ соединены с первой группой выходов регистра микрокоманд.

Таблица 1

,

Производится загрузка регистра адреса данными, поступающими по магистрали данных с ОШ, По адресной магистрали ОШ поступает адрес AJ операции.

Производится загрузка регистра данных данными, поступающими по магистрали с ОШ. По адресной магистрали ОШ поступает адрес А операции

Производится загрузка регистра вектора прерываний данными,поступающими по магистрали данных с ОШ. По адресной магистрали ОШ поступает адрес А, операции.

Производится загрузка ячейки ОЗУ данными, поступающими по магистрали данных с ОШ. По адресной магистрали ОШ подается адрес операций А. Адрес ячейки ОЗУ 9 определяется десятью разрядами регистра адреса. По окончании операции содержимое регистра адреса увеличивается на единицу.

Производится считывание содержимого с регистра на ОШ по команде СМ4, при этом по адресной магистрали ОШ поступает адрес А..

Производится считывание содержи-- мого регистра данных на ОШ команде СМ4, при этом по адресной магистрали ОШ поступает адрес А.

Производится считывание содержимого регистра вектора прерывания на ОШ по команде СМ4, при этом по адресной магистрали ОШ задается адрес А,.

1.7

iz::i:i;:i

Считывание ОЗУ 9 на ЧОП1 общую шину

Передача содержимого регистра данных на МПИ по фиксированному вектору прерывания

Считывание регистра 2 адреса на общую шину

УАП

Считывание регистра 3 данных на общую шину

ЧДП

Считывание вектора ЧВП прерывания на общую шину

Считывание ОЗУ 9 на общую шину

ЧОП2

18 Продолжение табл. 1

4

Производится считывание ячейки ОЗУ с адресом, указанньм содержимым регистра адреса. По адресной магистрали ОШ задается адрес операции Ag. По окончании операции содержимое регистра адреса уменьшается на единицу.

По адресной магистрали ОШ задается адрес А операции. Производится передача вектора прерывания В, на МПИ, а затем считывание содержимого регистра данных командой ДУГ от МПИ. По окончании операции ЧГД на ОШ вьщается вектор прерывания В .

Производится считывание содержимого регистра адреса на ОШ по команде СМ4, при этом по адресной магистрали ОШ поступает через адрес А 10 По окончании операции на МПИ выдается вектор прерывания В.

Производится считывание содержимого регистра данных на ОШ по команде СМ4, при-этом по адресной магистрали ОШ на устройство для сопряжения поступает адрес А(, . По окончании операции на МПИ выдается вектор прерывания В..

Производится считывание содержимого регистра вектора прерывания на ОШ по команде СМ4, при этом по адресной магистрали ОШ задается адрес А,г . По окончании операции на МПИ выдается вектор прерывания By.

По адресной магистрали ОШ задается адрес операции А,, . Производится считывание ячейки ОЗУ 9 с адресом указанным содержимым регистра 2 адреса. По окончании операции содержимое регистра 2 адреса уменьшается на единицу. На магистрали МПИ выдается вектор прерывания программы Bg.

Передача содержимого регистра 3 данных на МПИ по произвольному вектору прерывания

Передача ссдержи- мого регистра 3 данных на МПИ по прямому доступу

Передача содержимого. ОЗУ 9 На fflИ по прямому доступу

Загрузка регистра 3 данных от МПИ

Загрузка регистра ЗГЛ 1 1 адреса от ШИ

Загрузка регистра ЗГВ2 8 вектора прерывания

Загрузка ОЗУ 931112

от МПИ

III ;i;;per:i;(iH MarjfCTp.i.nii Oiil задает- гя pji;- А ,,, ). Производится . Ь . Гичча ::,1епжи..1о Ч1 регистра 8 I lopa nil. г.МБ. программы на МПИ,

Bi }i . нягтс - кчмлидл /(Ч Г от МПИ. По 1 H4-; ;iiii крмандн на 0111 выдает- Т-. р ii Г- икания . ,

, ;. м И , vii.i :;и 0111 задается .. .-iiC; , роичводится I . .ержим,) регистра адре14. I ра .- ных в режиме прямо- .,1 к МПИ. По окончании опе- 14 ОП1 BLuracrcR вектор прерыва,..,

маги1 рали ОШ задается

Прои подител передача . iiiM и ...ежиме прямого u H гом адрес каждого

ппредс, г одержимым - ipp , 1 1 тличается от

: I : минус «.-диницу .Млад1,чрндов л мигтра ад- .Ч -;-| 1Т ячРИ1 -у ОЗУ, Окон- ;.1 J ; о1те 1яотся нулеi.MbiM И сяти младших раз- ti-Tp,( J ipeca. Пг. оконча- - чг: ol -.l вы;тается вектор ; li,() Пр М чводится за. rj a ;1лнньгми, постуt- iP , адресной части - П .4,4:4 тся адрос А

Ь

.и .li. .;;11тги загоузка регистра 11 данными, Г10С гупающими от МПИ. В ;j .P t lioH чагти к; манды ЛЗП задает Я адрес Л

опе 1апии.

р11ячиоди гся загрузка регистра 8 врктор.ч прерывания данными, посту- паыщими от МПИ. В адресной части команды ;;31 задается адрес А,

. lit рЯ НИИ ,

Mq

Г|р,ияя-дигся загрузка ячейки ОЗУ 9 la.гиcTi)Jлeй данными, поступающими m грали МЛН. В адресной час- и команды ЛЗП задается адрес А .

ZZZEII

1

Считывание регистра 2 адреса на ИЛИ

ЧТА2

Считывание регистра 3 данных по МПИ

ЧТД2

Считывание регистра 8 вектора прерывания на МПИ

ЧТВ2

Считывание ОЗУ 9

ЧОП2

Передача содержимого регистра 8 вектора прерывания на ОШ

Считывание абонента с МПИ на общую шину

ЧАО

Передача вектора прерывания с МПИ на ОШ в режиме прерывания

j

4

25

Производится считывание содержимого регистра 2 адреса на МПИ при помощи команды ДЧТ. При этом в адресной части команды задается адрес A,j, .

Производится считывание содержимого регистра 3 данных на МПИ при помощи команды ДТЧ; при этом в адресной части команды задается адрес .

Производится считывание содержимого регистра 8 вектора прерывания на МПИ при помощи команды ДЧТ, при этом в адресной части команды задается адрес А.

Производится считывание содержимого ячейки ОЗУ 9, адрес которой указан десятью младшими разрядами регистра адреса на МПИ при помощи команды АЧТ, при этом в адресной части команды задается адрес А. Содержимое регистра адреса после

окончания операции меняется на .

минус единицу.

Производится загрузка регистра вектора прерываний программ данными, поступающими от МПИ. В адресной части команды ДЗП задается адрес А26 операции. В режиме прерывания на ОШ передается содержимое регистра вектора прерывания в качестве вектора прерывания .

6

По адресной магистрали ОШ задается адрес операции А. Регистр адреса загружается данными, поступающими по магистрали данных. Средствами устройства для сопряжения формируется команда ДЧТ, в адресной части которой передается содержимое регистра адреса. После приема информации на регистр данных в ОШ выдается вектор прерывания В„ .

После обработки сигнала запроса на прерывание ЗПР с шины МПИ на регистр вектора прерывания принимается вектор прерывания.

Передача вектора прерывания ОШ на

ПВП2

Передача содержимого ОЗУ на ОШ по прямому доступу

00

00

01

02

01

00

04

00

02

06

02

02

которьй транслируется на ОШ в режиме прерывания программ. После окончания операции на МПИ выдается вектор прерывания В, .

После обработки сигнала запроса на прерывание ЗП с ОШ на регистр вектора прерывания принимается вектор прерывания, который транслируется на МШ1 в режиме прерывания программ. После окончания операции на 0111 выдается вектор прерывания В , .

В адресной части команды с МПИ задается адрес А,. Производится передача массива данных, записанных с ОЗУ на ОШ в режиме прямого доступа. При этом адрес каждого сообщения определяется содержимым регистра адреса и отличается от пре- дьщущего на минус единицу. Младшие десять разрядов регистра адреса определяют адрес ячейки ОЗУ, Окончание операции определяется нулевым содержанием десяти младших разрядов регистра адреса. По окончании операции на МНИ вьщается вектор прерывания й, .

Таблица 2

Опрос мультиплексора 1 7 по первому каналу

Опрос мультиплексора 18 по первому каналу

Опрос мультиплексора 17 по второму каналу

Опрос пульти- плексора 18 по второму каналу

. f

Начало

Фие.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1509915A2 |

| Устройство для сопряжения двух магистралей | 1989 |

|

SU1615730A2 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Многоканальное устройство для сопряжения ЭВМ | 1988 |

|

SU1695311A1 |

| Микропрограммное устройство сопряжения | 1989 |

|

SU1700560A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1987 |

|

SU1476477A1 |

| Микропроцессор | 1985 |

|

SU1330634A1 |

| Мультипроцессорная система | 1983 |

|

SU1156088A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2042193C1 |

| Устройство для ввода информации | 1986 |

|

SU1352479A1 |

Изобретение относится к вычислительной технике и может быть использовано для связи между магистралью типа Общая шина и магистралью параллельного интерфейса. Целью изобретения является повышение производительности устройства. Цель достигается тем, что в устройство, содержащее три шинных формирователя, мультиплексор, регистр адреса второй магистра-- ли, две группы передатчиков и блок управления, введены счетчик адреса первой магистрали, регистр данных, группа элементов И-ШШ, регистр вектора прерывания, блок оперативной памяти, первый элемент И. Блок управления состоит из двух мультиплексоров, селектора адреса, генератора тактовых импульсов, элемента ИЛИ, элемента И, регистра адреса микрокоманды, триггера адреса, регистра микрокоманд и узла постоянной памяти. 1 з.п. ф-лы, 9 ил., 3 табл. а « (Л со 4 00 00

Адрес слова (йчшни или рееистро)

Дополнительные pojpff i расширения объегюв адресов папйти

Фие.З

Адрес байта S с/годе

Фие.З

Старший foam

Старший розряд

т

Вектор пр ыдония

15

Старший байт

Фиг.5

7 /5 /5 /«

II1

Расширитель adpefHOeo пространства

/ijfoOuji/u Saum

фцгЛ

Младший разряд

Младший разряд

8 7

Младший Saum

Младший разряд

7 Q

фиг. 7

Младший разряд

J

Вых. Г.Т.Н.

Bbix.pfiucm- P0d22,2it

Bbix.pn.JS

Вш.Тг.Гб

Фиг. 8

Вигод мпн

05

Выхов опистра авресо мпн

азп

Suiolnynunu- плеясоре и

бнгев гмппи разрявоехз

вмпд Jff и ftt

8ыхвд nyatmu- паекпро

lujroff oeiucmpa адреса npotpOHH

ОГВ.

вщвникоча- нонви YJ

Sujtof нихроквHOHiH Y,f

tput.S

IT

Составитель В.Вертлиб Редактор И.Сегляник Техред А.Кравчук Корректор В,Бутяга

Заказ 5193/51 Тираж 670Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

| Двухканальное устройство для сопряжения двух электронно-вычислительных машин | 1984 |

|

SU1180906A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропроцессорные средства и системы, 1985, № 1, стр | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-10-30—Публикация

1986-06-02—Подача