Изобретение относится к радйоизмерительной технике и может быть использовано в системах контроля статических и динамических параметров цифровых интегральных схем и цифровых узлов для задания стймулирующих воздействий на испытуемое уст-, ройство.

Целью изобретения является упроще ние формирователя и увеличение выходного сопротивления в высокоимпедансном состоянии.

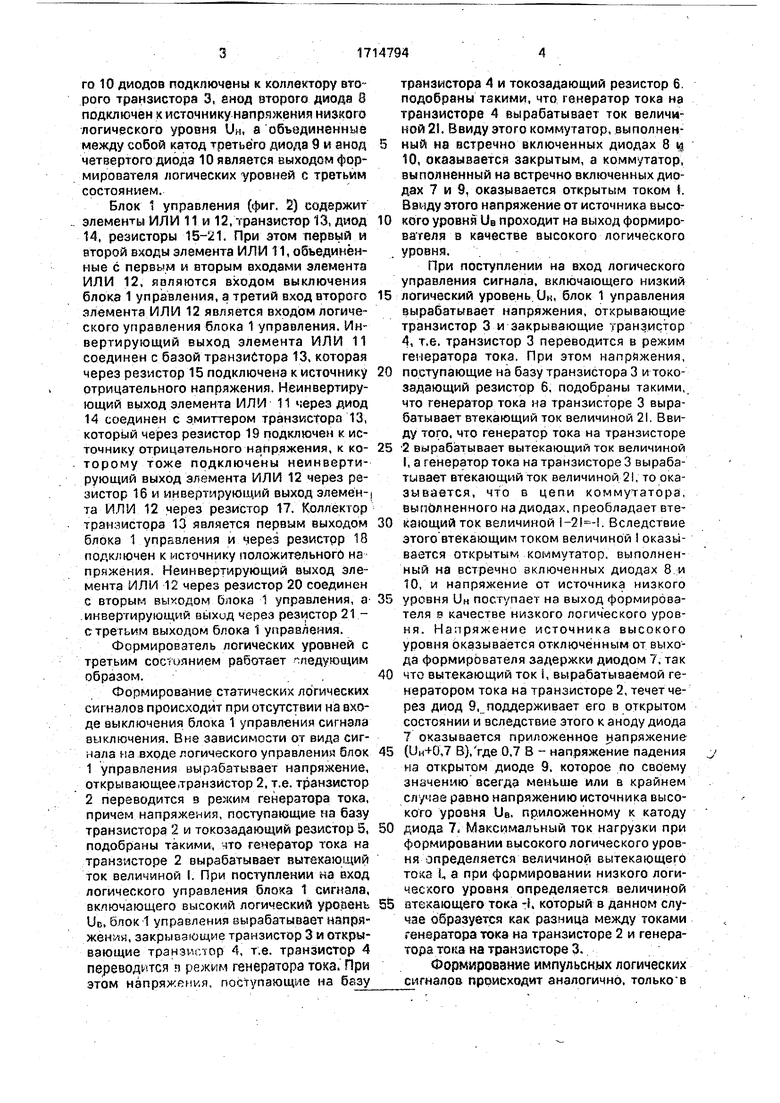

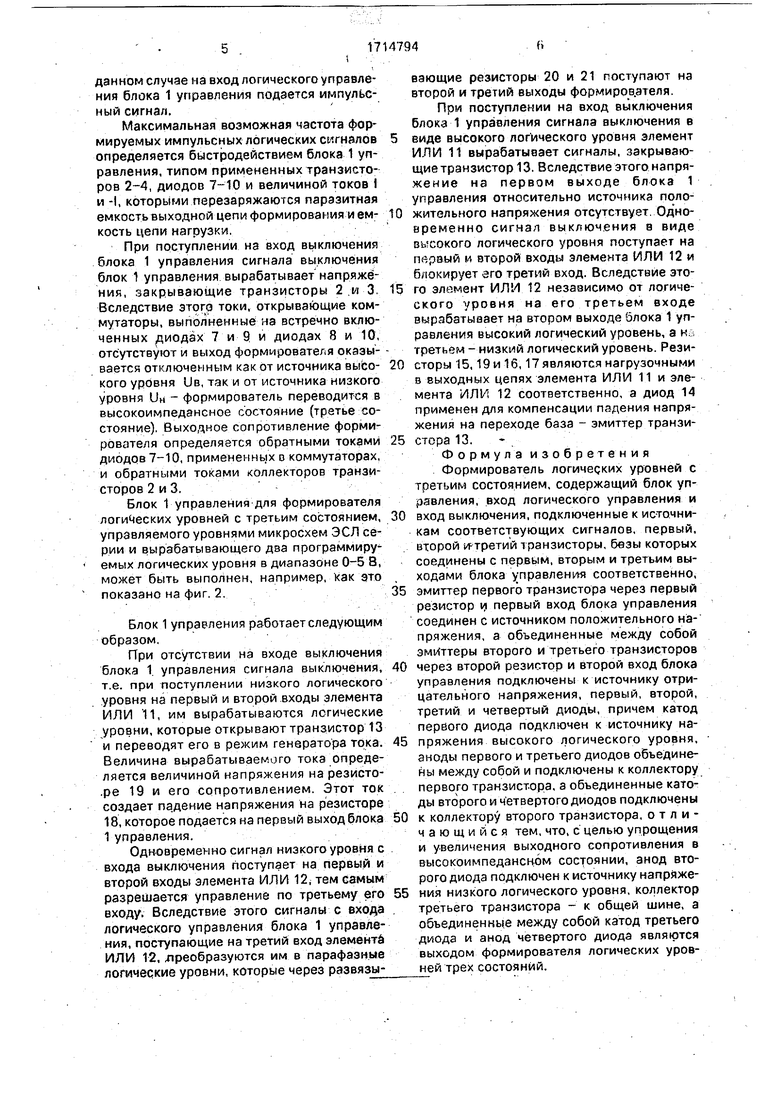

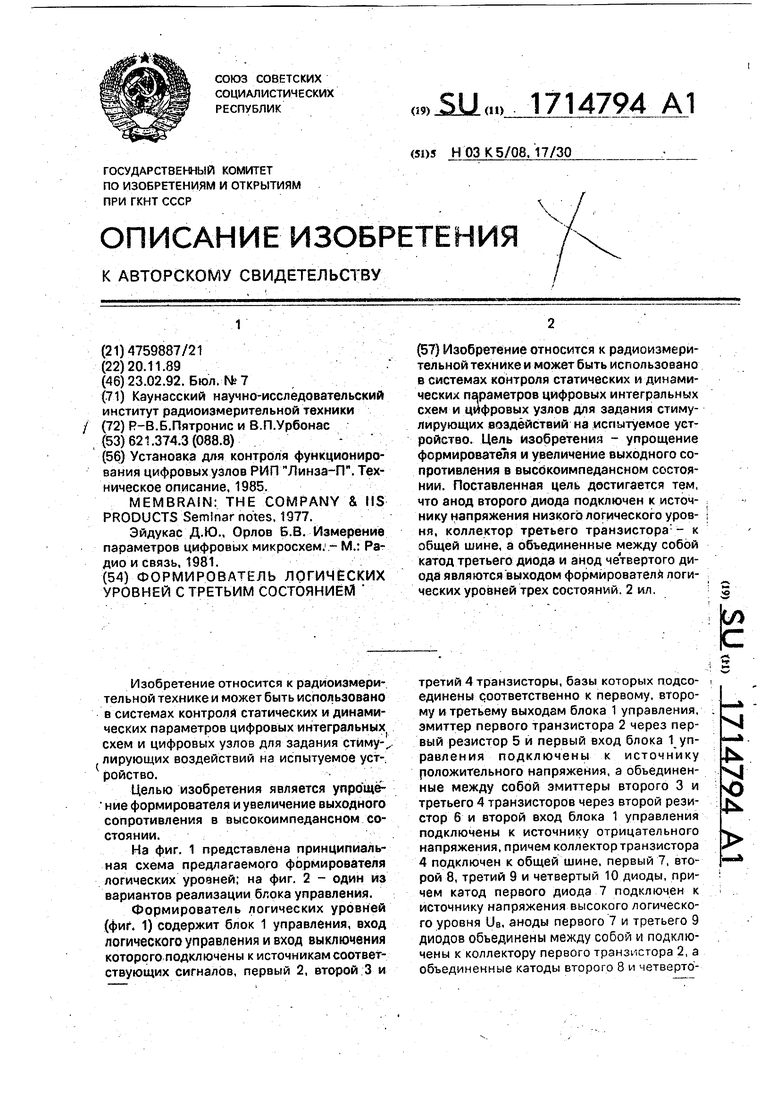

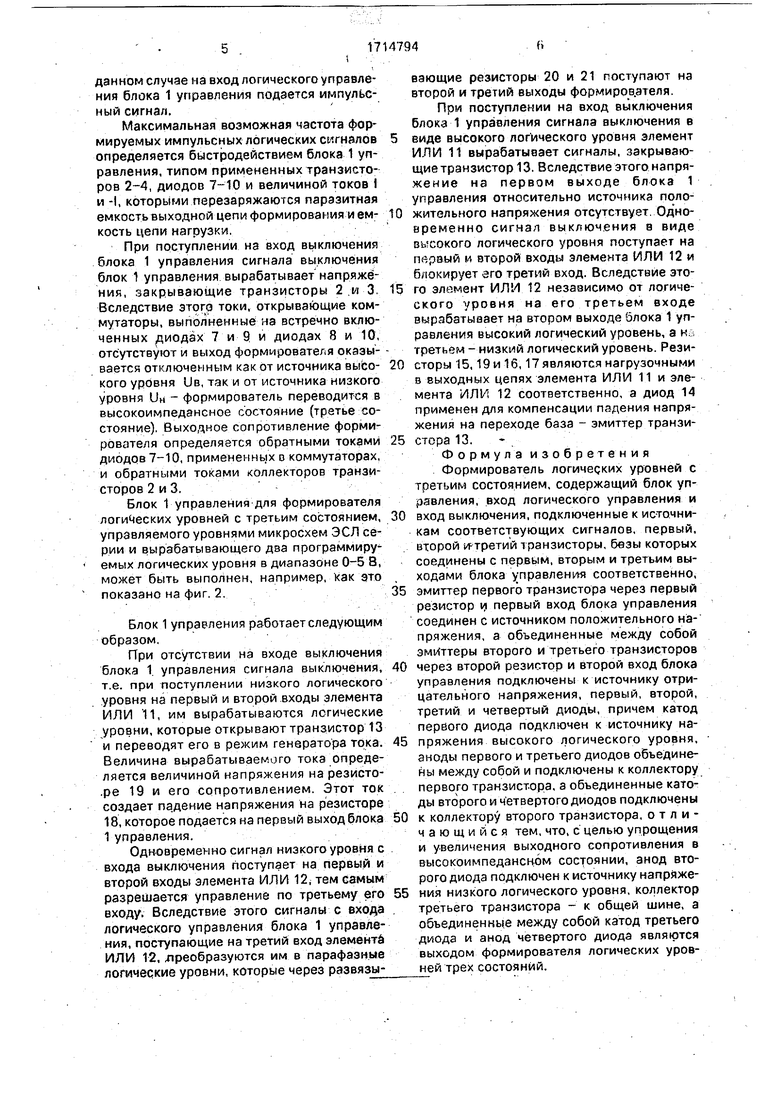

На фиг. 1 представлена принципиальная схема предлагаемого формирователя логических уровней; на фиг. 2 - один из вариантов реализации блока управления.

Формирователь логических уровней (фиГ. 1) содержит блок 1 управления, вход логического управления и вход выключения которого подключены к источникам соответствующих сигналов, первый 2, второй 3 и

третий 4 транзисторы, базы которых подсоединены соответственно к первому, второму и третьему выходам блока 1 управления, эмиттер первого транзистора 2 через первый резистор 5 и первый вход блока 1 управления подключены к источнику роложительного напряжения, а объединенные между собой змиттеры второго 3 и третьего 4 транзисторов через второй резистор 6 и второй вход блока 1 управления подключены к источнику отрицательного напряжения, причем коллектор транзистора 4 подключен к общей шине, первый 7, второй 8, третий 9 и четвертый 10 диоды, причем катод первого диода 7 подключен к источнику напряжения высокого логического уровня UB, аноды первого 7 и третьего 9 диодов объединены между собой и подключены к коллектору первого транзистора 2, а объединенные катоды второго 8 и четвертого 10 диодов подключены к коллектору второго транзистора 3, анод второго диода 8 подключен к источнику напряжения низкого логического уровня UH, а объединенные между собой катод третьего диода 9 и анод четвертого диода 10 является выходом формирователя логических уровней с третьим состоянием.

Блок 1 управления (фиг. 2) содержит элементы ИЛИ 11 и 12, транзистор 13, диод 14, резисторы 15-21. При этом Т1ервый и второй входы элемента ИЛИ 11, объединённые с первым и вторым входами элемента ИЛИ 12, являются входом выключения блока 1 управления, а третий вход второго элемента ИЛИ 12 является входом логического управления блока 1 управления. Инвертирующий выход элемента ИЛИ 11 соединен с баэой транзистора 13. которая через резистор 15 подключена к источнику отрицательного напряжения. Неинвертирующий выход элемента ИЛИ 11 через диод 14 соединен с эмиттером TpaH3«ctopa 13, который через резистор 19 подключен к источнику отрицательного напряжения, к которому тоже подключены неинвертирующий выход элемента ИЛИ 12 через резистор 16 и инвертирующий выход элемёнта ИЛИ 12 через резистор 17. Коллектор транзистора 13 является первым выходом блока 1 управления и через резистрр 18 подключен к источнику положительного на пряжения. Неинвертирующий выход элемента 12 через резистор 20 соединен с вторым выходом блока 1 управления, а .инвертирующий вь1хид через резистор 21 с третьим выходом блока 1 управления.

Формирователь логических уровней с третьим состоянием работает следующим образом.. .

Формирование статических логических сигналов происходит при отсутствии на входе выключения блока 1 управления сигнала выключения. Вне зависимости от вида сигнала на входе логического управления блок

1управления вырабатывает напряжение, открывающее (Транзистор 2, т.е. транзистор

2переводится в режим генератора тока, причем напряжения, поступающие на базу транзистора 2 и токозадающий резистор 5, подобраны такими, что генератор тока на транзисторе 2 вырабатывает вытекающий ток величиной I. При поступлении на вход логического управления блока 1 сигнала, включающего высокий логический уровень Uc. блок 1 управления вырабатываетнапря жений, закрывающие транзистор 3 и открывающие TpaH3Vi(vvop 4, т.е. транзистор 4 переводится п режим генератора тока. При этом напряжения, поступающие на базу

транзистора А и токозадающий резистор 6. подобраны такими, что генератор тока на транзисторе 4 вырабатывает ток величиной 2. Ввиду этого коммутатор, выполненный на встречно включенных диодах 8 i 10, оказывается закрытым, а коммутатор, выполненный на встречно включенных диодах 7 и 9, оказывается открытым током t. Ввиду этого напряжение от источника высокого уровня UB проходит на выход формирователя в качестве высокого логического уровня.

При поступлении на вход логического управления сигнала, включающего низкий

5 логический уровень. UH, блок 1 управления вырабатывает напряжения, открывающие транзистор 3 и закрывающие транзистор 4, т.е. транзистор 3 переводится в режим генератора тока. При этом напряжения,

0 поступающие на базу транзистора 3 и токозадающий резистор 6, подобраны такими, что генератор тока на транзисторе 3 вырабатывает втекающий ток величиной 21. Ввиду того, что генератор тока на транзисторе

5 2 вырабатывает вытекающий ток величиной I, а генератор тока на транзисторе 3 вырабатывает втекающий ток величиной. 21. то оказывается, что в цепи коммутатора, выполненного на диодах, преобладает втекающий ток величиной 1-2 Вследствие этого втекающим током величиной I оказь вается открытым коммутатор, выполненный на встречно включенных диодах 8 и 10, и напряжение от источника низкого

5 уровня UH поступает на выход формирователя 9 качестве низкого логического уровня. Напряжение источника высокого уровня Ьказывается отключённым от выхода формирователя задержки диодом 7, так

0 что вытекающий ток 1, вырабатываемой генератором тока на транзисторе 2, течет через диод 9, поддерживает его в открытом состоянии и вследствие этого к аноду диода 7 оказывается приложенное напряжение

5 (ин+0,7 В),где 0,7 В - напряжение падения на открытом диоде 9, которое по своему значению всегдэ меньше или в крайнем случае равно напряжению источника высокого уровня UB. приложенному к катоду

0 диода 7. Максимальный ток нагрузки при формировании высокого логического уровня определяется величиной вытекающего тока L а при формировании низкого логического уровня определяется величиной

S втекающего тока -}. который в данном случае образуется как разница между токами генератора тока на транзисторе 2 и генератора тока на транзисторе 3Формирование импульсных логических сигналов nptsMCxoAHT аналогично, тольков

данном случае на вход логического управления блока 1 управления подается импульсный сигнал.

Максимальная возможная частота формируемых импульсных логических сигналов определяется быстродействием блока 1 управления, типом примененных транзисторов 2-4, диодов 7-10 и величиной токов 1 и-I, которыми перезаряжаются паразитная емкость выходной цепи формирования и емкость цепи нагрузки,

При поступлении на вход выключения блока 1 управления сигнала выключения блок 1 управления вырабатывает напряжений, закрывающие транзисторы 2 .и 3, Вследствие зтогд токи, открывающие коммутаторы, выполненные на встречно включенных диодах 7 и Q и диодах 8 и 10, отсутствуют и выход формирователя оказывается отключенным как от источника выЬокого уровня UB, так и от источника низкого уровня UH - формирователь переводится в высокоимпедансное состояние (третье состояние). Выходное сопротивление формирователя определяется обратными токами диодов 7-10, применеинь1х о коммутаторах, и обратными токами коллекторов транзисторов 2 и 3.

Блок 1 управления для формирователя логи1еских уровней с третьим состоянием, управляемого уровнями микросхем ЭСЛ серии и вырабатывающего два программируемых логических уровня в диапазоне 0-58, может быть выполнен, например, Как это показано на фиг. 2.

Блок 1 управления работает следующим образом,

При отсутствии на входе выключения блока 1. управления сигнала выключения, т.е. при поступлении низкого логического уровня на первый и второй входы элемента ИЛИ 11, им вырабатываются логические уровни, которые открывают транзистор 13 и переводят его в режим генератора тока. Величина вырабатываемого тока определяется величиной напряжения на резисто.ре 19 и его сопротивлением. Этот ток создает па.дение напряжения на резисторе 18, которое подается на первый выход блока 1 управления.

Одновременно сигнал низкого уровня с входа выключения поступает на первый и второй входы элемента ИЛИ 12 тем самым разрешается управление по третьему его входу. Вследствие этого сигналы с входа логического управления блока 1 управления, поступающие на третий вход элемент ИЛИ 12, преобразуются им в парафаэные логические уровни, которые через развязывающие резисторы 20 и 21 поступают на второй и третий выходы формиров.ателя.

При поступлении на вход выключения блока 1 управления сигнала выключения в виде высокого логического уровня элемент ИЛИ 11 вырабатывает сигналы, закрывающие транзистор 13. Вследствие этого напряжение на первом выходе блока 1 управления относительно источника положительного напряжения отсутствует. Одновременно сигнал выключения в виде высокого логического уровня поступает на пераый и второй входы элемента ИЛИ 12 и блокирует его третий вход. Вследствие этого элемент ИЛИ 12 независимо от логического уровня на его третьем входе вырабатывает на втором выходе блока 1 управления высокий логический уровень, а на третьем - низкий логический уровень. Резисторы 15,19 и 16,17 являются нагрузочными и выходных цепях элемента ИЛИ 11 и элемента ИЛИ 12 соответственно, а диод 14 применен для компенсации падения напряжения на переходе база - эмиттер транзистора 13. Формул а изобретения Формирователь логических уровней с третьим состоянием, содержащий блок управления, вход логического управления и вход выключения, подключенные к источникам соответствующих сигналов, первый, второй и третий транзисторы, базы которых соединены с первым, вторым и третьим выходами блока управление соответственно, эмиттер первого транзистора через первый резистор ц первый вход блока управления соединен с источником положительного напряжения, а объединенные между собой эмиттеры второго и третьего транзисторов через второй резистор и второй вход блока управления подключены к источнику отрицательного напряжения, первый, второй, третий и четвертый диоды, причем катод переого диода подключен к источнику напряжения высокого логического уровня, аноды первого и третьего диодов объединены между собой и подключены к коллектору первого транзистора, а объединенные като ды второго и четвертого диодов подключены к коллектору второго транзистора, отличающийся тем, что, с целью упрощения и увеличения выходного сопротивления в высокоимпедансном состоянии, анод второго диода подключен к источнику напряжения низкого логического уровня, коллектор третьего транзистора - к общей шине, а объединеннь1е между собой катод третьего диода и анод четвертого диода являются выходом формирователя логических уровней трех состояний. В.Ьыкл, Bx.AQS.ynf).

Фи2.1

и Bbiwd

Bt Змклтенм

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых блоков | 1988 |

|

SU1619208A1 |

| ЧАСТОТНО-РЕГУЛИРУЕМЫЙ ЭЛЕКТРОПРИВОД С НЕУПРАВЛЯЕМЫМ ЗВЕНОМ ПОСТОЯННОГО ТОКА | 1993 |

|

RU2067352C1 |

| Формирователь тока | 1990 |

|

SU1734204A1 |

| ВЫХОДНАЯ СХЕМА С ТРЕМЯ СОСТОЯНИЯМИ | 1992 |

|

RU2072629C1 |

| Устройство для передачи двоичного сигнала в канал связи | 1987 |

|

SU1427591A1 |

| Система автоматического управления механической трансмиссией транспортного средства | 1987 |

|

SU1495154A1 |

| Формирователь адресных токов | 1979 |

|

SU924752A1 |

| РЕЛЕ ВРЕМЕНИ (С ВЫХОДОМ НА СИМИСТОРЕ) | 1992 |

|

RU2130213C1 |

| ОДНОТАКТНЫЙ СТАБИЛИЗИРУЮЩИЙ ПРЕОБРАЗОВАТЕЛЬ ПОСТОЯННОГО НАПРЯЖЕНИЯ | 1991 |

|

RU2007826C1 |

| Импульсный источник тока | 1982 |

|

SU1034181A1 |

Изобретение относится к радиоизмерительной технике и может быть использовано в системах контроля статических и динамических параметров цифровых интегральных схем и Ц14фровых узлов для задания стимулирующих воздействий на испытуемое устройство. Цель изобретения - упрощение формирователя и увеличение выходного сопротивления в высокоимпедансном состоянии. Поставленная цель достигается тем, что анод второго диода подключен к источнику напряжения низкого логического уровня, коллектор третьего транзистора'- к общей шине, а объединенные между собой катод третьего диода и анод четвертого диода являются выходом формирователи логических уровней трех состояний.2 ил.

| Установка для контроля функционирования цифровых узлов РИП"Линза-П" | |||

| Техническое описание, 1985.MEMBRAIN: THE COMPANY & IIS PRODUCTS Seminar notes | |||

| Шеститрубный элемент пароперегревателя в жаровых трубках | 1918 |

|

SU1977A1 |

| Орлов Б.В | |||

| Измерение параметров цифровых микросхем:- М.: Радио и связь, 1981. | |||

Авторы

Даты

1992-02-23—Публикация

1989-11-20—Подача