Изобретение относится к вычислительной технике и может быть использовано в магнитных оперативных запоминающих устройствах (МОЗУ) цифровых вычислительных.машин.

Известен формирователь адресных токов, содержащий общие потенциально связанные ключи для чтения и записи, опорные ключи тока, ключи для перезарядки паразитных ёмкостей, диодные ключи, генераторы тока, дешифратор и регистр адреса Формирователь адресного тока экономит ключи тока примерно в два разаП.

К недостаткам формирователя адресного тока относятся электрическая привязка ключей адресных токов к нулевому потенциалу, потребление мощности в статическом режиме потенционально связанными ключами, а также наличие большого числа ключей и диодов, включенных последователь но с нагрузкой, что нарушает условие

стабилизации адресных токов в шинах накопителя.

Наиболее близким к предлагаемому является формирователь адресных токов, содержащий группы трансформаторных ключей, в которых начала первичных обмоток подключены к соответствующим выходам первой группы т.око.зых ключей, а концы - к анодам диодов, эмиттеры транзисторов первого и второго ключа и коллекторы транзисторов третьего и четвертого ключа со-. единены с первой группой выходов, эмиттеры транзисторов третьего и четвертого ключа объединены во всех группах трансформаторных ключей и соединены с первым выходом второй группы выходов, коллекторы транзисторов первого и второго ключа объединены во всех группах трансформаторных ключей и соединены со вторым выходом второй группы выходов, первые и вторые входы двух групп токовых ключей подключены к источником питания, третьи входы первой группы токовых ключей подключены к выходам дешифраторов, входы которого подключены к выходам старших разрядов регистра адреса, третьи входы второй группы токовых ключей подключены к выходам логического блока, первые и вторые входы которого соединены с первым и вторым входами формирователя 2 .

Недостатком данного формирователя адресных токов является то, что для управления каждым трансформаторным ключом втекающего и вытекающего тока используется свой токовый ключ, подключенный к соответствую-. 14ему выходу дешифратора, и дополнительно два общих токовых ключа, управляемые логическим блоком, Всеэто прийодит к увеличению объема оборудо вания формирователя адресных токов.

Цель изобретения - повьниение надежности адресного формирователя.

Поставленная цель достигается тем, что формирователь адресных токов, содержащий группы ключей, состоящих из трансформатора, транзистора и диода, в которых начала первичных обмоток трансформаторов подключены к соответствующим выходам токовых ключей первой группы, а концы - к анодам диодов, эмиттеры транзисторов первого и второго ключей и коллекторы транзисторов третьего и четвертрго ключей соединены с выходами первой группы выходов формирователя адресных токов, эмиттеры транзисторов третьего и четвертого ключей каждой группы объединены и соединены с первым выходом второй группы выхо-. дов формирователя адресных токов, коллекторы транзисторов первого и второго ключей каждой группы объединены и соединены с вторым выходом второй группы выходов формирователя адресных токов, первые и вторые входы двух групп токовых ключей подг ключены к источникам питания, третий вход каждого токового ключа первой группы подключен к соответствующему выходу дешифратора, входы которого подключены к выходам старших разрядов регистра адреса, третий вход каждого токового ключа второй группы подключен к соответствующим выходам логического блока, первый и второй входы которого соединены с соответствующими входами формирователя адресных токов, к третьему и четвертому входам логического блока подключены соответственно инверсный и прямой выходы младшего разряда регистра адреса, при этом каждый из выходов токовых ключей второй группы подключен к соответствующим катодам диодов.

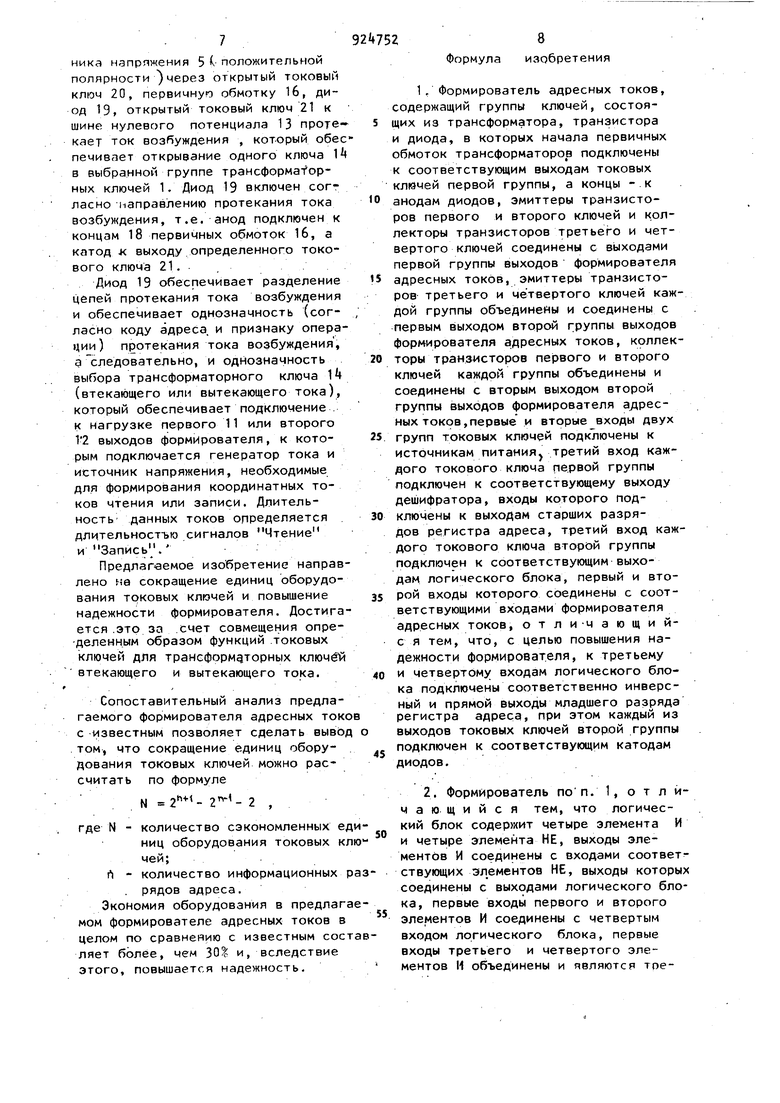

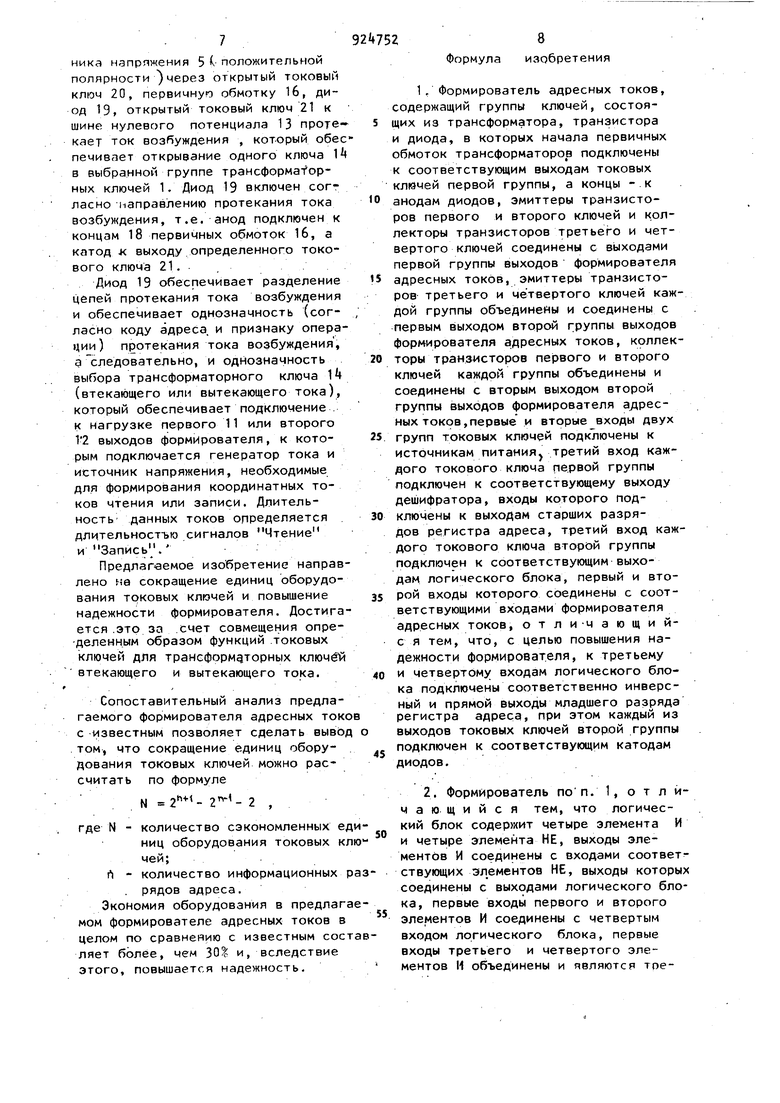

Кроме того, логический блок содержит четыре элемента И и четыре элемента НЕ, выходы элементов И соединены с входами соответствующих элементов НЕ, выходы которых соединены с выходами логического блока, первые

входы первого и второго Элементов И соединены с четвертым входом логического блока, первые входы третьего и четвертого элементов И объединены и являются третьим входом логического блока, вторые входы первого и

третьего элементов И объединены и являются вторым входом логического блоka, вторые входы второго и четвертого элементов И объединены и являются первым входом логического блока.

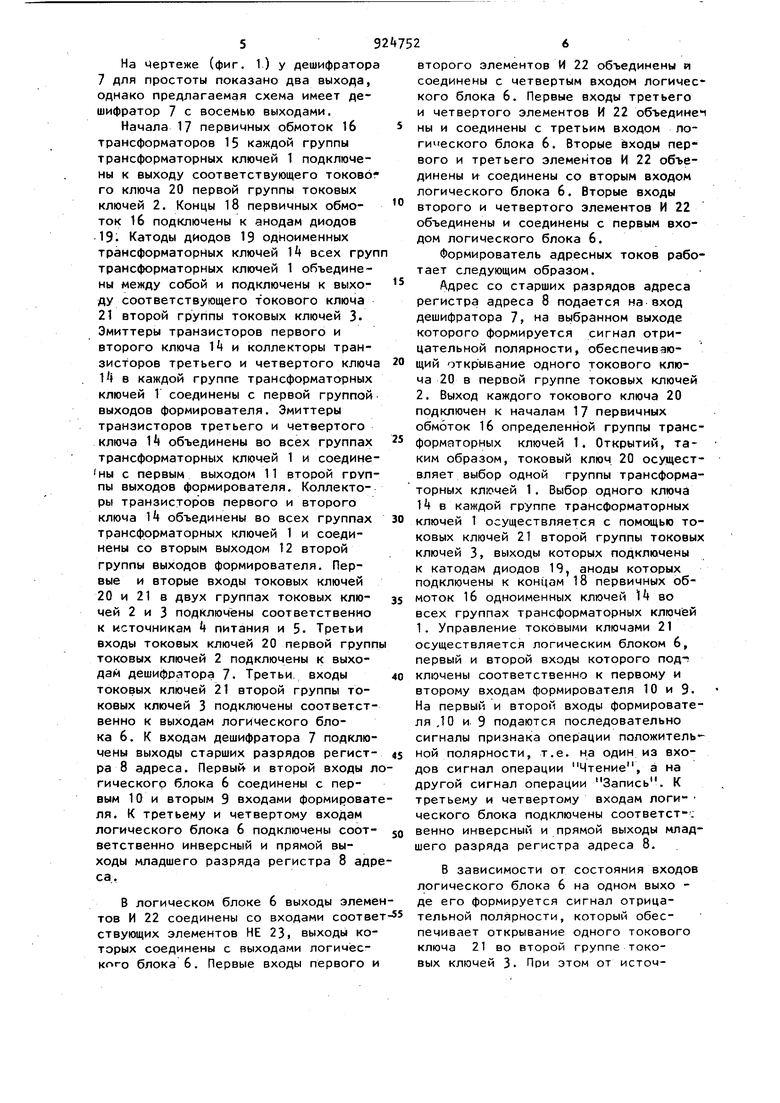

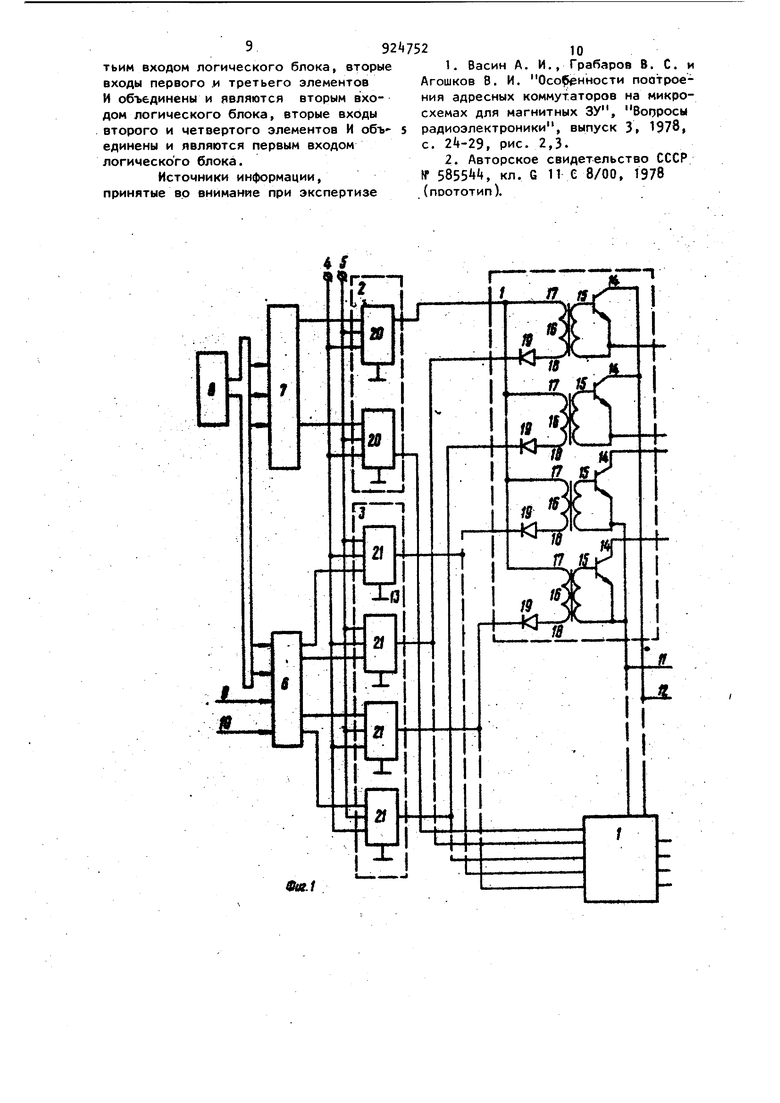

На фиг. 1 изображен предлагаемый формирователь, принципиальная схема; на фиг. 2 - логический блок, принципиальная схема.

Формирователь адресных токов содержит . восемь групп ключей 1 втекающего и вытекающего токов, первую группу токовых ключей 2, ВТОРУЮ группу токовых ключей 3, источники 4 и 5 питания токовых ключей, логический блок 6, дешифратор 7, регистр 8 адреса, второй вход адресного формирователя 9 и первый вход адресного формирователя 10, первый и второй выходы 11 и 12 второй группы выходов адресного формирователя, которые служат для подключения генератора тока и источника напряжения для формирования координатных токов чтения или записи, шину нулевого 13 потенциала.

Каждая группа ключей 1 содержит четыре транзистора ключа И (два втекающего и два вытекающего тока) с трансформаторами 15 в цепи управления, перйичные обмотки 16 которых имеют начало 17 и конец 18, четыре диода 19.

Первая группа токовых ключей 2 содержит восемь токовых ключей 20.

Вторая группа токовых ключей 3 содержит четыре токовых ключа 21. Логический блок 6 содержит четыре элемента И 22 и четыре элемента НЕ 23На чертеже (фиг. 1) у дешифратора 7 для простоты показано два выхода, однако предлагаемая схема имеет дешифратор 7 с восемью выходами.

Начала 17 первичных обмоток 1б трансформаторов 15 каждой группы трансформаторных ключей 1 подключены к выходу соответствующего токовог го ключа 20 первой группы токовых ключей 2. Концы 18 первичных обмоток 16 подключены к анодам диодов 19. Катоды диодов 19 одноименных трансформаторных ключей 1 всех груп трансформаторных ключей 1 объединены между собой и подключены к выходу соответствующего токового ключа 21 второй группы токовых ключей 3. Эмиттеры транзисторов первого и второго ключа 1 и коллекторы транзисторов третьего и четвертого ключа в каждой группе трансформаторных ключей 1 соединены с первой группой выходов формирователя. Эмиттеры транзисторов третьего и четвертого ключа I объединены во всех группах трансформаторных ключей 1 и соединены с первым выходом 11 второй ГРУППЫ выходов формирователя. Коллекторы транзисторов первого и второго ключа I объединены во всех группах трансформаторных ключей 1 и соединены со вторым выходом 12 второй группы выходов формирователя. Первые и вторые входы токовых ключей 20 и 21 в двух группах токовых ключей 2 и 3 подключены соответственно к источникам питания и 5 Третьи входы токовых ключей 20 первой групп токовых ключей 2 подключены к выходам дешифратора 7. Третьи входы токовых ключей 21 второй группы токовых ключей 3 подключены соответственно к выходам логического блока 6. К входам дешифратора 7 подключены выходы старших разрядов регистра 8 адреса. Первый и второй входы лгического блока 6 соединены с первым 10 и вторым 9 входами формироватля. К третьему и четвертому входам логического блока 6 подключены соответственно инверсный и прямой выходы младшего разряда регистра 8 адрса,

В логическом блоке 6 выходы элеметов И 22 соединены со входами соотве ствующих элементов НЕ 23, выходы которых соединены с выходами логического блока 6. Первые входы первого и

второго элементов И 22 объединены и соединены с четвертым входом логического блока 6. Первые входы третьего и четвертого элементов И 22 объединеч ны и соединены с третьим входом логического блока 6. Вторые входы первого и третьего элементов И 22 объединены н соединены со вторым входом логического блока 6. Вторые входы второго и четвертого элементов И 22 объединены и соединены с первым входом логического блока 6.

Формирователь адресных токов работает следующим образом.

Адрес со старших разрядов адреса регистра адреса 8 подается на вход дешифратора 7, на вь1бранном выходе которого формируется сигнал отрицательной полярности, обеспечивающий открывание одного токового ключа 20 в первой группе токовых ключей 2. Выход каждого токового ключа 20 подключен к началам 17 первичных обмоток 16 определенйой группы трансформаторных ключей 1. Открытий, таким образом, токовый ключ 20 осуществляет выбор одной группы трансформаторных ключей 1. Выбор одного ключа 14 в каждой группе трансформаторных ключей 1 осуществляется с помощью токовых ключей 21 второй группы токовых ключей 3, выходы которых подклю1чены к катодам диодов 19, аноды которых подключены к концам 18 первичных обмоток 16 одноименных ключей Н во всех группах трансформаторных ключей 1. Управление токовыми ключами 21 осуществляется логическим блоком 6, первый и второй входы которого под- клочены соответственно к первому и второму входам формирователя 10 и 9. На первый и второй входы формирователя ,10 и. 9 подаются последовательно сигналы признака операции положительной полярности, т.е. на один из входов сигнал операции Чтение, а на другой сигнал операции Запись. К третьему и четвертому входам логи- ческого блока подключены соответст-: венно инверсный и прямой выходы младшего разряда регистра адреса 8.

В зависимости от состояния входов логического блока 6 на одном выхо де его формируется сигнал отрицательной полярности, который обеспечивает открывание одного токового ключа 21 во второй группе токовых ключей 3. При этом от источника напряжения 5 ( положительной полярности через открытый токовый ключ 20, первичную обмотку 16, диод 19, открытый токовый ключ 21 к шине нулевого потенциала 13 проте- кает ток возбуждения , который обес печивает открывание одного ключа 1 в выбранной группе трансформаторных ключей 1. Диод 19 включен согг ласно направлению протекания тока возбуждения, т.е. анод подключен к концам 18 первичных обмоток 16, а катод X выходу определенного токового ключа 21, Диод 19 обеспечивает разделение цепей протекания тока возбуждения и обеспечивает однозначность (согласно коду адреса, и признаку операции ) протекания тока возбуждения , а следовательно, и однозначность выбора трансформаторного ключа 1 (втекающего или вытекающего тока), который обеспечивает подключение . К Нагрузке первого 11 или второго 12 выходов формирователя, к которым подключается генератор тока и источник напряжения, необходимые для формирования координатных токов чтения или записи. Длительность данных токов определяется . длительностъю сигналов Чтение и Запись . Предлагаемое изобретение направлено sa сокращение единиц оборудования токовых ключей и повышение надежности формирователя. Достигается .это за .счет совмещения определенн.ым образом функций .токовых ключей для трансформаторных ключёТй втекающего и вытекающего тока. / Сопоставительный анализ предлагаемого формирователя адресных токо с известным позволяет сделать вывЬд том, что сокращение единиц оборудования токовых ключей можно рассчитать по формуле 2 - 2 где N - количество сэкономленных ед ниц оборудования токовых кл чей; Л - количество информационных р . рядов адреса. Экономия оборудования в предлага мом формирователе адресных токов в целом по сравнению с известным сост ляет более, чем 30° и, вследствие этого, повышается надежность. 28 Формула изобретения 1,Формирователь адресных токов, содержащий группы ключей, состоящих из трансформатора, транзистора и диода, в которых начала первичных обмоток трансформаторов подключены к соответствующим выходам токовых кличей первой группы, а концы -.к анодам диодов, эмиттеры транзисторов первого и второго ключей и коллекторы транзисторов третьего и четвертого ключей соединены с вь1ходами первой группы выходов формирователя адресных токов, эмиттеры транзисторов третьего и четвертого ключей каждой группы объединены и соединены с первым выходом второй группы выходов формирователя адресных токов, коллекторы транзисторов первого и второго ключей каждой группы объединены и соединены с вторым выходом второй группы выходов формирователя а;;ресных токов,первые и вторые входы двух групп токовых ключей подключены к источникам питания, третий вход каждого токового ключа первой группы подключен к соответствующему выходу дешифратора, входы которого подключены к выходам старших разрядов регистра адреса, третий вход каждого токового ключа второй группы подключен к соответствующим выходам логического блока, первый и второй входы которого соединены с соответствующими входами формирователя адресных токов, отли-чающийс я тем, что, с целью повышения надежности формирователя, к третьему и четвертому входам логического блока подключены соответственно инверсный и прямой выходы младшего разряда регистра адреса, при этом каждый из выходов токовых ключей второй группы подключен к соответствующим катодам диодов. 2.Формирователь поп. 1, отличающийся тем, что логический блок содержит четыре элемента И и четыре элемейта НЕ, выходы элементов И соединены с входами соответ ствующих элементов НЕ, выходы которых соединены с выходами логического блока, первые входы первого и второго элементов И соединены с четвертым входом логического блока, первые входы третьего и четвертого элементов М объединены и являются тое992i 7тьим входом логического блока, вторые входы первого i третьего элементов И объединены и являются вторым входом логического блока, вторые входы второго и четвертого элементов И объ- 5 единены и являются первым входом логического блока. Источники информации, принятые во внимание при экспертизе 2 1.Васин А. И,, Грабаров В. С. и Агошков В. И. Осо нности построения адресных коммутаторов на микросхемах для магнитных ЗУ, Вопросы радиоэлектроники, выпуск 3, 1978, с. 2k-23, рис. 2,3. 2.Авторское свидетельство СССР ff , кл. G 11 С 8/00, 1978 (поототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОПОЗИЦИОННАЯ МАТРИЦА УПРАВЛЕНИЯ | 1972 |

|

SU337818A1 |

| Запоминающее устройство | 1983 |

|

SU1112412A1 |

| УСТРОЙСТВО ПРОТИВОАВАРИЙНОЙ АВТОМАТИКИ | 2001 |

|

RU2221318C2 |

| Устройство для адресно-разрядной выборки системы 2,5 д | 1973 |

|

SU531277A1 |

| УСТРОЙСТВО ДЛЯ ИМИТАЦИИ ОТКАЗОВ И ВНУТРИСХЕМНОГО ТЕСТИРОВАНИЯ ЭЛЕМЕНТОВ ДИСКРЕТНОЙ АППАРАТУРЫ | 1995 |

|

RU2093885C1 |

| Запоминающее устройство с сохранением информации при отключении питания | 1986 |

|

SU1365133A1 |

| Устройство для выбора информации из блоков памяти | 1982 |

|

SU1019491A1 |

| ФОРМИРОВАТЕЛЬ КОМАНД УПРАВЛЕНИЯ | 2003 |

|

RU2244960C2 |

| ПЬЕЗОТРАНСФОРМАТОРНОЕ ЗАПОЛИШАЮЩЕЕ УСТРОЙМТ?|11е0-1ЕЛКГ1:: | 1972 |

|

SU331421A1 |

| Полупостоянное запоминающее устройство с электрической перезаписью информации | 1983 |

|

SU1088068A1 |

23

23

23

23

Фиг. 2

Авторы

Даты

1982-04-30—Публикация

1979-08-06—Подача