Изобретение относится к вычислитель ной технике и может быть использовано в вычислительных системах, ориентированных на обработку потока запросов с циклической дисциплиной обслуживания.

Известно устройство приоритета, содержащее два регистра, сдвигающий рё- гистр, первую группу элементов И, первый элемент И, элемент запрета, триггер.

Недостатком данного устройства явля ется низкое быстродействие.

Наиболее близким по технической сущности к изобретению следует считать выбранное в качестве прототипа устройство циклического приоритета, содержащее два регистра, первую группу элементов И, пер- вый элемент ИЛИ, элемент запрета, триггер и первый сдвигающий регистр, вход сдвига которого соединен с выходом элемента запрета, прямой вход которого соединен с тактовым входом устройства, инверсный вход элемента запрета подключен к выходу первого элемента ИЛИ, выходы которого соединены с выходами элементов И первой группы, первый и второй входы каждого элемента И первой группы подключены к одноименным выходам соответственно первого регистра и первого Сдвигающего регистра, установочные входы которых и вход сброса триггера соединены с установочным входом устройства, каждый запросный вход которого соединен с единичным входом соответствующего разряда первого регистра. Кроме того, устройство содержит второй регистр, вторую, третью и четвертую группы элементов И, второй элемент ИЛИ и элемент И, единичный вход триггера подключен к выходу первого элемента ИЛИ, выход триггера

подключен к первому входу элемента И, второй вход которого подключен к тактовому входу устройства, выход элемента И подключен к входу сдвига второго сдвигающего регистра, выход каждого разряда которого, 5 кроме выхода дополнительного разряда, соединен с первым входом одноименного элемента И второй группы, второй вход которого соединен с выходом одноименного разряда второго регистра, выходы зле- 10 ментов И второй группы соединены с входами второго элемента ИЛИ, выход которого соединен с нулевым входом триггера и с первыми входами элементов И третьей и четвертой групп, вторые входы которых 15 подключены к выходам элементов И соответственно третьей и четвёртой групп, выходы которых являются выходами соответственно разрешения обслуживания

и идентификации каналов обслуживания ус- 20 тройства и соединены с нулевыми входами соответственно первого и второго регистров, единичные входы второго регистра подключены к входам готовности устройства, установочный вход устройства соединен 25 с установочными входами второго регистра и второго сдвигающего регистра, выходы элементов И первой и второй групп соединены с вторыми входами одноименных элементов И соответственно третьей и 30 четвертой групп.

Данное устройство обеспечивает выдачу кода запроса в свободный канал путем последовательного опроса регистра запросе посредством регистра сдвига, а затем 35 при обнаружении запроса - поиск свободного канала.

Недостатком известного устройства является низкое быстродействие, обусловленное последовательностью этапов поиска1 40 запроса и поиска канала..

Проведем оценку быстродействия устройства.

Время работы устройства можно определить по соотношению45

Tcp.1 tcp.3 + tcp.K,

где tcp.3 - время поиска запроса; tcp.K - время поиска канала.

(1)

Если регистр запросов содержит п разрядов, а запросы могут фиксироваться в любом из его разрядов, то время поиска запроса может быть вычислено, как среднее время

Тмин.З + tyaKcJ tcp.3 п

Где 1мин., Тмакс..

Отсюда

tcp.3 1L5Ll Тги.,(2)

Аналогичным образом время поиска канала представляет собой соотношение

tcp.K

tMHH.K .+ tмакс,к

где Т.мин.. tMaKC..

Отсюда

tcp.K

К -Г 1

tfM.

(3)

0 5 0

5

0

5

0

5

Подставив выражения (2) и (3) в (1). пол: учим

т п +к +2.,..

Тср.1 --g--

Из выражения (4) видно, что время передачи запроса на обслуживание зависит как от числа запросов, так и от количества каналов..Целью изобретения является повышение быстродействия за счет одновременного поиска запроса и свободного канала.

Указанная цель достигается тем, что в устройство циклического приоритета, со держащее два сдвигающих регистра, два регистра, первый элемент запрета, два элемента ИЛИ, четыре группы элементов И, элемент И и триггер, причем вход сдвига первого сдвигающего регистра соединение выходом первого элемента запрета, запрос ные входы и входы готовности каналов уст- ройства подключены к единичным входам первого и второго регистров соответственно, единичные выходы первого сдвигающего регистра и первого регистра подключены соответственно к первым и вторым входам одноименных элементов И первой группы, выходы элементов И первой группы соединены с первыми входами одноименных элементов И третьей группы и с соответствующими входами первого элемента ИЛИ, выход которого подключен к инверсному входу первого элемента запрета, единичные выходы второго сдвигающего регистра и второго регистра подключены соответственно к первым и вторым входам одноименных элементов И второй группы, выходы элементов И второй группы соедийены с соответствующими входами второго элемента ИЛИ и первыми входами одноименных элементов И четвертой группы, выход второго элемента ИЛИ подключен к вторым входам элементов И третьей группы, выходы которых являются выходами разрешения обслуживания устройства и соединены с нулевыми входами одноименных разрядов первого регистра, выходы элементов И четвертой группы являются выходами идентификации каналов устройства и подключены к нулевым входам одноименных разрядов второго регистра, введены два элемента ИЛЙ-НЕ, третий элемент ИЛИ, элемент задержки и второй элемент запрета, выход которого соединен с входом сдвига второго сдвигающего регистра, установочный вход которого подключен к установочному входу первого сдвигающего регистра, входам сброса первого и второго регистров, к единичному входу триггера и входу пуска устройства, выход готовности которого соединен с нулевым выходом тр.г- герэ, единичный выход которого подключен к вторым прямым входам первого и второго элементов запрета, выход второго элемента ИЛИ соединен с инверсным входом второго элемента запрета, выход первого элемента ИЛИ подключен к вторым входам элементов И четвертой группы, единичные выходы первого и второго регистров соединены соответственно с входами первого и второго элементов ИЛИ-НЕ, выходы которых подключены соответственно к первому и второму входам третьего элемента ИЛИ, выход которого соединен с первым входом элемента И, выход которого подключен к нулевому входу триггера, тактовый вход устройства соединен с третьими входами элементов И третьей и четвертой групп и через элемент задержки с первыми прямыми входами первого и второго элементов запрета и с вторым входом элемента И.

Сравнение с прототипом показывает, что предлагаемое устройство отличаетЪя применением элемента запрета, двух элементов ИЛ И-НЕ, элемента задержки, эле- мента ИЛИ и их связей с другими элементами схемы устройства.

Использование указанных элементов .и их связей в устройстве обеспечивает проявление новых свойств, заключающихся в одновременном поиске запроса и свободного канала.

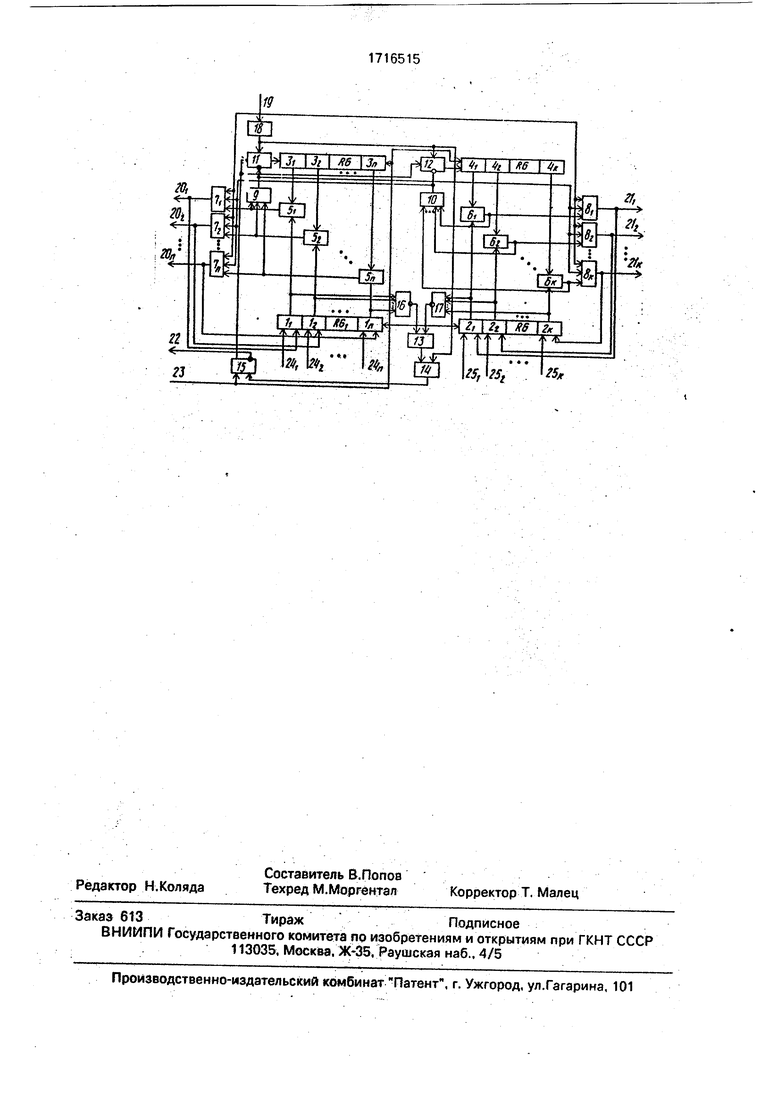

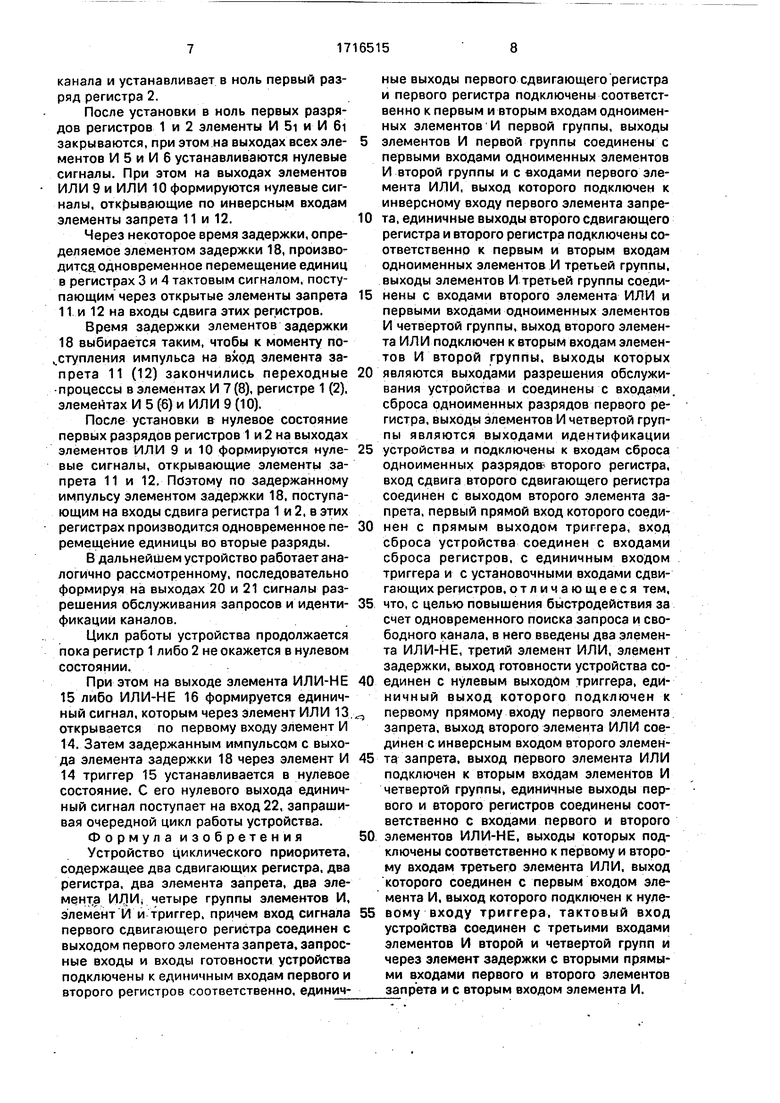

На чертеже приведена структурная схема устройства.

Устройство содержит регистры 1i-1n и 2г-2к, сдвигающие регистры 3i-3n и 4i-4K, группы 5.i-5n, б1-6к, 71-7п и 8i-8K элементов И, элементы ИЛИ 9, 10. элементы запрета

11, 12, элемент ИЛИ 13. элемент И 14, триггер 15, элементы ИЛИ-НЕ 16, 17, элемент задержки 18, тактовый вход 19 устройства, выходы 20i-20n разрешения обслуживания устройства, выходы 211-21к идентификации каналов устройства, выход 22 готовности устройства, вход 23 пуска устройства, запросные входы 24i-24n устройства и входы 25-|-25к готовности каналов устройства. 0 Устройство работает следующим образом.

Исходное состояние устройства характеризуется тем, что регистры 1-4 и триггер 15 установлены в состояние О (на чертеже 5 не показано).

Единичный сигнал с нулевого выхода триггера 15 поступает на вход 22 в качестве сигнала готовности устройства.

Работа устройства состоит из циклов, 0 каждый из которых начинается по сигналу запуска, поступающего на вход 23.t

По этому сигналу триггер 15 устанавливается в единичное состояние, регистры 1 и 2 - в нулевое, первые разряды регистров 3 5 и 4 - в единичное, а остальные разряды этих регистров - в нулевые состояния.

Затем по входам 24 и 25 соответственно . в регистры 1 и 2 поступают сигналы запросов и готовности каналов для распределе- 0 ния в данном цикле. После этого разрешается подача тактовых импульсов по входу 19.

После установки триггера 15 в единичное состояние единичным сигналом с его 5 единичного выхода открываются элементы запрета 11 и 12 по вторым прямым входам. Пусть все разряды регистров 1 и 2 установлены в единичное состояние,v Ввиду того, что первые разряды регист- 0 ров 3 и 4 находятся в единичных состояниях, на выходах первых элементов И 5 и И б формируются единичные сигналы. Единичным сигналом с выхода первого элемента И

5открыты первый элемент И 7 по первому 5 входу и через элемент ИЛИ 9 все элементы

И 8, а по инверсному входу закрыт элемент запрета 11. Аналогичным образом, единичным сигналом с выхода первого элемента И

6открыты первый элемент И 8 и через эле- 0 мент ИЛИ 10 все элементы И 7 и закрыт по

инверсному входу элемент запрета 12.

Так как элементы запрета 11 и 12 закрыты, то первый тактовый импульс поступает на первый выход 20i через элемент И 7i в 5 качестве сигнала разрешения обслуживания первого запроса и устанавливает в ноль первый разряд регистра 1.

Одновременно этот же импульс проходит через элемент И 8 на выход 211 в качестве сигнала идентификации первого

канала и устанавливает в ноль первый разряд регистра 2.

После установки в ноль первых разрядов регистров 1 и 2 элементы И 5i и И 6i закрываются, при этом на выходах всех элементов И 5 и И 6 устанавливаются нулевые сигналы. При этом на выходах элементов ИЛИ 9 и ИЛИ 10 формируются нулевые сигналы, открывающие по инверсным входам элементы запрета 11 и 12.

Через некоторое время задержки, определяемое элементом задержки 18, производится, одновременное перемещение единиц в регистрах 3 и 4 тактовым сигналом, поступающим через открытые элементы запрета 11 и 12 на входы сдвига этих регистров.

Время задержки элементов задержки 18 выбирается таким, чтобы к моменту по- ступления импульса на вход элемента запрета 11 (12) закончились переходные -процессы в элементах И 7(8), регистре 1 (2), элементах И 5 (6) и ИЛ И 9 (10).

После установки в нулевое состояние первых разрядов регистров 1 и 2 на выходах элементов ИЛИ 9 и 10 формируются нулевые сигналы, открывающие элементы запрета 11 и 12. Поэтому по задержанному импульсу элементом задержки 18, поступающим на входы сдвига регистра 1 и 2, в этих регистрах производится одновременное перемещение единицы во вторые разряды.

В дальнейшем устройство работает аналогично рассмотренному, последовательно формируя на выходах 20 и 21 сигналы разрешения обслуживания запросов и идентификации каналов.

Цикл работы устройства продолжается пока регистр 1 либо 2 не окажется в нулевом состоянии.

При этом на выходе элемента ИЛИ-НЕ 15 либо ИЛИ-НЕ 16 формируется единичный сигнал, которым через элемент ИЛИ 13. открывается по первому входу элемент И 14. Затем задержанным импульсом с выхода элемента задержки 18 через элемент И 14 триггер 15 устанавливается в нулевое состояние. С его нулевого выхода единичный сигнал поступает на вход 22, запрашивая очередной цикл работы устройства.

Формула изобретения

Устройство циклического приоритета, содержащее два сдвигающих регистра, два регистра, два элемента запрета, два эле- ментд И/1И( четыре группы элементов И, элемент И и триггер, причем вход сигнала первого сдвигающего регистра соединен с выходом первого элемента запрета, запросные входы и входы готовности устройства подключены к единичным входам первого и второго регистров соответственно, единичные выходы первого сдвигающего регистра и первого регистра подключены соответственно к первым и вторым входам одноименных элементов И первой группы, выходы

5 элементов И первой группы соединены с первыми входами одноименных элементов И второй группы и с входами первого элемента ИЛИ, выход которого подключен к инверсному входу первого элемента запре0 та, единичные выходы второго сдвигающего регистра и второго регистра подключены соответственно к первым и вторым входам одноименных элементов И третьей группы, выходы элементов И третьей группы соеди5 нены с входами второго элемента ИЛИ и первыми входами одноименных элементов И четвертой группы, выход второго элемента ИЛ И подключен к вторым входам элементов И второй группы, выходы которых

0 являются выходами разрешения обслуживания устройства и соединены с входами, сброса одноименных разрядов первого регистра, выходы элементов И четвертой группы являются выходами идентификации

5 устройства и подключены к входам сброса одноименных разрядов второго регистра, вход сдвига второго сдвигающего регистра соединен с выходом второго элемента запрета, первый прямой вход которого соеди0 нен с прямым выходом триггера, вход сброса устройства соединен с входами сброса регистров, с единичным входом триггера и с установочными входами сдвигающих регистров,отличающееся тем,

5 что, с целью повышения быстродействия за счет одновременного поиска запроса и свободного канала, в него введены два элемента ИЛИ-НЕ, третий элемент ИЛИ, элемент задержки, выход готовности устройства со0 единен с нулевым выходом триггера, единичный выход которого подключен к

первому прямому входу первого элемента запрета, выход второго элемента ИЛИ соединен с инверсным входом второго элемен5 та запрета, выход первого элемента ИЛИ подключен к вторым входам элементов И четвертой группы, единичные выходы первого и второго регистров соединены соответственно с входами первого и второго

0 элементов ИЛИ-НЕ, выходы которых подключены соответственно к первому и второму входам третьего элемента ИЛИ, выход которого соединен с первым входом элемента И, выход которого подключен к нуле5 вому входу триггера, тактовый вход устройства соединен с третьими входами элементов И второй и четвертой групп и через элемент задержки с вторыми прямыми входами первого и второго элементов запрета и с вторым входом элемента И.

К

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство циклического приоритета | 1990 |

|

SU1716516A1 |

| Устройство циклического приоритета | 1987 |

|

SU1418713A1 |

| Устройство для распределения заявок по процессорам | 1990 |

|

SU1798782A1 |

| Устройство циклического приоритета | 1990 |

|

SU1805468A1 |

| Устройство приоритета | 1990 |

|

SU1737449A1 |

| Устройство для распределения заявок по процессорам | 1989 |

|

SU1695302A1 |

| Устройство для организации доступа к ресурсам | 1988 |

|

SU1608663A1 |

| Устройство циклического приоритета | 1988 |

|

SU1543405A1 |

| Многоканальное устройство приоритета для распределения заявок по процессорам | 1985 |

|

SU1327105A1 |

| Многоканальное устройство для организации доступа к ресурсам | 1986 |

|

SU1322284A1 |

Изобретение относится к вычислительной технике и может быть использовано в вычислительных системах, ориентированных на обработку запросов с циклической дисциплиной обслуживания. Цель изобретения - повышение быстродействия за счет одновременного поиска запроса и свобод2 ного канала. Новым в устройстве является использование двух элементов ИЛИ-НЕ 16, 17,элемента ИЛИ 13 и элемента задержки 18.Устройство обеспечивает в каждом цикле работы выбор запроса и свободного канала для его обслуживания посредством регистров сдвига. Формирование сигналов разрешения обслуживания и идентификации каналов производится на основе совпадения единичных сигналов в одноименных разрядах соответствующих сдвигающих регистров и регистров запросов и каналов. Поиск запросов и каналов производится путем одновременного сдвига единицы в сдвигающих регистрах. При этом, если не найдены запрос и свободный канал одновременно, продолжается поиск либо запро са, либо свободного канала. 1 ил. fe

| Устройство циклического приоритета | 1983 |

|

SU1126960A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство циклического приоритета | 1987 |

|

SU1418713A1 |

Авторы

Даты

1992-02-28—Публикация

1990-01-11—Подача