Изобретение относится к вычислительной технике и может быть использовано в вычислительных системах.

Известно устройство циклического приоритета, содержащее четыре регистра, четыре группы элементов И, элементы ИЛИ, элемент запрета, кольцевой сдвигающий регистр, триггер, группу элементов задержки и формирователь импульсов.

Недостаток устройства - узкая область применения.

Наиболее близким к предлагаемому является устройство приоритета, содержащее пять регистров, три группы элементов И, два блока элементов И, четыре элемента ИЛИ, элемент запрета, регистр сдвига, два блока элементов ИЛИ, триггер, три элемента И, схему сравнения, два элемента задержки, формирователь импульсов и элемент НЕ.

Недостатком данного устройства является узкая область применения, так как при

слабой интенсивности поступления запросов возможны случаи, когда в момент окончания обслуживания данного абонента очередной запрос в первом регистре не найден. В этих случаях код приоритета обслуженной заявки остается во втором регистре Поэтому при поступлении очередной заявки с меньшим приоритетом при свободном канале обслуживания данная заявка к обслуживанию не принимается. В устройстве ведется просмотр поступивших заявок до тех пор, пока не будет обнаружена заявка с приоритетом, большим чем у последней обслуженной заявки,

Цель изобретения - повышение производительности работы устройства.

Поставленная цель достигается тем, что в устройство приоритета, содержащее пять регистров, три группы элементов И, два блока элементов И, четыре элемента ИЛИ, элемент НЕ, элемент запрета, первый-третий элементы И, два блока элементов ИЛИ, фор(Л

С

Ч

ы

xj

мирователь импульсов, первый и второй элементы задержки, схему сравнения и первый триггер, причем запросные входы и входы окончания обслуживания устройства подключены соответственно к единичным и нулевым входам первого регистра, единичные выходы которого соединены с группой информационных входов первого блока элементов И, выходы которого соединены с единичными входами второго регистра, единичный выход каждого разряда которого соединен с первым входом одноименного элемента И первой группы, второй вход которого соединен с одноименным выходом регистра сдвига, выходы элементов И пер- вой группы соединены с входами первого элемента ИЛИ и информационными входами второго блока элементов И, выходы которого соединены с единичными входами третьего регистра, единичные выходы кото- рого соединены с выходами устройства, единичный выход каждого разряда третьего регистра и выход каждого элемента И первой группы соединен с управляющим входом одноименной подгруппы элементов И соответственно третьей и четвертой групп, информационные выходы которых подключены к выходам одноименной группы разрядов четвертого регистра, а входы которого соединены с входами кодов при- оритета устройства, выход первого элемента ИЛИ соединен с входом элемента НЕ, первым входом первого элемента И и инверсным входом элемента запрета, прямой вход которого соединен с такто- вым входом устройства, а выход соединен с управляющим входом первого блока элементов И и. управляющим входом регистра сдвига, сбросовый вход устройства соединен с первым входом второго элемента И, второй вход которого соединен с выходом элемента НЕ, а выход - с первым входом второго элемента ИЛИ, выход которого соединен с управляющим входом второго блока элементов И, выходы элементов И, второй и третьей групп соединены с входами соответственно первого и второго блоков элементов ИЛИ, выходы которых соединены соответственно с информационными входами пятого регистра и первой группы информационных входов схемы сравнения, вторая группа информационных входов которой соединена с выходами пятого регистра, выход формирователя импульсов через пятый элемент задержки соединен с опросным входом схемы сравне-1 ния, выходы Равно, Больше и Меньше которой соединены с первыми входами соответственно третьего элемента И, третьего и четвертого элементов ИЛИ, выходы разрешения и запрещения прерывания устройства соединены соответственно с единичным и нулевым входами первого триггера, единичный выход которого соединен с вторым входом третьего элемента И, выход которого соединен с вторым входом третьего элемента ИЛИ, выход которого соединен с входом второго элемента задержки и вторым входом второго элемента ИЛИ, третий вход которого соединен с выходом первого элемента И, выход второго элемента задержки соединен с вторым входом четвертого элемента ИЛИ, выход которого соединен с входом сброса второго регистра, введены второй- триггер, четвертый элемент И, третий и четвертый элементы задержки, причем сбросовый вход устройства соединен с единичным входом второго триггера, единичный и нулевой выходы которого соедине- ны соответственно с вторым входом первого элемента И и первым входом четвертого элемента ИЛИ, а выход с входом формирователя импульсов, выход первого элемента И соединен с входом третьего элемента задержки, выход которого соединен с вторым входом четвертого элемента ИЛИ и входом четвертого элемента задержки, выход которого соединен с нулевым входом второго триггера1.

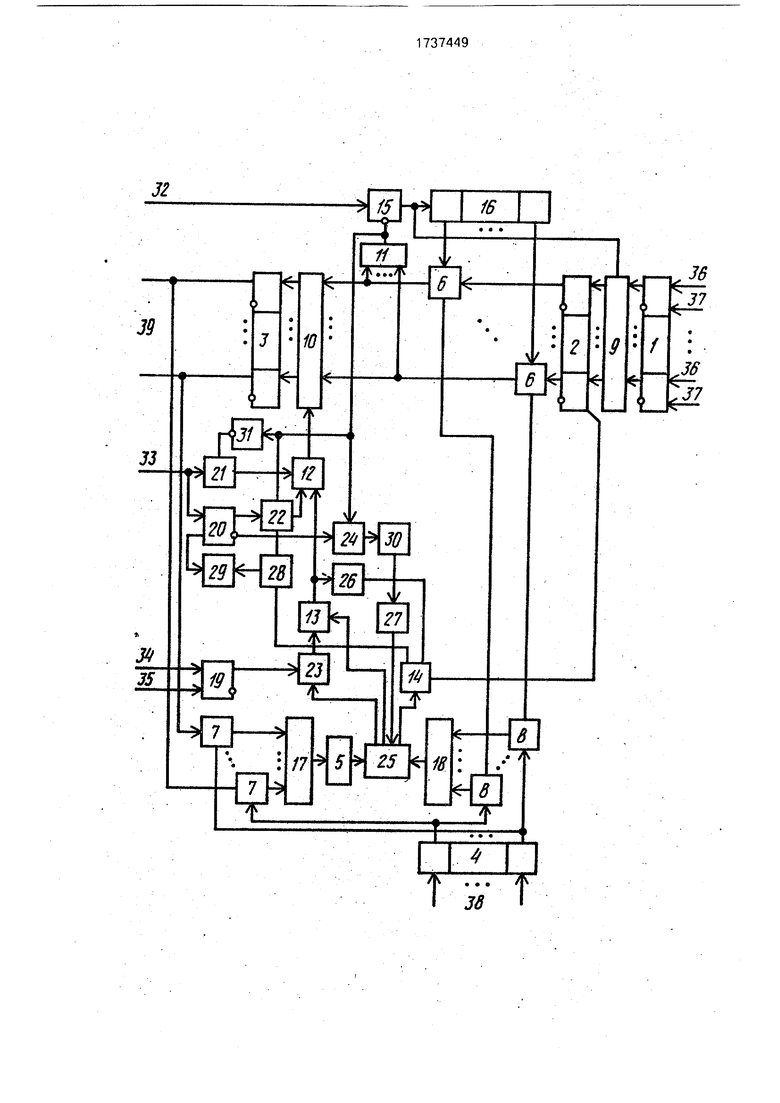

На чертеже приведена схема предлагаемого устройства приоритета.

Устройство содержит регистры 1-5, группы 6-8 элементов И, блоки 9 и 10 элементов И, элементы ИЛИ 11-14, элемент 15 запрета, регистр 16 сдвига, блоки ИЛИ 17 и 18, триггеры 19 и 20, элементы И 21-24, схему 25 сравнения, элементы 26-29 задержки, формирователь 30 импульсов, элемент НЕ 31, тактовый вход 32, сбросовый вход 33, входы 34 и 35 разрешения и запрещения прерывания соответственно, запросные входы 36, входы 37 окончания обслуживания, входы 38 приоритета и выходы 39.

В качестве схемы 25 сравнения используется обычное устройство для сравнения двоичных чисел.

Устройство работает следующим образом.

При включении питания регистры 1-3 обнуляются, в соответствующие группы разрядов регистра 4 по входам 38 заносятся коды приоритетов абонентов (более высокому приоритету соответствует меньший код), один из разрядов регистра 16 устанавливается в единичное состояние, а остальные разряды регистра 1 б - в нулевое. Цепи на- чальной установки схемы на чертеже не по- казаны. Триггер 19 в зависимости от разрешения либо запрещенияЧферывания для абонентов с одинаковыми кодами приоритетов устанавливаются в единичное либо нулевое состояние по соответствующим входам 34 и 35. Триггер 20 по входу 33 устанавливается в единичное состояние, что соответствует свободному каналу обслуживания,

После этого на вход 32 начинают поступать тактовые импульсы. Они проходят через открытый нулевым уровнем с выхода элемента ИЛИ 11 элемент 15 запрета и осуществляют сдвиг единицы в регистре 16 по кольцу. Запросы от абонентов поступают на входы 36 и записываются в соответствующие разряды регистра 1, а после поступле- ния очередного тактового импульса на вход блока 9 элементов И переписываются в соответствующие разряды регистра 2.

Если в данный момент присутствуют единицы в разрядах регистров 2 и 16, то на выходе соответствующего элемента И 6 появляется единичный уровень. Срабатывает элемент ИЛИ 11, вследствие чего закрывается элемент 15 запрета, временно прекращая сдвиг содержимого регистра 16. Если при этом триггер 20 установлен в единичное состояние (после начальной установки в последующем), то срабатывает элемент И 22, с выхода которого сигнал через элемент И 12 поступает на управляющий вход блока 10 элементов И, в результате срабатывания которого в соответствующий разряд регистра 3 записывается единица. На выходе 39 появляется сигнал, разрешающий установление связи абонента с обслу- живающим устройством (общим ресурсом). Начинается обслуживание. Единичный уровень с выхода регистра 3 проходит на вход соответствующей группы 7 элементов И, осуществляя запись кода приоритета при- пятого на обслуживание абонента из соответствующей группы разрядов регистра 4 через блок 17 элементов ИЛИ в регистр 5. Через время, необходимое для записи информации в регистр 3, срабатывает соеди- ненный с выходом элемента И 22 элемент 28 задержки, сигнал с выхода которого проходит через элемент ИЛИ 14 и обнуляет регистр 2. Это приводит к снятию единичного потенциала с выхода элемента И 6, эле- мента ИЛИ 11 и открыванию элемента 15 запрета. Вновь начинается сдвиг единицы в регистре 16 и осуществляется поиск следующего запроса на обслуживание. Первым же очередным тактовым импульсом произ- водится сдвиг содержимого регистра 16 и осуществляется поиск следующего запроса на обслуживание. Первым же очередным тактовым импульсом производится сдвиг содержимого регистра 16 и перепись информации из регистра 1 в регистр 2 (частота

тактовых импульсов и временные задержки срабатывания элементов И блока 9 и триггеров регистр 2 должен быть выбраны таким образом, чтобы перезапись информации из регистра 1 в регистр 2 производилась после сдвига содержимого регистра 16). Через время, необходимое для снятия высокого потенциала с выхода элемента ИЛИ 11, срабатывает соединенный с выходом элемента 28 задержки элемент 29 задержки, в результате чего триггер 20 устанавливается в нулевое состояние. Если в момент срабатывания элемента И 6 триггер 20 находится в нулевом состоянии (обслуживающее устройство занято), то срабатывает элемент И 24, высокий уровень с выхода которого поступает на вход формирователя 30 импульсов сигнал, с выхода которого подается на вход элемента 27 задержки. Через время, необходимое на поступление кода приоритета найденного в регистре запроса (В) из соответствующей группы разрядов регистра 4 через группу элементов И 8 и группу элементов ИЛИ 18 на входы схемы 25 сравнения, а также выполнения сравнения этого кода с хранящимися в регистре 5 кодом (А), срабатывает элемент 27 задержки. В результате опроса схемы 25 сравнения на одном из ее выходов появляется сигнал. Возможны три случая: А В, А В и А В.

Если А В, то срабатывает элемент ИЛИ 13, с выхода которого сигнал поступает на вход элемента ИЛИ 12. После этого срабатывает элемент 26 задержки, с выхода которого сигнал поступает на вход элемента ИЛИ 14. В результате произойдет прерывание обслуживаемого запроса.

Если А В, найденный запрос игнорируется, так как его приоритет ниже приоритета обслуживаемого в данный момент абонента. Срабатывание элемента ИЛИ 14 приводит к сбросу регистра 2 и продолжению опроса. Поскольку данный запрос не обслужен , то после очередного сдвига в регистре 16 он (наряду с другими запросами) вновь переписывается в из регистра 1 в регистр 2,

Если А В в зависимости от состояния триггера 19 производится либо прерывание текущего обслуживания (срабатывает элемент И 23, элемент ИЛИ 13 и т.д.), либо устройство переводится в состояние ожидания окончания обслуживания.

Если обслуживание завершается до того, как найден очередной запрос, на вход 33 подается сигнал, по которому триггер 20 устанавливается в единичное состояние, а также срабатывает элемент И 21, с выхода которого сигнал проходит через элемент

ИЛИ 12 на управляющий вход блока 10 элементов И, обнуляя регистр 3. Кроме того, производится установка в нулевое состояние соответствующего триггера регистра 1 по входу 37.

Если обслуживание завершается в момент , когда устройство находится в состоянии ожидания, по сигналу на входе 33 триггер 20 устанавливается в единичное состояние, в результате чего срабатывает элемент И 22, сигналом с выхода которого производятся описанные действия.

В дальнейшем устройство работает аналогично.

Формула изобретения Устройство приоритета, содержащее регистр сдвига, пять регистров, три группы элементов И, два блока элементов И, четыре элемента ИЛИ, элемент НЕ, элемент запрета, три элемента И, два блока элементов ИЛИ, формирователь импульсов, два элемента задержки, схему сравнения и первый триггер, причем запросные входы и входы окончания обслуживания устройства подключены соответственно к единичным и нулевым входам разрядов первого регистра, единичные выходы разрядов которого соединены с группой информационных входов первого блока элементов И, выходы которого соединены с единичными входами разрядов второго регистра, единичный выход каждого разряда которого соединен с первым входом одноименного элемента И первой группы, второй вход которого соединен с одноименным выходом регистра сдвига, выходы элементов И первой группы соединены с входами первого элемента ИЛИ и информационными входами второго блока элементов И, выходы которого соединены с единичными входами разрядов третьего регистра, единичные выходы разрядов которого соединены с выходами устройства, единичный выход каждого разряда третьего регистра и выход каждого элемента И первой группы соединены с первыми входами одноименных элементов И соответственно второй и третьей групп, вторые входы которых подключены к выходам одноименных разрядов четвертого регистра, единичные входы которых соединены с входами кодов приоритета устройства, выход первого элемента ИЛИ соединен с входом элемента НЕ, первым входом первого элемента И и инверсным входом элемента запрета, прямой вход которого соединен с тактовым входом

устройства, а вход - с управляющими входами первого блока элементов И и регистра сдвига, сбросовый вход устройства соединен с первым входом второго элемента И,

второй вход которого соединен с выходом элемента НЕ, а выход - с первым входом второго элемента ИЛИ, выход которого соединен с управляющим входом второго блока элементов И, выходы элементов И второй и

третьей групп соединены с входами соответственно первого и второго блоков элементов ИЛИ, выходы которых соединены соответственно с информационными входами пятого регистра и первой группы информационных входов схемы сравнения, вторая группа информационных входов которой соединена с выходами пятого регистра, выход формирователя импульсов через первый элемент задержки соединен с опросным

входом схемы сравнения, выходы Равно, Больше и Меньше которой соединены с первыми входами соответственно третьего элемента И, третьего и четвертого элементов ИЛИ, входы разрешения и запрещения

прерывания устройства соединены соответственно с единичным и нулевым входами первого триггера, единичный выход которого соединен с вторым входом третьего элемента И, выход которого соединен с вторым

входом третьего элемента ИЛИ, выход которого соединен с входом второго элемента задержки и вторым входом второго элемента ИЛИ, третий вход которого соединен с выходом первого элемента И, выход второго

элемента задержки соединен с вторым входом четвертого элемента ИЛИ, выход которого соединен с входом сброса второго регистра, отличающееся тем, что, с целью повышения производительности устройства, в него введены второй триггер, четвертый элемент И, третий и четвертый элементы задержки, причем сбросовый вход устройства соединен с единичным входом второго триггера, единичный и нулевой выходы которого соединены соответственно с вторым входом первого элемента И и первым входом четвертого элемента И, второй вход которого соединен с выходом первого элемента ИЛИ, а выход - с входом

формирователя импульсов, выход первого элемента И соединен с входом третьего элемента задержки, выход которого соединен с вторым входом четвертого элемента ИЛИ и входом четвертого элемента задержки, выход которого соединен с нулевым входом второго триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство приоритета | 1989 |

|

SU1633404A1 |

| Устройство циклического приоритета | 1990 |

|

SU1805468A1 |

| Устройство циклического приоритета | 1988 |

|

SU1543405A1 |

| Устройство циклического приоритета | 1990 |

|

SU1716515A1 |

| Устройство для управления очередностью обслуживания | 1987 |

|

SU1481765A2 |

| Устройство для обслуживания запросов | 1983 |

|

SU1124306A1 |

| Устройство для моделирования систем массового обслуживания | 1988 |

|

SU1532943A1 |

| Устройство для моделирования систем массового обслуживания | 1982 |

|

SU1067508A1 |

| Устройство для сопряжения абонентов с электронной вычислительной машиной | 1983 |

|

SU1132283A1 |

| Устройство для организации доступа к ресурсам | 1988 |

|

SU1608663A1 |

Изобретение относится к вычислительной технике и может быть использовано в вычислительных системах. Цель, изобретении - расширение области применения за счет обеспечения возможности организации обслуживания запросов при невысокой интенсивности их прихода. Устройство содержит пять регистров, три группы элементов И, два блока элементов И. четыре элемента ИЛИ, элемент запрета, регистр сдвига, два блока элементов ИЛИ, два триггера, четыре элемента И, схему сравнения, четыре элемента задержки, формирователь импульсов и элемент НЕ. Цикл работы устройства состоит в периодическом просмотре заявок и приеме их к обслуживанию в соответствии с приписанными им кодами приоритетов, 1 ил.

| Авторское свидетельство СССР № 4417232, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Запоминающее устройство | 1975 |

|

SU613404A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сравнения двух -разрядных двоичных чисел | 1976 |

|

SU652557A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-05-30—Публикация

1990-07-02—Подача