Изобретение относится к вычислительной технике и может быть использовано в многопроцессорных вычислительных системах при обнаружении потока заявок.

Цель изобретения - повышение быстродействия устройства за счет одновременного анализа состояния каналов.

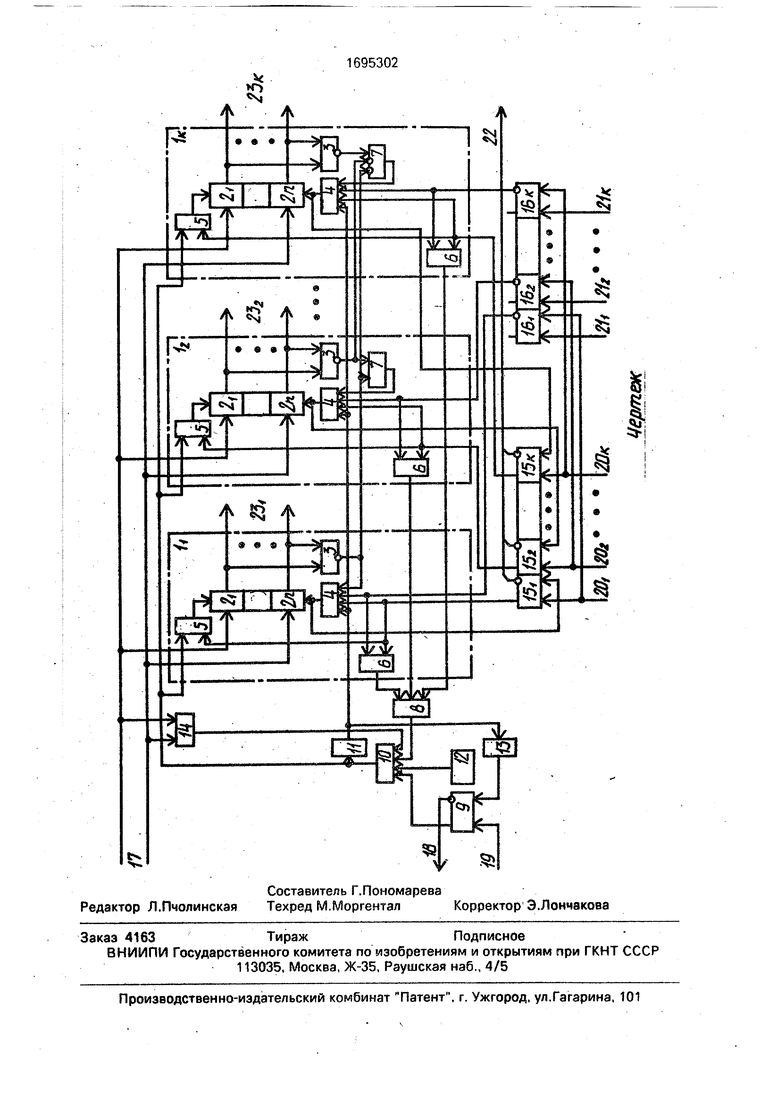

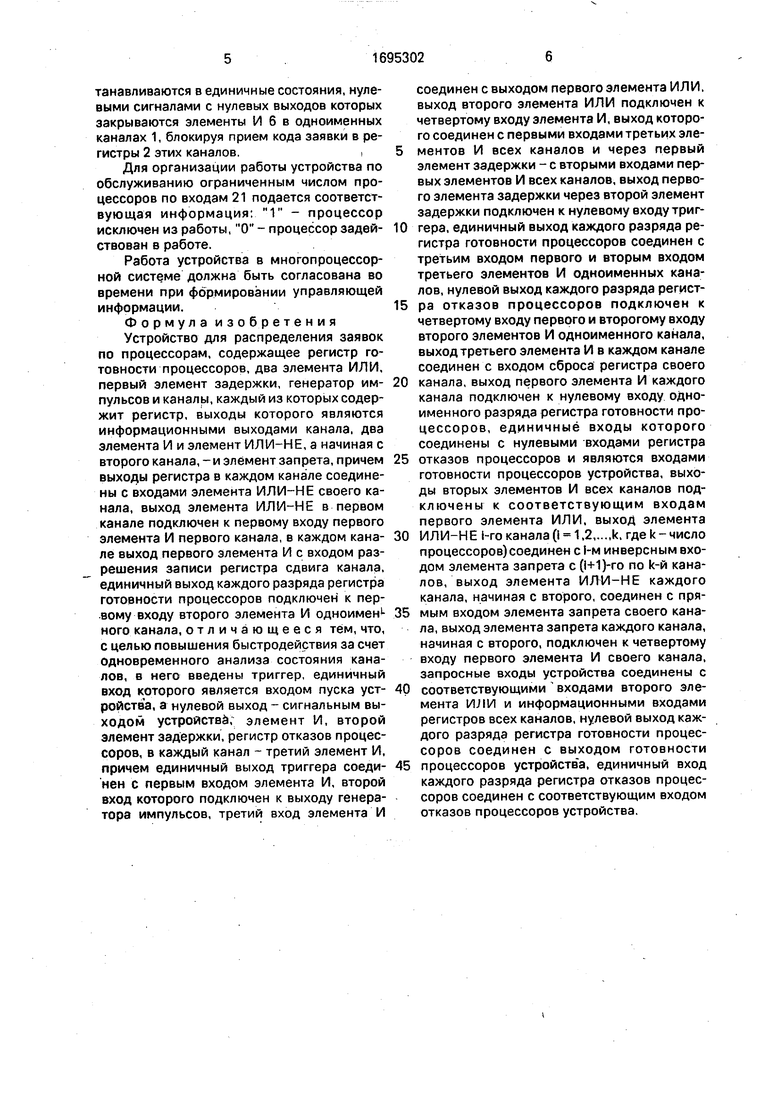

На чертеже приведена структурная схема устройства.

Устройство содержит каналы 1, каждый из которых состоит из регистра 2, элемента ИЛИ-НЕ 3 и элементов И 4-6. Каналы 1 начиная со второго, кроме того, содержат элемент 7 запрета, элемент ИЛИ 8, триггер 9, элемент И 10, элемент 11 задержки, генератор 12 импульсов, элемент 13 задержки, элемент ИЛИ 14. регистр 15 готовности процессоров, регистр 16 отказов процессоров, информационные входы 17, сигнальный выход 18, вход 19 пуска входы 20 сигналов готовности процессоров, входы 21 сигналов отказов процессоров, выходы 22 сигналов готовности и информационные выходы 23.

Исходное состояние устройства характеризуется тем, что регистры 2 каналов 1 и триггер 9 установлены в состояние О (на чертеже не показано).

Устройство обеспечивает передачу кода заявки, поступающего по входам 17, свободному и исправному процессору по схеме запрос - ответ, исключающий потерю информации.

О Ч)

ся

00

о

N3

Каждый процессор принимает код заявки по выходам 23 из регистра 2 соответствующего канала 1.

В этих регистрах фиксируется код заявки, когда от соответствующего процессора не поступает сигнал отказа и он готов к обслуживанию очередной заявки. Сигналы (готовности и отказа поступают в устройство (по входам 20 и 21 и принимаются в соответствующие одноименные разряды регистра 15 готовности процессоров и регистра 16 (отказа процессоров.

Рассмотрим работу устройства, когда все процессоры вычислительной системы (исправны.

В этом случае от всех процессоров по соответствующим входам 20 поступают импульсные сигналы. При этом разряды реги- (стра 15 устанавливаются в единичные состояния, а одноименные разряды регистра 16 - в нулевые. На выходах элементов И

6всех каналов 1 формируются единичные сигналы, поступающие на входы элемента ИЛИ 8, единичным сигналом с выхода которого элемент И 10 открыт по второму входу.

В качестве сигнала запроса устройством кода заявки используется единичный сигнал с нулевого выхода триггера 9, поступающий на вход 18.

По этому сигналу на входах 17 производится смена потенциального кода заявки, а по входу 19 - подача импульса пуска.

Этим сигналом триггер 9 устанвливает- ся в единичное состояние, открывая элемент И 10 по четвертому входу, Единичным Сигналом с выхода элемента ИЛИ 14 элемента И 10 открыт по второму входу. Поэтому импульсом генератора 12, проходящим йерез элемент И 10 и открытые единичными сигналами по первым входам с единичных выходов разрядов регистра 15 элементы И Б во всех каналах, устанавливаются в нуле- Вое состояние регистры 2 всех каналов 1. При этом на выходах элементов ИЛИ-НЕ 3 В каждом канале формируется единичный сигнал. Эти сигналы подаются на элементы

7запрета каждого последующего канала, Обеспечивая выбор приоритетного на данный момент свободного канала.

Так, единичным сигналом с выхода элемента ИЛИ-НЕ 3 первого канала блокируется прохождение единичных сигналов с выходов элементов ИЛИ-НЕ 3 всех последующих каналов 1 через соответствующие элементы запрета 7 по их инверсным входам. Поэтому элемент И 4 открыт только в первом канале, где задержанным импульсом элементом 11 задержки, проходящим йа синхровход регистра 2 первого канала, обеспечивается прием кода заявки в этот

регистр. Одновременно этим же импульсом устанавливается в О первый разряд регистра 15. Единичный сигнал с нулевого выхода этого разряда поступает на соответствующий

выход 22 устройства и используется в одноименном процессоре в качестве сигнала ответа, разрешающего считывание кода с выхода 23 своего канала.

Время задержки элемента 11 задержки

0 определяется временем переходных процессоров в элементе И 5, регистре 2 и элементе ИЛИ-НЕ 3. После приема кода заявки в регистр 2 первого канала на выходе элемента ИЛИ-НЕ 3 формируется нулевой сиг5 нал, открывающий по первым инверсным входам элементы 7 запрета во всех последующих каналах 1.

Дополнительно задержанным импульсом элементом задержки 13 устанавливает0 ся в О триггер 9, единичный сигнал с нулевого выхода которого поступает на выход 18 и используется в качестве сигнала готовности устройства к очередному циклу распределения заявки.

5 Время задержки элемента 13 задержки определяется временем переходных процессоров в элементе И 4, регистре 15, элементах И 6 и ИЛИ 8. На входах 17 производится смена потенциального кода очередной заяв0 ки с одновременной подачей сигнала пуска по входу 19.

Работа устройства происходит аналогично рассмотренному выше с записью кода заявки в регистр 2 второго канала.

5 Процесс приема k заявок в регистры 2 заканчивается приемом в регистр 2 k-ro канала 1. При этом регистр 15 оказывается в нулевом состоянии, что приводит к закрытию элементов И 6 во всех канавках 1 и

0 появлению нулевого сигнала на выходе элемента ИЛИ 8, закрывающего элемент И 10. Следующий, (к+1)-й цикл, начинается обычным порядком, но так как элемент И 10 закрыт, импульсы генератора 12 не воздей5 ствуют на элементы схемы устройства.

Цикл распределения (k-Hj-й заявки начинается по приходу по входам 20 сигналов готовности процессоров. Установка разрядов регистра 15 приводит к открыванию эле0 ментов И 5 и 6 в соответствующих каналах, а затем и элемента И 10. Импульсом генератора 12с выхода элемента И 10 устанавливаются в О регистры 2 свободных каналов, а заявка с входов 17 принимается в регистр

5 2 приоритетного на данный момент времени канала.

В случае, когда один или несколько процессоров неисправны, по входам 21 поступают импульсные сигналы отказов и соответствующие разряды регистров 16 устанавливаются в единичные состояния, нулевыми сигналами с нулевых выходов которых закрываются элементы И б в одноименных каналах 1, блокируя прием кода заявки в регистры 2 этих каналов.,

Для организации работы устройства по обслуживанию ограниченным числом процессоров по входам 21 подается соответствующая информация: 1 - процессор исключен из работы, О - процессор задействован в работе.

Работа устройства в многопроцессорной системе должна быть согласована во времени при формировании управляющей информации.

Формула изобретения

Устройство для распределения заявок по процессорам, содержащее регистр готовности процессоров, два элемента ИЛИ, первый элемент задержки, генератор импульсов и каналы, каждый из которых содержит регистр, выходы которого являются информационными выходами канала, два элемента И и элемент ИЛИ-НЕ, а начиная с второго канала, - и элемент запрета, причем выходы регистра в каждом канале соединены с входами элемента ИЛИ-НЕ своего канала, выход элемента ИЛИ-НЕ в первом канале подключен к первому входу первого элемента И первого канала, в каждом канале выход первого элемента И с входом разрешения записи регистра сдвига канала, единичный выход каждого разряда регистра готовности процессоров подключен к первому входу второго элемента И одноимен1- ного канала, отличающееся тем, что, с целью повышения быстродействия за счет одновременного анализа состояния каналов, в него введены триггер, единичный вход которого является входом пуска устройства, а нулевой выход - сигнальным выходом устройства; элемент И, второй элемент задержки, регистр отказов процессоров, в каждый канал - третий элемент И, причем единичный выход триггера соединен с первым входом элемента И, второй вход которого подключен к выходу генератора импульсов, третий вход элемента И

соединен с выходом первого элемента ИЛИ. выход второго элемента ИЛИ подключен к четвертому входу элемента И, выход которого соединен с первыми входами третьих элементов И всех каналов и через первый элемент задержки - с вторыми входами первых элементов И всех каналов, выход первого элемента задержки через второй элемент задержки подключен к нулевому входу триггера, единичный выход каждого разряда регистра готовности процессоров соединен с третьим входом первого и вторым входом третьего элементов И одноименных каналов, нулевой выход каждого разряда регистра отказов процессоров подключен к четвертому входу первого и второгому входу второго элементов И одноименного канала, выход третьего элемента И в каждом канале соединен с входом сброса регистра своего

канала, выход первого элемента И каждого канала подключен к нулевому входу одноименного разряда регистра готовности процессоров, единичные входы которого соединены с нулевыми входами регистра

отказов процессоров и являются входами готовности процессоров устройства, выходы вторых элементов И всех каналов подключены к соответствующим входам первого элемента ИЛИ, выход элемента

ИЛИ-НЕ 1-го канала (1 1,2к, где к - число

процессоров) соединен с l-м инверсным входом элемента запрета с (i+1)-ro по к-й каналов, выход элемента ИЛИ-НЕ каждого канала, начиная с второго, соединен с прямым входом элемента запрета своего канала, выход элемента запрета каждого канала, начиная с второго, подключен к четвертому входу первого элемента И своего канала, запросные входы устройства соединены с

соответствующими входами второго элемента ИЛИ и информационными входами регистров всех каналов, нулевой выход каждого разряда регистра готовности процессоров соединен с выходом готовности

процессоров устройств а, единичный вход каждого разряда регистра отказов процессоров соединен с соответствующим входом отказов процессоров устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для распределения заявок по процессорам | 1990 |

|

SU1798782A1 |

| Устройство для распределения заявок по процессорам | 1987 |

|

SU1462314A1 |

| Устройство для распределения приоритетных заявок по процессорам | 1987 |

|

SU1495795A1 |

| Устройство для организации очереди | 1988 |

|

SU1575184A2 |

| Устройство для организации доступа к ресурсам | 1988 |

|

SU1608663A1 |

| Устройство для распределения заданий процессорам | 1985 |

|

SU1290324A1 |

| Устройство для диспетчеризации заявок | 1985 |

|

SU1247873A1 |

| Многоканальное устройство для организации доступа к ресурсам | 1986 |

|

SU1322284A1 |

| Многоканальное устройство приоритета для распределения заявок по процессорам | 1985 |

|

SU1327105A1 |

| Устройство для распределения задач между процессорами | 1989 |

|

SU1663611A1 |

Изобретение относится к вычислительной технике и может быть использовано в многопроцессорных вычислительных системах при обслуживании потока заявок. Цель изобретения - повышение быстродействия за счет одновременного анализа состояния каналов. Новым в устройстве является использование триггера, элемента И, элемента задержки, регистра отказов процессоров, а в каждом канале - элемента И. Устройство обеспечивает распределение заявок по процессорам с учетом их занятости либо исправности. При этом поиск свободного процессора производится на основе одновременного анализа состояния регистров кодов заявок каналов. Если свободно несколько каналов, т.е. процессоров, то передача кода заявки происходит в приоритетный по меньшему номеру канал. Взаимодействиеустройтсва в вычислительной системе организовано по схеме Запрос - ответ. В качестве сигнала запроса используется сигнал готовности устройства к приему заявки, а в качестве сигнала ответа - сигнал о размещении этого кода в регистре свободного канала. 1 ил. -5 Ј

| Многоканальное устройство для обслуживания запросов в порядке их поступления | 1981 |

|

SU966696A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Многоканальное устройство для обслуживания заявок в многопроцессорной системе | 1985 |

|

SU1291982A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-11-30—Публикация

1989-12-29—Подача