(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ АНАЛОГО1ВЫХ ПАРАМЕТРОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для контроля аналоговых параметров | 1977 |

|

SU739483A1 |

| Устройство для измерения линейной массыдВижущЕйСя СТЕКлОНиТи | 1979 |

|

SU842389A1 |

| Устройство для контроля аналоговых объектов | 1989 |

|

SU1718189A1 |

| Устройство для контроля радиоэлектронных объектов | 1990 |

|

SU1714622A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ | 1983 |

|

SU1840568A1 |

| Устройство для контроля объектов | 1975 |

|

SU572764A1 |

| АВТОМАТИЗИРОВАННОЕ УСТРОЙСТВО КОНТРОЛЯ И ДИАГНОСТИРОВАНИЯ РАДИОЭЛЕКТРОННЫХ ИЗДЕЛИЙ | 1998 |

|

RU2174699C2 |

| Устройство для контроля параметров | 1989 |

|

SU1667009A1 |

| Устройство для контроля качества ферромагнитных изделий | 1987 |

|

SU1499212A1 |

| Устройство для контроля схем цифровых вычислительных машин | 1978 |

|

SU734691A1 |

Иаофетение относится к области иэмерешш аналоговых параметров и может быть вспользсфано в системах автоматического контроля параметров.

Известно устройство, для контроля параметров, в котором измерение проводится последовательным их подключением коммутатор к измер 1телю 1.

При последовательиом контроле парамет ров сравнительно н ысокого б1 стродействия электромеханических коммутаторов значительное время, автрачива уюе при измерении комплекса параметров объек та контроля, приходится иа процесс коммутации, причем оно может быть существенно больше времени, затрачиваемого собст венно на измерение. При большом числе контролируемых параметров объекта и ог paшLчe:iнo 4 времени контроля необходимо сокращать суммарное время па раметров.

Сокршдение времени контр опя путем введения в состав а|1Ш}«фа:туры контроля нескольких измерителей проводит к аппаратурной нэбыточности1

Из известных устройств наиболее бпиэким по технической сущности является устройство, содержащее поспедоватеаьно соединенные переобразоватепь анапо1 -коа, блок сравнения, бпок вывода и блок памяти, выход подключен ко второму входу блока сравнения, н блок управления, выходы которого подключены соответственно к командным входам коммутатора, блоjca памяти, блока сравнения и блока вывода 2.

При последовательном контроле параметров после коммутации и преофазования в кодовую форму каждый контролируемый параметр сравнивается первоначально с номинальным значением, и далее результат вычитания сравнивается с полем допуска. Величины номинального значения и поля допуска считываются из блока памяти по соответствующим командам нз блока управлшгая-.

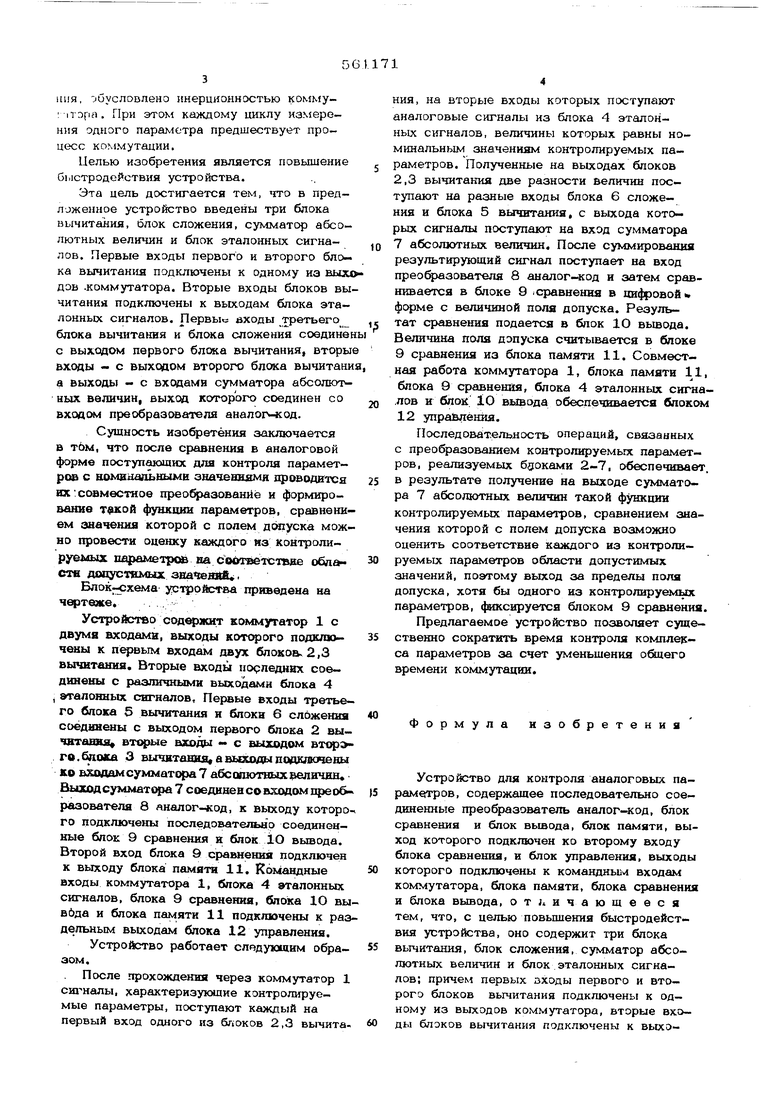

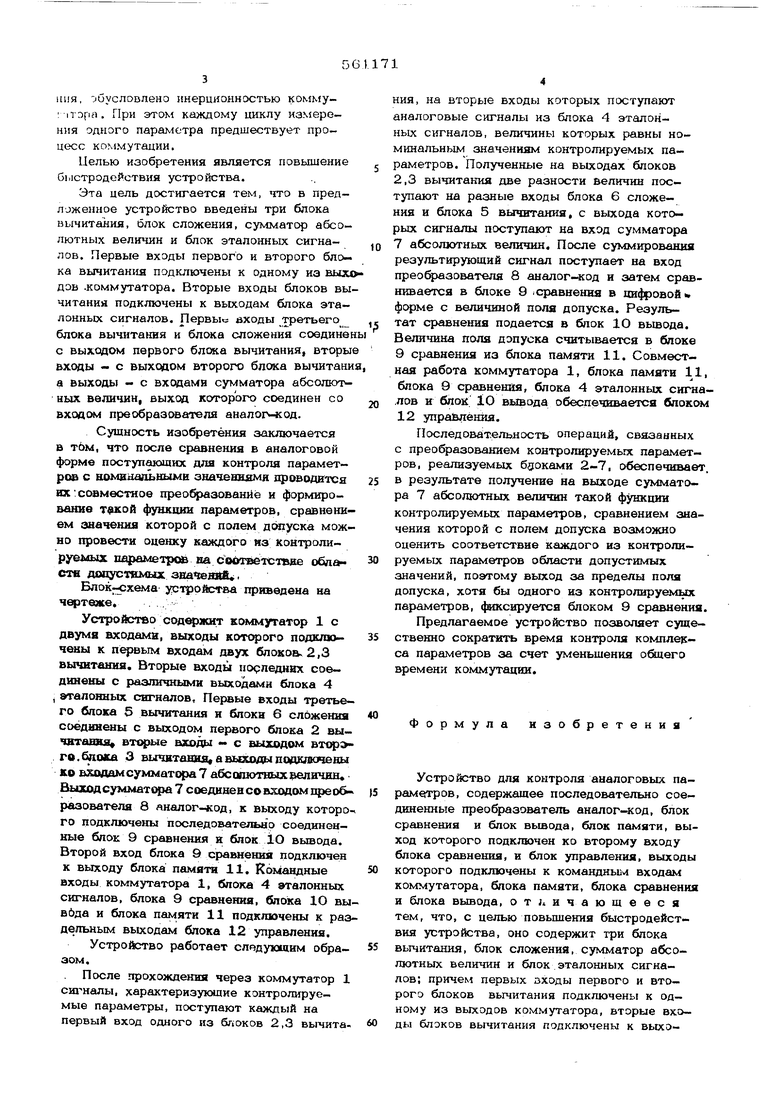

Большое о&цее время, затрач1тваемое на контроль комплекса параметров, по сравнению с суммарным временем, тре,буемым собственно для процесса измереиия, обусловлено инерционностью коммуriTDpa. При этом каждому циклу измерения одного параметра предшествует процесс коммутации, Целью изобретения является повышение б1.1стродействия устройства. Эта цель достигается тем, что в предложенное устройство введены три блока вычитания, блок сложения, сумматор абсолютных велимин и блок эталонных сигналов. Первые входы первого и второго блока вычитания подключены к одному иэ выза дов .коммутатора. Вторые входы блоков вы читания подключены к выходам блока эталонных сигналов. Первые аходы третьего блока вычитания и блока сложения соедине с выходом первого блока вычитания, вторы входы - с выходом второго блока вычитани а выходы - с входами сумматора абсолютных величин, выход которого соединен со входом преобразователя анал01%-код. Сущность изобретения заключается в тЬм, что после сравнения в аналоговой форме поступающих для контроля параметров с номвнапьвымв значеввями хфоводится вх: совместное преобразование и формирование Т4ЖОЙ фуикции параметров, сравнением значения которой с полем допуска можно провести оценку каждого нз контролируемых параметров на с оотаетствие областв дооусткмых звачевШ. устройства пряведена на чертеже. Устройство коммутатор 1 с двумя входамв, выходы которого подключены к входам двух блокоь. 2,3 вычитания. Вторые входы порледнах соединены с различными ъъкодами блока 4 i аталонных сигналов. Первые входы третьего блока 5 вычитания н блоки 6 сложения соединены с выходом первого блока 2 вторые входы - с выходом Bxt гл.блокй 3 вычвтавия« а выходы п(шаспены ко входам сумматора 7 абсопютвыхэелачин, ВыходсумматораТсоеднневсовходомпреоб разователя 8 аналог-код, к выходу которо го подключены последоватеташо соединенные блок 9 сравнения и блок 10 вывода. Второй вход блока 9 сравнения подключен к выходу блока памяти 11. Командные входы коммутатора 1, блока 4 эталонных сигналов, блока 9 сравнения, блока 1О вы вбда и блока памяти 11 подключены к раз дельным выходам блока 12 управления. Устройство работает следующим образом. После прохождения через коммутатор 1 , характеризующие контролируемые параметры, поступают каждый на первый вход одного из бгюков 2,3 вычита ия, на вторые входы которых поступают налоговые сигналы из блока 4 эталоных сигналов, величины которых равны ноинальным значениям контролируемых пааметров. Полученные на выходах блоков ,3 вычитаьшя две разности величин посупают на разные входы блока 6 сложеия и блока 5 вычитания, с выхода котоых сигналы поступают на вход сумматора 7 абсолютных величин. После суммирования результирующий сигнал поступает на вход преофазователя 8 аналог-код и затем сравнивается в блоке 9 сравнения в цифровой форме с величиной поля допуска. Результат сравнения подается в блок 1О вьшода. Величина поля допуска считывается в блоке 9 сравнения из блока памяти 11. Совместная работа коммутатора 1, блока памяти 11, блока 9 сравнения, блока 4 эталонных сигналов и блок 10 вывода обеспечивается блоком 12 управления. Последовательность операций, связанных с преобразованием контролируемых параметров, реализуемых бдоками 2-7, обеспечивает, в результате получение на выходе сумматора 7 абсолютных величин такой функции контролируемых параметров, сравнением значения которой с полем допуска возможно оценить соответствие каждого из контролируемых параметров области допустимых значений, поэтому выход за пределы поля допуска, хотя бы одного из контролируемых параметров, фиксируется блоком 9 сравнения. Предлагаемое устройство позволяет существенно сократить время контроля комплекса параметров за счет уменьщения общего времени коммутации. Формула изобретения Устройство для контроля аналоговых параметров, содержащее последовательно соединенные преобразователь аналог-код, блок сравнения и блок вывода, блок памяти, выход Которого подключен ко второму входу блока сравнения, и блок управления, выходы которого подключены к кoмaндныlv входам коммутатора, блока памяти, блока сравнения и блока вьшода, от ji и чающееся тем, что, с целью повьпиения быстродействия устройства, оно содержит три блока вычитания, блок сложения, сумматор абсолютных величин и блок эталонных сигналов; причеь первых входы первого и второго блоков вычитания подключены к одному из выходов коммутатора, вторые входы блоков вычитания подключены к выхэflahi блока эталонных сигналов; первые входы третьего блока вычитания и блока сложения соединены с выходом первого блока вычитания, вторые входы - с выходом второго блока вычитания, а входы - с входами сумматора абсолютных величин, выход которого соединен со входом преобразователя аналог-код.

Источники информации, принятые во рнцмание при эксп угизе.

№ 418833, Млл . О 05 В 23/02,1970 г.

8

10

Авторы

Даты

1977-06-05—Публикация

1976-04-06—Подача