со

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для реализации быстрого преобразования Хартли | 1987 |

|

SU1444815A1 |

| Арифметическое устройство для процессора быстрого преобразования Фурье | 1989 |

|

SU1631556A1 |

| Арифметическое устройство для процессора быстрого преобразования Фурье | 1989 |

|

SU1631555A1 |

| Процессор быстрых дискретных преобразований | 1989 |

|

SU1725227A1 |

| Устройство для вычисления двумерного быстрого преобразования Фурье | 1986 |

|

SU1408442A1 |

| Устройство для вычисления быстрого преобразования Фурье | 1989 |

|

SU1619300A1 |

| Устройство для умножения | 1981 |

|

SU1012245A1 |

| Устройство для умножения комплексных чисел | 1986 |

|

SU1388851A1 |

| Устройство для цифровой обработки сигналов | 1985 |

|

SU1336028A1 |

| Устройство для реализации алгоритма Волдера | 1983 |

|

SU1115049A1 |

Изобретение относится к вычислительной технике и может быть использовано в системах цифровой обработки сигналов. Цель изобретения - сокращение оборудования. Поставленная цель достигается за счет того, что устройство содержит три элемента И, три триггера, девять регистров, три элемента ИЛИ, шесть коммутаторов, суммато- ры-вычитатели, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и соответствующие связи между узлами устройства.2 ил.

Изобретение относится к вычислительной технике и может быть использовано в системах цифровой обработки сигналов.

Известно устройство для выполнения базовой операции быстрого преобразования Фурье, содержащее четыре умножителя, три сумматора и три вычитателя.

Недостатки устройства - низкое быстродействие и большие аппаратные затраты.

Наиболее близким по технической сущности к изобретению является устройство выполнения базовой операции быстрого преобразования Хартли - Фурье вещественных последовательностей, содержащее четыре регистра, сумматор, вычитатель, комплексный умножитель и два коммутатора, причем выход первого регистра соединен с первыми входами сумматора,, вычитателя и комплексного умножителя, выход второго регистра соединен с вторыми входами сумматора,, вычитателя и комплексного умножителя, третий вход которого соединен с выходом третьего регистра, выход четвертого регистра соединен с четверым входом комплексного умножителя, выход сумматора соединен с первым входом первого коммутатора, второй вход которого соединен с первым выходом комплексного умножителя, второй выход комплексного умножителя соединен с вторым входом второго коммутатора, первый вход которого со- единен с выходом вычитателя, входы управления коммутаторами соединены с входом управления устройства, выходы коммутаторов являются выходамиустройства, а входы регистров - входами устройства.

Недостаток известного устройства - большие аппаратные затраты, так как оно содержит комплексный умножитель, сумматор и вычитатель.

Цель изобретения -сокращение объема оборудования.

со го ho

ю

В устройство для выполнения базовой операции быстрого преобразования Хартли - Фурье вещественных последовательностей, содержащее четыре регистра и два коммутатора, дополнительно введены пять регистров, два сумматора-вычитателя, четыре коммутатора, три триггера, три элемента ИЛИ, три элемента И и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, причем тактовый вход устройства соединен с вторыми входами первого и второго элементов И, сиихровходами пятого, седьмого, девятого регистров, второго триггера и инверсным входом сброса третьего триггера, вход начальной установки соединен с вторым входом элемента ИЛИ и входом сброса первого, второго триггеров, вход режима работы устройства соединен с информэционким входом первого триггера, синхровход которого соединен с первым входом записи устройства, первый, второй, третий и четвертый информационные входы устройства соединены с информационными входами первого, второго, третьего и четвертого регистров, второй вход записи устройства соединен с си нх ровходамй первого и второго регистров, третий вход записи устройства соединен с первым входом третьего элемента ИЛИ, выход которого соединен с синхровходами третьего и четвертого регистров, первый вход первого элемента И соединен с выходом (п+1)-го разряда девятого регистра, выход первого, элемента И соединен с первым входом первого элемента ИЛИ, выход которого соединен с входом сброса девятого регистра, информационный вход которого соединен с прямым выходом первого триггера, инверсный выход которого соединен с вторым входом второго элемента ИЛИ, первый вход которого соединен с выходом n-го разряда девятого регистра, с входом управления первого сумматора-вычитателя и с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход второго элемента ИЛИ соединен с информационным входом второго триггера и вторым выходом состояния устройства, первый выход состояния устройства соединен с выходом второго триггера, выход первого разряда девятого регистра соединен, с входами задания режима третьего и четвертого регистров, входами управления первого, второго, третьего и пятого коммутаторов, синхровходами шестого, восьмого регистров и третьего триггера, выход которого соединен с входами сброса пятого и седьмого регистров, первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, соединен с третьим выходом второго коммутатора, выходы первого коммутатора соединены с управляющими входами четвертого коммутатора, управляющие входы шестого коммутатора соединены с первым и вторым выходами .второго коммутатора, третий разряд второго входа которого соединен с выходом третьего элемента И, выход n-го разряда третьего регистра соединен с первым разрядом второго входа первого коммутатора, с первым входом третьего элемента И и вторым разрядом второго входа коммутатора, вход первого разря0 да которого соединен с входом второго разряда второго входа первого коммутатора и выходом n-го разряда четвертого регистра, инверсный выход n-го разряда которого соединен с вторым входом третьего элемента И,

5 выход второго разряда девятого регистра - с первым входом элемента И, выход которого соединен с вторым входом третьего элемента ИЛИ, выход первого регистра соединен с первыми информационными входами третьего

0 и пятого коммутаторов, третьими входами

четвертого и шестого коммутаторов, выход

второго регистра соединен с,вторыми входами

четвертого и шестого коммутаторов,

выход третьего коммутатора соединен с пер5 вым входом первого сумматора-вычитателя, второй вход которого соединен с выходом четвертого коммутатора, четвертый вход которого соединен с выходом шестого регистра, вход которого соединен входом пятого

0 регистра и выходом первого сумматора-вычитателя, выход пятого регистра соединен с первым информационным выходом устройства и сдвигом на один разряд вправо с вторым входом третьего коммутатора, выход элемен

5 та ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с управляющимвходомвторогосумматора-вычитателя, первый вход которого соединен с выходом пятого регистра, второй вход которого соединен со сдвигом на один

0 разряд вправо с выходом седьмого регистра,; вход которого соединен с входом восьмого регистра и выходом второго сумматора-вычитателя, второй вход соединен с выходом шестого коммутатора, четвертый вход которого

5 соединен с выходом восьмого регистра, выход седьмого регистра соединен с вторым выходом устройства, первые разряды первых входов первого, второго коммутаторов и первые входы четвертого, шестого коммутато0 ров соединены с потенциалом Лог. О, второй разряд первого входа первого коммутатора, второй и третий разряды первого входа второго коммутатора и информационный вход третьего триггера соединены с по5 тенциэлом Лог. 1.

Сокращение затрат оборудования в предлагаемом устройстве по сравнению с известным достигается за счет вычисления базовой операции быстрого преобразования Хартли - Фурье на базе двух сумматоров-вычитателей. Предлагаемое устройство отличается наличием новых блоков: четырех коммутаторов, пг.ти регистров, двух сумма- торов-вычитатйлей, двух триггеров, трех элементов ИЛИ, двух элементов И, элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и их связей с остальными элементами схемы.

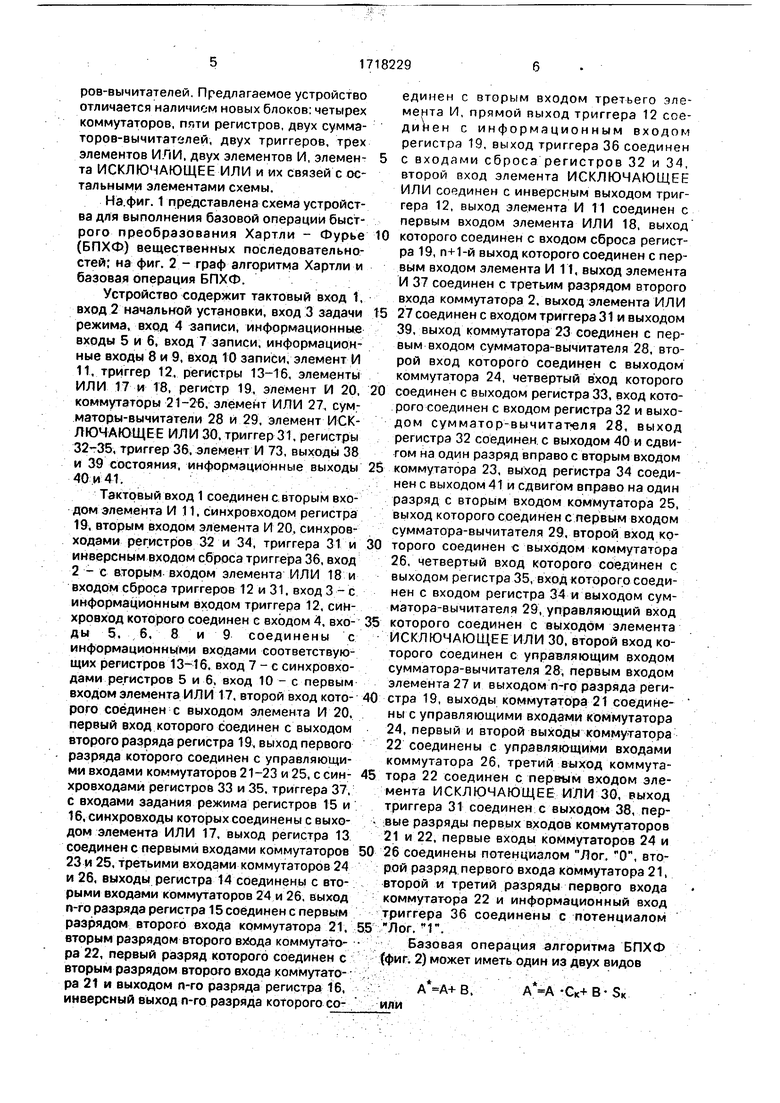

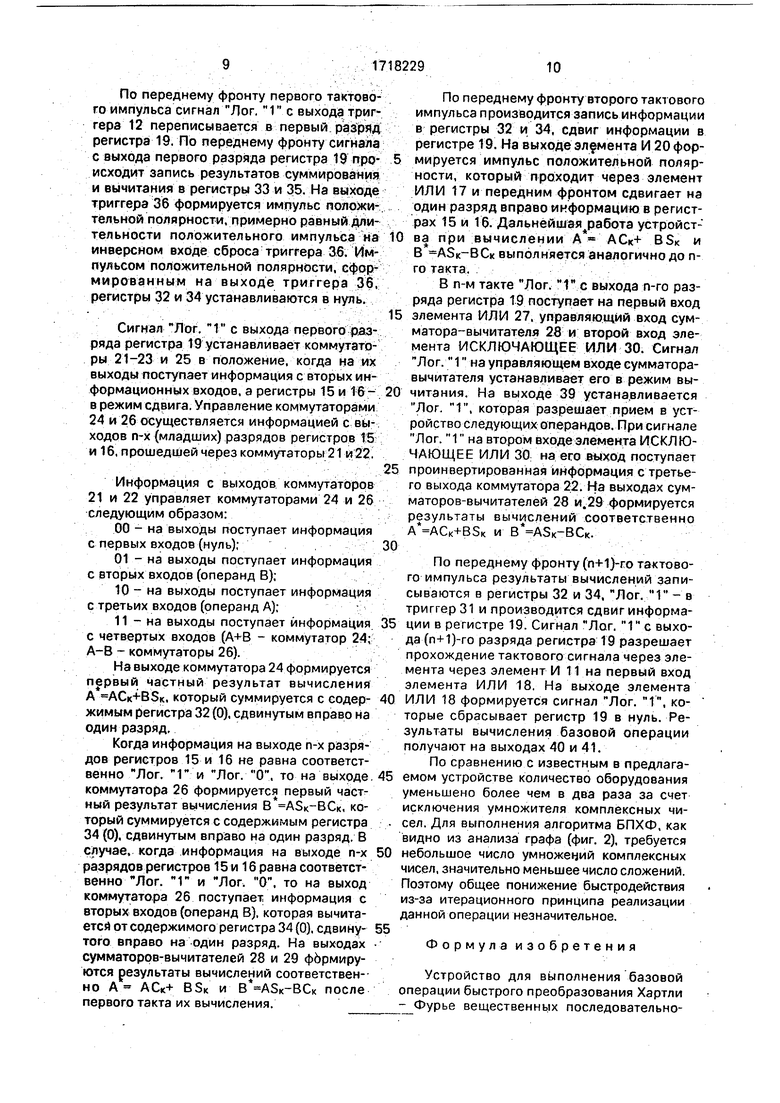

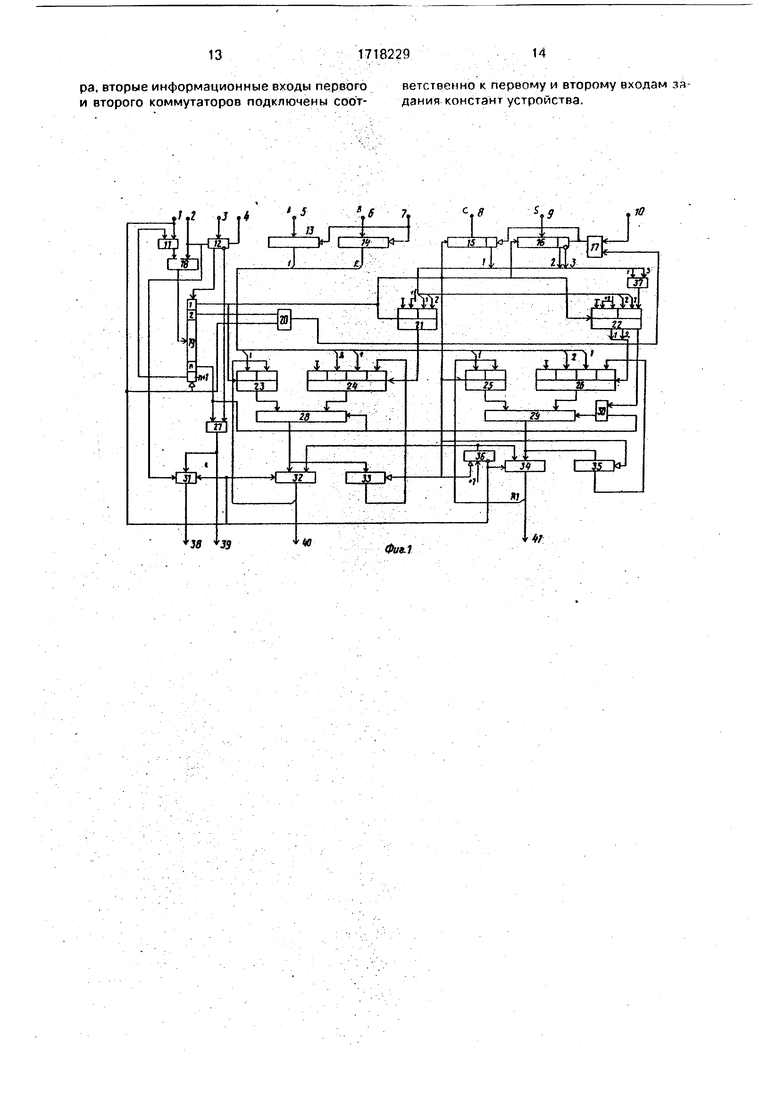

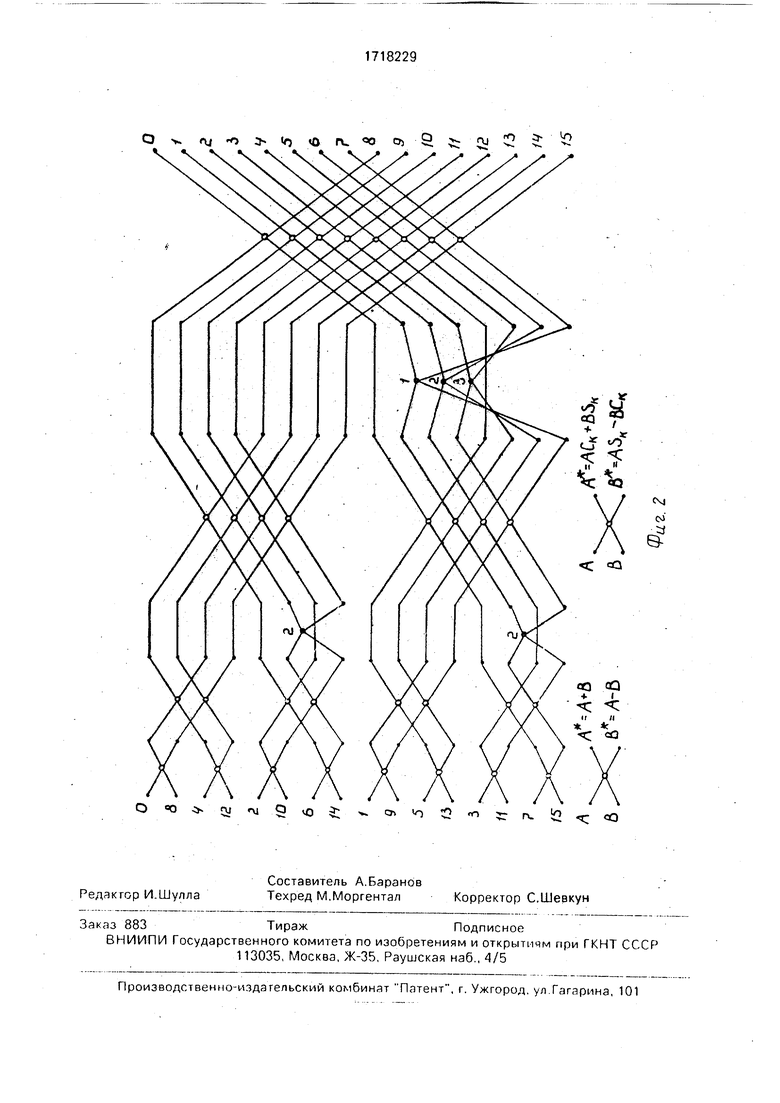

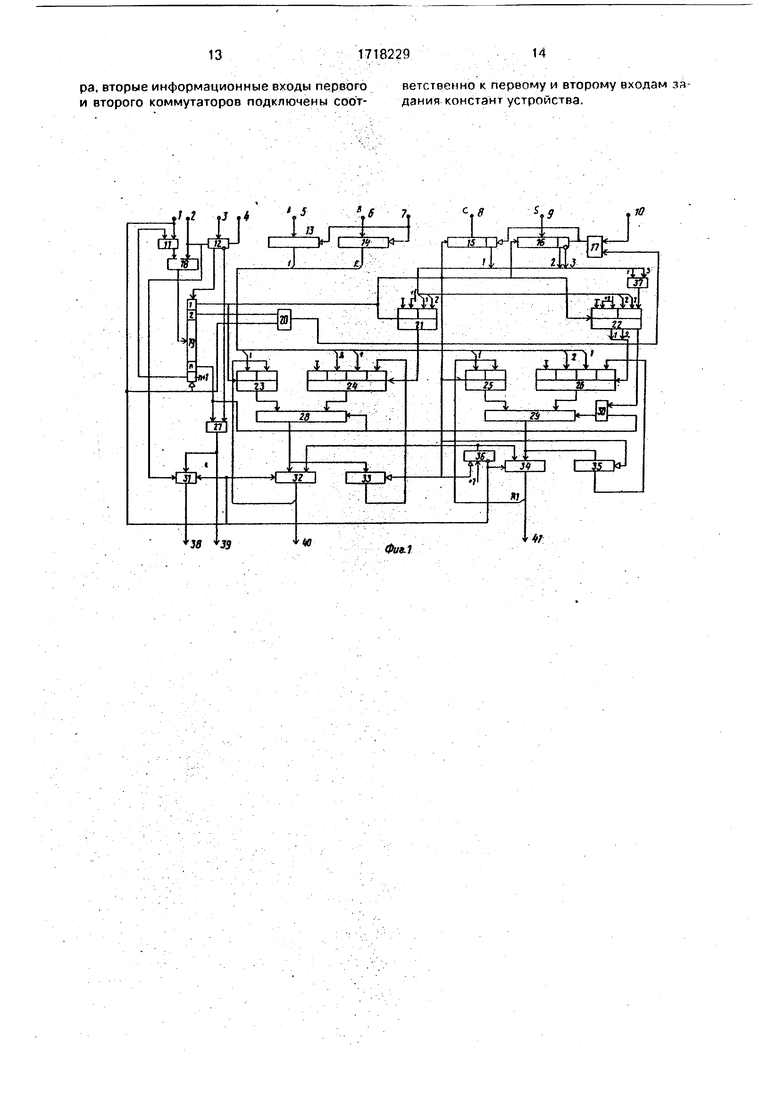

На фиг. 1 представлена схема устройства для выполнения базовой операции быстрого преобразования Хартли - Фурье (БПХФ) вещественных последовательностей; на фиг. 2 - граф алгоритма Хартли и базовая операция БПХФ.

Устройство содержит тактовый вход 1, вход 2 начальной установки, вход 3 задачи режима, вход 4 записи, информационные входы 5 и 6, вход 7 записи, информацион- ные входы 8 и 9, вход 10 записи, элемент И 11, триггер 12. регистры 13-16, элементы ИЛИ 17 и 18, регистр 19, элемент И 20, коммутаторы 21-26. элемент ИЛИ 27, сум- маторы-вычитатели 28 и 29, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 30. триггер 31, регистры , триггер 36, элемент И 73, выходы 38 и 39 состояния, информационные выходы 40 и 41.

Тактовый вход 1 соединен с вторым входом элемента И 11, синхровходом регистра 19, вторым входом элемента И 20, синхров- ходами регистров 32 и 34, триггера 31 и инверсным входом сброса триггера 36, вход 2 - с вторым входом элемента ИЛИ 18 и входом сброса триггеров 12 и 31. вход 3-е информационным входом триггера 12, син- хровход которого соединен с входом 4, входы 5. 6, 8 и 9 соединены с информационными входами соответствующих регистров 13-16. вход 7 - с синхровхо- дами регистров 5 и 6, вход 10 - с первым входом элемента ИЛ И 17. второй вход которого соединен с выходом элемента И 20, первый вход которого соединен с выходом второго разряда регистра 19, выход первого разряда которого соединен с управляющими входами коммутаторов 21-23 и 25. с син- хровходами регистров 33 и 35. триггера 37, с входами задания режима регистров 15 и 16, синхровходы которых соединены с выходом элемента ИЛИ 17, выход регистра 13 соединен с первыми входами коммутаторов 23 и 25, третьими входами коммутаторов 24 и 26, выходы регистра 14 соединены с вторыми входами коммутаторов 24 и 26, выход п-го разряда регистра 1.5 соединен с первым разрядом второго входа коммутатора 21, вторым разрядом второго вх&да коммутатора 22, первый разряд которого соединен с вторым разрядом второго входа коммутато-; ра 21 и выходом п-го разряда регистра 16, инверсный выход п-го разряда которого соединен с вторым входом третьего элемента И, прямой выход триггера 12 соединен с информационным входом регистра 19, выход триггера 36 соединен 5 с входами сброса регистров 32 и 34, второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с инверсным выходом триггера 12, выход элемента И 11 соединен с первым входом элемента ИЛИ 18, выход 10 которого соединен с входом сброса регистра 19, n+1-й выход которого соединен с первым входом элемента И 11, выход элемента И 37 соединен с третьим разрядом второго входа коммутатора 2, выход элемента ИЛИ 15 27 соединен с входом триггера 31 и выходом 39, выход коммутатора 23 соединен с первым входом сумматора-вычитателя 28, второй вход которого соединен с выходом коммутатора 24, четвертый вход которого 0 соединен с выходом регистра 33, вход которого соединен с входом регистра 32 и выходом сумматор-вычитат-еля 28, выход регистра 32 соединен, с выходом 40 и сдвигом на один разряд вправо с вторым входом 5 коммутатора 23, выход регистра 34 соединен с выходом 41 и сдвигом вправо на один разряд с вторым входом коммутатора 25, выход которого соединен с первым входом сумматора-вычитателя 29, второй вход ко- 0 торого соединен с выходом коммутатора 26, четвертый вход которого соединен с выходом регистра 35, вход которого соединен с входом регистра 34 и выходом сумматора-вычитателя 29, управляющий вход 5 которого соединен с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 30, второй вход которого соединен с управляющим входом сумматора-вычитателя 28, первым входом элемента 27 и выходом п-го разряда реги- 0 стра 19, выходы коммутатора 21 соединены с управляющими входами коммутатора 24, первый и второй выходы коммутатора 22 соединены с управляющими входами коммутатора 26, третий выход коммута- 5 тора 22 соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 30, выход триггера 31 соединен с выходом 38, пер- . вые разряды первых входов коммутаторов 21 и 22, первые входы коммутаторов 24 и 0 26 соединены потенциалом Лог. О, второй разряд первого входа коммутатора 21, второй и третий разряды первого входа коммутатора 22 и информационный вход триггера 36 соединены с потенциалом 5 Лог. Г.

Базовая операция алгоритма БЛХФ

{фиг. 2) может иметь один из двух видов

А А+ В,

Ск+В- S

или

,

B -A-SH-B-CK

где

Ск cos(2 л к/N); (2як/М).

В первом случае для выполнения базовой операции необходимо выполнить операции сложения и вычитания, во втором случае - операцию типа комплексного умножения, время выполнения которой намного больше времени выполнения операций сложения и вычитания.

Устройство для выполнения базовой операции БПХФ работает следующим образом.

Перед началом работы по входу 2 поступает импульс положительной полярности, который устанавливает регистр 19 и триггеры 12 и 31 в состояние Лог. О, Сигнал Лог.. О с выхода первого разряда регистра. 19 устанавливает регистры 15 и 16 в режим параллельной записи, а коммутаторы 21-23 и 25 в состояние, когда на их выходы поступает информация с первых входов. Информация 01 с выходов, коммутаторов 21 и 22 поступает на управляющие входы коммутаторов 24 и 26 и устанавливает их в положе- нии, когда на выходы поступает информация с вторых входов. В зависимости от информации на управляющих входах сумматоров-вычитателей 28 и 29 они могут устанавливаться в режим суммирования (на управляющем входе Лог. О) или в режим вычитания (на управляющем входе Лог. Т). Сигнал Лог. О с выхода n-го разряда регистра 19 устанавливает сумматор-вычи- татель 28 в режим суммирования.

Управление сумматором-вычитателем 29 осуществляется сигналом с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 30, который при одинаковой информации на входах равен Лог. О, а при равной - Лог. 1, так как на первый и второй входы элемента ИСКЛ ЮЧА- ЮЩЕ Е ИЛ И 30 поступают соответствен но Лог. 1 и Лог. О, на выходе формируются Лог.., устанавливающая сумматор-вычи- татель 29 в режим вычитания.

Информация о виде выполнения базовой операции поступает на вход 3 (0 - выполняются операции А А+В и 1 - выполняются операции А АСк+В5к и В А8к-ВСк), а операнды для выполнения базовой операции - на входы 5 (операнд А), 6 (операнд В), 8 (операнд Ск) и 9 (операнд SK). На выходе 39 формируется сигнал разрешающий (Лог. 1) или запрещающий (Лог. О) прием информации в устройство. Сигнал Лог. 1 с инверсного выхода триггера 12 проходит через элемент ИЛИ 27 на выход

39и разрешает прием информации в устройство.

Рассмотрим работу устройства при выполнении первого вида базовой операции, т.е. при вычислении А А+В и В А-В, На вход 3 поступает сигнал Лог. О, а на входы 5 и 6 - соответственно операнд А и В. По

0 переднему фронту сигналов (перепаду уровней с Лог. О в Лог. 1) на входах 4 и 7 происходит запись информации в триггер 12 и регистры 13 и 14. Информация с выходов регистра 13 (операнд А) проходит через

5 коммутаторы 23 и 25 и поступает на первые сумматрров-вычитателей 28 и 29, на вторые входы которых поступает информация с выходов регистра 14 (операнд В), прошедшая через коммутаторы 24 и 26. На выходах

0 сумматора-вычитателя 28 получают результат суммирования (А+ В), а на выходах Сумматора -вычитателя 29 - результат вычитания (А-В). Сигнал Лог. 1 с инверсного выхода триггера 12 проходит через

5 элемент ИЛИ 27 на выход 39 и разрешают прием следующих операндов.

По переднему фронту первого тактового импульса происходит запись результатов суммирования и вычитания в регистры

0 32 и 34, а также запись Лог. 1 в триггер 31, которая указывает нато, что на выходах

40и 41 сформирован результат базовой операций;

Одновременно с приходом первого так5 тового импульса на вход 1 на вход 7 поступает сигнал записи, по которому происходит запись следующей пары операндов в регистры 13 и 14. Устройство позволяет в каждом такте получать на выходах

0 40 и 41 результаты выполнения базовой операции.

Рассмотрим работу устройства при выполнении второго базовой операции, т.е. при вычитании А АСк+ВЗк и В А5к5 ВСк. На вход 3 поступает сигнал Лог. 1, на входы 5, 6, 8 и 9 - соответственно операнды А, В, Ск и Зк. По переднему фронту сигналов на входах 4, 7 и 10 происходит запись информации в триггер 12 и регистры 13-16. Йнфор0 мация с выходов регистров .13 и 14 проходит через коммутаторы 23-26 и поступает на входы сумматоров-вычитателей 28 и 29.

На выходах сумматоров-вычитателей 28 и 29 формируются результаты соответ5 ственно суммирования (А+В) и вычитания (А-В). На первый и второй входы элемента ИЛИ 27 поступает сигнал Лог. О, который проходит через данный элемент на выход 39 и запрещает прием информации е устройство.

По переднему фронту первого тактового импульса сигнал Лог. 1 с выхода триггера 12 переписывается в первый, разряд регистра 19. По переднему фронту сигнала с выхода первого разряда регистра 19 про- исходит запись результатов суммирования и вычитания в регистры 33 и 35. На выходе триггера 36 формируется импульс положительной полярности, примерно равный длительности положительного импульса на инверсном входе сброса триггера 36. Импульсом положительной полярности, сформированным на выходе триггера 36, регистры 32 и 34 устанавливаются в нуль. . ... . . ; :v :;

Сигнал Лог. 1 с выхода первого разряда регистра 19 устанавливает коммутаторы 21-23 и 25 в положение, когда на их выходы поступает информация с вторых информационных входов, а регистры 15 и 16в режим сдвига. Управление коммутаторами 24 и 26 осуществляется информацией с выходов n-х (младших) разрядов регистров 15г и 16, прошедшей через коммутаторы 21 и22.

: . . .. . .-. :: ; ..

Информация с выходов коммутаторов 21 и 22 управляет коммутаторами 24 и 2$ следующим образом:

00- на выходы поступает информация

с первых входов (нуль);,

01- на выходы поступает информация с вторых входов (операнд В);

10- на выходы поступает информация с третьих входов (операнд А);

11- на выходы поступает информация с четвертых входов (А+В - коммутатор 24;

А-В - коммутаторы 26).

На выходе коммутатора 24 формируется первый частный результат вычисления А -АСк+В5к, который суммируется с еодер- жимым регистра 32 (0), сдвинутым вправо на один разряд.

Когда информация на выходе n-х разрядов регистров 15 и 16 не равна соответственно Лог. 1 и Лог. О, то на выходе. коммутатора 26 формируется первый частный результат вычисления В , который суммируется с содержимым регистра 34 (0), сдвинутым вправо на один разряд. В случае, когда информация на выходе п-х разрядов регистров 15 и 16 равна соответственно Лог. Г и Лог, О, то на выход коммутатора 26 поступает, информация с вторых входов (операнд В), которая вычитается от содержимого регистра 34 (0), сдвину- того вправо на один разряд. На выходах сумматоров-вычитателей 28 и 29 фбрмиру- ются результаты вычислений соответственно А АСк+ BSK и В А5к-ВСк после первого такта их вычисления.

По переднему фронту второго тактового импульса производится запись информации в регистры 32 и 34, сдвиг информации в регистре 19. На выходе элемента И 20 формируется импульс положительной полярности; который проходит через элемент ИЛИ 17 и передним фронтом сдвигает на один разряд вправо информацию в регистрах 15 и 16. Дальнейшая работа устройства при вычислении А АСк+ В8к и В AS«-BCx выполняется аналогично до п- го такта.

В n-м такте Лог. 1 с выхода n-го разряда регистра 19 поступает на первый вход элемента ИЛИ 27. управляющий вход сум- матора-вычитателя 28 и второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 30. Сигнал Лог. 1 на управляющем входе еумматора- вычитателя устанавливает его в режим вычитания. На выходе 39 устанавливается Лог. 1, которая разрешает прием в устройство следующих операндов. При сигнале Лог. 1 на втором входе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 30: на его выход поступает проинвертированная информация с третьего выхода коммутатора 22. На выходах сумматоров-вычитателей 28 и. 29 формируется результаты вычислений соответственно А АСк+В5к и В А5к-ВСк.

По переднему фронту (п+1)-го тактового импульса результаты вычислений записываются в регистры 32 и 34, Лог. 1 - в триггер 31 и производится сдвиг информации в регистре 19. Сигнал Лог. 1 с выхода (п+1)-го разряда регистра 19 разрешает прохождение тактового сигнала через элемента через элемент И 11 на первый вход элемента ИЛИ 18. На выходе элемента ИЛИ 18 формируется сигнал Лог. 1, ко- торые сбрасывает регистр 19 в нуль. Результаты вычисления базовой операции получают на выходах 40 и 41.

По сравнению с известным в предлагаемом устройстве количество оборудования уменьшено более чем в два раза за счет исключения умножителя комплексных чисел. Для выполнения алгоритма БПХФ, как видно из анализа графа (фиг. 2), требуется небольшое число умножений комплексных чисел, значительно меньшее число сложений. Поэтому общее понижение быстродействия из-за итерационного принципа реализации данной операции незначительное.

Формул а изобретения

Устройство для выполнения базовой операции быстрого преобразования Хартли - Фурье вещественных последовательностей, содержащее первый и второй регистры , первый и второй сдвиговые регистры и первый и второй коммутаторы, отличающееся тем, что, с целью сокращения обьема оборудования, оно содержит тре- тий-шестой регистры, первый и второй сум- маторы-вычитатели, третий регистр сдвига, первый-третий триггеры, первый-третий элементы И, первый-третий элементы ИЛИ и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ. причем выход старшего разряда первого регистра сдвига подключен к первому входу первого элемента И и первому разряду первого информационного входа первого коммутатора и второму разряду первого информационного входа второго коммутатора, прямой выход старшего разряда второго регистра сдвига подключен к второму разряду первого информационного входа первого коммутатора и первому разряду первого информационного входа второго коммутатора, выход которого подключён к первому входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого подключен к управляющему входу первого сумматора-вычйта- теля, первый и второй информационные входы которого подключены к выходам соответственно третьего и четвертого коммутаторов, первые информационные входы которых соединены с первыми информационными входами пятого и шестого коммутаторов и подключены к выходу первого, регистра, информационный вход которого является входом первого операнда устройства, входом второго операнда которого является информационный вход второго регистра, выход которого подключен к вторым информационным входам третьего и пятого коммутаторов, выход первого сумматора- вычитателя подключен к информационным входам .третьего и четвертого регистров, выходы которых подключены соответственно к третьему информационному входу третьего и второму информационному входу четвертого коммутаторов, выходы пятого и шестого коммутаторов подключены соответственно к первому и второму информационным входам второго сумматора-вычитателя, выходы которых подключены к информационным входам соответственно пятого и шестого регистров, выходы которых подключены соответственно к третьему информационному входу ше- стого коммутаторов, четвертые информационные входы третьего и пятого коммутаторов подключены к входу задания логического нуля устройства, первый тактовый вход которого подключен к первым входам второго и третьего элементов И, тактовым входам четвертого и шестого регистров, первого триггера, входу сброса второго триггера и тактовому входу третьего регистра сдвига, выход первого разряда которого подключен к тактовым входам третьего и пятого регистров, второго триггера, входам режима первого и второго регистров сдвига, управляющим входам первого, второго, четвертого и шестого коммутаторов, второй выход первого коммутатора подклю0 чен к управляющему входу третьего коммутатора, выход второго коммутатора - к управляющему входу пятого коммутатора, выход второго разряда третьего регистра сдвига подключен к второму входу третьего

5 элемента И, выход которого подключен к первому входу первого элемента ИЛИ, выход которого подключен к тактовым входам первого и второго регистров сдвига, информационные входы которых подключе0 ны соответственно к первому и второму входам коэффициентов устройства, вход начальной установки которого подключен к входам сброса первого и третьего триггеров, и первому входу второго элемента

5 ИЛИ, выход которого подключен к входу сброса третьего регистра сдвига, выход последнего разряда котороголодключен к второму входу второго элемента И, выход которого подключен к второму входу второ0 го элемента ИЛ И, вход задания режима устройства подключен к информационному входу третьего триггера, прямой выход которого подключен к информационному последовательному входу третьего регистра

5 сдвига, выход предпоследнего разряда которого подключен к управляющему входу второго сумматора-вычитателя. второму входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и первому входу третьего элемента ИЛИ. вы0 ход которого подключен к информационному входу первого триггера, объединен с выходом первого триггера и является выходом состояния устройства, первым и вторым выходом результата являются выходы соот5 ветственно четвертого и шестого регистров, входы сброса которых подключены к выходу второго триггера, второй тактовый вход устройства подключен к тактовому входу третьего триггера, инверсный выход которого.

0 подключен к второму входу третьего элемента ИЛИ, тактовые входы первого и второго регистров подключены к третьему тактовому входу устройства, к четвертому тактовому входу которого подключен вто5 рой вход первого элемента ИЛИ, четвертый выход старшего разряда второго регистра сдвига подключен к второму входу первого элемента И, выход которого подключен к третьему разряду первого информационного входа первого коммутатоpa, вторые информационные входы первого ветстеенно к первому и второму входам зд- и второго коммутаторов подключены соо т- дания констант устройства.

О . М -О :}- «О «О IV О О)

О у «м .О j 3;

01

)

C4J

CM

6

ел о tЈ п

п.

«t; «О

| Каляев А.В | |||

| Многопроцессорные системы с программируемой архитектурой.-- М.: | |||

| Радио и связь, 1984 | |||

| с | |||

| Питательный кран для вагонных резервуаров воздушных тормозов | 1921 |

|

SU189A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Процессор быстрого преобразования Хартли-Фурье вещественных последовательностей | 1988 |

|

SU1594562A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-03-07—Публикация

1990-03-19—Подача