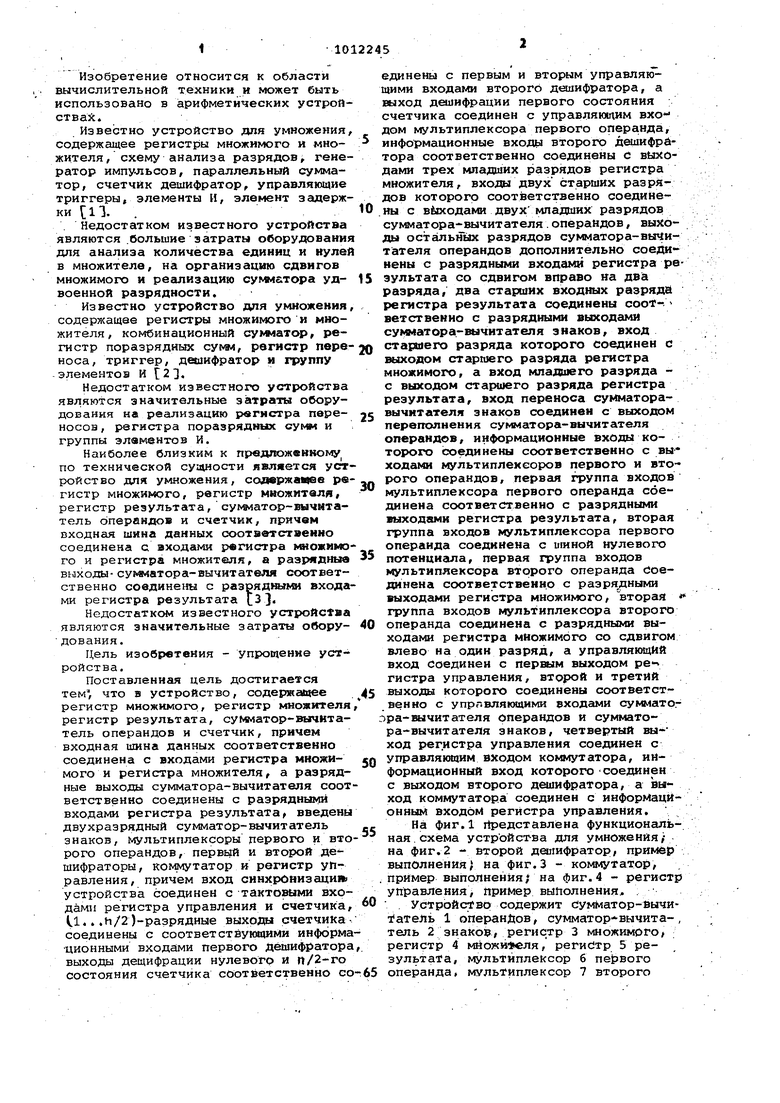

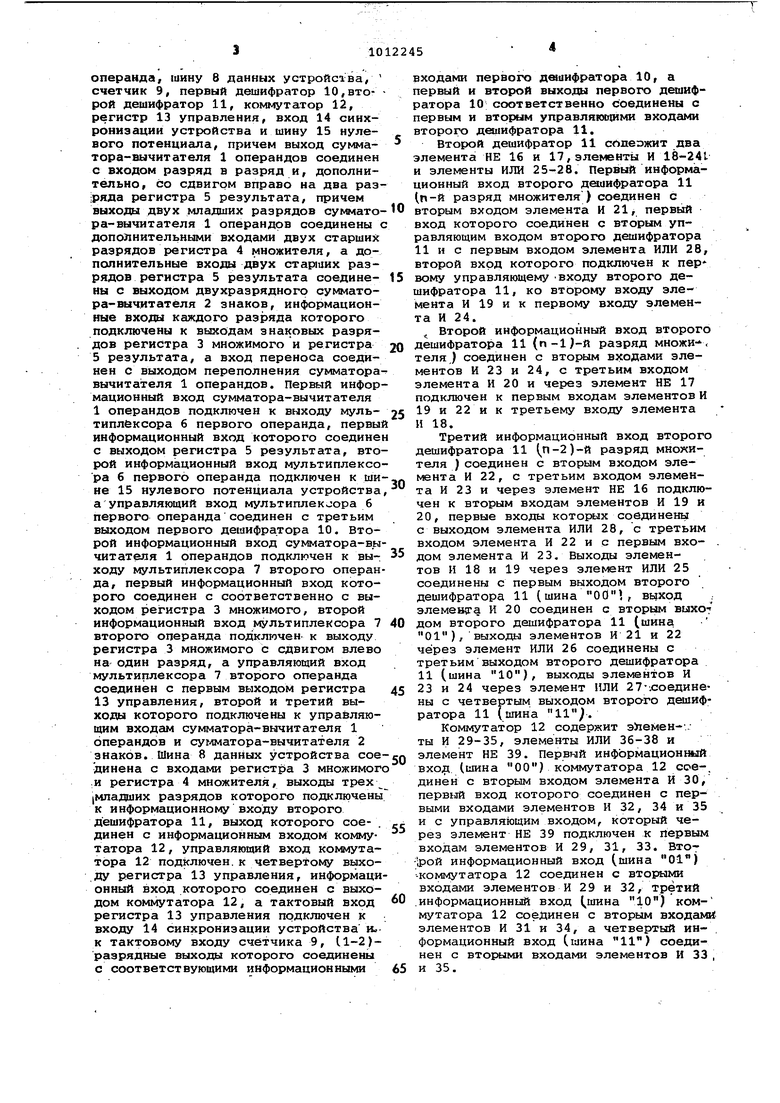

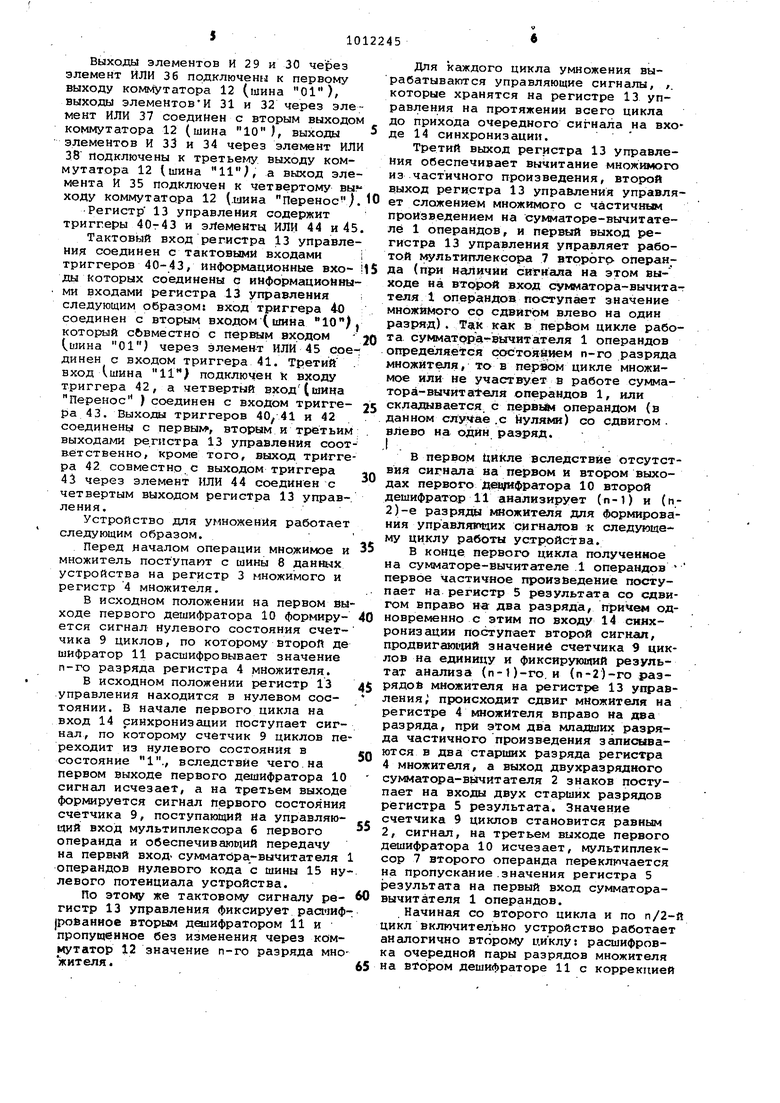

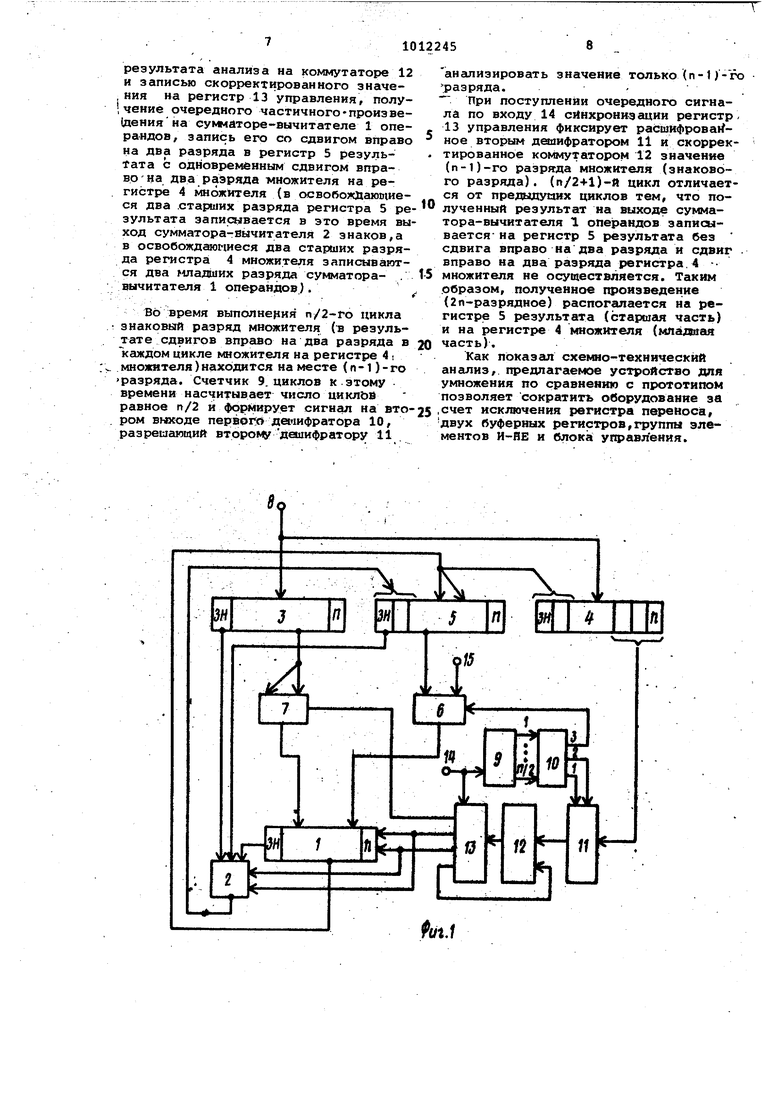

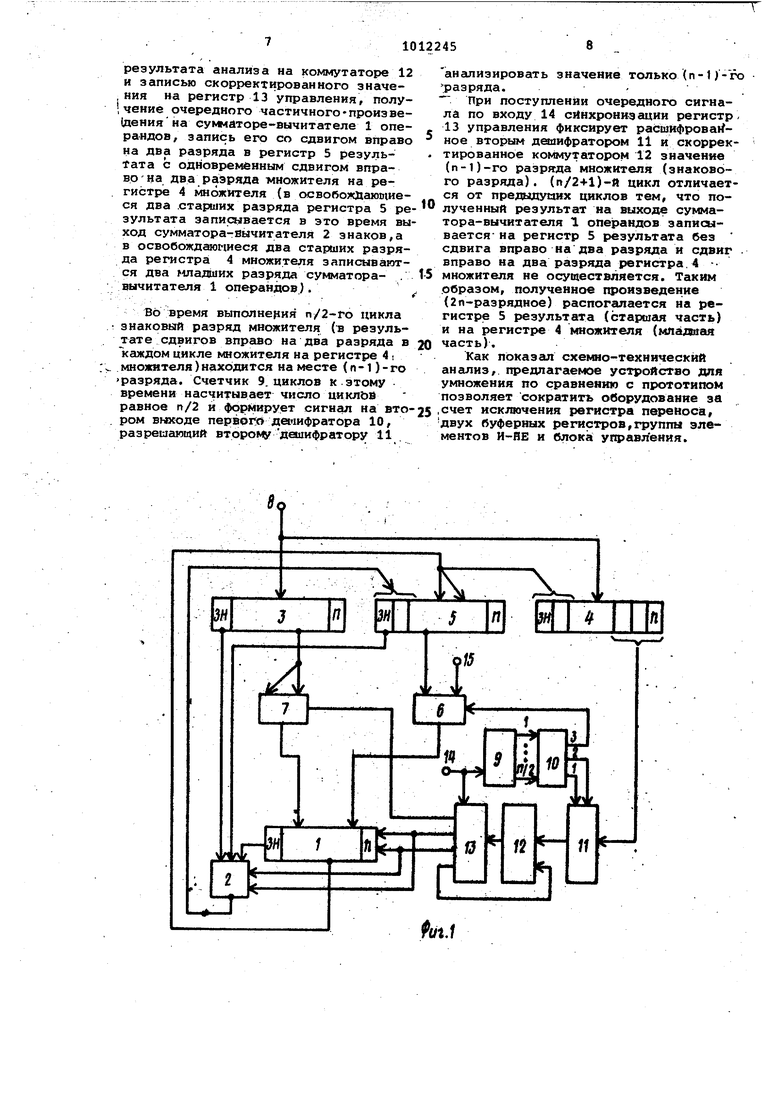

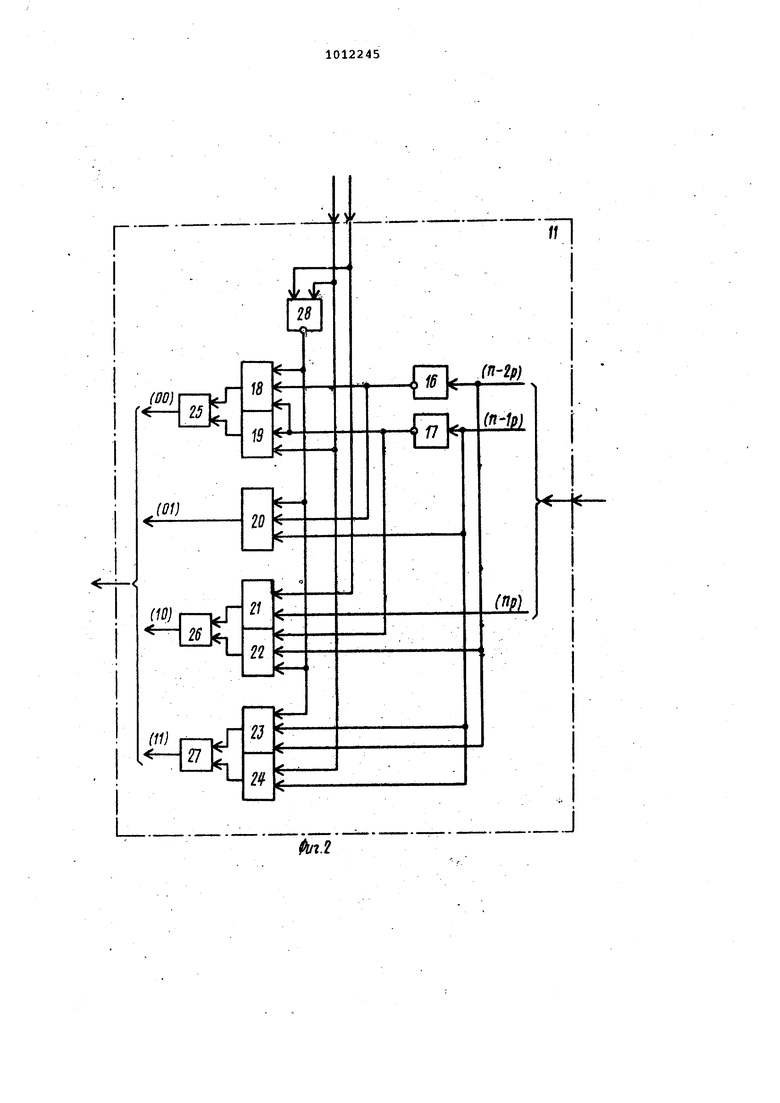

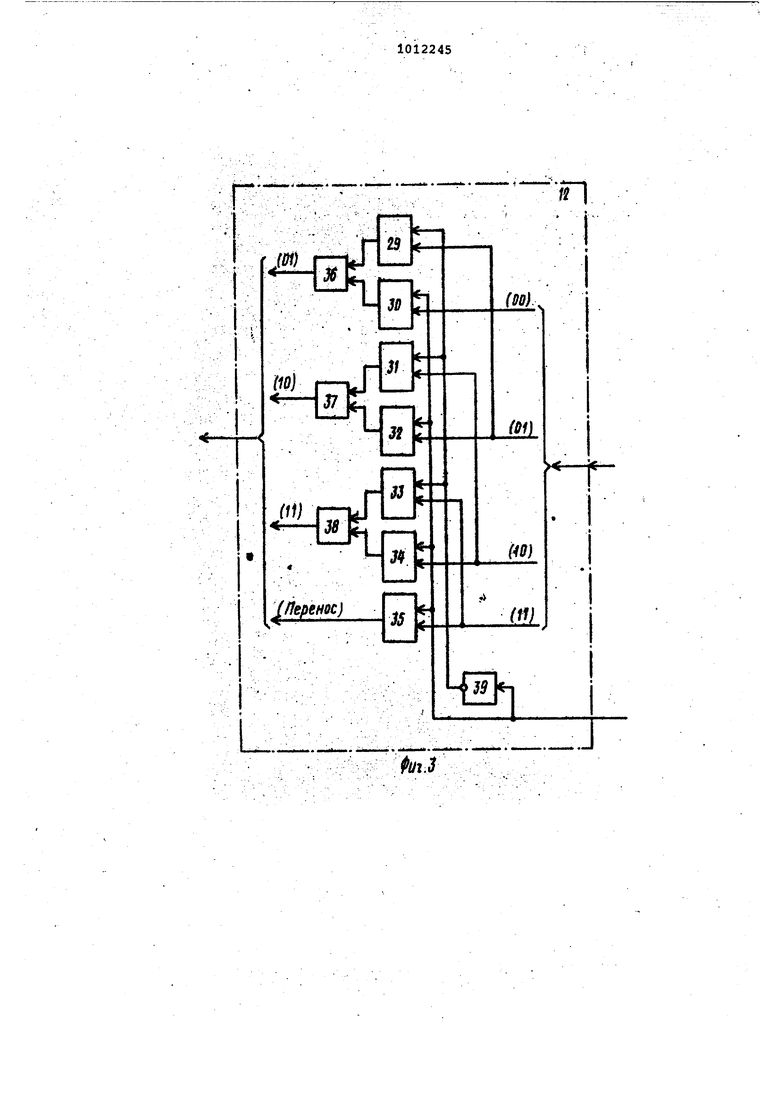

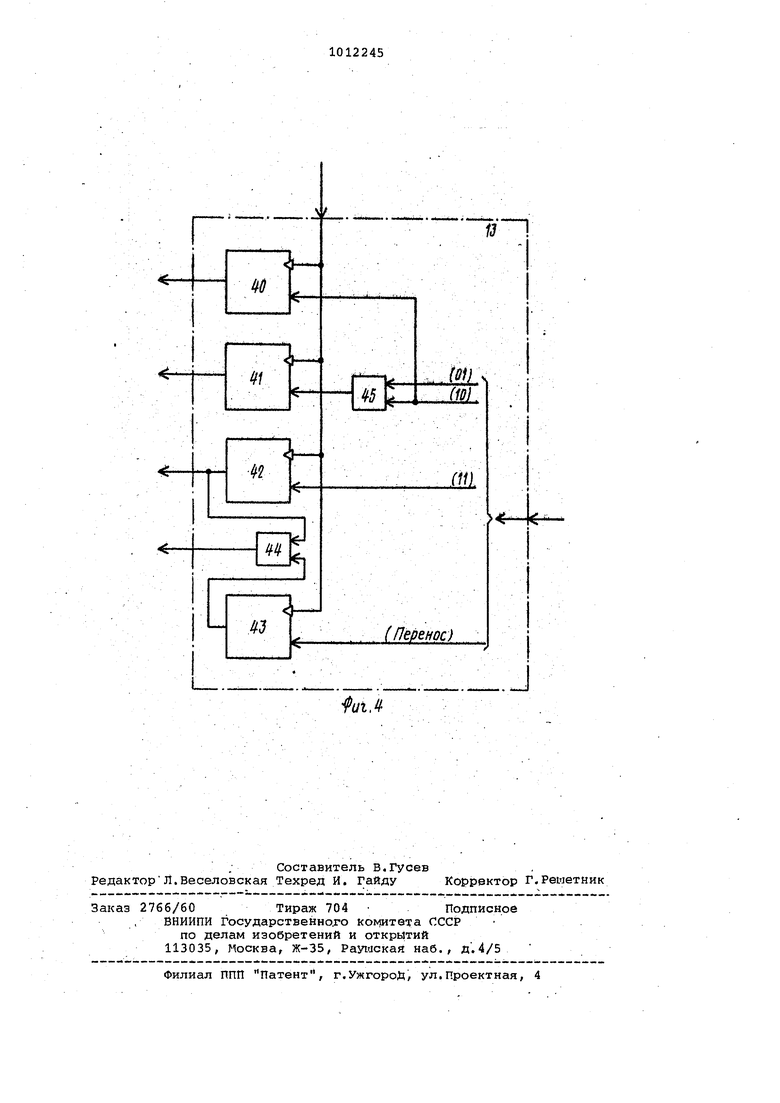

Изобретение относится к области вычислительной техники и может быть использовано в арифметических устроП cTBak. Известно устройство для умножения содержащее регистры множи «юго и множителя, схему анализа разрядов, гене ратор импульсов, параллельный сумматор, счетчик дешифратор, управляющие триггеры, элементы И, элемент задерж ки 11. . Недостатком известного устройства являются .большие затраты оборудовани для анализа количества единиц и куле в множителе, на организацию сдвигов множимого и регшизацию cyNM&Topa удвоенной разрядности. Известно устройство для умножения содержащее регистры множимого и множителя , комбинационный сумматор, регистр поразрядных суми, регистр пере носа, триггер, дешифратор и группу - элементов И 23. Недостатком известного устройства являются значительные затраты оборудования на реализацию регистра переносов, регистра поразрядных оумн и группы элементов И. Наиболее близким к предложенному по технической суауюсти является уст ройство для умножения, содержацее ре гистр множи1« го, регистр множителя, регистр результата,суг 1атор-вычмтатель операндов и счетчик, причем входная шина данных соотаетственно соединена с входами р егистра 11ШожимО го и регистра множителя, а разрядные выходы-суивлатора-вычитателя соответственно соединены с разрядк ми входа ми регистра результата . Недостатком известного устройства являются значительные затраты оборудования. Цель изобретения - упрощение устройства. Поставленная цель достигается тем , что в устройство, содержащее регистр множимого, регистр множителя регистр результата, сумматор-вычитатель операндов и счетчик, причем входная шина данных соответственно соединена с входами регистра множиМОго и регистра множителя, а разрядные выходы сумматора-вычитатеяя соот ветственно соединены с разрядными входами регистра результата, введены двухразрядный сумматор-вычитатель знаков, мультиплексоры первого и вто рого операндов, первый и второй дешифраторы, KONDviyTaTop и регистр управления, причем вход синхронизацил устройства соединен с тактовыми входами регистра управления и счетчика. Ц,..h/2)-разрядные выходы счетчикасоединены с соответстёуивдими информа ционными входами первого дешифратора выходы дешифрации нулевого и п/2-го состояния счетчика соответственно со единены с первым и вторым управляющими входами второго дешифратора, а выход дешифрации первого состояния ; счетчика соединен с управляющим дом мультиплексора первого операнда, информационные входы второго дешифратора соответственно соединены с выходами трех младших разрядов регистра множителя, входы двух старших разрядов которого соответственно соединеиы с вйподами двух младших разрядов сумматора-вычитателя.операндов, выходы остальных разрядов сумматора-вычитателя операндов дополнительно соединены с разрядными входами регистра результата со сдвигом вправо на два разряда, два старших входных разряда регистра результата соединены соот- ветственио с разрядными выходами сумматора-вычитателя знаков, вход старшего разряда которого Соединен с выходом старшего разряда регистра множимого, а вход младшего разряда с выходом craixiiero разряда регистра результата, вход переноса сумматоравычнтателя знаков соединен с выходом переполнения сумматора-вычитателя операндов, информационные входы которого соединены соответственно с вы ходами мультиплексоров первого и второго операндов, первгл группа входов мультиплексора первого операнда соединена соответственно с разрядными выходшли регистра результата, вторая группа входов мультиплексора первого операнда соединена с итной нулевого потенциала, первая группа входов мультиплексора второго операнда Соединена соответственно с разря,дными выходами регистра множимого, вторая группа входов мультиплексора второго операнда соединена с разрядными выходами регистра множимого со сдвигом влево на один разряд, а управлякицйй вход соединен с первым выходом регистра управления, второй и третий выходы которого соединены соответственно с упрг.влякнцими входами суммато.ра-вычитателя операндов и сумматора-вычитателя знаков, четвертый выход регистра управления соединен с управляияцим входом коммутатора, информационный вход которого-соединен с выходом второго дешифратора, а аыход коммутатора соединен с информационным входом регистра управления. На фиг.1 Представлена функциональная схема устройст-ва для умножения,на фиг.2 - второй дешифратор, пример выполнения; на фиг.3 - коммутатор, пример выполнения; на фиг.4 - регистр управления, пример выполнения. Устройстввр содержит с умМатор-Вычи1 атель 1 операнйов, сумматор-вычита-, тель 2 знаков, регистр 3 множимого, регистр 4 ьв1ожЙ1 еля, регистр 5 результата, мультиплексор 6 первого операнда, мультиплексор 7 второго операнда, шину 8 данных устройсхва, счетчик 9, первый дешифратор 10,второй дешифратор 11, коммутатор 12, регистр 13 управления, вход 14 синхронизации устройства и шину 15 нулевого потенциала, причем выход сумматора-вычитателя 1 операндов соединен с входом разряд в разряд и, дополнительно, со сдвигом вправо на два раз ;ряда регистра 5 результата, причем выходы двух младших разрядов cyivwaTo ра-вычитателя 1 операндов соединены дополнительными входами двух старших разрядов регистра 4 множителя, а дополнительные входы двух cTapiuHx разрядов регистра 5 результата соединены с выходом двухразрядного сумматора-вычитатёля 2 знаков, информационные входы каждого разряда которого подключены к выходам знаковых разрядов регистра 3 множимого и регистра 5 результата, а вход переноса соединен с выходом переполнения сумматора вычитателя 1 операндов. Первый инфор мационный вход сумматора-вычитателя 1 операндов подключен к выходу мультиплексора 6 первого операнда, первы информационный вход которого соедине с выходом регистра 5 результата, вто рой информационный вход мультиплексо ра б первого операнда подключен к ши не 15 нулевого потенциала устройства ауправляющий вход мультиплексора б первого операнда соединен с третьим выходом первого дешифратора 10. Второй информационный вход сумматора-вы читателя 1 операндов подключен к выходу мультиплексора 7 второго операн да, первый информационный вход которого соединен с соответственно с выходом регистра 3 множимого, второй информационный вход мультиплексора 7 второго операнда подключен- к выходу регистра 3 множимого с сдвигом влево на один разряд, а управляющий вход мультиплексора 7 второго операнда соединен с первым выходом регистра 13 управления, второй и третий выходы которого подключены к управляющим входам сумматора-вычитателя 1 операндов и суглматора-вычитателя 2 знаков. Шина 8 данных устройства сое динена с входами регистра 3 множимог и регистра 4 множителя, выходы младших разрядов которого подключены к информационному входу второго дешифратора 11, выход которого сое-. динен с информационным входом коммутатора 12, управляющий вход коьадутатора 12 подключен, к четвертому выходу регистра 13 управления, информаци онный вход которого соединен с выходом коммутатора 12, а тактовый вход регистра 13 управления подключен к входу 14 синхронизации устройства н.к тактовому входу счетчика 9, 11-2)разрядные выходы которого соединены с соответствующими информационными входами первохчэ де1иифратора 10, а первый и второй выходы первого дешифратора 10 соответственно соединены с первым и вторым управлякмгдами входами второго дешифратора 11. Второй дешифратор 11 сйдеэжит два элемента НЕ 16 и 17,элементы И 18-241 и элементы ИЛИ 25-28. Первый информационный вход второго де1иифратора 11 (п-й разряд множителя ) соединен с вторым входом элемента И 21, первый вход которого соединен с вторым управляющим входом второго дешифратора 11 и с первым входом элемента ИЛИ 28, второй вход которого подключен к пер вому управляющему входу второго дешифратора 11, ко второму входу элемента И 19 и к первому входу элемента И 24. Второй информационный вход второго дешифратора 11 {п-1)-й разряд множи- теля,) соединен с вторым входами элементов И 23 и 24, с третьим входом элемента И 20 и через элемент НЕ 17 подключен к первым входам элементов И 19 и 22 и к третьему входу элемента Н 18. Третий информационный вход второго дешифратора 11 (П-2)-й разряд множителя ) соединен с вторым входом элемента И 22, с третьим входом элемента И 23 и через элемент НЕ 16 подключен к вторым входам элементов И 19 и 20, первые входы которых соединены с выходом элемента ИЛИ 28, с третьим входом элемента VI 22 и с первым вхо- . дом элемента И 23. Выходы элементов И 18 и 19 через элемент ИЛИ 25 соединены с первым выходом второго дешифратора 11 (шина ООМ , выход . элеме1«га И 20 соединен с вторым выхот дом второго дешифратора 11 (шина 01 ), BHXOJWJ элементов И 21 и 22 через элемент ИЛИ 26 соединены с третьим выходом второго дешифратора 11 (шина 10), выходы элементов И 23 я 24 через элемент ИЛИ 27чсоединены с четвертым выходом второго дешифратора 11 (шина . Коммутатор 12 содержит э емен--..; ты И 29-35, элементы ИЛИ 36-38 и элемент НЕ 39. Первый информационный вхо (шина 00) коммутатора 12 сое-, динен с вторым входом элемента И 30, первый вход которого соединен с первыми входами элементов И 32, 34 и 35 и с управляющим входом, который через элемент НЕ 39 подключен к первым входам элементов И 29, 31, 33. Втофой информационный вход (шина 01) -коммутатора 12 соединен с вторыми входами элементов И 29 и 32, третий .информационный вход (шина 10) коммутатора 12 соединен с вторым входами элементов И 31 и 34, а четвертый информационный вход (мина 11) соединен с вторыми входами элементов И 33, и 35. Выходы элементов И 29 и 30 через элемент ИЛИ 36 подключены к первому выходу коммутатора 12 (шина 01 ), выходы элементовИ 31 и 32 через эле мент ИЛИ 37 соединен с вторым выходо коммутатора 12 (шина 10 ), выходы элементов И 33 и 34 через элемент ИЛ 38 Подключены к третьеглу. выходу коммутатора 12 (шина 11, а выход эле мента И 35 подключен к четвертому вы ходу коммутатора 12 (.шина Перенос) Регистр 13 управления содержит триггеры 40г43 и элементы ИЛИ 44 и 45 Тактовый вход регистра 13 управле ния соединен с тактовыми входами триггеров 40-43, информационные входы Которых соединены с информациойны ми входами регистра 13 управления следующим образом: вход триггера 40 соединен с вторым входом (шина 10) который сбвместно с первым входом (шина 01) через элемент ИЛИ 45 сое динен с входом триггера 41. Третий вход (шина 11) подключен К входу триггера 42, а четвертый вход (шина Перенос ) соединен с входом триггера 43. Выходы триггеров 40,41 и 42 соединены с первым, вторым и третьим выходами регистра 13 управления соот нетственно, кроме того, выход тригге ра 42 совместно.с выходом триггера 45 через элемент ИЛИ 44 соединен с четвертым выходом регистра 13 управления. Устройство для умножения работает следующим образом. Перед началом операции множимое и множитель поступают с шины 8 данных устройства на регистр 3 множимого и регистр 4 множителя. В исходном положении на первом вы ходе первого дешифратора 10 формируется сигнал нулевого состояния счетчика 9 циклов, по которому второй де шифратор 11 расшифровывает значение п-го разряда регистра 4 множителя. В исходном положении регистр 13 управления находится в нулевом состоянии. В начале первого цикла на вход 14 синхронизации поступает сигнал, по которому счетчик 9 циклов пе реходит из нулевого состояния в состояние 1., вследствие чего, на первом выходе первого дешифратора 10 сигнал исчезает, а на третьем выходе формируется сигнал первого состояния счетчика 9, поступающий на управляющий вход мультиплексора б первого операнда и обеспечивающий передачу на первый вход- сумматора-вычитателя операндов нулевого кода с шины 15 ну левого потенциала устройства. По этому же тактовому сигналу регистр 13 управления фиксирует рас1чиф jpofiaKHoe вторым дешифратором 11 и пропущенное без изменения через коммутатор 12 значение п-го разряда мно жителя. Для каждого цикла умножения вырабатываются управляющие сигналы, ,. которые хранятся на регистре 13 управления на протяжении всего цикла до прихода очередного сигнала на входе 14 синхронизации. Третий выход регистра 13 управления обеспечивает вычитание множимого из частичного произведения, второй выход регистра 13 управления управляет сложением множимого с частичным произведением на сумматоре-вычитателе 1 операндов, и первый выход регистра 13 управления управляет работой мультиплексора 7 второгр операнда (при наличии сигнала на этом вы- ходе на втор-Ы вход сумматора-вычитателя 1 операндов поступает значение множимого со сдвигом влево на один разряд) . как в перйбм цикле работа суммат1эд)а-вычитателя 1 операндов определяется COCTOHHI M п-го разряда множителя, то в первом цикле множимое или не участвует в работе сумматор а- вычита еля операндов 1, или складывается, с первые операндом (в данном случае .с йулями) со сдвигом . влево на один разряд. . -- . в первом Цикле вследствие отсутствия сигнала на первом и втором выходах первого (е14Ифратора 10 второй дешифратор 11 анализирует (п-1) и (п2)-е разряды множителя для формирования управляющих сигналов к следующему циклу работы устройства. В конце первого цикла полученное на сумматоре-вычитателе 1 операндов первое частичное произьедение поступает на регистр 5 результата со сдвигом вправо на два разряда, примем одновременно с этим по входу 14 синхронизации поступает второй сигнал, продвигаюцнй значение счетчика 9 циклов на единицу и фиксирующий результат анализа (n-l)-ro. и (п-2)-го разрядо;& множителя на регистре 13 ущэавления; происходит сдвиг множителя на регистре 4 множителя вправо на два разряда, при этом два младших разряда частичного произведения записываются в два старших разряда регистра 4 множителя, а выход двухразрядного сумматора-вычитателя 2 знаков поступает на входы двух старших разрядов регистра 5 результата. Значение счетчика 9 циклов становится равным 2, сигнал, на третьем выходе первого дешифратора 10 исчезает, мультиплексор 7 второго операнда переключается на пропускание .значения регистра 5 результата на первый вход сумматоравычитателя 1 операндов. Начиная со второго цикла и по n/2-й цикл включительно устройство работает аналогично второму циклу; расшифровка очередной пары разрядов множителя на втором дешифраторе 11с коррекцией результата анализа на коммутаторе 12 и записью скорректированного значе, ния на регистр 13 управления, полу чение очередного частичного-произве(денияна сумматоре-вычитателе 1 операндов, запись его со сдвигом вправо на два разряда в регистр 5 результата с одновременным сдвигом вправо на два разряда множителя на регистре 4 множителя (в освобождающиеся два .старших разряда регистра 5 ре зультата записывается в это время вы ход сумматора-вычитателя 2 знаков,а в освобождающиеся два старших разряда регистра 4 множителя записываются два гшадших разряда сумматора- . вычитателя 1 операндов.}. Во время выполнения п/2-го цикла знаковый разряд множителя {в результате сдвигов вправо на два разряда в каждом цикле множителя на регистре 41 . множителя) находится на месте (п -1) - го разряда. Счетчик 9. циклов к этому времени насчитывает число циклъв равное п/2 и формирует сигнал на вто ром вшсоде первогс дешифратора 10, разреи1г1Ю ций второму дешифратору 11 анализировать значение только (п-t)-го разряда. При поступлении очередного сигнала по входу 14 синхронизации регистр/ 13 управления фиксирует расшифрова ное вторым дешифратором 11 и скорректированное коммутатором 12 значение (n-l)-ro разряда множителя (знакового разряда). (п/2+1)-й цикл отличается от предыду1зих циклов тем, что полученный результат на выходе сумматора-вычитателя 1 операндов записывается- на регистр 5 результата без сдвига вправо на два разряда и сдвиг . вправо на два разряда регистра. 4 множителя не осуществляется. Таким .образом, полученное произведение (2п-разрядное) распогалается на регистре 5 результата (старшая часть) и на регистре 4 множителя (мпадная часть). Как показал схемно-техническйй анализ,, предлагаемое устройство для умножения по сравнению с прототигюм позволяет сократить оборудование за счет исключения регистра переноса, двух буферных регистров,группы элементов И-ПЕ и 6floKk управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1982 |

|

SU1136151A1 |

| Устройство для выполнения операций умножения и деления | 1980 |

|

SU955038A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Арифметическое устройство | 1988 |

|

SU1578708A1 |

| Процессор для обработки массивов данных | 1982 |

|

SU1381532A1 |

| Устройство для выполнения операций умножения и деления | 1986 |

|

SU1403061A1 |

| Устройство для умножения | 1976 |

|

SU651341A1 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

| Число-импульсное арифметическое устройство | 1980 |

|

SU951303A1 |

| Устройство управления микропроцессором | 1983 |

|

SU1156072A1 |

УСТЮЙСТВО ДЛЯ УМНОЖЕНИЯ, содержаыее регистр множимого, регистр) МИожителй, регистр результата, суммаг тор- вычитатель операндов и счетчик/ причем входная ишна данных соответственно соединена с входами регистра множимого и регистра множители, а - разрядные выходы сумматора-вычитателя собтветстйенно соединены с разрядными входаМи регистра результата, о т л и ч а ю щ ее с я Гем) что, с целью упрощения, в него введены дЬухрйзрядный сумматор-вЫчитатель зйакоб мультиплексоры ПервогЬ н второгоohe рандон, первый и второй диииФраторы, коммутатор и регистр управления,причем вход синхронизации устройства соединен с тактовыми входами регистра ; управления и счётчика, { li.l-fi/2)-pa3рядные выходы счетчика соединены с COOT вет ст вующими и нформацион ными входами первого дешифратора выход Дешифрации нулевого и Н/2-ГО состояния счетчика соответственно соединен с первым- и вторим управлякидико входами второго дешифратора, а йыход даиифрйции nepBoIo состояния счетчика соединен с управляющим входом мультиплексора перво операнда, информационные входы второго донифратора соответственно соединены с выходами Tpeji младших разрядов регистра множителя, входы двух старших разрядов которого соответственно соединены С выходами двух мпадших разрядов сумматора-вычи;тателя операндов, выходы остальных разрядов cyNMaTopa-шдчитателя операн:дов дополнительно соединены с раз;рЯдными входами регистра результата со сдвигом вправо на два разряда, дйа старваих входных разряда регистре результата соединены Соответственно ,. с разрядными выходами сумматора-вычйтатёля знаков, вход ст.аршего разряда .которого соединен с выходом старшего разряда регистра Множимого, а вход ;млад1:аего разряда - с выходом старшего разряда регистра результата,вход переноса сумматора-вычитателя знаков соединен с выходом переполнения сумi Матора-вйчитателя операндов, информа;ционные входы которого соединены соГответствейно с выходами мультиплек,соров первого и второго операндов, Гпервая группа входов мультиплексора .первого операнда соединена сортветст; венно с paзpядны вt выходами регнс -ра результата, вторая группа .мультиплексора первого операнда соединена с шиной нулевого потенциала, первая группа входов мультиплексора N N3 У1 второго.операнда соединена соответственно с разрядными выходами регистра множимого, вторая группа-входов мульi типлексор Звторогр операнда соадине- на с разрядными выходами регистра множимого со сдвигом влево,на один : разряд, а управлякяций вход соединен I первым выходом регистра управления, : второй и третий выходы которого соединены соответственно с управляющими входами сумматора-вычитателя операндов и сумматора-вычитателя знаков, четвертый выход регистра управления ;соединен с управляющим Ьходом комму татОра, информационный вход которого соединенс выходом второго дешифратора / а выход коммутатора соединен с .информационным входом регистра управления.

..

fin.l

.J

Г

Ыл

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для умножения двоичных чисел | 1973 |

|

SU482741A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для умножения | 1975 |

|

SU555401A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| (прототип) . | |||

| - | |||

Авторы

Даты

1983-04-15—Публикация

1981-07-10—Подача