СЛ

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отображения символьной информации на экране видеоконтрольного блока | 1991 |

|

SU1836678A3 |

| Синхрогенератор | 1989 |

|

SU1672586A1 |

| УСТРОЙСТВО ДЛЯ ДИАГНОСТИРОВАНИЯ ТЕЛЕВИЗИОННОЙ АППАРАТУРЫ | 1989 |

|

RU2050700C1 |

| Устройство для отображения информации на экране телевизионного приемника | 1987 |

|

SU1494778A1 |

| Устройство для отображения информации на экране цветного видеоконтрольного блока | 1988 |

|

SU1529280A1 |

| УСТРОЙСТВО ДЛЯ ОТОБРАЖЕНИЯ ИНФОРМАЦИИ НА ЭКРАНЕ ТЕЛЕВИЗИОННОГО ИНДИКАТОРА | 1991 |

|

RU2018977C1 |

| Устройство для отображения информации на экране телевизионного приемника | 1985 |

|

SU1367036A1 |

| Устройство для отображения объектов | 1985 |

|

SU1288937A1 |

| Устройство для контроля видеосигнала | 1982 |

|

SU1069190A1 |

| Телевизионное устройство для обнаружения движущихся объектов | 1986 |

|

SU1385331A1 |

Изобретение относится к телевидению. Целью изобретения является расширение функциональных возможностей путем вывода изображения постречного разложения с полуформатной ПЗС матрицы на весь экран стандартного видеоконтрольного устройства. Поставленная цель достигается введением в синхрогенератор последовательно соединенных блока коммутации 5, первого счетчика импульсов 6, второго счетчика импульсов 7 и триггера 9, а также блока памяти 8, причем М адресных входов блока памяти 8 соединены с соответствующими адресными выходами первого счетчика 6, выход триггера 9 соединен с третьим входом блока коммутации 5, (М + 1)-м входом блока памяти 8 и вторым входом второго счетчика 7, a (N + 1)-й выход блока памяти 8 соединен с вторыми входами первого счетчика 6 и триггера 9. 5 ил.

Фиг.1

vj ю

00 CJ

Ю

Изобретение относится к телевидению, в частности к синхрогенераторам систем технического зрения, и преимущественно может быть использовано в передающих телевизионных камерах на твердотельных многоэлементных преобразователях свет - сигнал с числом строк разложения изображения существенно меньшим относительно установленного стандартом.

Известен синхрогенератор, содержащий тактовый генератор, два счетчика, два формирователя установочных кодов, два формирователя установки синхросигнала, четыре дешифратора и два формирователя импульсов.

Недостаток синхрогенератора в том, что реализованный в нем стандарт разложения изображения накладывает ограничения на область применения, так при выводе изображения на экран стандартного видеоканального устройства либо бытового телевизора с телевизионной камеры с преобразователем свет - сигнал с малым числом строк разложения изображение занимает лишь половину экрана и меньше.

Известен синхрогенератор, содержащий тактовый генератор, два счетчика импульсов, два делителя частоты, мультиплексор, два блока памяти и два регистра. Синхрогенератор предназначен для использования в составе передающей части телевизионных систем.

Недостаток синхрогенератора - ограниченная область применения, так как непосредственно невозможно использовать его в передающей части, например, систем технического зрения с телекамерами на ПЗС-матрицах.

Наиболее близким к предлагаемому является синхрогенератор, содержащий генератор тактовых импульсов, управляемый делитель частоты, два делителя частоты, компаратор, два элемента совпадения и реверсивный счетчик. Синхрогенератор формирует последовательности строчных и кадровых синхроимпульсов и обеспечивает жесткую привязку частот кадровых и строчных синхроимпульсов к частоте напряжения питающей сети.

Недостатком известного синхрогенератора является невозможность его применения в передающей части телевизионных систем с телевизионными камерами, где в качестве преобразователя свет - сигнал применяются полуформатные ПЗС-матри- цы.

Целью изобретения является расширение функциональных возможностей путем вывода изображений построчного разложения с полуформатной ПЗС-матрицы на весь

экран стандартного видеоконтрольного устройства.

Указанная цель достигается тем, что в синхрогенератор введены блок коммутации, первый вход которого соединен с выходом первого делителя частоты и входом второго делителя частоты, а второй вход - с выходом второго делителя частоты, первый счетчик импульсов, первый вход которого

0 подключен к выходу блока коммутации, второй счетчик импульсов, подключенный первым входом к разряду переполнения первого счетчика импульсов, блок памяти, М адресных входов которого подключены к со5 ответствующим разрядным выходам первого счетчика, триггер, первый вход которого подключен к выходу второго счетчика импульсов, а выход подключен к второму входу второго счетчика импульсов, к (М + 1)-му

0 входу блока памяти, к управляющему входу блока коммутации, при этом N выходов блока памяти являются выходами устройства, а ( N+1 )-й выход подключен к второму входу триггера и второму входу первого счетчика

5 импульсов.

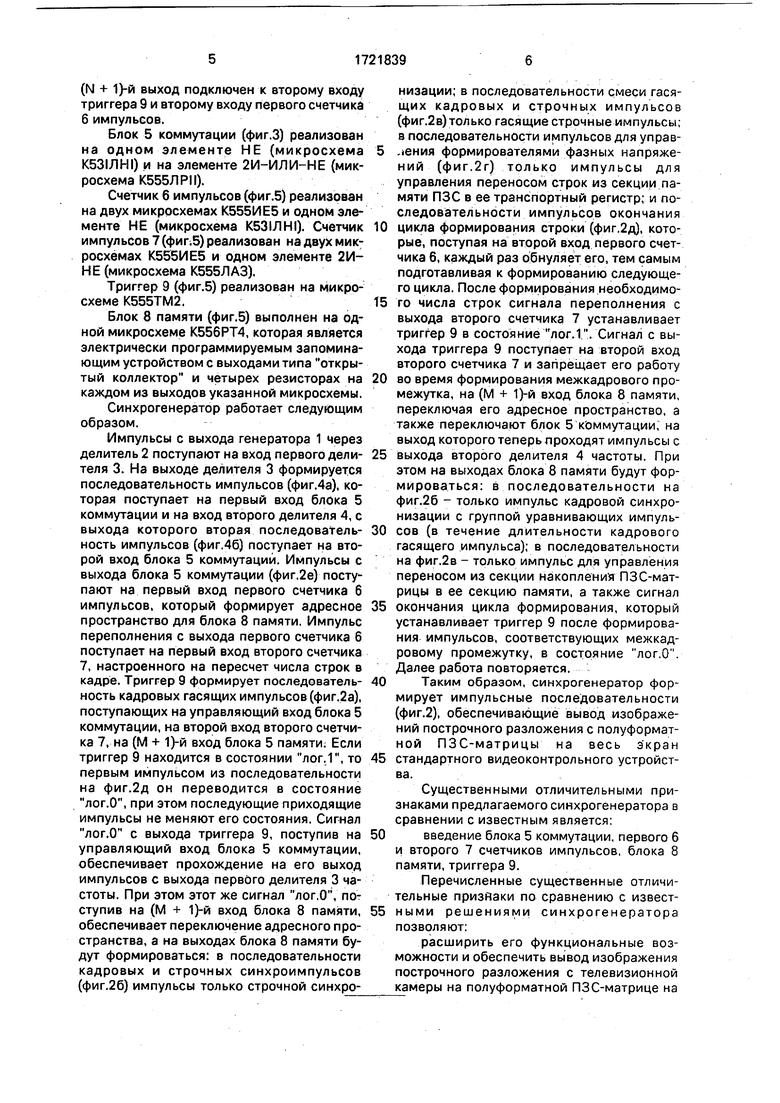

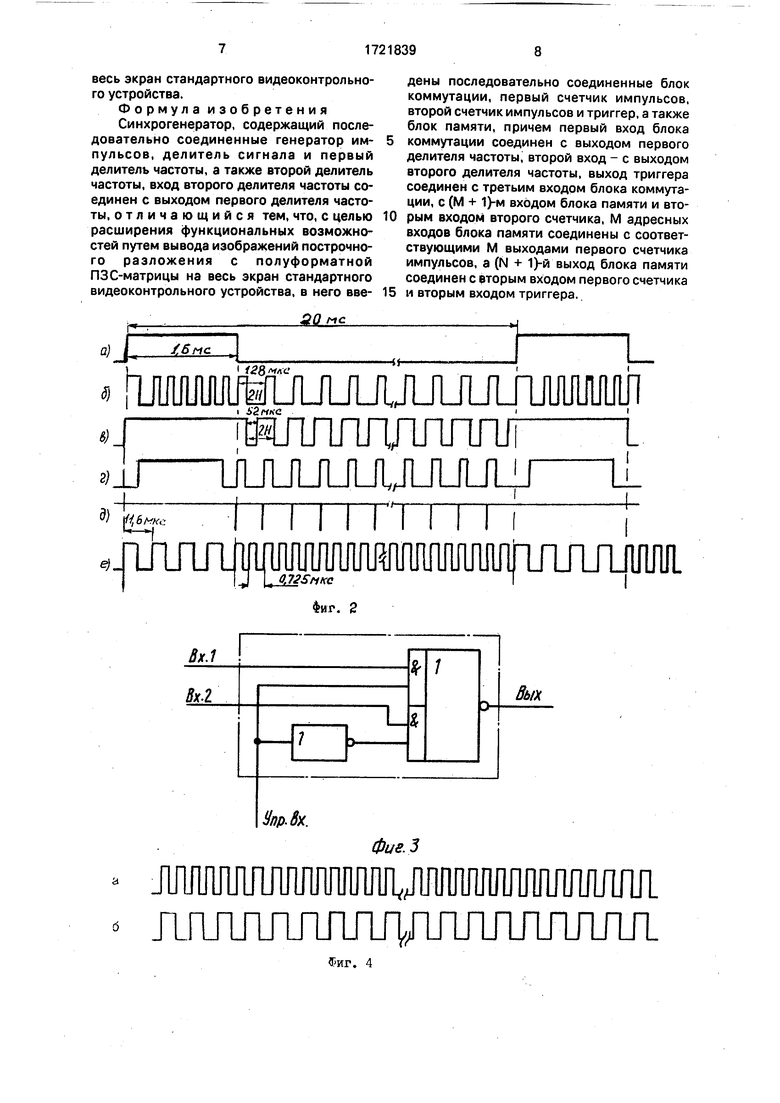

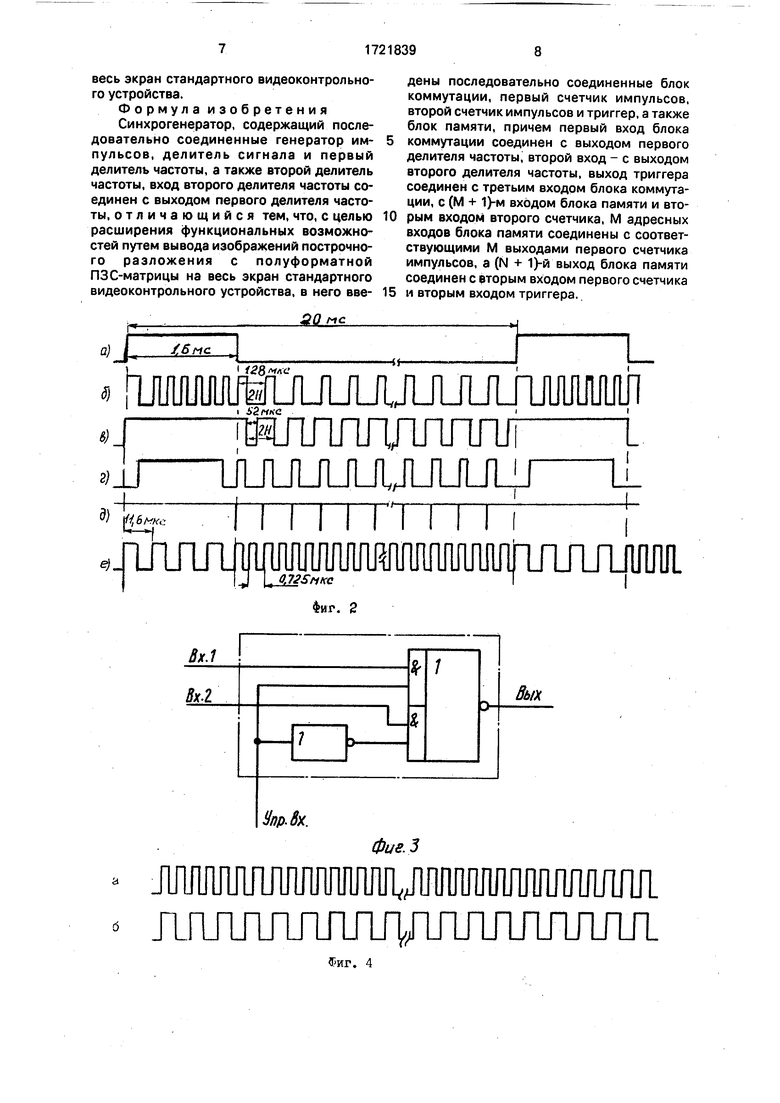

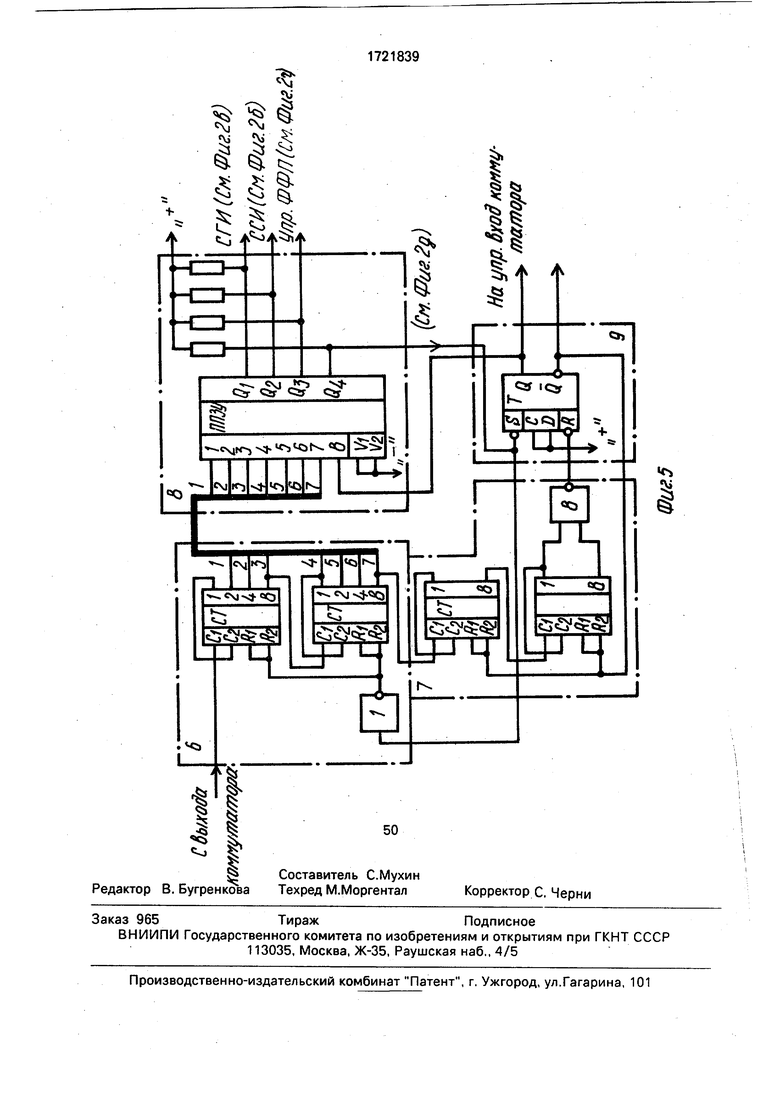

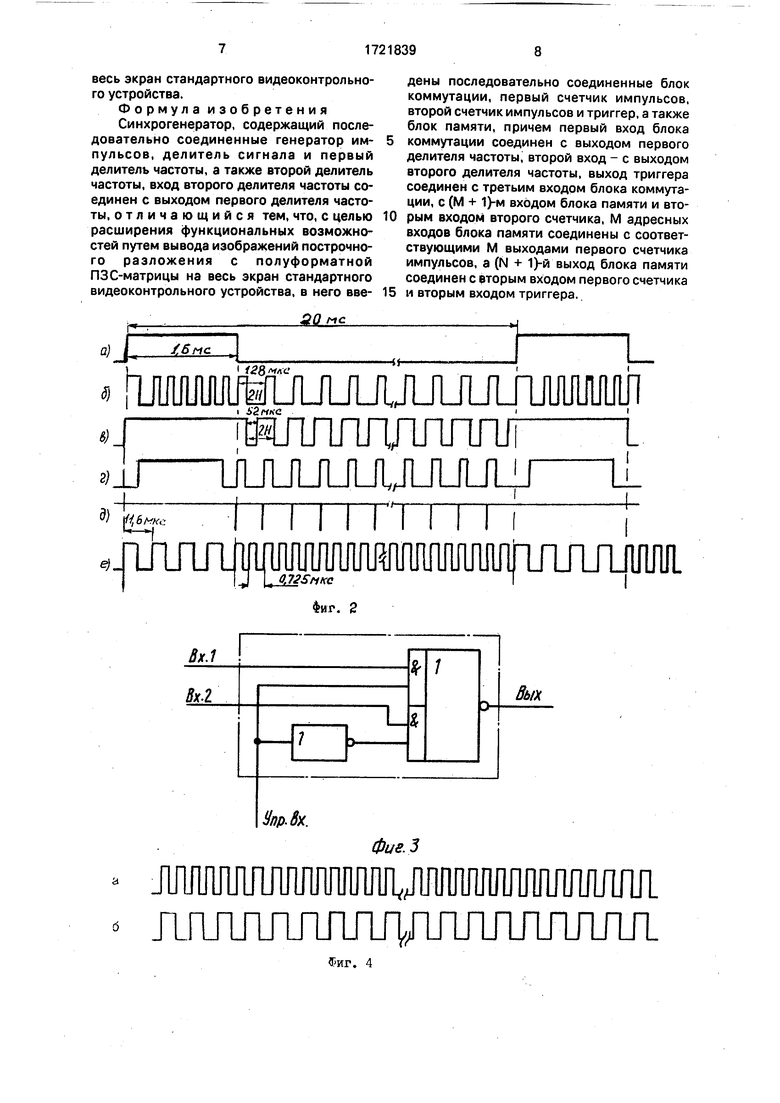

На фиг.1 приведена структурная схема синхрогенератора; на фиг.2 - диаграммы временных последовательностей импульсов; на фиг.З - блок коммутации; на фиг.4 0 последовательности импульсов, формируемые первым и вторым делителями частоты; на фиг.5 - блок памяти и его взаимосвязи. Синхрогенератор содержит генератор 1 импульсов, делитель 2, первый 3 и второй 4

5 делители частоты, блок 5 коммутации, первый б и второй 7 счетчики импульсов, блок 8 памяти, триггер 9.

Генератор 1 своим выходом подключен к входу делителя 2. Выход делителя 2 соеди0 нен с входом первого делителя 3 частоты, вход которого соединен с входом второго делителя 4 частоты. Первый вход блока 5 коммутации соединен с выходом первого делителя 3 частоты и входом второго дели5 теля 4 частоты, а второй вход - с выходом второго делителя 4 частоты. Первый вход первого счетчика б импульсов подключен к выходу блока 5 коммутации. Второй счетчик

7импульсов подключен своим первым вхо- 0 дом к разряду переполнения первого счетчика 6 импульсов. М адресных входов блока

8памяти подключены к соответствующим разрядным выходам первого счетчика 6. Триггер 9, первый вход которого подключен

5 к выходу второго счетчика 7 импульсов, а выход подключен к второму входу второго счетчика 7 импульсов, к (М + 1)-му входу блока 8 памяти, к управляющему входу блока 5 коммутации, при этом N выходов блока 8 памяти являются выходами устройства, а

(N + 1)-й выход подключен к второму входу триггера 9 и второму входу первого счетчики б импульсов.

Блок 5 коммутации (фиг.З) реализован на одном элементе НЕ (микросхема К531ЛН1) и на элементе 2И-ИЛИ-НЕ (микросхема К555ЛРН).

Счетчик б импульсов (фиг.5) реализован на двух микросхемах К555ИЕ5 и одном элементе НЕ (микросхема К531ЛHI). Счетчик импульсов 7 (фиг.5) реализован на двух микросхемах К555ИЕ5 и одном элементе 2И- НЕ (микросхема К555ЛA3).

Триггер 9 (фиг.5) реализован на Микросхеме К555ТМ2.

Блок 8 памяти (фиг.5) выполнен на одной микросхеме К556РТ4, которая является электрически программируемым запоминающим устройством с выходами типа открытый коллектор и четырех резисторах на каждом из выходов указанной микросхемы.

Синхрогенератор работает следующим образом.

Импульсы с выхода генератора 1 через делитель 2 поступают на вход первого делителя 3. На выходе делителя 3 формируется последовательность импульсов (фиг.4а), которая поступает на первый вход блока 5 коммутации и на вход второго делителя 4, с выхода которого вторая последовательность импульсов (фиг.4б) поступает на второй вход блока 5 коммутации. Импульсы с выхода блока 5 коммутации (фиг.2е) поступают на первый вход первого счетчика б импульсов, который формирует адресное пространство для блока 8 памяти. Импульс переполнения с выхода первого счетчика б поступает на первый вход второго счетчика 7, настроенного на пересчет числа строк в кадре. Триггер 9 формирует последовательность кадровых гасящих импульсов (фиг.2а), поступающих на управляющий вход блока 5 коммутации, на второй вход второго счетчика 7, на (М + 1)-й вход блока 5 памяти: Если триггер 9 находится в состоянии лог.1, то первым импульсом из последовательности на фиг.2д он переводится в состояние лог.О, при этом последующие приходящие импульсы не меняют его состояния. Сигнал лог.О с выхода триггера 9, поступив на управляющий вход блока 5 коммутации, обеспечивает прохождение на его выход импульсов с выхода первйго делителя 3 частоты. При этом этот же сигнал лог.О, поступив на (М + 1)-й вход блока 8 памяти, обеспечивает переключение адресного пространства, а на выходах блока 8 памяти будут формироваться: в последовательности кадровых и строчных синхроимпульсов (фиг.2б) импульсы только строчной синхронизации; в последовательности смеси гасящих кадровых и строчных импульсов (фиг.2в) только гасящие строчные импульсы; в последовательное™ импульсов для управ,,ения формирователями фазных напряжений (фиг.2г) только импульсы для управления переносом строк из секции памяти ПЗС в ее транспортный регистр; и последовательности импульсов окончания

0 цикла формирования строки (фиг.2д), которые, поступая на второй вход первого счетчика 6, каждый раз обнуляет его, тем самым подготавливая к формированию следующего цикла. После формирования необходимо5 то числа строк сигнала переполнения с выхода второго счетчика 7 устанавливает триггер 9 в состояние лог.1. Сигнал с выхода триггера 9 поступает на второй вход второго счетчика 7 и запрещает его работу

0 во время формирования межкадрового промежутка, на (М + 1)й вход блока 8 памяти, переключая его адресное пространство, а также переключают блок 5 коммутации, на выход которого теперь проходят импульсы с

5 выхода второго делителя 4 частоты. При этом на выходах блока 8 памяти будут формироваться: в последовательности на фиг.2б - только импульс кадровой синхронизации с группой уравнивающих импуль0 сов (в течение длительности кадрового гасящего импульса); в последовательности на фиг.2в - только импульс для управления переносом из секции накоплений ПЗС-мат- рицы в ее секцию памяти, а также сигнал

5 окончания цикла формирования, который устанавливает триггер 9 после формирования импульсов, соответствующих межкадровому промежутку, в состояние лог.О. Далее работа повторяется.

0 Таким образом, синхрогенератор формирует импульсные последовательности (фиг.2), обеспечивающие вывод изображений построчного разложения с полуформатной ПЗС-матрицы на весь э кран

5 стандартного видеоконтрольного устройства.

Существенными отличительными признаками предлагаемого синхрогенератора в сравнении с известным является:

0введение блока 5 коммутации, первого 6

и второго 7 счетчиков импульсов, блока 8 памяти, триггера 9.

Перечисленные существенные отличительные признаки по сравнению с извест5 ными решениями синхрогенератора позволяют:

расширить его функциональные возможности и обеспечить вывод изображения построчного разложения с телевизионной камеры на полуформатной ПЗС-матрице на

весь экран стандартного видеоконтрольного устройства.

Ф о р м у л а и з о б р е т е н и я Синхрогенератор, содержащий последовательно соединенные генератор импульсов, делитель сигнала и первый делитель частоты, а также второй делитель частоты, вход второго делителя частоты соединен с выходом первого делителя частоты, отличающийся тем, что, с целью расширения функциональных возможностей путем вывода изображений построчного разложения с полуформатной ПЗС-матрицы на весь экран стандартного видеоконтрольного устройства, в него вве.- ...,c

gj, j„IL

tamjfi

i i 2«« C

0

Ш1ЛЛЛДГ1Г1ГиГ

,jj-шиции олиш

d) Шнкс

W |

31ПЛА

iniwuiw

J 0.72SMKCII

Фиг. 2

ВхЛ

8x2

Упр.8х.

Ж1МПШШШ1ШЩДШ11ШШШ1Ш1ЛЯЛ ЛГШЛЛ1ШЩДШҐ1ЛЯГ1Г1Л

Фиг. 4

0

дены последовательно соединенные блок коммутации, первый счетчик импульсов, второй счетчик импульсов и триггер, а также блок памяти, причем первый вход блока коммутации соединен с выходом первого делителя частоты, второй вход - с выходом второго делителя частоты, выход триггера соединен с третьим входом блока коммутации, с (М + 1)-м входом блока памяти и вторым входом второго счетчика, М адресных входов блока памяти соединены с соответствующими М выходами первого счетчика импульсов, a (N + 1)-й выход блока памяти соединен с вторым входом первого счетчика и вторым входом триггера.

Вш

Фие.З

$

§§i

$ $ Ј

t i

sst

Ј

I

, xh r 5y Qg

.)

.

C4J

Г)

4i

«M

Ъ

.

JJpQr Г

ill±n г

-gyjsb

1721839

I

U

Ч

4

i

:

f1

U

±n г

.J

«CJ

i..j

i

I

1

| Синхрогенератор | 1985 |

|

SU1252971A1 |

| кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Прибор для получения стереоскопических впечатлений от двух изображений различного масштаба | 1917 |

|

SU26A1 |

| Патрон для двухступенчатого сверла | 1958 |

|

SU119053A1 |

| кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1992-03-23—Публикация

1989-07-11—Подача