налах и относительно высокая эксплуатационная нестабильность задержек.

Наиболее близким по технической сущности к предлагаемому является программируемое устройство выравнивания задержки, содержащее К одинаковых каналов задержки, каждый из которых имеет свой информационный вход и выход, к выходу К-го канала подключен первый вход блока определения величины нестабильности, второй вход последнего соединен с входом эталонного сигнала, а также генератор импульсов, выход которого соединен с входом опорного канала и первым входом блока определения величины нестабильности, выполненного в виде компаратора преобразователя время - напряжение, второй вход которого подключен к выходу опорного канала, а выход соединен с одним из входов компаратора, другой вход которого соединен с источником управляющего напряжения, причем выход компаратора подключен к шине питания опорного и информационных каналов.

Недостатками этой схемы является относительно невысокая точность задержек, определяемая наличием в схеме двух эталонов различного типа - цифрового (период генератора) и аналогового (управляющее напряжение), невозможность раздельной регулировки (выравнивания), задержек между различными каналами. Другим недостатком известной схемы является то, что напряжение питания каналов является принципиально изменяемым (нестабильным), что приводит к возможному рассогласованию сигналов по уровню на входах и выходах устройства, что ограничивает ее функциональные возможности.

Цель изобретения - повышение точности выравнивания величины задержки и обеспечение программно независимой для каждого канала начальной установки величины задержки.

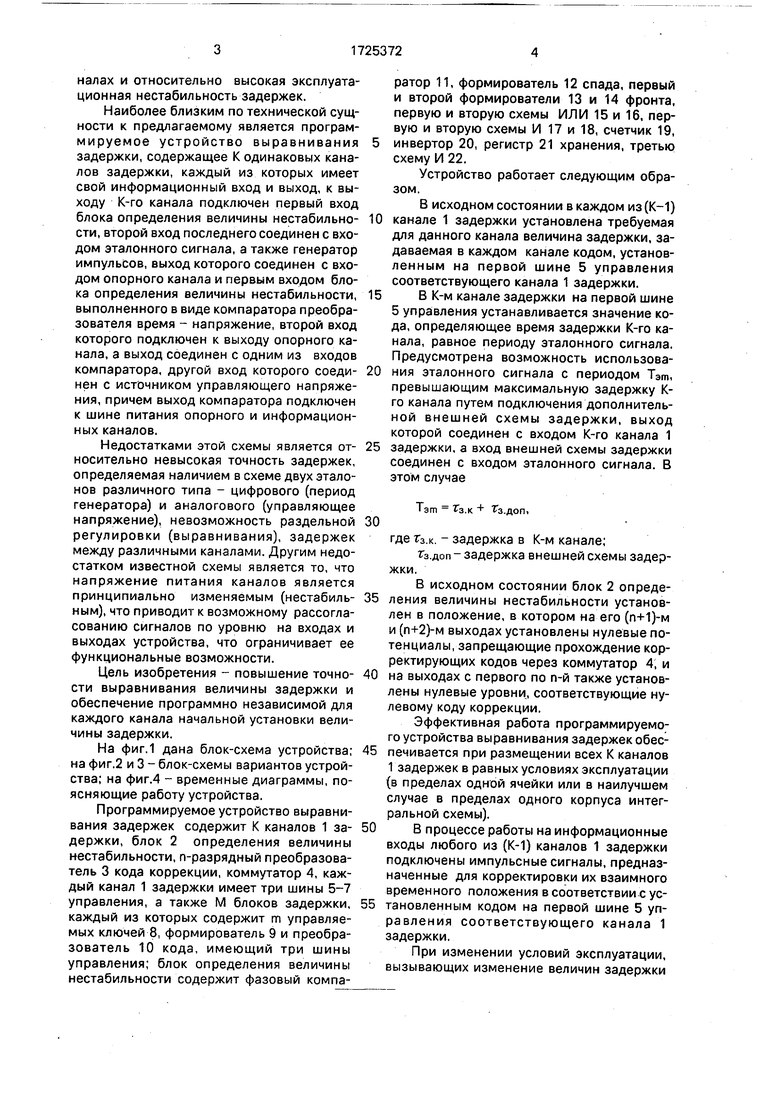

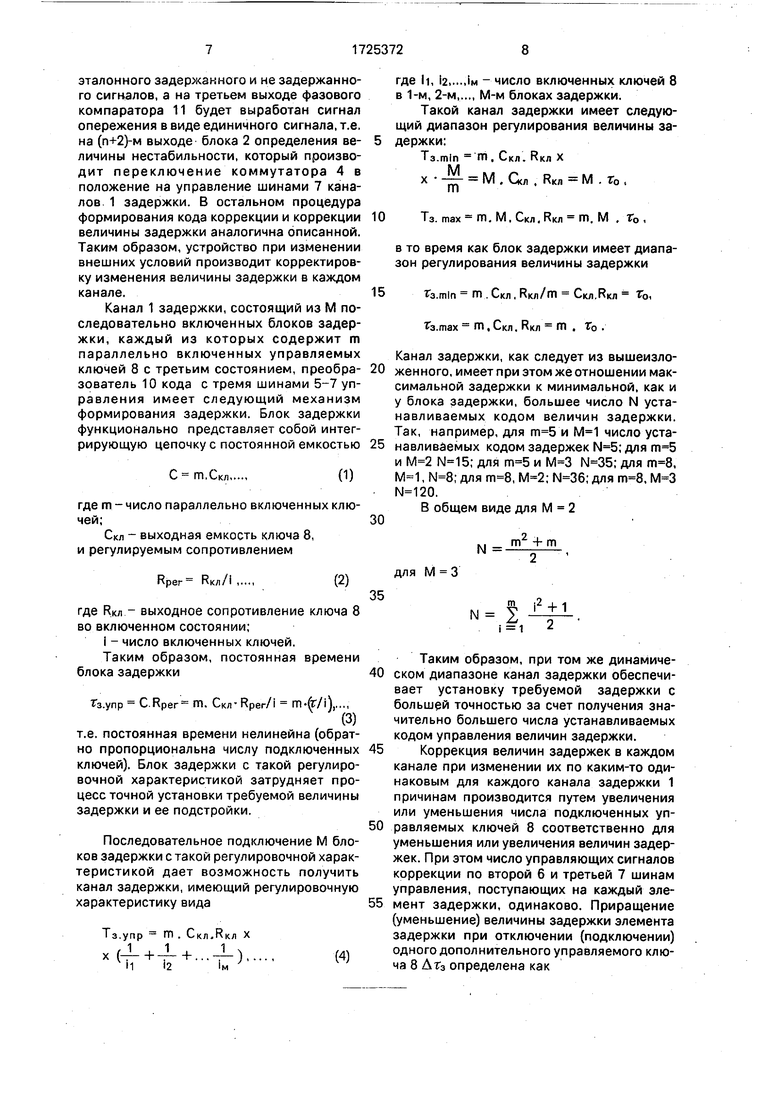

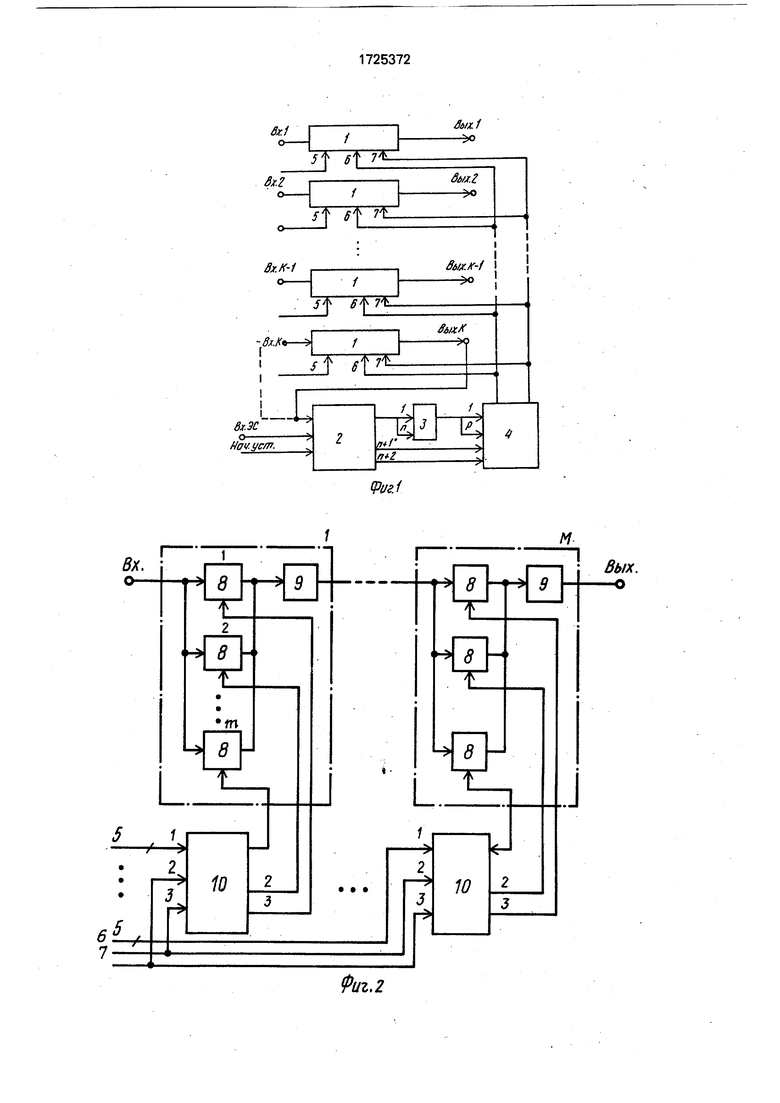

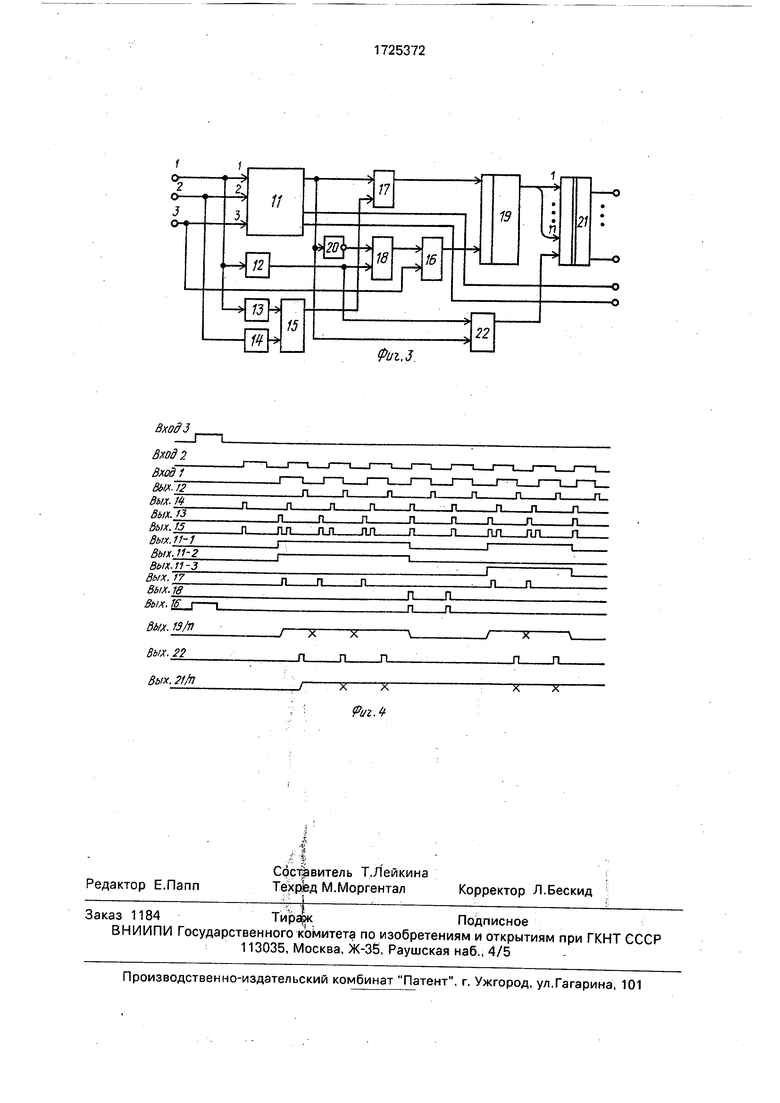

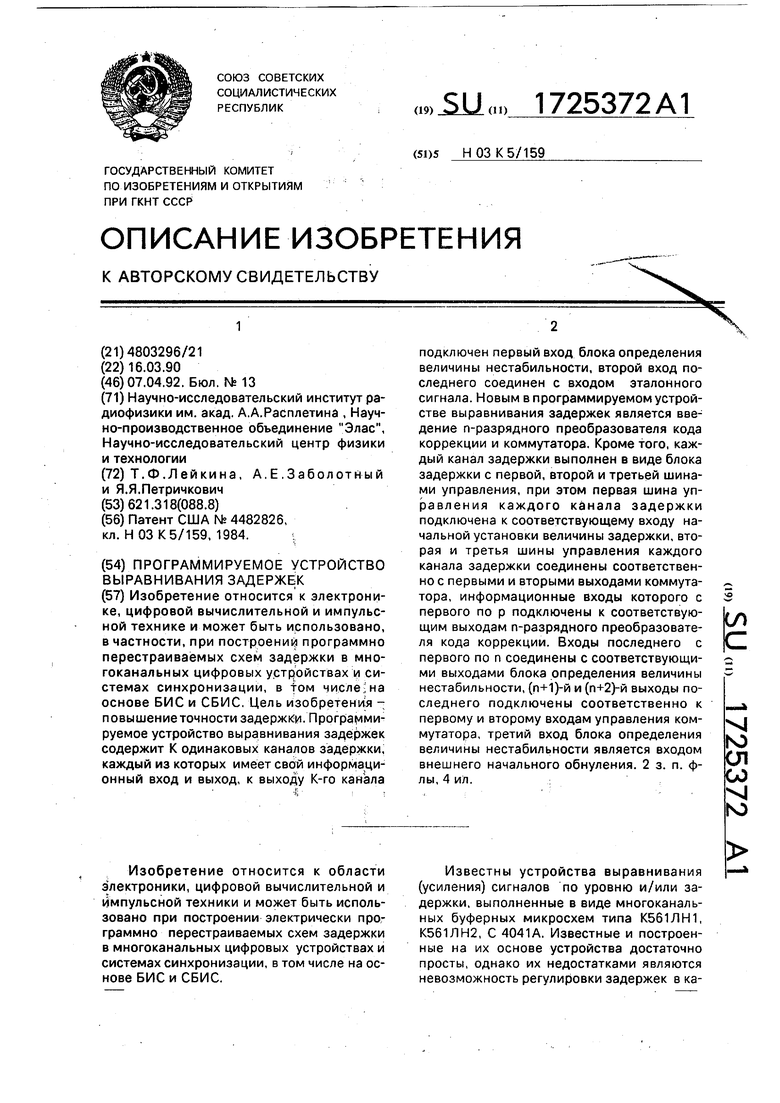

На фиг,1 дана блок-схема устройства; на фиг.2 и 3 - блок-схемы вариантов устройства; на фиг.4 - временные диаграммы, поясняющие работу устройства.

Программируемое устройство выравнивания задержек содержит К каналов 1 задержки, блок 2 определения величины нестабильности, n-разрядный преобразователь 3 кода коррекции, коммутатор 4, каждый канал 1 задержки имеет три шины 5-7 управления, а также М блоков задержки, каждый из которых содержит m управляемых ключей 8, формирователь 9 и преобразователь 10 кода, имеющий три шины управления; блок определения величины нестабильности содержит фазовый компаратор 11, формирователь 12 спада, первый и второй формирователи 13 и 14 фронта, первую и вторую схемы ИЛИ 15 и 16, первую и вторую схемы И 17 и 18, счетчик 19,

инвертор 20, регистр 21 хранения, третью схему И 22.

Устройство работает следующим образом.

В исходном состоянии в каждом из (К-1)

канале 1 задержки установлена требуемая для данного канала величина задержки, задаваемая в каждом канале кодом, установленным на первой шине 5 управления соответствующего канала 1 задержки.

В К-м канале задержки на первой шине 5 управления устанавливается значение кода, определяющее время задержки К-го канала, равное периоду эталонного сигнала. Предусмотрена возможность использования эталонного сигнала с периодом Тэт, превышающим максимальную задержку К- го канала путем подключения дополнительной внешней схемы задержки, выход которой соединен с входом К-го канала 1

задержки, а вход внешней схемы задержки соединен с входом эталонного сигнала. В этом случае

30

Тэт - Тз.к з.до

где Т3.к. - задержка в К-м канале;

Тз.доп - задержка внешней схемы задержки,

В исходном состоянии блок 2 определения величины нестабильности установлен в положение, в котором на его (п+1)-м и (п+2)-м выходах установлены нулевые потенциалы, запрещающие прохождение корректирующих кодов через коммутатор 4, и

на выходах с первого по n-й также установлены нулевые уровни, соответствующие нулевому коду коррекции.

Эффективная работа программируемого устройства выравнивания задержек обеспечивается при размещении всех К каналов 1 задержек в равных условиях эксплуатации (в пределах одной ячейки или в наилучшем случае в пределах одного корпуса интегральной схемы).

В процессе работы на информационные входы любого из (К-1) каналов 1 задержки подключены импульсные сигналы, предназначенные для корректировки их взаимного временного положения в соответствии с установленным кодом на первой шине 5 управления соответствующего канала 1 задержки.

При изменении условий эксплуатации, вызывающих изменение величин задержки

в К каналах 1 задержки, например, в сторону увеличения, увеличится величина задержки К-ro канала 1 задержки, например, на AtaKi, в результате этого на первом входе блока 2 определения величины нестабильности т.е. и на первом входе фазового ком- паратора 11 появится задержанный эталонный сигнал на величину, большую Тэт, т.е. позже эталонного сигнала, поступающего на второй вход фазового компаратора 11. Последний вырабатывает сигнал несовпадения сигналов во времени на первом и втором входах фазового компаратора 11, что соответствует появлению на его первом входе единичного сигнала, вырабатывается сигнал несовпадения-запаздывания, чему соответствует единичный сигнал на втором выходе компаратора 11, т.е. и на (п+1)-м выходе блока 2 определения величины нестабильности, который устанавливает коммутатор 4 в положение на управление шинами 6 каналов 1 задержки. Сигналы с первого и второго входов последнего поступают также на входы формирователя 12 спада, первого 14 и второго 13 формирователей фронта.

Выделенные в формирователях 13 и 14 фронта фронты этих сигналов, пройдя через первую схему ИЛИ 15, поступают на второй вход второй схемы И 17, которая пропустит только фронт запаздывающего сигнала, так как сигнал разрешения на ее первом входе или сигнал на первом выходе фазового компаратора 11 появится лишь в соответствии с запаздывающим сигналом на входах последнего. Сигнал с выхода второй схемы И 17, поступая на счетный вход счетчика 19, изменяет его состояние, т.е. изменяется код на информационных входах регистра 21 хранения. Импульс спада при наличии сигнала рассогласования на первом входе третьей схемы И 22 проходит через последнюю на вход записи регистра 21 хранения, т.е. происходит запоминание состояния счетчика 19. Таким образом и на выходах с первого по n-й блока определения величины нестабильности изменился код (появился код коррекции), который в n-разрядном преобразователе 3 кода коррекции «преобразуется 1. В рассматриваемый момент работы устройства на входе n-разрядного преобразователя кода коррекции 3 появился код 1 и соответственно на выходе последнего появился единичный сигнал лишь на одном из выходов. Этот сигнал, пройдя в соответствии с положением коммутатора 4 на входы второй шины 6 управления каждого канала 1 задержки, изменит (увеличит) число подключенных ключей 8 в каждом канале 1 задержки на один.

Это вызовет уменьшение величин задержки в каждом канале задержки, в том числе и в К-м канале задержки, например на Дт, т.е. величина задержки в К-м канале станет рав- ной

1з.к. Тэт + АТзк,-Ata.Kg .

Если At3.K, - At3.K4 О, то следующий

эталонный сигнал, пройдя К-й канал 1 задержки, вновь окажется запаздывающим относительно эталонного сигнала. Фазовый компаратор 11 подтвердит свое состояние, т.е. на выходе второй схемы И 17 появится

следующий счетный импульс, а счетчик 19 увеличит значение кода на своем выходе, которое, запишется импульсом спада в регистр 21 хранения. Это вызовет изменение на единицу в сторону увеличения значения

кода на входах n-разрядного преобразователя 3 кода еще на единицу, т.е. и числа единиц на его выходах тоже на единицу, в том числе и на выходах коммутатора 4, на входах второй шины 6 управления каждого

канала 1 задержки. Это вызовет подключение еще одного ключа 8 в каждом элементе задержки, т.е. уменьшение величины задержки каждого элемента задержки каждого канала 1 задержки. Пусть при этом величина

задержки К-го канала уменьшится теперь на величину АТз.к,.

При Дг3.к At3.K4- А Т.зк3 0 фазовый компаратор 11 вырабатывает сигнал совпадения задержанного и не задержанного эталонных сигналов, т.е. нулевой сигнал на своем первом выходе, запрещающий прохождение счетных импульсов на счетный вход счетчика 19. При этом на первом входе первой схемы И 18 появится сигнал разрешения прохождения сигнала спада задержанного эталонного сигнала, полученного на выходе формирователя 12 спада, который, пройдя через вторую схему ИЛИ 16, обнуляет счетчик 19. .Одновременно сигнал

совпадения запрещает прохождение сигнала спада с выхода формирователя 12 спада через третью схему И 22 и на вход записи регистра 21 хранения. В результате на его выходах сохраняется код коррекции до тех

пор, пока не возникнет вновь сигнал рассогласования, при наличии которого процедура формирования кода коррекции повторится.

При At3.K4- At3.Kt- At 3.Kj 0 эталонный

сигнал, пройдя К-й канал 1 задержки, окажется опережающим относительно эталонного сигнала. Фазовый компаратор 11 выработает на своем первом выходе единичный сигнал несовпадения во времени

эталонного задержанного и не задержанного сигналов, а на третьем выходе фазового компаратора 11 будет выработан сигнал опережения в виде единичного сигнала, т.е. на (п+2)-м выходе блока 2 определения величины нестабильности, который производит переключение коммутатора 4 в положение на управление шинами 7 каналов. 1 задержки. В остальном процедура формирования кода коррекции и коррекции величины задержки аналогична описанной. Таким образом, устройство при изменении внешних условий производит корректировку изменения величины задержки в каждом канале.

Канал 1 задержки, состоящий из М последовательно включенных блоков задержки, каждый из которых содержит m параллельно включенных управляемых ключей 8 с третьим состоянием, преобразователь 10 кода с тремя шинами 5-7 управления имеет следующий механизм формирования задержки. Блок задержки функционально представляет собой интегрирующую цепочку с постоянной емкостью

С т.Ск

(D

где т - число параллельно включенных ключей;

Скл выходная емкость ключа 8, и регулируемым сопротивлением

где И, - число включенных ключей 8

в 1-м, 2-м,..., М-м блоках задержки.

Такой канал задержки имеет следующий диапазон регулирования величины за- держки:

Ta.mln П1. Скл. RIUI X

М М . Ол . R™ М . То ,

х

m

Т3. max m. М. Скл. Ркл т. М , То ,

в то время как блок задержки имеет диапазон регулирования величины задержки

Ta.min V- Скл . Rioi/fn Скл.Ркл То, Тз.глах т. Скл. RWI ITI . То .

Канал задержки, как следует из вышеизло- женного, имеет при этом же отношении максимальной задержки к минимальной, как и у блока задержки, большее число N устанавливаемых кодом величин задержки. Так, например, для и число уста- навливаемых кодом задержек для и для и для , , для , для , .

В общем виде для М 2

N

т2 + т

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для многоканальной магнитной записи и воспроизведения сигналов с коррекцией временных искажений | 1990 |

|

SU1777178A1 |

| Устройство для многоканальной магнитной записи и воспроизведения сигналов с коррекцией временных искажений | 1990 |

|

SU1783577A2 |

| КАЛИБРОВОЧНОЕ УСТРОЙСТВО ДЛЯ УЛЬТРАЗВУКОВОГО РАСХОДОМЕРА | 1995 |

|

RU2082951C1 |

| Цифровой фазометр | 1983 |

|

SU1155957A1 |

| Устройство для функционального контроля больших интегральных схем | 1990 |

|

SU1798743A1 |

| ПРИЕМНИК ИМПУЛЬСНЫХ РАДИОСИГНАЛОВ И ИЗМЕРИТЕЛЬ УРОВНЯ ДЛЯ НЕГО | 1996 |

|

RU2097922C1 |

| Устройство для автоматического контроля больших интегральных схем | 1986 |

|

SU1529220A1 |

| Устройство для передачи частотно-временных сигналов | 1991 |

|

SU1818619A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2020565C1 |

| Интегрирующий аналого-цифровой преобразователь | 1985 |

|

SU1279069A1 |

R

регIWI

(2)

где Ккл.- выходное сопротивление ключа 8 во включенном состоянии;

i - число включенных ключей.

Таким образом, постоянная времени блока задержки

Тз.упр C.Rper m. Скл- Rper/i m«(r/i),...,

(3)

т.е. постоянная времени нелинейна (обратно пропорциональна числу подключенных ключей). Блок задержки с такой регулировочной характеристикой затрудняет процесс точной установки требуемой величины задержки и ее подстройки.

Последовательное подключение М блоков задержки с такой регулировочной харак- теристикой дает возможность получить канал задержки, имеющий регулировочную характеристику вида

Тз.упр -

+

т J

12

Скл.Нкл J

м

+ ...

для М 3

N

5

i2 + 1

i 1

Таким образом, при том же динамическом диапазоне канал задержки обеспечивает установку требуемой задержки с большей точностью за счет получения значительно большего числа устанавливаемых кодом управления величин задержки.

Коррекция величин задержек в каждом канале при изменении их по каким-то одинаковым для каждого канала задержки 1 причинам производится путем увеличения или уменьшения числа подключенных управляемых ключей 8 соответственно для уменьшения или увеличения величин задержек. При этом число управляющих сигналов коррекции по второй 6 и третьей 7 шинам управления, поступающих на каждый элемент задержки, одинаково. Приращение (уменьшение) величины задержки элемента задержки при отключении (подключении) одного дополнительного управляемого ключа 8 Дт3 определена как

А m TOm to

ДГа--j - ,w +1 m.ro()

m. r0

(5)

(), +1 )..

Относительное изменение величины задержки

1

(-;

+ 1

Для схемы задержки по фиг.З приращения (уменьшения) величины задержки при отключении (подключении) одного дополнительного управляемого ключа 8 в каждом элементе задержки А Т3 согласно (3), (4) и (5)

. г0.(...+-р-) 1 2 м

11

- ПЛ . То /:Г-Г- +:ГТ +

° Н(-) +1 i2(-) +1 - +...+--r) m.r0x

) +1 .

,s . т - 1 .j .. л ч

И Ой-) +1) i2(i2(- +1)

+ + 1)Х

где И, 12,...м -любые целые числа от 1 до т, соответствующие количеству подключенных управляемых ключей 8 в первом (И), втором 02) и т.д., М-м (1М) элементах задержки.

Из (7) следует, что для каждого канала может быть получен линейный закон приращения задержки, т.е. получен одинаковый относительный уровень коррекции величин задержек в каждом канале.

Преобразователи кодов 10 в каждом канале 1 задержки, предназначенные для преобразования двоичного кода, поступа- ющего по первой шине 5 управления ключами 8 в код числа единиц, содержат две группы выходных элементов, вторые входы первой из которых соединены с второй шиной б управления, а вторые входы второй группы выходных элементов соединены с третьей шиной 7 управления канала задержки. Выходные элементы первой группы увеличивают число единичных сигналов управления на ключи 8, т.е. подключенных

15

20

25

30

35

4045

50 55

ключей 8 в соответствии с кодом коррекции. Выходные элементы второй группы уменьшают число единиц управления на ключи 8, т.е. подключенных ключей 8 в соответствии с кодом коррекции.

На основании изложенного выше следует, что выполнение каналов задержки 1 в виде, представленном на фиг.2, обеспечивает одновременную программно независимую установку для каждого канала величины задержки с повышенной точностью, а блок 2 определения величины неста- бильности, выполненный по фиг.З, совместно с n-разрядным преобразователем 3 кода, коммутатором 4 и К-м каналом 1 задержки обеспечивают корректировку установленных значений задержек в каждом канале 1 задержки; при изменении последних при воздействии общих внешних факторов путем сравнения времени задержки в К-м канале 1 задержки с периодом внешнего эталонного сигнала и выработки по результатам сравнения кода коррекции, передачи этих кодов в каждый канал 1 задержки. Таким образом, программируемое устройство выравнивания задержек обеспечивает устранение недостатков известных устройств и приводит к повышению точности установленной в каждом канале величины задержки и программно независимой для каждого канала начальной установки величины задержки.:

Формула изобретения 1. Программируемое устройство выравнивания задержек, содержащее К одинаковых каналов задержки; каждый из которых имеет свой информационный, вход и выход, к выходу К-го канала подключен первый вход блока определения величины нестабильности, второй вход последнего соединен с входом эталонного сигнала, отличающееся тем, что, с целью повышения точности выравнивания задержек, в него дополнительно введены п-разрядный преобразователь кода коррекции, коммутатор, каждый канал задержки имеет три шины управления, при этом первая шина управления каждого из каналов задержки подключена к соответствующему входу начальной установки величины задержки, вторая и третья шины управления каждого канала задержки соединены соответственно с первыми и вторыми выходами коммутатора, информационные входы которого с первого по п подключены к соответствующим выходам п-разрядного преобразователя кода коррекции, входы последнего с первого по п соединены с соответствующими выходами блока определения величины нестабильности, (п+1) и (п+2) выходы последнего подключены соответственно к первому и второму входам управления коммутатора, третий вход блока определения величины нестабильности является входом внешнего на- чального обнуления.

в виде М последовательно включенных блоков задержки, каждый из которых содержит группу из m параллельно включенных управляемых ключей, выход группы соединен с входом формирователя, выход последнего является информационным выходом блока задержки, и преобразователя кода, имеющего первую, вторую и третью шины управления, разрядность первой из которых равна М Iog2m вторая и третья шины управления имеют по р входов, где М,т,р - целые числа, а каждый из выходов преобразователя кода соединен с входом управления соответствующего управляемого ключа блока задержки, а вторая и третья шины управления каждого преобразователя кода каждого блока задержи соединен соответственно с второй и третьей шинами управления канала задержки, а первые шины управления последнего являются соответствующими первыми входами управления преобразователей кода.

и второй схем ИЛИ и регистра хранения, при этом первый вход блока определения величины нестабильности является первым входом фазового компаратора и соединен с входом первого формирователя фронта и входом формирователя спада, выход последнего подключен к первому входу первой схемы И, второй вход которой соединен с выходом инвертора, вход последнего подключен к первому выходу фазового компаратора и первому входу второй схемы И, второй вход последней подключен к выходу первой схемы ИЛИ, первый вход которой соединен с выходом второго формирователя фронта, вход последнего соединен с вторым входом фазового компаратора, являющимся также вторым входом блока определения величины нестабильности, третий вход последнего соединен с третьим входом фазового компаратора и первым входом второй схемы ИЛИ, второй вход которой подключен к выходу первой схемы И, выход второй схемы ИЛИ соединен с входом обнуления счетчика, каждый выход которого соединен с соответствующим, информационным входом регистра хранения, выходы последнего являются выходами с первого по n-й блока определения величины нестабильности, (п+1) и (п+2) выходы которого являются соответственно вторым и третьим выходами фазового компаратора, выход первого формирователя фронта соединен с вторым входом первой схемы ИЛИ, выход второй схемы И подключен к счетному входу счетчика, вход записи регистра хранения соединен с выходом третьей схемы И, первый вход которой подключен к входу инвертора, второй вход третьей схемы И соединен с выходом формирователя спада.

Вх.К-1

6

7

Риг. 2

I

Вшх-1 I |

Вых. 21/П

Авторы

Даты

1992-04-07—Публикация

1990-03-16—Подача