Изобретение относится к контрольно- измерительной технике, в частности к измерительному оборудованию для полупроводниковых приборов, с повышенной степенью интеграции, и предназначено для использования в системах автоматического контроля динамического функционирования больших интегральных схем (БИС) с количеством выводов до 256 и классификации их пб результатам/контроля на группы. .. : ..

Целью изобретения является устранение отмеченного недостатка, а именно повышение производительности работы устройства для функционального контроля БИС за счет повышения эффективности использования аппаратных средств по групповому принципу, заключающемуся в распределении ресурсов измерения N каналов в л групп по m каналов в каждой группе и одновременном контроле временных параметров в каждой группе по каждому контролируемому выводу схемы.

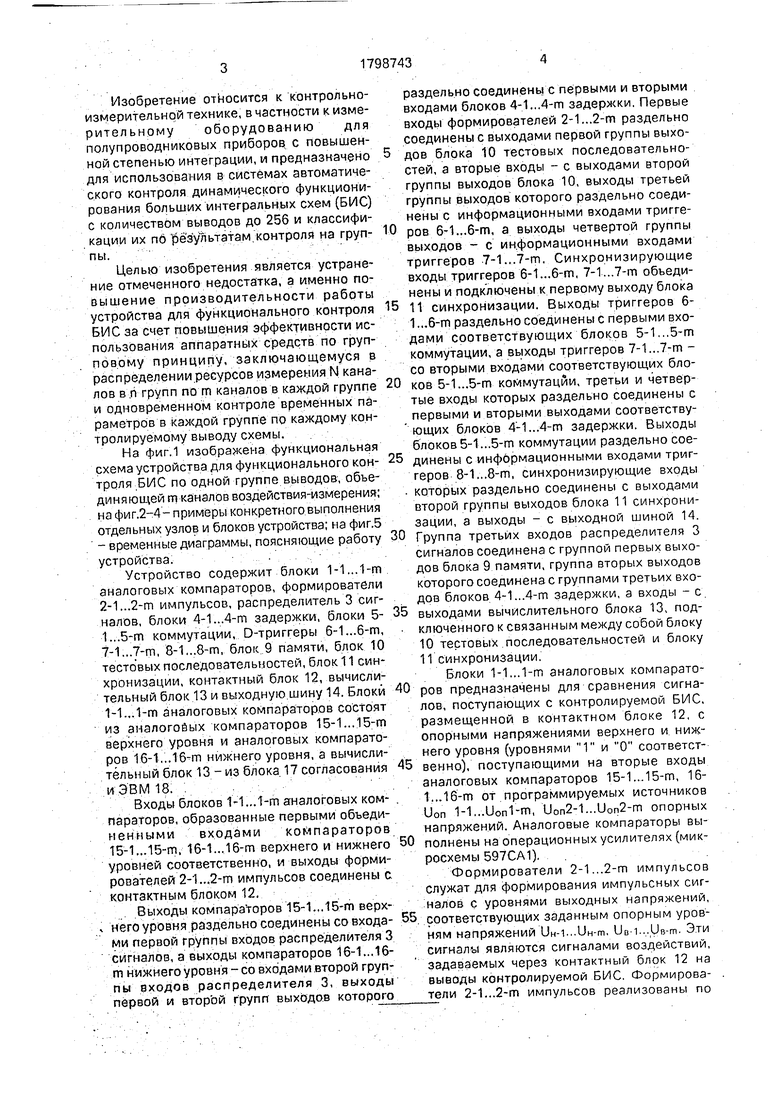

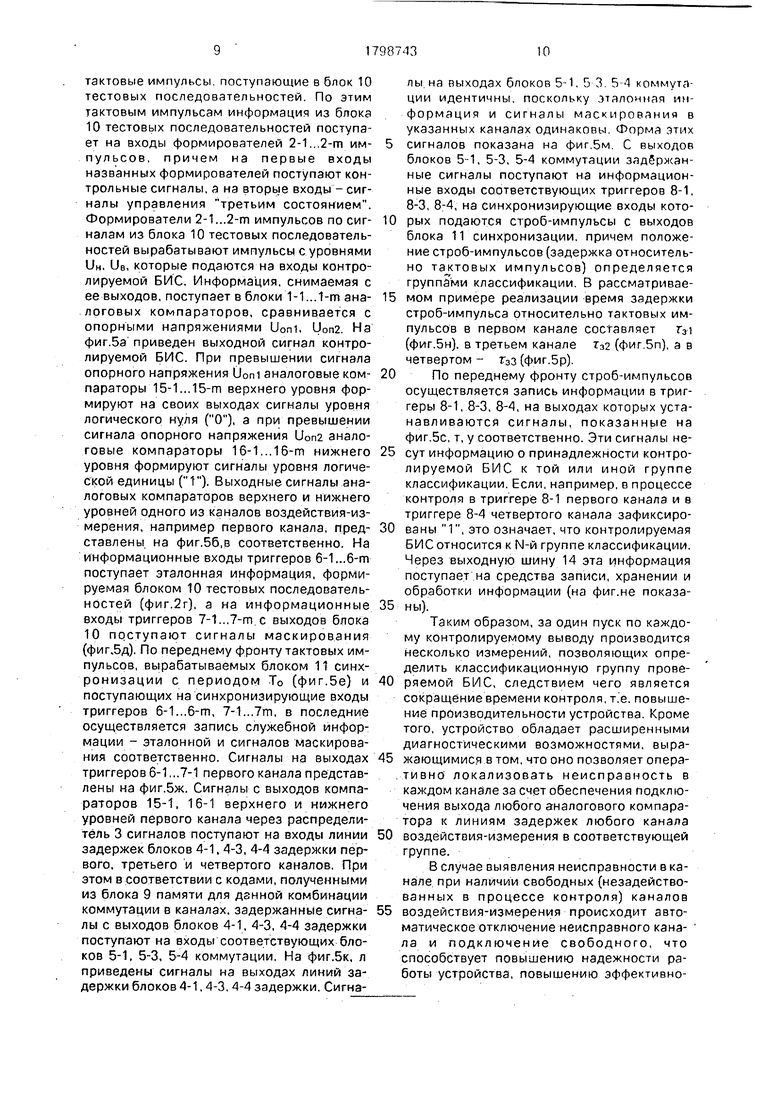

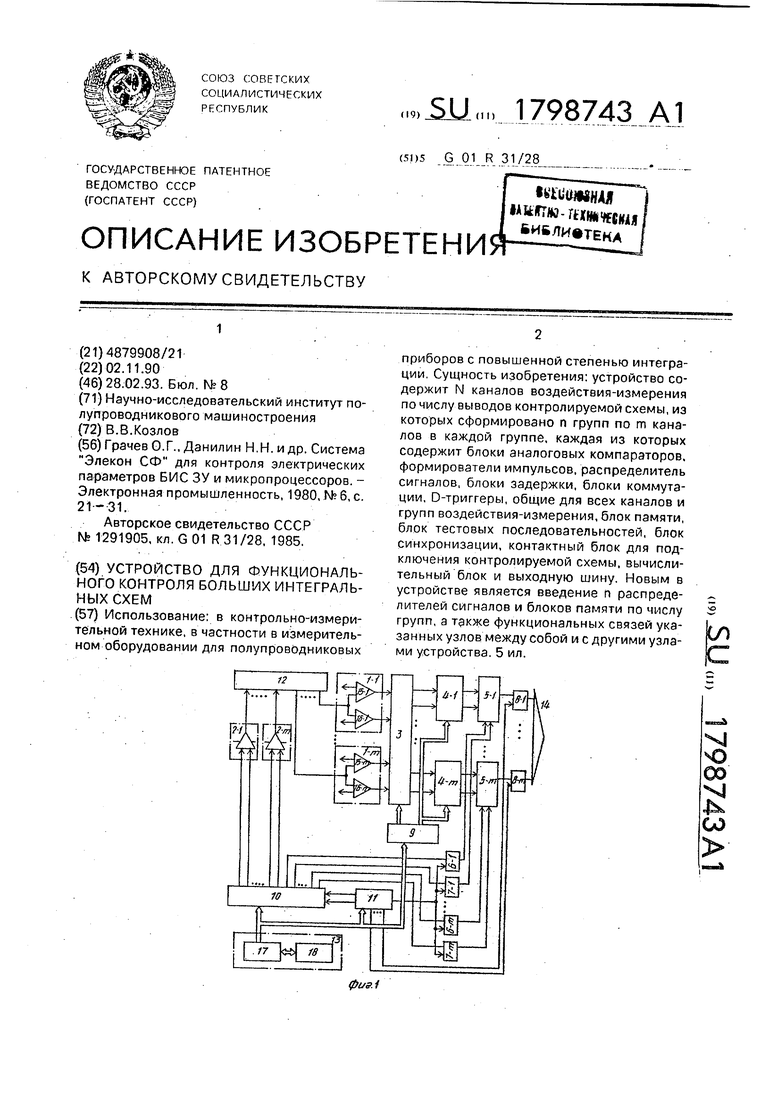

На фиг. 1 изображена функциональная схема устройства для функционального контроля БИС по одной группе выводов, объединяющей m каналов воздействия-измерения; на фиг.2-4- примеры конкретного выполнения отдельных узлов и блоков устройства; на фиг.5 - временные диаграммы, поясняющие работу устройства..

Устройство содержит блоки 1-1...1-т аналоговых компараторов, формирователи 2-1...2-т импульсов, распределитель 3 сигналов, блоки 4-1...4-т задержки, блоки 5- 1...5-ПП коммутации, D-триггеры 6-1...6-т, 7-1.„7-т, 8-1,..8-т, блок 9 памяти, блок 10 тестовых последовательностей, блок 11 синхронизации, контактный блок 12, вычислительный блок 13 и выходную.шину 14. Блоки 1-1.,.1-т аналоговых компараторов состоят из аналоговых компараторов 15-1...15-т верхнего уровня и аналоговых компараторов 16-1,. нижнего уровня, а вычислительный блок 13 - из блока 17 согласования

и эвм 18; : . , .. : . .

Входы блоков 1-1..Л-m аналоговых компараторов, образованные первыми объеди- иенными входами компараторов 15-1...15-т, 16-1... 16-т верхнего и нижнего уровней соответственно, и выходы формирователей 2-1..,2-т импульсов соединены с. контактным блоком 12.

. Выходы компараторов 15-1.„15-т верх- , него уровня раздельно соединены со входами первой группы входов распределителя 3 сигналов, а выходы компараторов 16-1...16- m нижнего у ровня -со входами второй группы входов распределителя 3, выходы первой и второй групп выходов которого

раздельно соединеныте первыми и вторыми входами блоков 4-1...4-т задержки. Первые входы формирователей 2-1...2-т раздельно соединены с выходами первой группы выходов блока ТО тестовых последовательностей, а вторые входы - с выходами второй группы выходов блока 10, выходы третьей группы выходов которого раздельно соединены с информационными входами триггеров 6-1...6-т, а выходы четвертой группы выходов - с информационными входами триггеров 7-1...7-т, Синхронизирующие входы триггеров 6-1..,6-т, 7-1...7-т объединены и подключены к первому выходу блока

И синхронизации. Выходы триггеров 6- 1 ...6-т раздельно соединены с первыми входами соответствующих блоков 5-1...5-т коммутации, а выходы триггеров 7-1...7-т - со вторыми входами соответствующих блоков 5-1...5-т коммутации, третьи и четвертые входы которых раздельно соединены с первыми и вторыми выходами соответству- ющих блоков 4-1...4-т задержки. Выходы блоков 5-1...5-т коммутации раздельно соединены с информационными входами триггеров 8-1...8-т, синхронизирующие входы которых раздельно соединены с выходами второй группы выходов блока 11 синхронизации, а выходы - с выходной шиной 14.

Группа третьих входов распределителя 3 сигналов соединена с группой первых выходов блока 9 памяти, группа вторых выходов которого соединена с группами третьих входов блоков 4-1...4-т задержки, а входы - с

выходами вычислительного блока 13, под- ключенного к связанным между собой блоку

10 тестовых последовательностей и блоку

11 синхронизации.

Блоки 1-1.„1-т аналоговых компараторов предназначены для сравнения сигналов, поступающих с контролируемой БИС, размещенной в контактном блоке 12, с опорными напряжениями верхнего и нижнего уровня (уровнями 1 и О соответственно), поступающими на вторые входы аналоговых компараторов 15-1.,.15-т, 16- 1...16-т ОТ программируемых источников Don 1-1...Uon1-m, Uon2-1...U0n2-m опорных напряжений. Аналоговые компараторы выполнены на операционных усилителях (микросхемы 597СА1).

Формирователи 2-1...2-т импульсов служат для формирования импульсных сигналов с уровнями выходных напряжений,

соответствующих заданным опорным уровням напряжений Un-i.,.UH-m, UB-i....ye-m. Эти сигналы являются сигналами воздействий, задаваемых через контактный блок 12 на выводы контролируемой БИС. Формировагели 2-1...2-т импульсов реализованы по

схеме формирователя типа три состояния (драйвера).

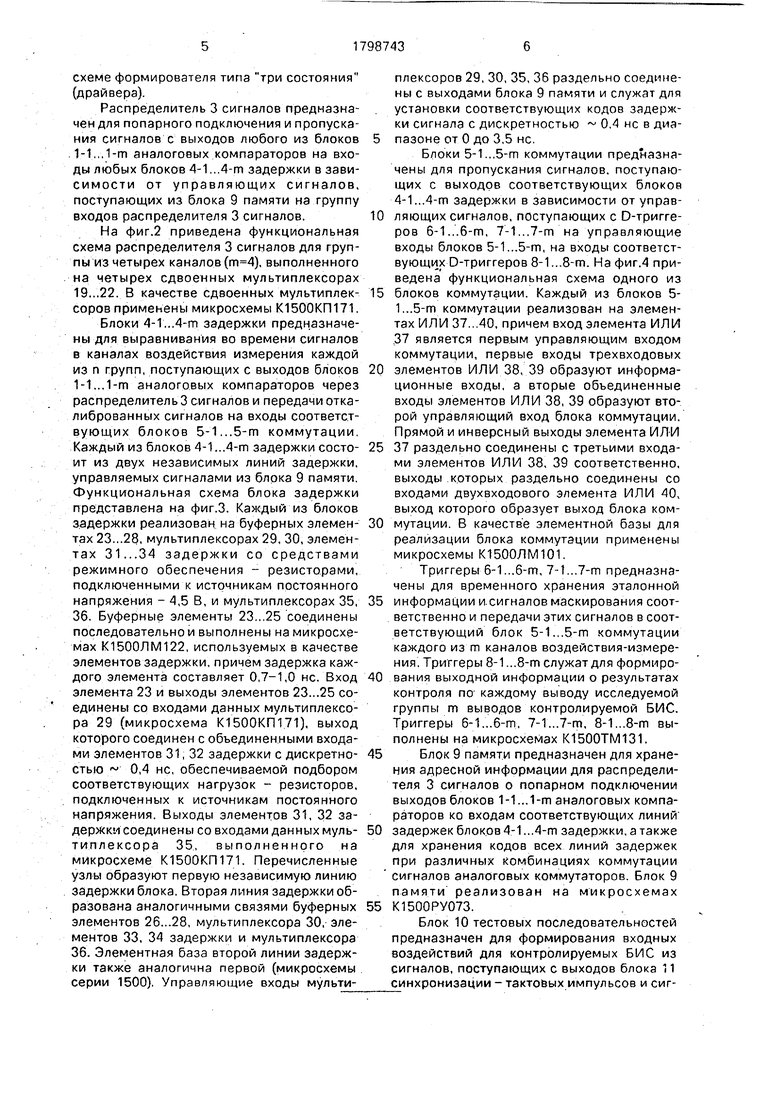

Распределитель 3 сигналов предназначен для попарного подключения и пропускания сигналов с выходов любого из блоков .1-1... 1-т аналоговых компараторов на входы любых блоков 4-1, ..4-т задержки в зависимости от управляющих сигналов, поступающих из блока 9 памяти на группу входов распределителя 3 сигналов.

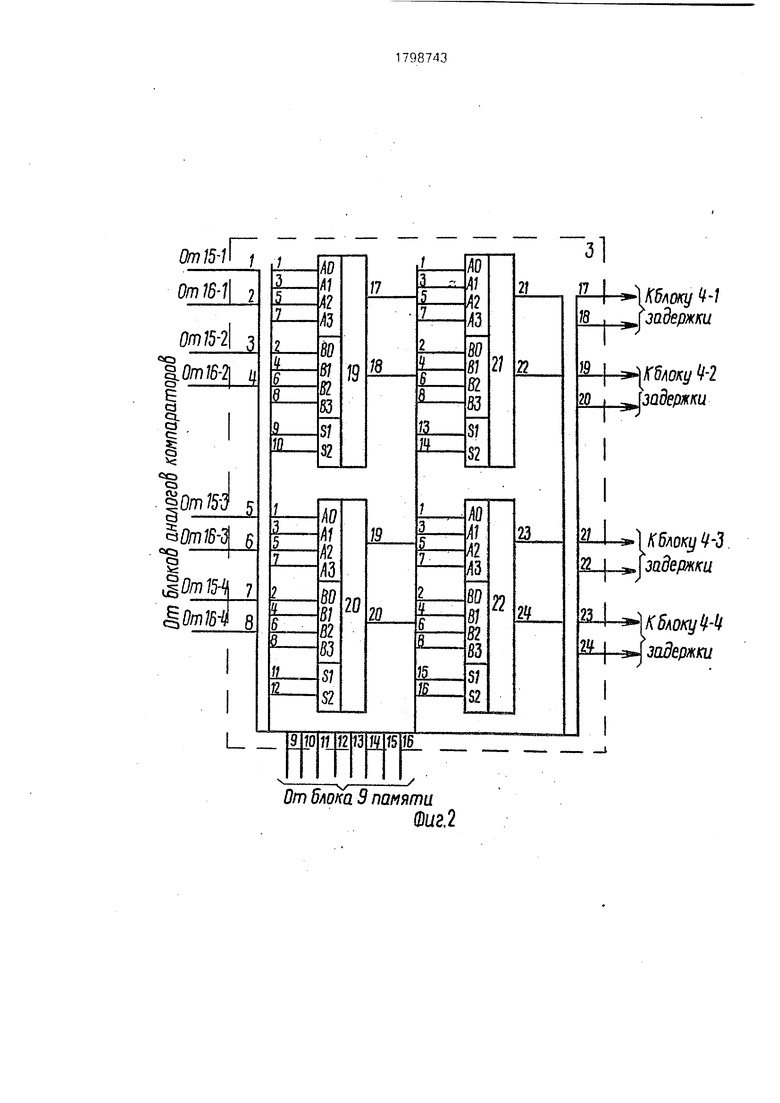

На фиг.2 приведена функциональная схема распределителя 3 сигналов для группы из четырех каналов (), выполненного на четырех сдвоенных мультиплексорах 19...22. В качестве сдвоенных мультиплексоров применены микросхемы К1500КП171.

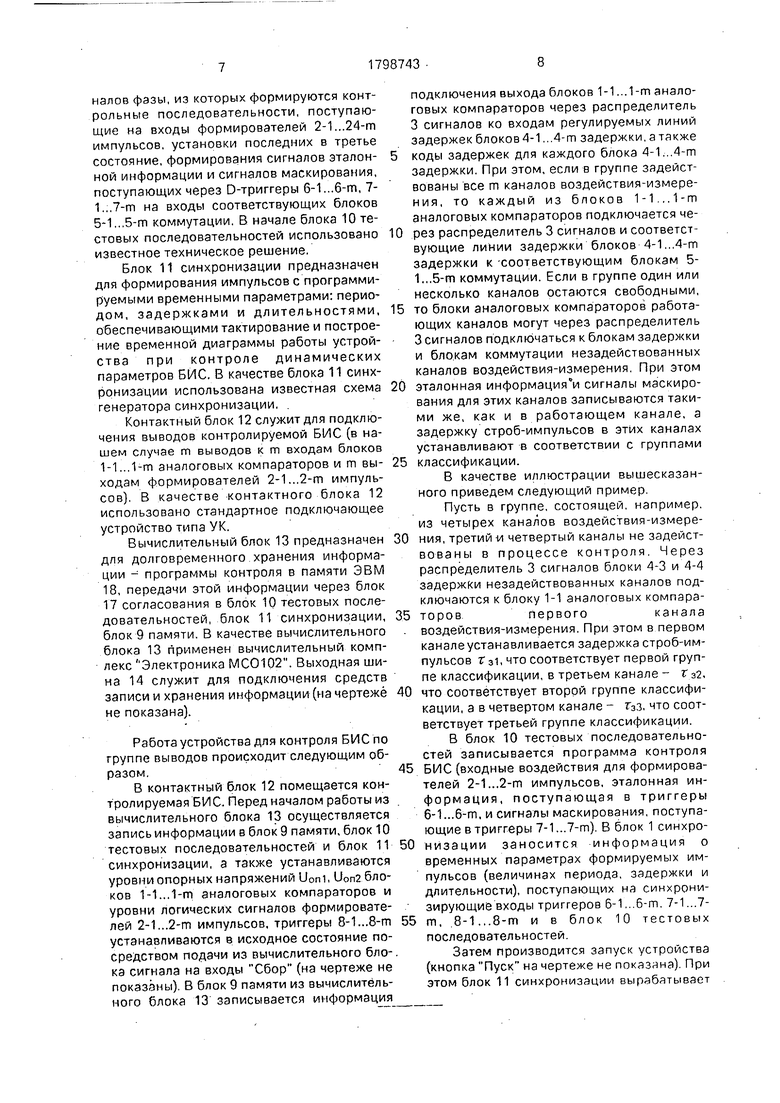

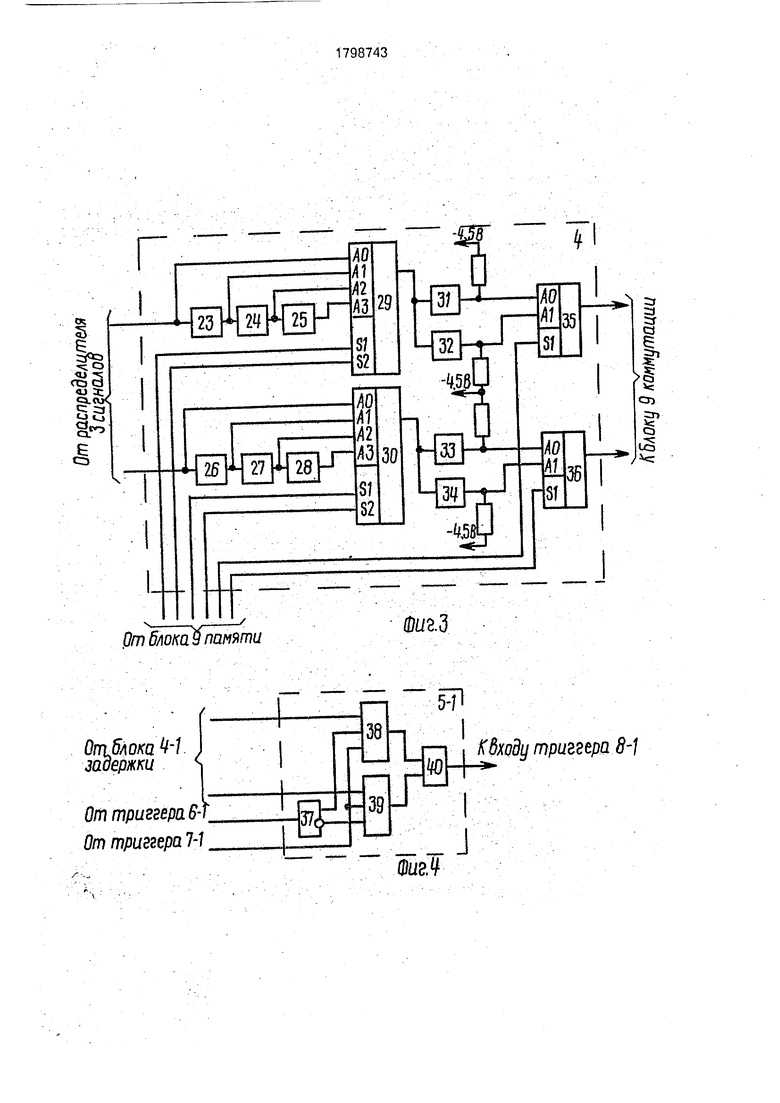

Блоки 4-1...4-т задержки предназначены для выравнивания во времени сигналов в каналах воздействия измерения каждой из п групп, поступающих с выходов блоков 1-1...1-т аналоговых компараторов через распределитель 3 сигналов и передачи отка- либрованных сигналов на входы соответствующих блоков 5-1...5-т коммутации. Каждый из блоков 4-1...4-т задержки состоит из двух независимых линий задержки, управляемых сигналами из блока 9 памяти. Функциональная схема блока задержки представлена на фиг.З. Каждый из блоков задержки реализован на буферных элементах 23...28, мультиплексорах 29, 30, элементах 31...34 задержки со средствами режимного обеспечения - резисторами, подключенными к источникам постоянного напряжения - 4,5 В, и мультиплексорах 35, 36. Буферные элементы 23...25 соединены последовательной выполнены на микросхемах К1500ЛМ122, используемых в качестве элементов задержки, причем задержка каждого элемента составляет 0,7-1,0 не. Вход элемента 23 и выходы элементов 23...25 соединены со входами данных мультиплексора 29 (микросхема К1500КП171), выход которого соединен с объединенными входами элементов 31, 32 задержки с дискретностью 0,4 не, обеспечиваемой подбором соответствующих нагрузок - резисторов, подключенных к источникам постоянного напряжения. Выходы элементов 31, 32 задержки соединены со входами данных мультиплексора 35, выполненного на микросхеме К1500КП171. Перечисленные узлы образуют первую независимую линию задержки блока. Вторая линия задержки образована аналогичными связями буферных элементов 26...28, мультиплексора 30, элементов 33, 34 задержки и мультиплексора 36. Элементная база второй линии задержки также аналогична первой (микросхемы серии 1500). Управляющие входы мультиплексоров 29, 30, 35, 36 раздельно соединены с выходами блока 9 памяти и служат для установки соответствующих кодов задержки сигнала с дискретностью 0,4 не в диа- пазоне от 0 до 3,5 не.

Блоки 5-1...5-т коммутации предназначены для пропускания сигналов, поступающих с выходов соответствующих блоков 4-1...4-т задержки в зависимости от управ0 ляющих сигналов, поступающих с D-тригге- ров 6-1...6-т, 7-1...7-т на управляющие входы блоков 5-1...5-т, на входы соответствующих D-триггеров 8-1...8-т. На фиг.4 приведена функциональная схема одного из

5 блоков коммутации. Каждый из блоков 5- 1...5-т коммутации реализован на элементах ИЛИ 37...40, причем вход элемента ИЛИ .37 является первым управляющим входом коммутации, первые входы трехвходовых

0 элементов ИЛИ 38, 39 образуют информационные входы, а вторые объединенные входы элементов ИЛИ 38, 39 образуют второй управляющий вход блока коммутации. Прямой и инверсный выходы элемента ИЛИ

5 37 раздельно соединены с третьими входами элементов ИЛИ 38, 39 соответственно, выходы которых раздельно соединены со входами двухвходового элемента ИЛИ 40, выход которого образует выход блока ком0 мутации. В качестве элементной базы для реализации блока коммутации применены микросхемы К1500ЛМ101.

Триггеры 6-1...6-т, 7-1...7-т предназначены для временного хранения эталонной

5 информации сигналов маскирования соответственно и передачи этих сигналов в соответствующий блок 5-1...5-т коммутации каждого из m каналов воздействия-измерения. Триггеры 8-1...8-т служат для формиро0 вания выходной информации о результатах контроля по каждому выводу исследуемой группы m выводов контролируемой БИС. Триггеры 6-1...6-т, 7-1...7-т, 8-1...8-т выполнены на микросхемах К1500ТМ131.

5 Блок 9 памяти предназначен для хранения адресной информации для распределителя 3 сигналов о попарном подключении выходов блоков 1-1...1-т аналоговых компараторов ко входам соответствующих линий

0 задержек блоков 4-1...4-т задержки, а также

для хранения кодов всех линий задержек

при различных комбинациях коммутации

сигналов аналоговых коммутаторов. Блок 9

памяти реализован на микросхемах

5 К1500РУ073.

Блок 10 тестовых последовательностей предназначен для формирования входных воздействий для контролируемых БИС из сигналов, поступающих с выходов блока 11 синхронизации - тактовых импульсов и сигналов фазы, из которых формируются контрольные последовательности, поступающие на входы формирователей 2-1...24-т импульсов, установки последних в третье состояние, формирования сигналов эталонной информации и сигналов маскирования, поступающих через D-триггеры 6-1...6-т, 7- 1...7-ГЛ на входы соответствующих блоков 5-1...5-т коммутации. В начале блока 10 тестовых последовательностей использовано известное техническое решение.

Блок 11 синхронизации предназначен для формирования импульсов с программируемыми временными параметрами: перио дом, задержками и длительностями, обеспечивающими тактирование и построение временной диаграммы работы устройства при контроле динамических параметров БИС. В качестве блока 11 синхронизации использована известная схема генератора синхронизации, .

Контактный блок 12 служит для подключения выводов контролируемой БИС (в нашем случае m выводов к m входам блоков 1-1...1-т аналоговых компараторов и m выходам формирователей 2-1...2-т импульсов). В качестве контактного блока 12 использовано стандартное подключающее устройство типа УК.

Вычислительный блок 13 предназначен для долговременного хранения информации - программы контроля в памяти ЭВМ 18, передачи этой информации через блок 17 согласования в блок 10 тестовых последовательностей, блок 11 синхронизации, блок 9 памяти. В качестве вычислительного блока 13 применен вычислительный комплекс Электроника МСОЮ2. Выходная шина 14 служит для подключения средств записи и хранения информации (на чертеже не показана).

Работа устройства для контроля БИС по группе выводов происходит следующим образом.

В контактный блок 12 помещается контролируемая БИ С. Перед началом работы из вычислительного блока 13 осуществляется запись информации в блок 9 памяти, блок 10 тестовых последовательностей и блок 11 синхронизации, а также устанавливаются уровни опорных напряжений U0ni, Uon2 блоков 1-1...1-m аналоговых компараторов и уровни логических сигналов формирователей 2-1...2-т импульсов, триггеры 8-1...8-т устанавливаются в исходное состояние посредством подачи из вычислительного блока сигнала на входы Сбор (на чертеже не показаны). В блок 9 памяти из вычислительного блока 13 записывается информация

подключения выхода блоков 1-1 ...1-т аналоговых компараторов через распределитель 3 сигналов ко входам регулируемых линий задержек блоков 4-1...4-m задержки, а также

коды задержек для каждого блока 4-1...4-т задержки. При этом, если в группе задействованы все m каналов воздействия-измерения, то каждый из блоков 1-1...1-т аналоговых компараторов подключается через распределитель 3 сигналов и соответствующие линии задержки блоков 4-1...4-т задержки к -соответствующим блокам 5- 1...5-т коммутации. Если в группе один или несколько каналов остаются свободными,

то блоки аналоговых компараторов работающих каналов могут через распределитель 3 сигналов подключаться к блокам задержки и бло.кам коммутации незадействованных каналов воздействия-измерения. При этом

эталонная информация и сигналы маскирования для этих каналов записываются такими же, как и в работающем канале, а задержку строб-импульсов в этих каналах устанавливают в соответствии с группами

классификации.

В качестве иллюстрации вышесказанного приведем следующий пример.

Пусть в группе, состоящей, например, из четырех каналов воздействия-измерения, третий -и четвертый каналы не задейст- вованы в процессе контроля. Через распределитель 3 сигналов блоки 4-3 и 4-4 задержки незадействованных каналов подключаются к блоку 1-1 аналоговых компараторовпервого канала воздействия-измерения. При этом в первом канале устанавливается задержка строб-импульсов г з1, что соответствует первой группе классификации, в третьем канале - г 32,

что соответствует второй группе классификации, а в четвертом канале - Г3з. что соответствует третьей группе классификации.

В блок 10 тестовых последовательностей записывается программа контроля

БИС (входные воздействия для формирователей 2-1...2-т импульсов, эталонная информация, поступающая в триггеры 6-1...6-т, и сигналы маскирования, поступающие в триггеры 7-1 ...7-гп). В блок 1 синхронйзации заносится информация о временных параметрах формируемых импульсов (величинах периода, задержки и длительности), поступающих на синхронизирующие входы триггеров 6-1 ...6-т. 7-1 ...7т, .8-1...8-т и в блок 10 тестовых последовательностей.

Затем производится запуск устройства (кнопка Пуск на чертеже не показана). При этом блок 11 синхронизации вырабатывает

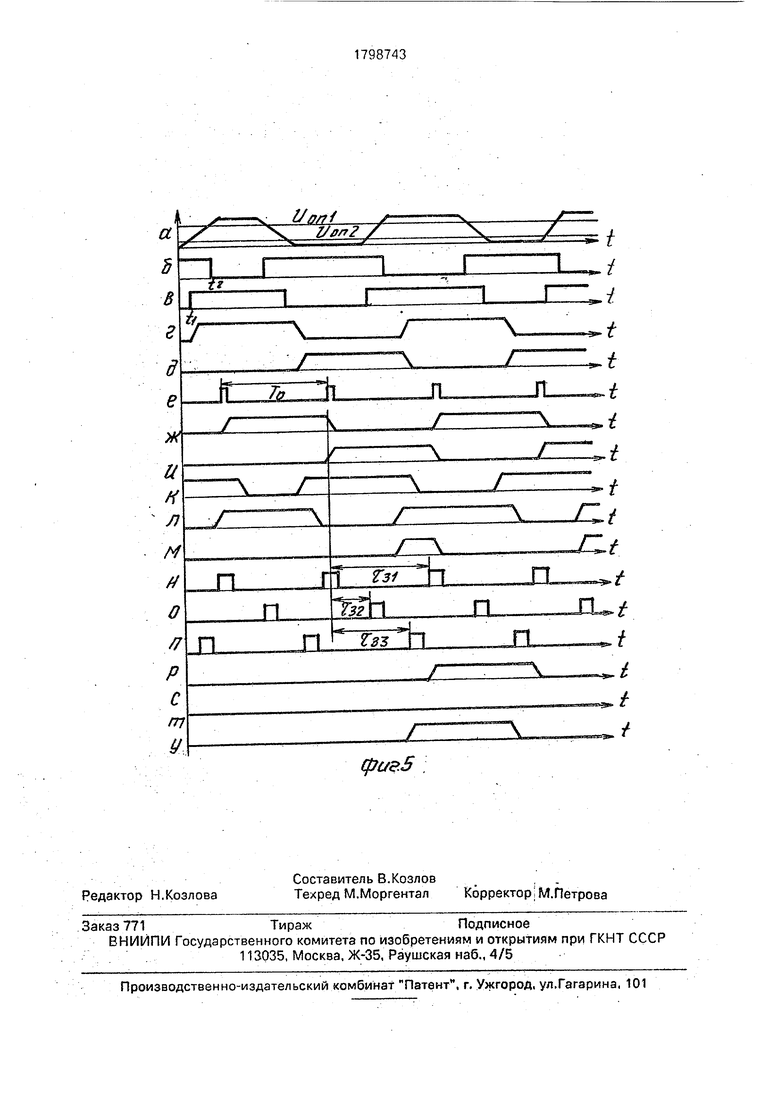

тактовые импульсы, поступающие в блок 10 тестовых последовательностей. По этим тактовым импульсам информация из блока 10 тестовых последовательностей поступает на входы формирователей 2-1...2-т импульсов, причем на первые входы названных формирователей поступает контрольные сигналы, а на вторые входы - сигналы управления третьим состоянием. Формирователи 2-1...2-т импульсов по сигналам из блока 10 тестовых последовательностей вырабатывают импульсы с уровнями UH. UB, которые подаются на входы контролируемой БИС. Информация, снимаемая с ее выходов, поступает в блоки 1-1...1-т аналоговых компараторов, сравнивается с опорными напряжениями Uoni, Uon2. На фиг.5а приведен выходной сигнал контролируемой БИС. При превышении сигнала опорного напряжения 00п1 аналоговые компараторы 15-1...15-гп верхнего уровня формируют на своих выходах сигналы уровня логического нуля (О), а при превышении сигнала опорного напряжения U0n2 аналоговые компараторы 16-1...16-т нижнего уровня формируют сигналы уровня логической единицы (1). Выходные сигналы аналоговых компараторов верхнего и нижнего уровней одного из каналов воздействия-измерения, например первого канала, представлены на фиг.56,в соответственно. На информационные входы триггеров 6-1...б-т поступает эталонная информация, формируемая блоком 10 тестовых последовательностей (фиг.2г), а на информационные входы триггеров 7-1...7-т.с выходов блока 10 поступают сигналы маскирования (фиг.5д). По переднему фронту тактовых импульсов, вырабатываемых блоком 11 синхронизации с периодом То (фиг.5е) и поступающих на синхронизирующие входы триггеров 6-1.,.6-гп, 7-1...7т. в последние осуществляется запись служебной информации - эталонной и сигналов маскирования соответственно. Сигналы на выходах триггеров 6-1,..7-1 первого канала представлены на фиг.бж. Сигналы с выходов компараторов 1.5-1, 16-1 верхнего и нижнего уровней первого канала через распределитель 3 сигналов поступают на входы линии задержек блоков 4-1, 4-3, 4-4 задержки первого, третьего и четвертого каналов. При этом в соответствии с кодами, полученными из блока 9 памяти для данной комбинации коммутации в каналах, задержанные сигналы с выходов блоков 4-1, 4-3, 4-4 задержки поступают на входы соответствующих блоков 5-1, 5-3, 5-4 коммутации. На фиг.бк, л приведены сигналы на выходах линий задержки блоков 4-1, 4-3, 4-4 задержки. Сигналы, на выходах блоков 5-1, 53. 5-4 коммутации идентичны, поскольку эталонная информация и сигналы маскирования в указанных каналах одинаковы. Форма этих сигналов показана на фиг.5м. С выходов блоков 5-1, 5-3, 5-4 коммутации задержанные сигналы поступают на информационные входы соответствующих триггеров 8-1, 8-3, 8:4, на синхронизирующие входы которых подаются строб-импульсы с выходов блока 1Г синхронизации, причем положение строб-импульсов (задержка относительно тактовых импульсов) определяется группами классификации. В рассматриваемом примере реализации время задержки строб-импульса относительно тактовых импульсов в первом канале составляет r3i (фиг.5н). в третьем канале Тз2 (фиг.5п), а в четвертом - тэз (фиг.5р).

По переднему фронту строб-импульсов осуществляется запись информации в триггеры 8-1,8-3, 8-4, на выходах которых устанавливаются сигналы, показанные на фиг.5с, т, у соответственно. Эти сигналы несут информацию о принадлежности контролируемой БИС к той или иной группе классификации. Если, например, в процессе контроля в триггере 8-1 первого канала и в триггере 8-4 четвертого канала зафиксированы 1, это означает, что контролируемая БИС относится к N-й группе классификации. Через выходную шину 14 эта информация поступает на средства записи, хранении и обработки информации (на фиг.не показэны).

Таким образом, за один пуск по каждому контролируемому выводу производится несколько измерений, позволяющих определить классификационную группу проверяемой БИС, следствием чего является сокращение времени контроля, т. е. повышение производительности устройства. Кроме того, устройство обладает расширенными диагностическими возможностями, выражающимися в том, что оно позволяет опера- .тивно локализовать неисправность в каждом канале за счет обеспечения подключения выхода любого аналогового компаратора к линиям задержек любого канала

воздействия-измерения в соответствующей группе.

8 случае выявления неисправности в канале, при наличии свободных (незадействованных в процессе контроля) каналов

воздействия-измерения происходит автоматическое отключение неисправного кана- ла и подключение свободного, что способствует повышению надежности работы устройства, повышению эффективности использования аппаратных средств и увеличению коэффициента использования его узлов.

Техническое преимущество предложенного устройства для функционального контроля БИС по сравнению с прототипом заключается в реализации возможности распределения ресурсов измерения N каналов в п групп no m каналов s каждой группе и одновременном контроле временных параметров в каждой группе по каждому контролируемому выводу.

Общественно полезные преимущества,, производные от технического, заключаются в повышении производительности устройства, повышении эффективности использования аппаратных средств и расширении диагностических возможностей устройства.

Предложенное устройство для функционального контроля БИС планируется использовать в комплексе контроля статических параметров и динамического функционирования сверхбольших интегральных схем с количеством выводов до 256 и рабочей частотой до 50 МГц,

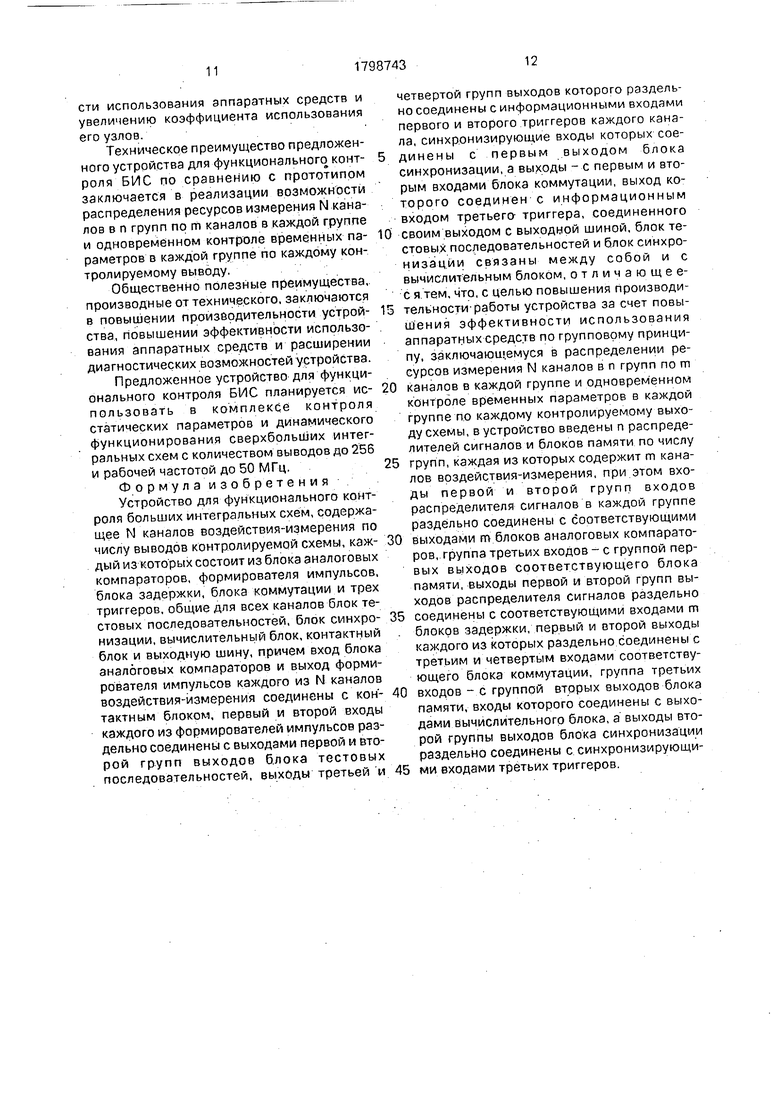

Формула изобретения

Устройство для функционального контроля больших интегральных схем, содержащее N каналов воздействия-измерения по числу выводов контролируемой схемы, каждый из которых состоит из блока аналоговых компараторов, формирователя импульсов, блока задержки, блока коммутации и трех триггеров, общие для всех каналов блок тестовых последовательностей, блок синхронизации, вычислительный блок, контактный блок и выходную шину, причем вход блока аналоговых компараторов и выход формирователя импульсов каждого из N каналов воздействия-измерения соединены с контактным блоком, первый и второй входы каждого из формирователей импульсов раздельно соединены с выходами первой и второй групп выходов б.лока тестовых последовательностей, выходы третьей и

четвертой групп выходов которого раздельно соединены с информационными входами первого и второго триггеров каждого канала, синхронизирующие входы которых соединены с первым выходом блока синхронизации, а выходы - с первым и вторым входами блока коммутации, выход которого соединен с информационным входом третьего- триггера, соединенного

своим выходом с выходной шиной, блок тестовых последовательностей и блок синхро- низац.йи связаны между собой и с вычислительным блоком, отличающееся, тем, что, с целью повышения производительности-работы устройства за счет повышения эффективности использования аппаратных средств по групповому принципу, заключающемуся в распределении ресурсов измерения N каналов в п групп по т

каналов в каждой группе и одновременном контроле временных параметров в каждой группе по каждому контролируемому выходу схемы, в устройство введены п распределителей сигналов м блоков памяти по числу

групп, каждая из которых содержит m каналов воздействия-измерения, при этом входы первой и второй групп входов распределителя сигналов в каждом группе раздельно соединены с соответствующими

выходами m блоков аналоговых компараторов, группа третьих входов - с группой первых выходов соответствующего блока памяти, выходы первой и второй групп выходов распределителя сигналов раздельно

соединены с соответствующими входами m блоков задержки/первый и второй выходы каждого из которых раздельно соединены с третьим и четвертым входами соответствующего блока коммутации, группа третьих

входов - с группой вторых выходов блока памяти, входы которого соединены с выходами вычислительного блока, а выходы второй группы выходов блока синхронизации раздельно соединены с синхронизирующими входами третьих триггеров.

От блока 9 памяти Фиг.2

РтбшаЗпамяти

fe.3

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для функционального контроля больших интегральных схем | 1990 |

|

SU1809398A1 |

| Устройство для функционального контроля больших интегральных схем | 1985 |

|

SU1291905A1 |

| Устройство для контроля цифровых объектов | 1983 |

|

SU1160373A1 |

| Устройство для автоматического контроля больших интегральных схем | 1986 |

|

SU1529220A1 |

| Устройство для автоматического контроля больших интегральных схем | 1984 |

|

SU1205083A1 |

| Устройство для тестового контроля логических узлов | 1991 |

|

SU1837297A1 |

| Устройство для функционального контроля больших интегральных схем | 1983 |

|

SU1109687A1 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| Устройство для контроля логических схем | 1986 |

|

SU1381517A1 |

| Устройство для контроля лоических блоков | 1986 |

|

SU1453409A1 |

OnrSiDKQ /. задержки

От триггера 6- От триггера 7-7

№2$

| Грачев О.Г., Данилин Н.Н | |||

| и др | |||

| Система Элекон СФ для контроля электрических параметров БИС ЗУ и микропроцессоров | |||

| Электронная промышленность, 1980, №6, с | |||

| Выбрасывающий ячеистый аппарат для рядовых сеялок | 1922 |

|

SU21A1 |

| Устройство для функционального контроля больших интегральных схем | 1985 |

|

SU1291905A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для установки двигателя в топках с получающими возвратно-поступательное перемещение колосниками | 1917 |

|

SU1985A1 |

Авторы

Даты

1993-02-28—Публикация

1990-11-02—Подача