Изобретение относится к автоматике и вычислительной технике и может быть использовано при контроле параметров, когда необходимо выявлять предотказовые состояния технических объектов с последующей возможностью регулировки этих параметров.

Известно устройство для контроля параметров, содержащее индикатор, вход которого соединен с выходом первого блока памяти, блок управления, вход которого соединен с выходом генератора импульсов, коммутатор, информационные входы которого являются соответствующими входами устройства, управляющий вход соединен с первым выходом блока управления, а выход коммутатора соединен с входом элемента задержки, элемент И, второй блок памяти и

селектор вида параметра, информационный вход которого соединен с выходом элемента задержки, адресный вход соединен с первым выходом блока управления, адресными входами первого и второго блоков памяти и первым выходом устройства, выход селектора вида параметра соединен с информационным входом второго блока памяти и первым входом элемента И, второй вход которого соединен с выходом второго блока памяти, выход элемента И соединен с управляющим входом первого блока памяти и вторым выходом устройства, второй и третий выходы блока управления соединены с входами чтения и записи второго блока памяти соответственно.

Недостатком этого устройства является низкая эффективность контроля по причине

VJ

ю

00 00

о о

отсутствия выявления предотказового состояния.

Наиболее близким к предлагаемому является анализатор параметрических отказов, содержащий пороговый блок, два формирователя импульсов, два инвертора, с первого по третий элементы И, первый триггер, первый и второй счетчики, генератор импульсов, дифференцирующий элемент, вход порогового блока является входом устройства для подключения объекта контроля, а выход соединен с входом первого формирователя импульсов, выход третьего элемента И подключен к счетному входу второго счетчика, элемент задержки, элемент ИЛИ, четвертый и пятый элементы И, делитель частоты, регистр, третий счетчик и второй триггер, выход порогового блока через элемент задержки и выход первого формирователя импульсов через первый ин- вертор подключены к соответствующим входам первого элемента И, выход которого подключен к первому входу второго элемента И, через.дифференцирующий элемент- к первому входу третьего элемента И и через второй инвертор - к входу второго формирователя импульсов и к первому установочному входу второго триггера, выход порогового блока соединен с первым входом четвертого элемента И и с первым уста- новочным входом первого триггера, второй установочный вход которого подключен к выходу четвертого элемента И, второй вход которого соединен с выходом второго формирователя импульсов, прямой выход пер- вого триггера подключен к второму входу третьего элемента И, выход генератора импульсов соединен с первым входом пятого элемента И и через делитель частоты с вторым входом второго элемента И, выход ко- торого подключен к первому входу элемента ИЛИ, выход которого соединен со счетным входом первого счетчика, выход пятого элемента И соединен с вторым входом элемента ИЛИ и со счетным входом третьего счетчика, выход которого подключен к входу управления регистра, выход которого соединен с установочным входом третьего счетчика, выход которого соединен с вторым установочным входом второго триггера, прямой выход которого подключен к второму входу пятого элемента.

Недостатком прототипа являются низкие точность и достоверность, поскольку он не позволяет осуществлять классификацию предотказового состояния и выявлять необходимость регулировки контролируемого параметра.

Целью изобретения является повышение достоверности и точности контроля за

счет классификации предотказового состояния контролируемого объекта.

Предлагаемое изобретение позволяет повысить точность и достоверность контроля за счет использования в расчетах ошибки первого рода и учета результатов прогноза поведения параметра при его классификации в момент контроля. Точность и достоверность контроля могут быть выражены через ошибку второго рода. Результаты моделирования на ЭВМ показывают, что ошибка второго рода может быть снижена на 10-15%.

Возможность распознавания предотказового состояния в зависимости от глубины прогноза является основой для проведения соответствующих регулировок. Это позволяет уменьшить время нахождения изделия в состоянии скрытого отказа, что приводит к повышению коэффициента готовности технического объекта в ряде случаев на 20- 25%.

Реализуемый в устройстве метод классификации позволяет обеспечить минимум ожидаемых затрат при эксплуатации, зависящих от различных факторов, таких как выход параметра за допуск, ошибка первого рода и регулировка параметра из i-й градации в j-ю.

Достоверность и точность контроля могут быть повышены путем реализации следующего алгоритма.

Для контролируемого параметра устанавливаются номинальное значение Do и допуск 2А , который для простоты можно принять симметричным относительно Do. Считается, что анализ параметров с целью контроля осуществляется в градациях поля допуска. Это означает, что поле допуска Uo-Д, DO +А параметра разбитого на 2т одинаковых частей (градаций). Результатом контроля в момент времени tK является определение номера градации i и его знака (I ± 1, ±2,..., +т), где т - предельный номер градации. Измерение производится с точностью до величины одной градации

-Ј

(1)

В дальнейшем для 1-й градации оценивается вероятность выхода параметра за пределы допуска по следующей формуле:

. + 2)

где Ф(х) -,-- J ёг dt - интеграл вероятности;

5Z - среднее квадратическое отклонение случайного винеровского процесса z(r) изменения параметра при 0 г Tk+1, Tk+1 tk+1 - tk,

U(Tk+i)U(tk+i)-U(tk),(3)

где U(tk)- значение параметра при контроле в момент времени tk;

U(tk+i) - прогнозируемое значение параметра к моменту времени tk+1.

Затем проверяется выполнение неравенства

,(4)

где q - требуемый уровень вероятности.

Если условие (4) выполняется, то необходимо найти такую j-ю градацию, в которой это условие нарушается, т.е. провести регулировку из i-й градации в j-ю (|i| /Д) и добиться невыполнения неравенства (4). В этом случае затраты на регулировку не играют роли.

В случае, когда неравенство (4) не соблюдается, т.е. qi q и условие параметрической надежности выполняется, необходимо решить вопрос о том, будет ли выгодно провести регулировку в какую-нибудь j-ю градацию или нет. Это вопрос решается после проверки выполнения следующего неравенства:

Cp(ij)c(0-C(j);(5)

Cp(i,j)b(i-j)a;(6)

где a, b - назначаемые коэффициенты, которые больше 0;

C(i) и CQ) - суммарные затраты, связанные с возможным отказом или ложным браком при условии, что параметр находится в i-й или j-й градациях;

C(i) qiCa + (1 - qi) a Слб; (7) СО) qjCa + (1 - qj) «j Слб, (8) где Са и Слб некоторые постоянные величины;

qj - вероятность выхода параметра за пределы допуска для j-й градации (qj определяется по формуле (2), только вместо i подставляется значение j);

а и а - вероятности ложного брака для i-й и j-й градации соответственно (они не зависят от величины параметра и могут быть вычислены заранее).

Если условие (5) выполняется, то регулировку проводить целесообразно. В случае невыполнения неравенства (5), т.е. при Cp(i.J) C(i)- СО), регулировку проводить не стоит, так как затраты на нее и возможные затраты СО) будут больше, даже если из i-й градации параметр выйдет за поле допуска к следующему моменту контроля.

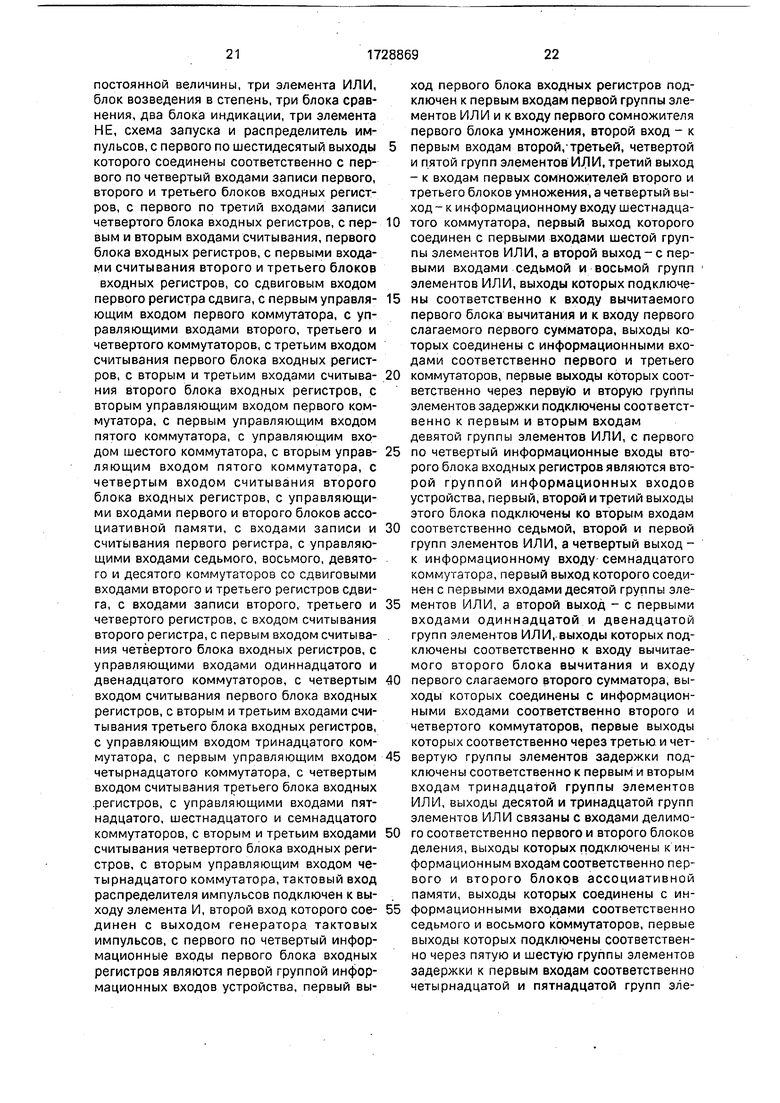

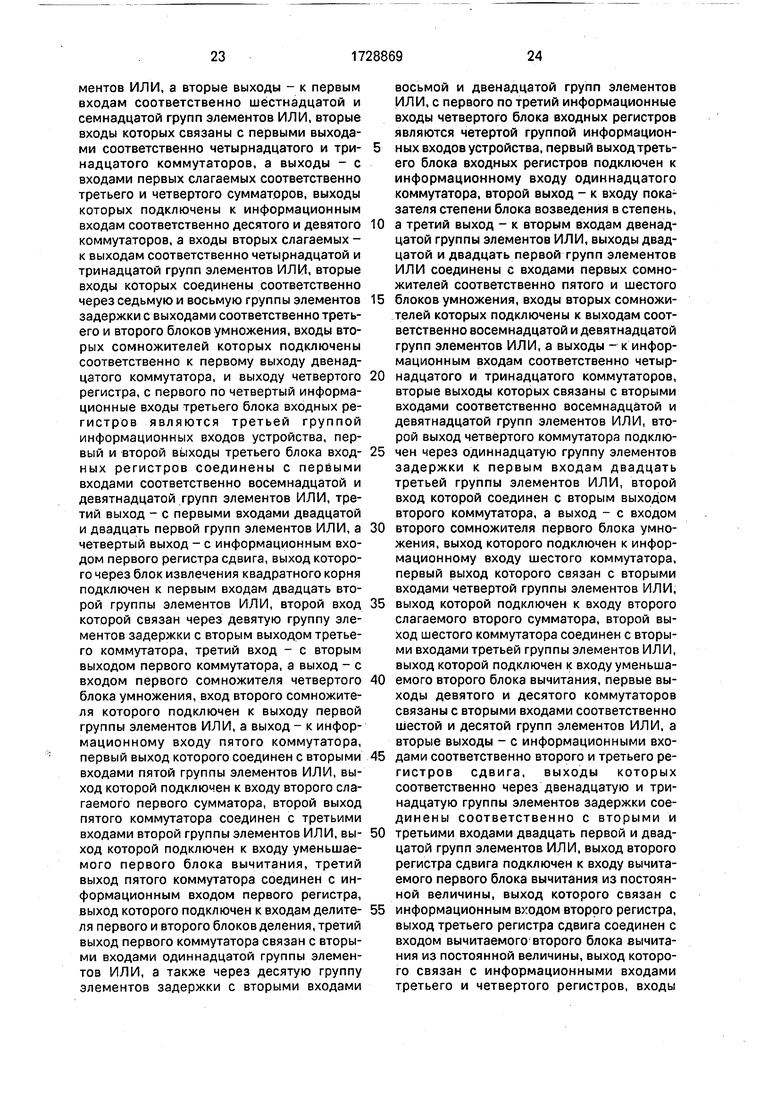

Цель изобретения достигается тем, что в устройство для контроля параметров, содержащее элемент И, первую группу элементов задержки, первую группу элементов

ИЛИ, генератор тактовых импульсов, триггер, прямой выход которого подключен к первому входу элемента И, первый регистр, введены четыре блока входных регистров, с второй по двадцать третью группы эле0 ментов ИЛИ, два блока деления, два блока ассоциативной памяти, семнадцать коммутаторов, шесть блоков умножения, три блока вычитания, с второй по четырнадцатую группы элементов задержки, второй, третий

5 и четвертый регистры, блок извлечения квадратного корня, три регистра сдвига, четыре сумматора, два блока вычитания из постоянной величины, три элемента ИЛИ, блок возведения в степень, три блока срав0 нения, два блока индикации, три элемента НЕ, схема запуска и распределитель импульсов, с первого по шестидесятый выходы которого соединены соответственно с первого по четвертый входами записи первого,

5 второго и. третьего блоков входных регист- , ров, с первого по третий входами записи четвертого блока входных регистров, с первым и вторым входами считывания первого блока входных регистров, с первыми входа0 ми считывания второго и третьего блоков входных регистров, со сдвиговым входом первого регистра сдвига, с первым управляющим входом первого коммутатора, с управляющими входами второго, третьего и

5 четвертого коммутаторов, с третьим входом считывания первого блока входных регистров, с вторым и третьим входами считывания второго блока входных регистров, с вторым управляющим входом первого ком0 мутатора, с первым управляющим входом пятого коммутатора, с управляющим входом шестого коммутатора, с вторым управляющим входом пятого коммутатора, с четвертым входом считывания второго

5 блока входных регистров, с управляющими входами первого и второго блоков ассоциативной памяти, с входами записи и считывания первого регистра, с управляющими входами седьмого, восьмого, девятого

0 и десятого коммутаторов, со сдвиговыми входами второго и третьего регистров сдвига, с входами записи второго, третьего и четвертого регистров, с входом считывания второго регистра, с первым входом считыва5 ния четвертого блока входных регистров, с управляющими входами одиннадцатого и двенадцатого коммутаторов, с четвертым входом считывания первого блока входных регистров, с вторым и третьим входами считывания третьего блока входных регистров,

с управляющим входом тринадцатого коммутатора, с первым управляющим входом четырнадцатого коммутатора, с четвертым входом считывания третьего блока входных регистров, с управляющими входами пятнадцатого, шестнадцатого и семнадцатого коммутаторов, с вторым и третьим входами считывания четвертого блока входных регистров, с вторым управляющим входом четырнадцатого коммутатора, тактовый вход распределителя импульсов подключен к выходу элемента И, второй вход которого с выходом генератора тактовых импульсов, с первого по четвертый информационные входы первого блока входных регистров являются первой группой информационных входов устройства, первый выход первого блока входных регистров подключен к первым входам первой группы элемента ИЛИ и к входу первого сомножителя первого блока умножения, второй выход - к первым входам второй, третьей, четвертой и пятой групп элементов ИЛИ, третий выход - к входам первых сомножителей второго и третьего блоков умножения, а четвертый выход - к информационному входу шестнадцатого коммутатора, первый выход которого соединен с первыми входами шестой группы элементов ИЛИ, а второй выход - с первыми входами седьмой и восьмой групп элементов ИЛИ, выходы которых подключены соответственно к входу вычитаемого первого блока вычитания и к входу первого слагаемого первого сумматора, выходы которых соединены с информационными входами соответственно первого и третьего коммутаторов, первые выходы которых соответственно.через первую и вторую группы элементов задержки подключены соответственно к первым и вторым входам девятой группы элементов ИЛИ, с первого по четвертый информационные входы второго блока входных регистров являются второй группой информационных входов устройства, первый, второй и третий выходы этого блока подключены к вторым входам соответственно седьмой, второй и первой групп элементов ИЛИ, а четвертый выход - к информационному входу семнадцатого коммутатора, первый выход которого соединен с первыми входами десятой группы элемента ИЛИ, а второй выход - с первыми входами одиннадцатой и двенадцатой групп элементов ИЛИ, выходы которых подключены соответственно к входу вычитаемого второго блока вычитания и к входу первого слагаемого второго сумматора, выходы которых соединены с информационными входами соответственно второго и четвертого коммутаторов, первые выходы которых соответственно через третью и четвертую группы элементов задержки подключены соответственно к первым и вторым входам тринадцатой группы элементов ИЛИ, выходы десятой и тринадцатой групп элементов ИЛИ связаны с входами делимого соответственно первого и второго блоков деления, выходы которых подключены к информационным входам соответственно первого и

0 второго блоков ассоциативной памяти, выходы которых соединены с информационными входами соответственно седьмого и восьмого коммутаторов, первые выходы которых подключены соответственно через

5 пятую и шестую группы элементов задерж- . ки к первым входам соответственно четырнадцатой и пятнадцатой групп элементов ИЛИ, а вторые выходы - к первым входам соответственно шестнадцатой и семнадца0 той групп элементов ИЛИ, вторые входы которых связаны с первыми выходами соответственно четырнадцатого коммутаторов, а выходы - с входами первь х слагаемых соответственно третьего и четвертого сум5 маторов, выходы которых подключены к информационным входам соответственно десятого и девятого коммутаторов, а входы вторых слагаемых - к выходам соответственно четырнадцатой и тринадцатой групп

0 элементов ИЛИ, вторые входы которых соединены соответственно через седьмую и восьмую группы элементов задержки с выходами соответственно третьего и второго блоков умножения, входы вторых сомножи5 телей которых подключены соответственно к первому выходу двенадцатого коммутатора и выходу четвертого регистра, с первого по четвертый информационные входы третьего блока входных регистров являются

0 третьей группой информационных входов устройства, первый и второй выходы третьего блока входных регистров соединены с первыми входами соответственно восемнадцатой и девятнадцатой групп элементов

5 ИЛИ, третий выход - с первыми входами двадцатой и двадцать первой групп элементов ИЛИ, а четвертый выход - с информационным входом первого регистра сдвига, выход которого через блок извлечения квад0 ратного корня подключен к первым входам двадцать второй группы элементов ИЛИ, второй вход которой связан через девятую группу элементов задержки с вторым выходом третьего коммутатора, третий вход - с

5 вторым выходом первого коммутатора, а выход-с входом первого сомножителя четвертого блока умножения, вход второго сомножителя которого подключен к выходу первой группы элементов ИЛИ, а выход - к информационному входу пятого коммутатоpa, первый выход которого соединен с вторыми входами пятой группы элементов ИЛИ, выход которой подключен к входу второго слагаемого первого сумматора, второй выход пятого коммутатора соединен с третьими входами второй группы элементов ИЛИ, выход которой подключен к входу уменьшаемого первого блока вычитания, третий выход пятого коммутатора соединен с информационным входом первого регистра, выход которого подключен к входам делителя первого и второго блоков деления, третий выход первого коммутатора связан с вторыми входами одиннадцатой группы элементов ИЛИ, а также через десятую группу элементов задержки с вторыми входами восьмой и двенадцатой групп элементов ИЛИ, с первого по третий информационные входы четвертого блока входных регистров являются четвертой группой информационных входов устройства, первый выход третьего блока входных регистров подключен к информационному входу одиннадцатого коммутатора, второй выход - к входу показателя степени блока возведения в степень, а третий выход - к вторым входам двенадцатой группы элементов ИЛИ, выходы двенадцатой и двадцать первой групп элементов ИЛИ соединены с входами первых сомножителей соответственно пятого и шестого блоков умножения, входы вторых сомножителей которых подключены к выходам соответственно восемнадцатой и девятнадцатой групп элементов ИЛИ, а выходы - к информационным входам соответственно четырнадцатого и тринадцатого коммутаторов, вторые выходы которых связаны с вторыми входами соответственно восемнадцатой и девятнадцатой групп элементов ИЛИ, второй выход четвертого коммутатора подключен через одиннадцатую группу элементов задержки к первым входам двадцать третьей группы элементов ИЛИ, второй вход которой соединен с вторым выходом второго коммутатора, а выход - с входом второго сомножителя первого блока умножения, выход которого подключен к информационному входу шестого коммутатора, первый выход которого связан с вторыми входами четвертой группы элементов ИЛИ, выход которой подключен к входу второго слагаемого второго сумматора, второй выход шестого коммутатора соединен с вторыми входами третьей группы элементов ИЛИ, выход которой подключен к входу уменьшаемого второго блока вычитания, первые выходы девятого и десятого коммутаторов связаны с вторыми входами соответственно шестой и десятой групп элементов ИЛИ, а вторые выходы информационными входами соответственно второго и третьего регистров сдвига, выходы которых соответственно через двенадцатую и тринадцатую группы элементов задержки соединены соответственно с вторыми и третьими входами двадцать первой и двадцатой групп элементов ИЛИ, выход второго регистра сдвига подключен к входу вычитаемого первого блока вычита0 ния из постоянной величины, выход которого связан с информационным входом второго регистра, выход третьего регистра сдвига соединен с входом вычитаемого второго блока вычитания из постоянной

5 величины, выход которого связан с информационными входами третьего и четвертого регистров, входы уменьшаемого и вычитаемого третьего блока вычитания.подключены соответственно к выходам шестой и десятой

0 групп элементов ИЛИ, а выход - к информационному входу пятнадцатого коммутатора, первый выход которого соединен с входом основания блока возведения в степень, выход которого подключен к третьим входам

5 восемнадцатой группы элементов ИЛИ, второй выход пятнадцатого коммутатора связан через четырнадцатую группу элементов задержки с первым входом первого блока сравнения, второй вход которого подклю0 чен к третьему выходу четырнадцатого коммутатора, а выход - к первым входам первого и второго элементов ИЛИ, и к входу первого элемента НЕ, выход которого связан с первым входом третьего элемента

5 ИЛИ, выход которого соединен с входом первого блока индикации, второй вход - с выходом второго блока сравнения, а третий вход - через второй элемент НЕ с выходом третьего блока сравнения, выход которого

0 подключен также к вторым входам второго и первого элементов ИЛИ, выходы которых соединены соответственно с входами второго блока индикации и с нулевым входом триггера, единичный вход которого подклю5 чен к выходу схемы запуска, информацион- ный вход двадцатого коммутатора соединен с выходом второго регистра, а второй выход - с первым входом второго блока сравнения, выход которого подклю0 чен к входу считывания третьего регистра, и с входом третьего элемента НЕ, выход которого связан с входом считывания четвертого регистра, второй вход второго блока сравне- ния подключен к первому выходу одиннад5 цатого коммутатора, второй выход которого соединен с первым входом третьего блока сравнения, второй вход которого подключен к выходу третьего регистра.

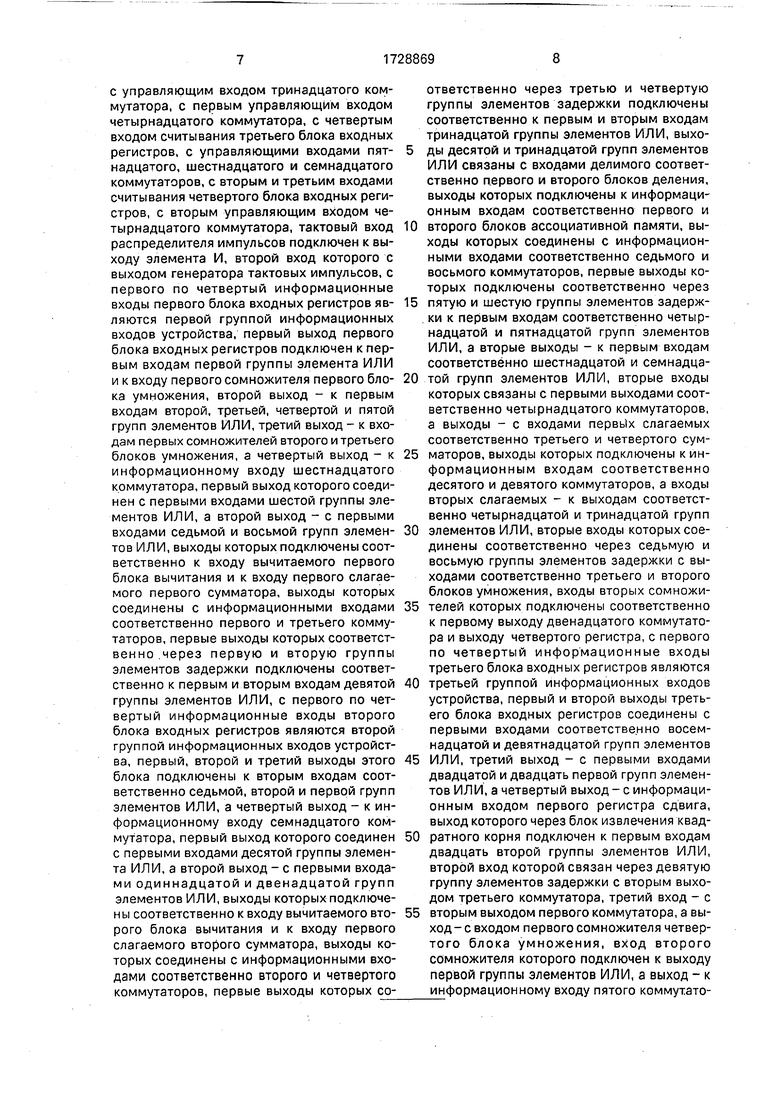

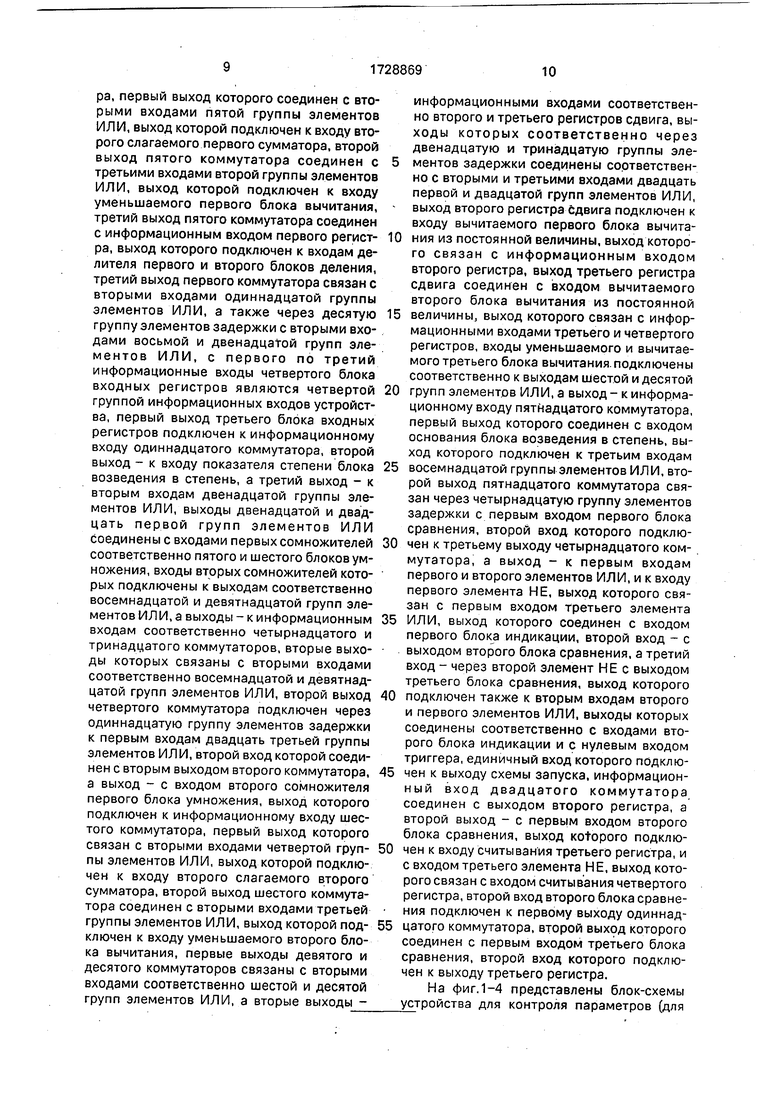

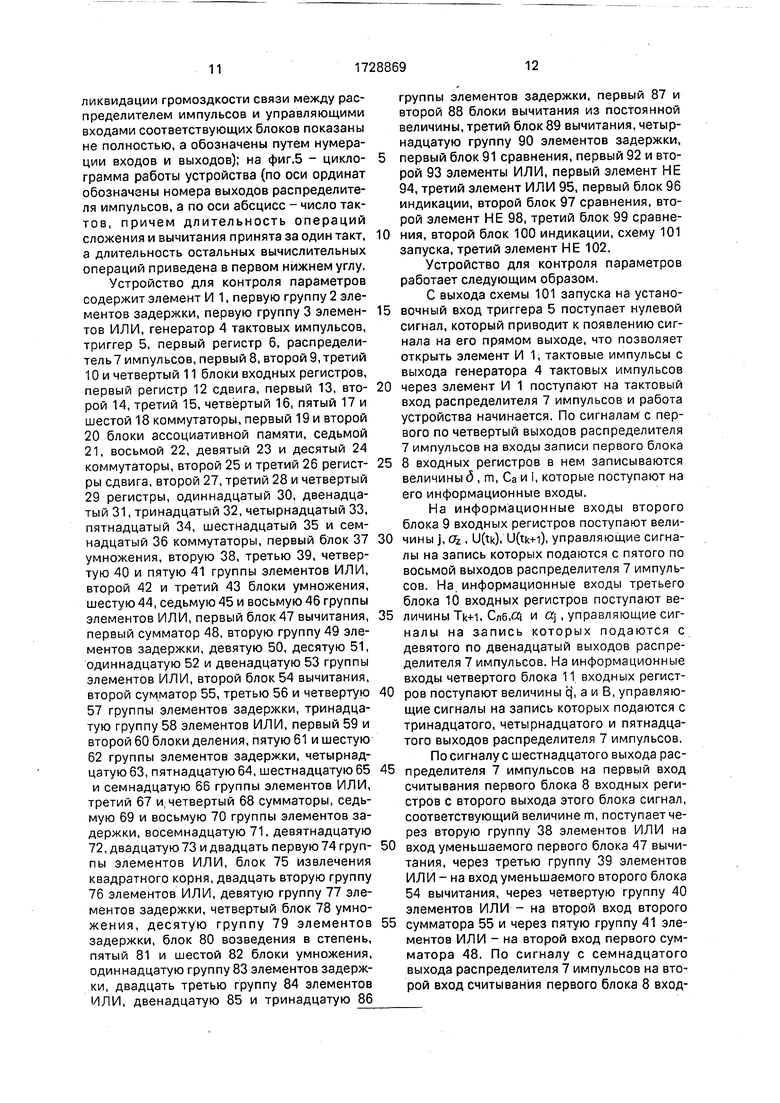

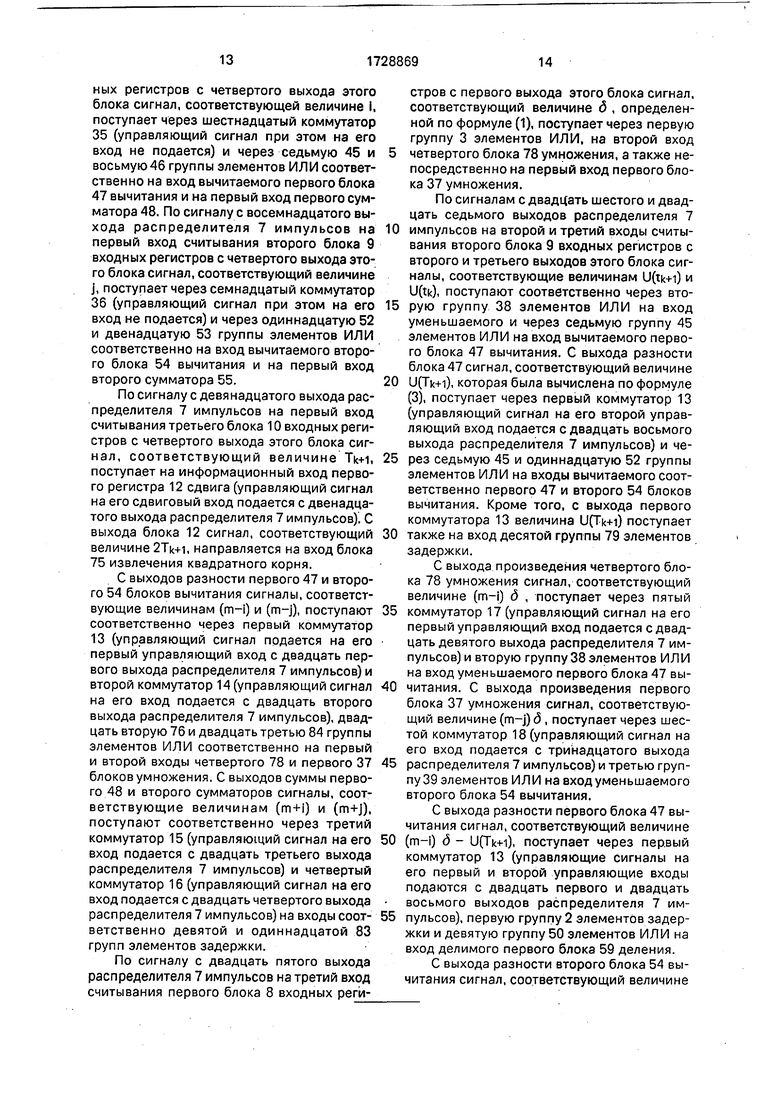

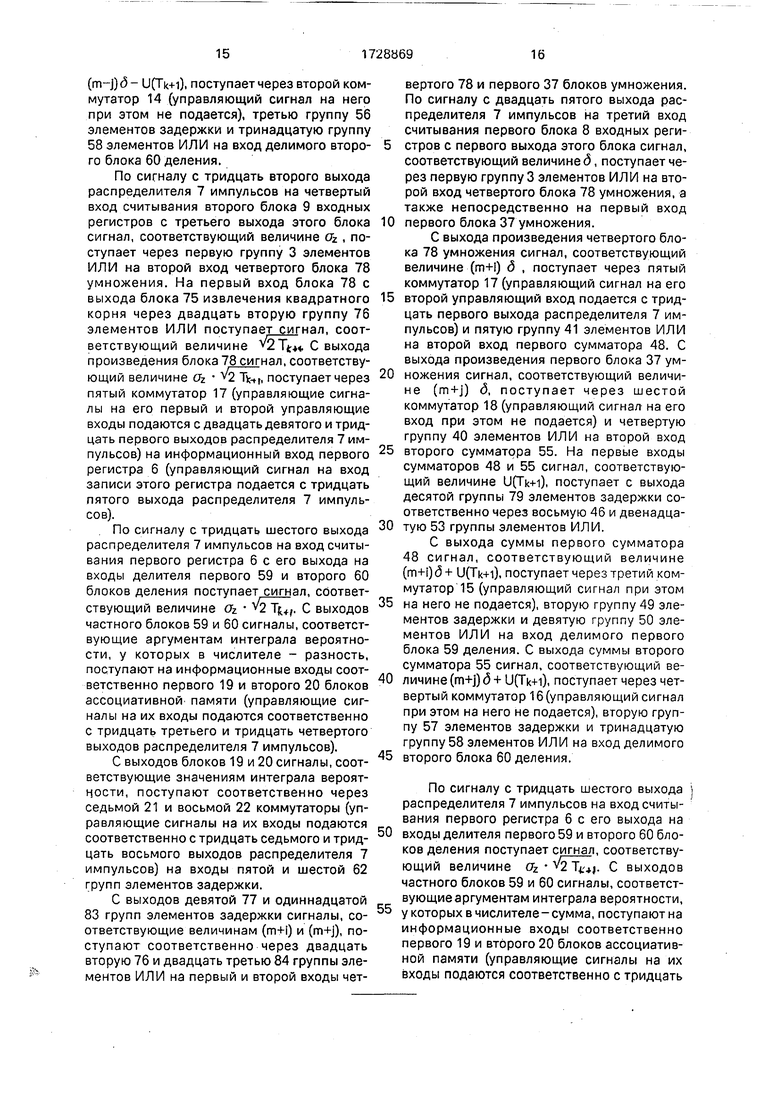

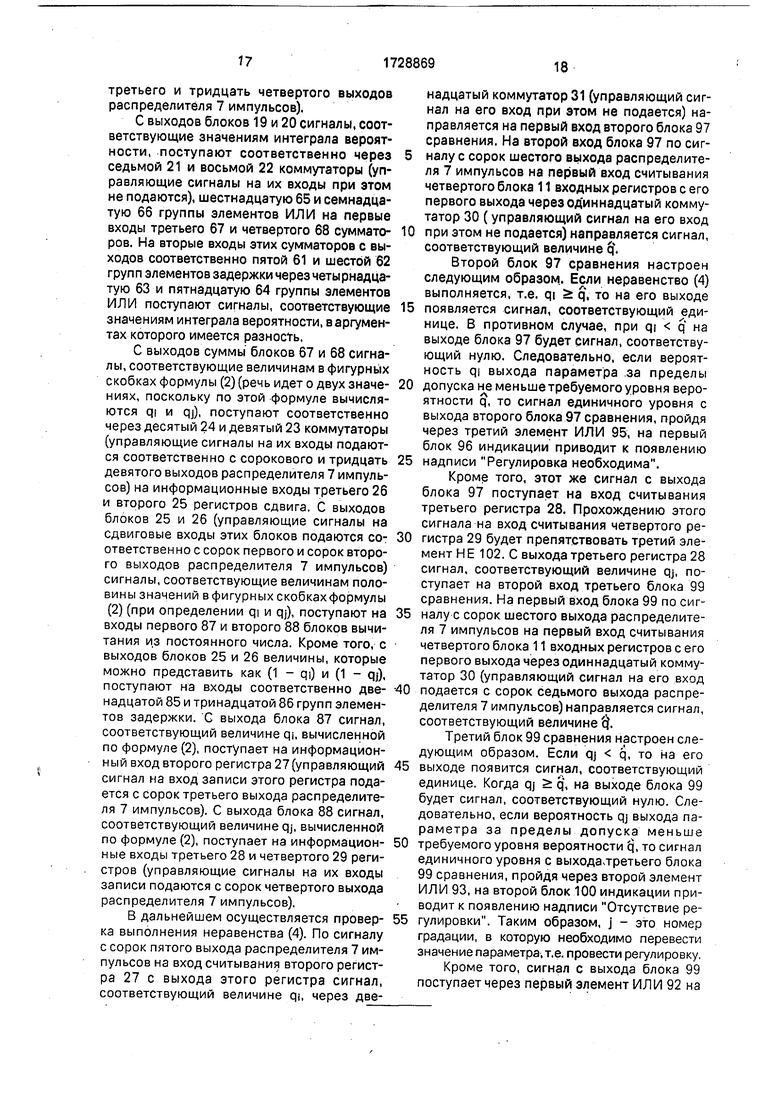

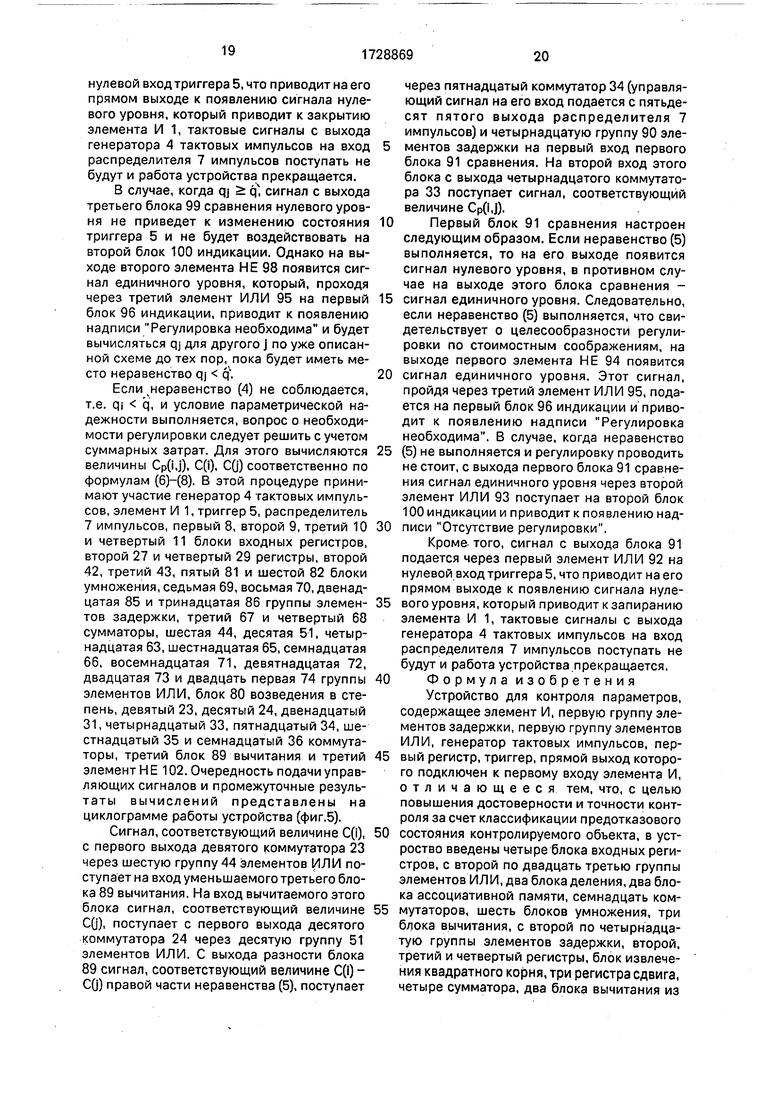

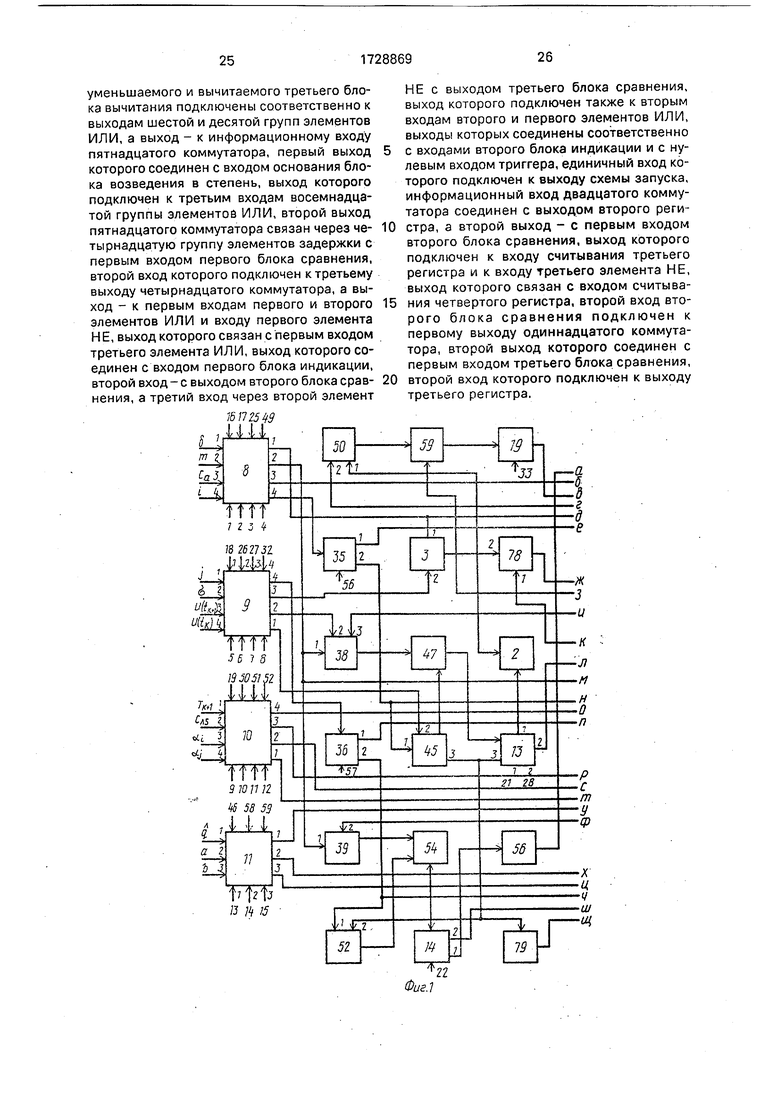

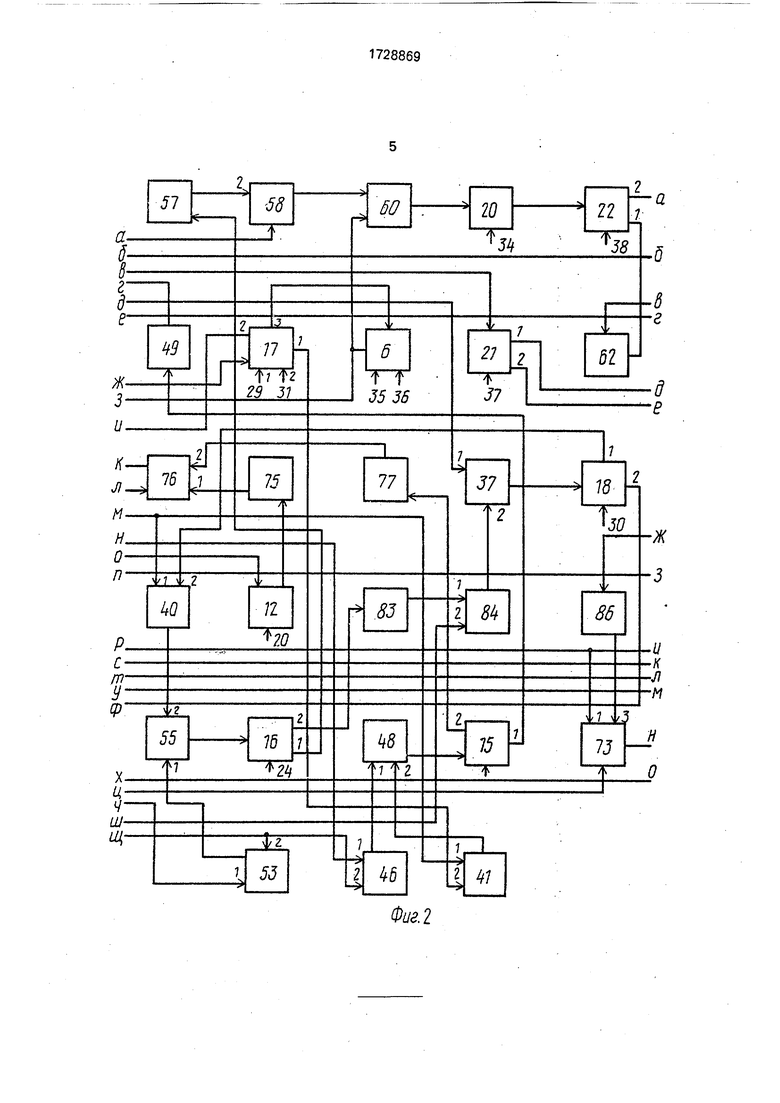

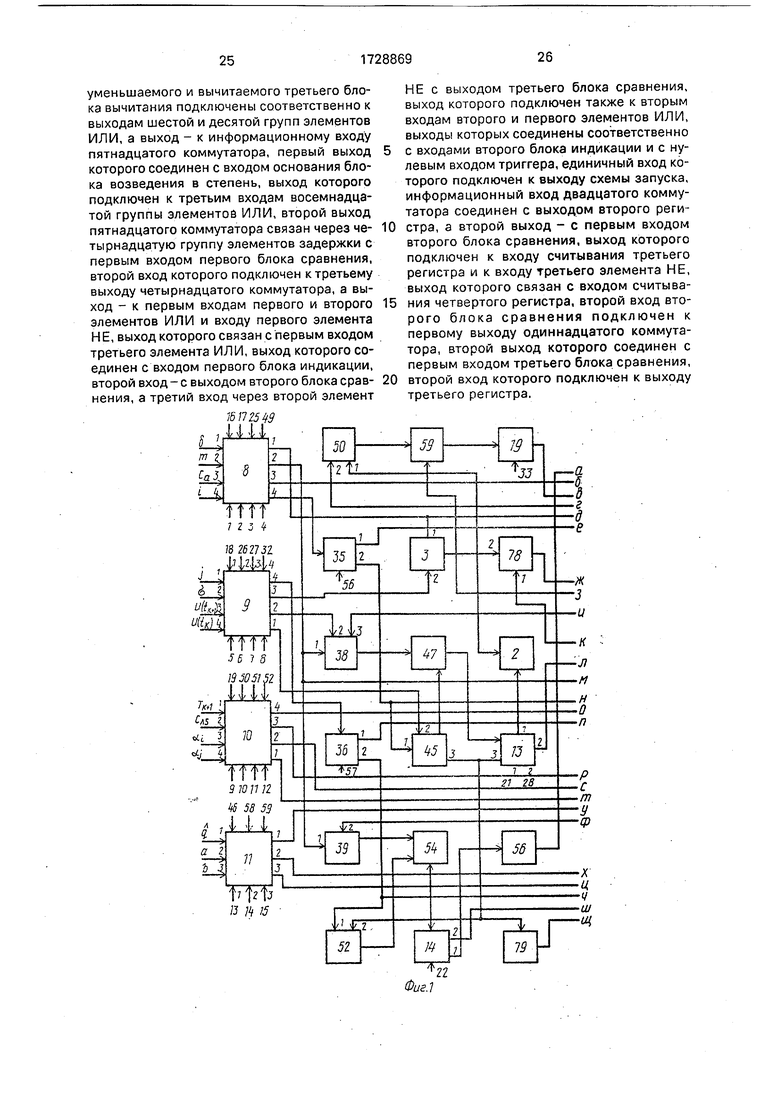

На фиг.1-4 представлены блок-схемы устройства для контроля параметров (для

ликвидации громоздкости связи между распределителем импульсов и управляющими входами соответствующих блоков показаны не полностью, а обозначены путем нумерации входов и выходов); на фиг.5 - циклограмма работы устройства (по оси ординат обозначены номера выходов распределителя импульсов, а по оси абсцисс - число тактов, причем длительность операций сложения и вычитания принята за один такт, а длительность остальных вычислительных операций приведена в первом нижнем углу. Устройство для контроля параметров содержит элемент И 1, первую группу 2 элементов задержки, первую группу 3 элементов ИЛИ, генератор 4 тактовых импульсов, триггер 5, первый регистр 6, распределитель импульсов, первый 8, второй 9, третий 10 и четвертый 11 блоки входных регистров, первый регистр 12 сдвига, первый 13, второй 14, третий 15, четвёртый 16, пятый 17 и шестой 18 коммутаторы, первый 19 и второй 20 блоки ассоциативной памяти, седьмой 21, восьмой 22, девятый 23 и десятый 24 коммутаторы, второй 25 и третий 26 регистры сдвига, второй 27, третий 28 и четвертый 29 регистры, одиннадцатый 30, двенадцатый 31, тринадцатый 32, четырнадцатый 33, пятнадцатый 34, шестнадцатый 35 и семнадцатый 36 коммутаторы, первый блок 37 умножения, вторую 38, третью 39, четвертую 40 и пятую 41 группы элементов ИЛИ, второй 42 и третий 43 блоки умножения, шестую44, седьмую 45 и восьмую 46 группы элементов ИЛИ, первый блок 47 вычитания, первый сумматор 48, вторую группу 49 элементов задержки, девятую 50, десятую 51, одиннадцатую 52 и двенадцатую 53 группы элементов ИЛИ, второй блок 54 вычитания, второй сумматор 55, третью 56 и четвертую 57 группы элементов задержки, тринадцатую группу 58 элементов ИЛИ, первый 59 и второй 60 блоки деления, пятую 61 и шестую 62 группы элементов задержки, четырнадцатую 63, пятнадцатую 64, шестнадцатую 65 и семнадцатую 66 группы элементов ИЛИ, третий 67 и, четвертый 68 сумматоры, седьмую 69 и восьмую 70 группы элементов задержки, восемнадцатую 71, девятнадцатую 72, двадцатую 73 и двадцать первую 74 груп- пы элементов ИЛИ, блок 75 извлечения квадратного корня, двадцать вторую группу 76 элементов ИЛИ, девятую группу 77 элементов задержки, четвертый блок 78 умножения, десятую группу 79 элементов задержки, блок 80 возведения в степень, пятый 81 и шестой 82 блоки умножения, одиннадцатую группу 83 элементов задержки, двадцать третью группу 84 элементов ИЛИ, двенадцатую 85 и тринадцатую 86

группы элементов задержки, первый 87 и второй 88 блоки вычитания из постоянной величины, третий блок 89 вычитания, четырнадцатую группу 90 элементов задержки,

первый блок 91 сравнения, первый 92 и второй 93 элементы ИЛИ, первый элемент НЕ 94, третий элемент ИЛИ 95, первый блок 96 индикации, второй блок 97 сравнения, второй элемент НЕ 98, третий блок 99 сравнения, второй блок 100 индикации, схему 101 запуска, третий элемент НЕ 102.

Устройство для контроля параметров работает следующим образом,

С выхода схемы 101 запуска на установочный вход триггера 5 поступает нулевой сигнал, который приводит к появлению сигнала на его прямом выходе, что позволяет открыть элемент И 1, тактовые импульсы с выхода генератора 4 тактовых импульсов

через элемент И 1 поступают на тактовый вход распределителя 7 импульсов и работа устройства начинается. По сигналам с первого по четвертый выходов распределителя 7 импульсов на входы записи первого блока

8 входных регистров в нем записываются величины б , т, Са и i, которые поступают на его информационные входы.

На информационные входы второго блока 9 входных регистров поступают величины j, 72 , U(tk), U(tk+i), управляющие сигналы на запись которых подаются с пятого по восьмой выходов распределителя 7 импульсов. На, информационные входы третьего блока 10 входных регистров поступают величины Тм-1, СлбД и а, управляющие сигналы на запись которых подаются с девятого по двенадцатый выходов распределителя 7 импульсов. На информационные входы четвертого блока 11 входных регистров поступают величины cj, а и В, управляющие сигналы на запись которых подаются с тринадцатого, четырнадцатого и пятнадцатого выходов распределителя 7 импульсов. По сигналу с шестнадцатого выхода распределителя 7 импульсов на первый вход считывания первого блока 8 входных регистров с второго выхода этого блока сигнал, соответствующий величине т, поступает через вторую группу 38 элементов ИЛИ на

вход уменьшаемого первого блока 47 вычитания, через третью группу 39 элементов ИЛИ - на вход уменьшаемого второго блока 54 вычитания, через четвертую группу 40 элементов ИЛИ - на второй вход второго

сумматора 55 и через пятую группу 41 элементов ИЛИ - на второй вход первого сумматора 48. По сигналу с семнадцатого выхода распределителя 7 импульсов на второй вход считывания первого блока 8 входных регистров с четвертого выхода этого блока сигнал, соответствующей величине I, поступает через шестнадцатый коммутатор

35(управляющий сигнал при этом на его вход не подается) и через седьмую 45 и восьмую46 группы элементов ИЛИ соответственно на вход вычитаемого первого блока 47 вычитания и на первый вход первого сумматора 48. По сигналу с восемнадцатого выхода распределителя 7 импульсов на первый вход считывания второго блока 9 входных регистров с четвертого выхода этого блока сигнал, соответствующий величине j, поступает через семнадцатый коммутатор

36(управляющий сигнал при этом на его вход не подается) и через одиннадцатую 52 и двенадцатую 53 группы элементов ИЛИ соответственно на вход вычитаемого второго блока 54 вычитания и на первый вход второго сумматора 55.

По сигналу с девянадцатого выхода распределителя 7 импульсов на первый вход считывания третьего блока 10 входных регистров с четвертого выхода этого блока сигнал, соответствующий величине Tk+1, поступает на информационный вход первого регистра 12 сдвига (управляющий сигнал на его сдвиговый вход подается с двенадцатого выхода распределителя 7 импульсов) С выхода блока 12 сигнал, соответствующий величине 2Tk+i, направляется на вход блока 75 извлечения квадратного корня.

С выходов разности первого 47 и второго 54 блоков вычитания сигналы, соответствующие величинам (m-i) и (m-j), поступают соответственно через первый коммутатор 13 (управляющий сигнал подается на его первый управляющий вход с двадцать первого выхода распределителя 7 импульсов) и второй коммутатор 14 (управляющий сигнал на его вход подается с двадцать второго выхода распределителя 7 импульсов), двадцать вторую 76 и двадцать третью 84 группы элементов ИЛИ соответственно на первый и второй входы четвертого 78 и первого 37 блоков умножения. С выходов суммы первого 48 и второго сумматоров сигналы, соответствующие величинам (m+i) и (m+j), поступают соответственно через третий коммутатор 15 (управляющий сигнал на его вход подается с двадцать третьего выхода распределителя 7 импульсов) и четвертый коммутатор 16 (управляющий сигнал на его вход подается с двадцать четвертого выхода распределителя 7 импульсов) на входы соответственно девятой и одиннадцатой 83 групп элементов задержки.

По сигналу с двадцать пятого выхода распределителя 7 импульсов на третий вход считывания первого блока 8 входных регистров с первого выхода этого блока сигнал, соответствующий величине 6 , определенной по формуле (1), поступает через первую группу 3 элементов ИЛИ, на второй вход

четвертого блока 78 умножения, а также непосредственно на первый вход первого блока 37 умножения.

По сигналам с двадцать шестого и двадцать седьмого выходов распределителя 7

импульсов на второй и третий входы считывания второго блока 9 входных регистров с второго и третьего выходов этого блока сигналы, соответствующие величинам U(tk+i) и U(tk), поступают соответственно через вторую группу 38 элементов ИЛИ на вход уменьшаемого и через седьмую группу 45 элементов ИЛИ на вход вычитаемого первого блока 47 вычитания. G выхода разности блока 47 сигнал, соответствующий величине

U(Tk+i), которая была вычислена по формуле (3), поступает через первый коммутатор 13 (управляющий сигнал на его второй управляющий вход подается с двадцать восьмого выхода распределителя 7 импульсов) и через седьмую 45 и одиннадцатую 52 группы элементов ИЛИ на входы вычитаемого соответственно первого 47 и второго 54 блоков вычитания. Кроме того, с выхода первого коммутатора 13 величина U(Tk-n) поступает

также на вход десятой группы 79 элементов задержки.

С выхода произведения четвертого блока 78 умножения сигнал, соответствующий величине (m-i) д , поступает через пятый

коммутатор 17 (управляющий сигнал на его первый управляющий вход подается с двадцать девятого выхода распределителя 7 импульсов) и вторую группу38 элементов ИЛИ на вход уменьшаемого первого блока 47 вычитания. С выхода произведения первого блока 37 умножения сигнал, соответствующий величине (m-j)5 , поступает через шестой коммутатор 18 (управляющий сигнал на его вход подается с тринадцатого ЁЫХОДЭ

распределителя 7 импульсов) и третью груп- пу39 элементов ИЛИ на вход уменьшаемого второго блока 54 вычитания.

С выхода разности первого блока 47 вычитания сигнал, соответствующий величине

(m-i) 6 - U(Tk+i), поступает через первый коммутатор 13 (управляющие сигналы на его первый и второй управляющие входы подаются с двадцать первого и двадцать восьмого выходов распределителя 7 импульсов), первую группу 2 элементов задержки и девятую группу 50 элементов ИЛИ на вход делимого первого блока 59 деления.

С выхода разности второго блока 54 вычитания сигнал, соответствующий величине

(m-j)d- U(Tk+i), поступает через второй коммутатор 14 (управляющий сигнал на него при этом не подается), третью группу 56 элементов задержки и тринадцатую группу 58 элементов ИЛИ на вход делимого второго блока 60 деления.

По сигналу с тридцать второго выхода распределителя 7 импульсов на четвертый вход считывания второго блока 9 входных регистров с третьего выхода этого блока сигнал, соответствующий величине сг2 , поступает через первую группу 3 элементов ИЛИ на второй вход четвертого блока 78 умножения. На первый вход блока 78 с выхода блока 75 извлечения квадратного корня через двадцать вторую группу 76 элементов ИЛИ поступает сигнал, соответствующий величине 2 Т.ц, С выхода произведения блока 78 сигнал, соответствующий величине ffz 2 ТУН,, поступает через пятый коммутатор 17 (управляющие сигналы на его первый и второй управляющие входы подаются с двадцать девятого и тридцать первого выходов распределителя 7 импульсов) на информационный вход первого регистра 6 (управляющий сигнал на вход записи этого регистра подается с тридцать пятого выхода распределителя 7 импульсов).

По сигналу с тридцать шестого выхода распределителя 7 импульсов на вход считывания первого регистра 6 с его выхода на входы делителя первого 59 и второго 60 блоков деления поступает сигнал, соответствующий величине Oz 2 +t- С выходов частного блоков 59 и 60 сигналы, соответствующие аргументам интеграла вероятности, у которых в числителе - разность, поступают на информационные входы соответственно первого 19 и второго 20 блоков ассоциативной памяти (управляющие сигналы на их входы подаются соответственно с тридцать третьего и тридцать четвертого выходов распределителя 7 импульсов).

С выходов блоков 19 и 20 сигналы, соответствующие значениям интеграла вероятности, поступают соответственно через седьмой 21 и восьмой 22 коммутаторы (управляющие сигналы на их входы подаются соответственно с тридцать седьмого и тридцать восьмого выходов распределителя 7 импульсов) на входы пятой и шестой 62 групп элементов задержки.

С выходов девятой 77 и одиннадцатой 83 групп элементов задержки сигналы, соответствующие величинам (m+i) и (m+j), поступают соответственно через двадцать вторую 76 и двадцать третью 84 группы элементов ИЛИ на первый и второй входы чет0

5

0

5

0

5

0

5

0

5

вертого 78 и первого 37 блоков умножения. По сигналу с двадцать пятого выхода распределителя 7 импульсов на третий вход считывания первого блока 8 входных регистров с первого выхода этого блока сигнал, соответствующий величине д, поступает через первую группу 3 элементов ИЛИ на второй вход четвертого блока 78 умножения, а также непосредственно на первый вход первого блока 37 умножения.

С выхода произведения четвертого блока 78 умножения сигнал, соответствующий величине (m+i) 6 , поступает через пятый коммутатор 17 (управляющий сигнал на его второй управляющий вход подается с тридцать первого выхода распределителя 7 импульсов) и пятую группу 41 элементов ИЛИ на второй вход первого сумматора 48. С выхода произведения первого блока 37 умножения сигнал, соответствующий величине (m+j) д, поступает через шестой коммутатор 18 (управляющий сигнал на его вход при этом не подается) и четвертую группу 40 элементов ИЛИ на второй вход второго сумматора 55. На первые входы сумматоров 48 и 55 сигнал, соответствующий величине U(Tk+i), поступает с выхода десятой группы 79 элементов задержки соответственно через восьмую 46 и двенадцатую 53 группы элементов ИЛИ.

С выхода суммы первого сумматора 48 сигнал, соответствующий величине (m+i) д + U(Tk+i), поступает через третий коммутатор 15 (управляющий сигнал при этом на него не подается), вторую группу 49 элементов задержки и девятую группу 50 элементов ИЛИ на вход делимого первого блока 59 деления. С выхода суммы второго сумматора 55 сигнал, соответствующий величине (m+j) д + U(Tk+i), поступает через четвертый коммутатор 16 (управляющий сигнал при этом на него не подается), вторую группу 57 элементов задержки и тринадцатую группу 58 элементов ИЛИ на вход делимого второго блока 60 деления.

По сигналу с тридцать шестого выхода распределителя 7 импульсов на вход считывания первого регистра 6 с его выхода на входы делителя первого 59 и второго 60 блоков деления поступает сигнал, соответствующий величине ffz 2 Тщ. С выходов частного блоков 59 и 60 сигналы, соответствующие аргументам интеграла вероятности, у которых в числителе - сумма, поступают на информационные входы соответственно первого 19 и второго 20 блоков ассоциативной памяти (управляющие сигналы на их входы подаются соответственно с тридцать

третьего и тридцать четвертого выходов распределителя 7 импульсов).

С выходов блоков 19 и 20 сигналы, соответствующие значениям интеграла вероятности, поступают соответственно через седьмой 21 и восьмой 22 коммутаторы (управляющие сигналы на их входы при этом не подаются), шестнадцатую 65 и семнадцатую 66 группы элементов ИЛИ на первые входы третьего 67 и четвертого 68 суммато- ров. На вторые входы этих сумматоров с выходов соответственно пятой 61 и шестой 62 групп элементов задержки через четырнадцатую 63 и пятнадцатую 64 группы элементов ИЛИ поступают сигналы, соответствующие значениям интеграла вероятности, в аргументах которого имеется разность.

С выходов суммы блоков 67 и 68 сигналы, соответствующие величинам в фигурных скобках формулы (2) (речь идет о двух значе- ниях, поскольку по этой формуле вычисляются qi и qj), поступают соответственно через десятый 24 и девятый 23 коммутаторы (управляющие сигналы на их входы подаются соответственно с сорокового и тридцать девятого выходов распределителя 7 импульсов) на информационные входы третьего 26 и второго 25 регистров сдвига. С выходов блоков 25 и 26 (управляющие сигналы на сдвиговые входы этих блоков подаются со- ответственно с сорок первого и сорок второго выходов распределителя 7 импульсов) сигналы, соответствующие величинам половины значений в фигурных скобках формулы (2) (при определении qi и qj), поступают на входы первого 87 и второго 88 блоков вычитания из постоянного числа. Кроме того, с выходов блоков 25 и 26 величины, которые можно представить как (1 - qi) и (1 - qj), поступают на входы соответственно две- надцатой 85 и тринадцатой 86 групп элементов задержки. С выхода блока 87 сигнал, соответствующий величине qi, вычисленной по формуле (2), поступает на информационный вход второго регистра 27(управляющий сигнал на вход записи этого регистра подается с сорок третьего выхода распределителя 7 импульсов). С выхода блока 88 сигнал, соответствующий величине qj, вычисленной по формуле (2), поступает на информацион- ные входы третьего 28 и четвертого 29 регистров (управляющие сигналы на их входы записи подаются с сорок четвертого выхода распределителя 7 импульсов).

В дальнейшем осуществляется провер- ка выполнения неравенства (4). По сигналу с сорок пятого выхода распределителя 7 импульсов на вход считывания второго регистра 27 с выхода этого регистра сигнал, соответствующий величине qi, через двенадцатый коммутатор 31 (управляющий сигнал на его вход при этом не подается) направляется на первый вход второго блока 97 сравнения. На второй вход блока 97 по сигналу с сорок шестого выхода распределителя 7 импульсов на первый вход считывания четвертого блока 11 входных регистров с его первого выхода через одиннадцатый коммутатор 30 (управляющий сигнал на его вход при этом не подается) направляется сигнал, соответствующий величине q.

Второй блок 97 сравнения настроен следующим образом. Если неравенство (4) выполняется, т.е. qi 2: q, то на его выходе появляется сигнал, соответствующий единице. В противном случае, при qi q на выходе блока 97 будет сигнал, соответствующий нулю. Следовательно, если вероятность qi выхода параметра .за пределы допуска не меньше требуемого уровня вероятности q, то сигнал единичного уровня с выхода второго блока 97 сравнения, пройдя через третий элемент ИЛИ 95, на первый блок 96 индикации приводит к появлению надписи Регулировка необходима.

Кроме того, этот же сигнал с выхода блока 97 поступает на вход считывания третьего регистра 28. Прохождению этого сигнала на вход считывания четвертого регистра 29 будет препятствовать третий элемент НЕ 102. С выхода третьего регистра 28 сигнал, соответствующий величине qj, поступает на второй вход третьего блока 99 сравнения. На первый вход блока 99 по сигналу с сорок шестого выхода распределителя 7 импульсов на первый вход считывания четвертого блока 11 входных регистров с его первого выхода через одиннадцатый коммутатор 30 (управляющий сигнал на его вход подается с сорок седьмого выхода распределителя 7 импульсов) направляется сигнал, соответствующий величине q4.

Третий блок 99 сравнения настроен следующим образом. Если qj q, то на его выходе появится сигнал, соответствующий единице. Когда qj q, на выходе блока 99 будет сигнал, соответствующий нулю. Следовательно, если вероятность qj выхода параметра за пределы допуска меньше требуемого уровня вероятности q, то сигнал единичного уровня с выходал-ретьего блока 99 сравнения, пройдя через второй элемент ИЛИ 93, на второй блок 100 индикации приводит к появлению надписи Отсутствие регулировки. Таким образом, j - это номер градации, в которую необходимо перевести значение параметра, т.е. провести регулировку.

Кроме того, сигнал с выхода блока 99 поступает через первый элемент ИЛИ 92 на

нулевой вход триггера 5, что приводит на его прямом выходе к появлению сигнала нулевого уровня, который приводит к закрытию элемента И 1, тактовые сигналы с выхода генератора 4 тактовых импульсов на вход распределителя 7 импульсов поступать не будут и работа устройства прекращается.

В случае, когда QJ q, сигнал с выхода третьего блока 99 сравнения нулевого уровня не приведет к изменению состояния триггера 5 и не будет воздействовать на второй блок 100 индикации. Однако на выходе второго элемента НЕ 98 появится сигнал единичного уровня, который, проходя через третий элемент ИЛИ 95 на первый блок 96 индикации, приводит к появлению надписи Регулировка необходима и будет вычисляться qj для другого j по уже описанной схеме до тех пор, пока будет иметь место неравенство QJ q .

Если неравенство (4) не соблюдается, т.е. qi q, и условие параметрической надежности выполняется, вопрос о необходимости регулировки следует решить с учетом суммарных затрат. Для этого вычисляются величины Cp(i.j), C(i), CQ) соответственно по формулам (6)-(8). В этой процедуре принимают участие генератор 4 тактовых импульсов, элемент И 1, триггер 5, распределитель 7 импульсов, первый 8, второй 9, третий 10 и четвертый 11 блоки входных регистров, второй 27 и четвертый 29 регистры, второй 42, третий 43, пятый 81 и шестой 82 блоки умножения, седьмая 69, восьмая 70, двенадцатая 85 и тринадцатая 86 группы элемен- тов задержки, третий 67 и четвертый 68 сумматоры, шестая 44, десятая 5-1, четырнадцатая 63, шестнадцатая 65, семнадцатая 66, восемнадцатая 71, девятнадцатая 72, двадцатая 73 и двадцать первая 74 группы элементов ИЛИ, блок 80 возведения в степень, девятый 23, десятый 24, двенадцатый 31, четырнадцатый 33, пятнадцатый 34, шестнадцатый 35 и семнадцатый 36 коммутаторы, третий блок 89 вычитания и третий элемент НЕ 102. Очередность подачи управляющих сигналов и промежуточные результаты вычислений представлены на циклограмме работы устройства (фиг.5).

Сигнал, соответствующий величине C(i), с первого выхода девятого коммутатора 23 через шестую группу 44 элементов ИЛИ поступает на вход уменьшаемого третьего блока 89 вычитания. На вход вычитаемого этого блока сигнал, соответствующий величине CQ), поступает с первого выхода десятого коммутатора 24 через десятую группу 51 элементов ИЛИ. С выхода разности блока 89 сигнал, соответствующий величине C(i) - СО) правой части неравенства (5), поступает

через пятнадцатый коммутатор 34 (управляющий сигнал на его вход подается с пятьдесят пятого выхода распределителя 7 импульсов) и четырнадцатую группу 90 элементов задержки на первый вход первого блока 91 сравнения. На второй вход этого блока с выхода четырнадцатого коммутатора 33 поступает сигнал, соответствующий величине Cp(i.j).

Первый блок 91 сравнения настроен следующим образом. Если неравенство (5) выполняется, то на его выходе появится сигнал нулевого уровня, в противном случае на выходе этого блока сравнения - сигнал единичного уровня. Следовательно, если неравенство (5) выполняется, что свидетельствует о целесообразности регулировки по стоимостным соображениям, на выходе первого элемента НЕ 94 появится сигнал единичного уровня. Этот сигнал, пройдя через третий элемент ИЛИ 95, подается на первый блок 96 индикации и приводит к появлению надписи Регулировка необходима. В случае, когда неравенство (5) не выполняется и регулировку проводить не стоит, с выхода первого блока 91 сравнения сигнал единичного уровня через второй элемент ИЛИ 93 поступает на второй блок 100 индикации и приводит к появлению надписи Отсутствие регулировки.

Кроме того, сигнал с выхода блока 91 подается через первый элемент ИЛИ 92 на нулевой вход триггера 5, что приводит на его прямом выходе к появлению сигнала нулевого уровня, который приводит к запиранию элемента И 1, тактовые сигналы с выхода генератора 4 тактовых импульсов на вход распределителя 7 импульсов поступать не будут и работа устройства прекращается.

Формула изобретения

Устройство для контроля параметров, содержащее элемент И, первую группу элементов задержки, первую группу элементов ИЛИ, генератор тактовых импульсов, первый регистр, триггер, прямой выход которого подключен к первому входу элемента И, отличающееся тем, что, с целью повышения достоверности и точности контроля за счет классификации предотказового состояния контролируемого объекта, в уст- роство введены четыре блока входных регистров, с второй по двадцать третью группы элементов ИЛ И, два блока деления, два блока ассоциативной памяти, семнадцать коммутаторов, шесть блоков умножения, три блока вычитания, с второй по четырнадцатую группы элементов задержки, второй, третий и четвертый регистры, блок извлечения квадратного корня,три регистра сдвига, четыре сумматора, два блока вычитания из

постоянной величины, три элемента ИЛИ, блок возведения в степень, три блока сравнения, два блока индикации, три элемента НЕ, схема запуска и распределитель импульсов, с первого по шестидесятый выходы которого соединены соответственно с первого по четвертый входами записи первого, второго и третьего блоков входных регистров, с первого по третий входами записи четвертого блока входных регистров, с пер- вым и вторым входами считывания, первого блока входных регистров, с первыми входами считывания второго и третьего блоков входных регистров, со сдвиговым входом первого регистра сдвига, с первым управля- ющим входом первого коммутатора, с управляющими входами второго, третьего и четвертого коммутаторов, с третьим входом считывания первого блока входных регистров, с вторым и третьим входами считыва- ния второго блока входных регистров, с вторым управляющим входом первого коммутатора, с первым управляющим входом пятого коммутатора, с управляющим входом шестого коммутатора, с вторым управ- ля ющим входом пятого коммутатора, с четвертым входом считывания второго блока входных регистров, с управляющими входами первого и второго блоков ассоциативной памяти, с входами записи и считывания первого регистра, с управляющими входами седьмого, восьмого, девятого и десятого коммутаторов со сдвиговыми входами второго и третьего регистров сдвига, с входами записи второго, третьего и четвертого регистров, с входом считывания второго регистра, с первым входом считывания четвертого блока входных регистров, с управляющими входами одиннадцатого и двенадцатого коммутаторов, с четвертым входом считывания первого блока входных регистров, с вторым и третьим входами считывания третьего блока входных регистров, с управляющим входом тринадцатого коммутатора, с первым управляющим входом четырнадцатого коммутатора, с четвертым входом считывания третьего блока входных .регистров, с управляющими входами пятнадцатого, шестнадцатого и семнадцатого коммутаторов, с вторым и третьим входами считывания четвертого блока входных регистров, с вторым управляющим входом четырнадцатого коммутатора, тактовый вход распределителя импульсов подключен к выходу элемента И, второй вход которого сое- динен с выходом генератора тактовых импульсов, с первого по четвертый информационные входы первого блока входных регистров являются первой группой информационных входов устройства, первый выход первого блока входных регистров подключен к первым входам первой группы элементов ИЛИ и к входу первого сомножителя первого блока умножения, второй вход - к первым входам второй,-третьей, четвертой и пятой групп элементов ИЛИ, третий выход - к входам первых сомножителей второго и третьего блоков умножения, а четвертый выход-к информационному входу шестнадцатого коммутатора, первый выход которого соединен с первыми входами шестой группы элементов ИЛИ, а второй выход - с первыми входами седьмой и восьмой групп элементов ИЛИ, выходы которых подключены соответственно к входу вычитаемого первого блока вычитания и к входу первого слагаемого первого сумматора, выходы которых соединены с информационными входами соответственно первого и третьего коммутаторов, первые выходы которых соответственно через первую и вторую группы элементов задержки подключены соответственно к первым и вторым входам девятой группы элементов ИЛИ, с первого по четвертый информационные входы второго блока входных регистров являются второй группой информационных входов устройства, первый, второй и третий выходы этого блока подключены ко вторым входам соответственно седьмой, второй и первой групп элементов ИЛИ, а четвертый выход - к информационному входу семнадцатого коммутатора, первый выход которого соединен с первыми входами десятой группы элементов ИЛИ, а второй выход - с первыми входами одиннадцатой и двенадцатой групп элементов ИЛИ, выходы которых подключены соответственно к входу вычитаемого второго блока вычитания и входу первого слагаемого второго сумматора, выходы которых соединены с информационными входами соответственно второго и четвертого коммутаторов, первые выходы которых соответственно через третью и четвертую группы элементов задержки подключены соответственно к первым и вторым входам тринадцатой группы элементов ИЛИ, выходы десятой и тринадцатой групп элементов ИЛИ связаны с входами делимого соответственно первого и второго блоков деления, выходы которых подключены к информационным входам соответственно первого и второго блоков ассоциативной памяти, выходы которых соединены с информационными входами соответственно седьмого и восьмого коммутаторов, первые выходы которых подключены соответственно через пятую и шестую группы элементов задержки к первым входам соответственно четырнадцатой и пятнадцатой групп элементов ИЛИ, а вторые выходы - к первым входам соответственно шестнадцатой и семнадцатой групп элементов ИЛИ, вторые входы которых связаны с первыми выходами соответственно четырнадцатого и три- надцатого коммутаторов, а выходы - с входами первых слагаемых соответственно третьего и четвертого сумматоров, выходы которых подключены к информационным входам соответственно десятого и девятого коммутаторов, а входы вторых слагаемых - к выходам соответственно четырнадцатой и тринадцатой групп элементов ИЛИ, вторые входы которых соединены соответственно через седьмую и восьмую группы элементов задержки с выходами соответственно третьего и второго блоков умножения, входы вторых сомножителей которых подключены соответственно к первому выходу двенадцатого коммутатора, и выходу четвертого регистра, с первого по четвертый информационные входы третьего блока входных регистров являются третьей группой информационных входов устройства, первый и второй выходы третьего блока вход- ных регистров соединены с первыми входами соответственно восемнадцатой и девятнадцатой групп элементов ИЛИ, третий выход - с первыми входами двадцатой и двадцать первой групп элементов ИЛИ, а четвертый выход - с информационным входом первого регистра сдвига, выход которого через блок извлечения квадратного корня подключен к первым входам двадцать второй группы элементов ИЛИ, второй вход которой связан через девятую группу элементов задержки с вторым выходом третьего коммутатора, третий вход - с вторым выходом первого коммутатора, а выход - с входом первого сомножителя четвертого блока умножения, вход второго сомножителя которого подключен к выходу первой группы элементов ИЛИ, а выход - к информационному входу пятого коммутатора, первый выход которого соединен с вторыми входами пятой группы элементов ИЛИ, выход которой подключен к входу второго слагаемого первого сумматора, второй выход пятого коммутатора соединен с третьими входами второй группы элементов ИЛИ, вы- ход которой подключен к входу уменьшаемого первого блока вычитания, третий выход пятого коммутатора соединен с информационным входом первого регистра, выход которого подключен к входам делите- ля первого и второго блоков деления, третий выход первого коммутатора связан с вторыми входами одиннадцатой группы элементов ИЛИ, а также через десятую группу элементов задержки с вторыми входами

восьмой и двенадцатой групп элементов ИЛИ, с первого по третий информационные входы четвертого блока входных регистров являются четертой группой информационных входов устройства, первый выход третьего блока входных регистров подключен к информационному входу одиннадцатого коммутатора, второй выход - к входу показателя степени блока возведения в степень, а третий выход - к вторым входам двенадцатой группы элементов ИЛИ, выходы двадцатой и двадцать первой групп элементов ИЛИ соединены с входами первых сомножителей соответственно пятого и шестого блоков умножения, входы вторых сомножителей которых подключены к выходам соответственно восемнадцатой и девятнадцатой групп элементов ИЛИ, а выходы - к информационным входам соответственно четырнадцатого и тринадцатого коммутаторов, вторые выходы которых связаны с вторыми входами соответственно восемнадцатой и девятнадцатой групп элементов ИЛИ, второй выход четвертого коммутатора подключен через одиннадцатую группу элементов задержки к первым входам двадцать третьей группы элементов ИЛИ, второй вход которой соединен с вторым выходом второго коммутатора, а выход - с входом второго сомножителя первого блока умножения, выход которого подключен к информационному входу шестого коммутатора, первый выход которого связан с вторыми входами четвертой группы элементов ИЛИ, выход которой подключен к входу второго слагаемого второго сумматора, второй выход шестого коммутатора соединен с вторыми входами третьей группы элементов ИЛИ, выход которой подключен к входу уменьшаемого второго блока вычитания, первые выходы девятого и десятого коммутаторов связаны с вторыми входами соответственно шестой и десятой групп элементов ИЛИ, а вторые выходы - с информационными входами соответственно второго и третьего регистров сдвига, выходы которых соответственно через двенадцатую и тринадцатую группы элементов задержки соединены соответственно с вторыми и третьими входами двадцать первой и двадцатой групп элементов ИЛИ, выход второго регистра сдвига подключен к входу вычитаемого первого блока вычитания из постоянной величины, выход которого связан с информационным входом второго регистра, выход третьего регистра сдвига соединен с входом вычитаемого второго блока вычитания из постоянной величины, выход которого связан с информационными входами третьего и четвертого регистров, входы

уменьшаемого и вычитаемого третьего блока вычитания подключены соответственно к выходам шестой и десятой групп элементов ИЛИ, а выход - к информационному входу пятнадцатого коммутатора, первый выход которого соединен с входом основания блока возведения в степень, выход которого подключен к третьим входам восемнадцатой группы элементов ИЛИ, второй выход пятнадцатого коммутатора связан через четырнадцатую группу элементов задержки с первым входом первого блока сравнения, второй вход которого подключен к третьему выходу четырнадцатого коммутатора, а выход - к первым входам первого и второго элементов ИЛИ и входу первого элемента НЕ, выход которого связан с первым входом третьего элемента ИЛИ, выход которого соединен с входом первого блока индикации,

НЕ с выходом третьего блока сравнения, выход которого подключен также к вторым входам второго и первого элементов ИЛИ, выходы которых соединены соответственно

5 с входами второго блока индикации и с нулевым входом триггера, единичный вход которого подключен к выходу схемы запуска, информационный вход двадцатого коммутатора соединен с выходом второго реги10 стра, а второй выход - с первым входом второго блока сравнения, выход которого подключен к входу считывания третьего регистра и к входу третьего элемента НЕ, выход которого связан с входом считыва15 ния четвертого регистра, второй вход второго блока сравнения подключен к первому выходу одиннадцатого коммутатора, второй выход которого соединен с первым входом третьего блока сравнения,

второй вход-с выходом второго блока срав- 20 второй вход которого подключен к выходу нения, а третий вход через второй элемент третьего регистра.

ЪП25Щ

НЕ с выходом третьего блока сравнения, выход которого подключен также к вторым входам второго и первого элементов ИЛИ, выходы которых соединены соответственно

с входами второго блока индикации и с нулевым входом триггера, единичный вход которого подключен к выходу схемы запуска, информационный вход двадцатого коммутатора соединен с выходом второго регистра, а второй выход - с первым входом второго блока сравнения, выход которого подключен к входу считывания третьего регистра и к входу третьего элемента НЕ, выход которого связан с входом считывания четвертого регистра, второй вход второго блока сравнения подключен к первому выходу одиннадцатого коммутатора, второй выход которого соединен с первым входом третьего блока сравнения,

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ОЦЕНКИ ЭФФЕКТИВНОСТИ | 2006 |

|

RU2306598C1 |

| УСТРОЙСТВО ДЛЯ РЕШЕНИЯ ЗАДАЧ НЕЛИНЕЙНОГО СТОХАСТИЧЕСКОГО ПРОГРАММИРОВАНИЯ | 1991 |

|

RU2006933C1 |

| УСТРОЙСТВО ДЛЯ ВЗАИМОДЕЙСТВИЯ С ЭКСПЕРТАМИ ПРИ ОПРЕДЕЛЕНИИ КАРДИНАЛЬНОЙ СОГЛАСОВАННОЙ ОЦЕНКИ | 2004 |

|

RU2256214C1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОЙ ОЦЕНКИ ФАЗОВОЙ НАПРЯЖЕННОСТИ РЕСПОНДЕНТА | 2012 |

|

RU2492520C1 |

| УСТРОЙСТВО ДЛЯ ТЕХНИКО-ЭКОНОМИЧЕСКОЙ ОЦЕНКИ ВЫПОЛНЕНИЯ НАУЧНО-ИССЛЕДОВАТЕЛЬСКИХ И ОПЫТНО-КОНСТРУКТОРСКИХ РАБОТ | 2011 |

|

RU2470365C1 |

| УСТРОЙСТВО ДЛЯ ОЦЕНКИ ЭФФЕКТИВНОСТИ | 2001 |

|

RU2178201C1 |

| УСТРОЙСТВО ДЛЯ ОЦЕНКИ И СРАВНЕНИЯ ЭФФЕКТИВНОСТИ ФУНКЦИОНИРОВАНИЯ ОДНОТИПНЫХ ОРГАНИЗАЦИЙ | 2008 |

|

RU2363042C1 |

| УСТРОЙСТВО ДЛЯ ОЦЕНКИ И СРАВНИВАНИЯ ЭФФЕКТИВНОСТИ ФУНКЦИОНИРОВАНИЯ ОДНОТИПНЫХ ОРГАНИЗАЦИЙ | 2007 |

|

RU2349954C1 |

| УСТРОЙСТВО ДЛЯ ОЦЕНКИ ФУНКЦИИ РАСПРЕДЕЛЕНИЯ СЛУЧАЙНЫХ ВЕЛИЧИН И ЕЕ ТОЛЕРАНТНЫХ ГРАНИЦ ПО МАЛЫМ ВЫБОРКАМ | 2014 |

|

RU2553120C1 |

| Цифровой функциональный преобразователь | 1983 |

|

SU1107136A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при контроле параметров, когда необходимо выявлять предотказовые состояния технических объектов с последующей возможностью регулировки этих параметров. Устройство позволяет повысить достоверность и точность контроля за счет классификации предотказного состояния контролируемого объекта. Устройство для контроля параметров содержит четыре блока входных регистров, двадцать три группы элементов ИЛИ, два блока деления, два блока ассоциативной памяти, семнадцать коммутаторов, элемент И, шесть блоков умножения, три блока вычитания, четырнадцать групп элементов задержки, генератор тактовых импульсов, триггер, четыре регистра, блок извлечения квадратного корня три регистра сдвига, четыре сумматора, два блока вычитания из постоянной величины, три элемента ИЛИ, блок возведения в степень, три блока сравнения, два блока индикации, три элемента НЕ, схему запуска и распределитель импульсов. 5 ил. (Л С

Фиг.З

| Устройство для контроля параметров | 1985 |

|

SU1298770A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Анализатор параметрических отказов | 1985 |

|

SU1302298A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-04-23—Публикация

1990-03-21—Подача