Изобретение относится к вычислительной технике, к оборудованию для обработки данных и может быть использовано для оценки эффективности различных систем, например систем массового обслуживания (СМО).

Известно цифровое вычислительное устройство, содержащее блок ввода, запоминающий блок, дешифратор, коммутатор, шифратор, арифметический блок, блок ввода и блок управления (авторское свидетельство СССР 752345, кл. G 06 F 15/31, 1980).

Недостатком данного устройства является отсутствие возможности определения вероятности наступления события.

Наиболее близким аналогом (прототипом) является статистический анализатор, содержащий два блока хранения, два блока умножения, два блока вычитания, блок извлечения квадратного корня и сумматор (патент РФ 2015554, кл. G О6 F 17/18, 1994).

Недостатком этого устройства является отсутствие возможности оценки вероятности того, что одна случайная величина больше или меньше другой случайной величины.

Техническим результатом заявленного изобретения является возможность оценки эффективности различных систем за счет определения вероятности выполнения этими системами благодаря вычислению вероятности того, что одна случайная величина больше или меньше другой случайной величины. В качестве примера такой системы может фигурировать СМО.

Для выполнения задачи СМО необходимо, чтобы случайное число каналов обслуживания было не меньше случайного количества заявок. Следовательно, в качестве показателя эффективности функционирования СМО W можно рассматривать вероятность выполнения задачи этой системой:

- случайное располагаемое число каналов обслуживания;

- случайное располагаемое число каналов обслуживания; - случайное потребное число каналов обслуживания;

- случайное потребное число каналов обслуживания;

kи - исходное располагаемое число каналов обслуживания (без учета возможности отказов); - условная функция распределения потребного числа каналов обслуживания относительно гипотезы, согласно которой

- условная функция распределения потребного числа каналов обслуживания относительно гипотезы, согласно которой  - текущему значению числу каналов обслуживания

- текущему значению числу каналов обслуживания

- соответственно функция и плотность распределения реального числа каналов обслуживания при значении

- соответственно функция и плотность распределения реального числа каналов обслуживания при значении  .

.

Принимая во внимание, что распределение случайных величин  и

и  можно описать биноминальным законом и с учетом формулы (2), формулу (1) можно представить в следующем виде:

можно описать биноминальным законом и с учетом формулы (2), формулу (1) можно представить в следующем виде:

где lи - исходное потребное число каналов обслуживания (потенциально возможное количество заявок на обслуживание);

Рn - вероятность безотказной работы одного канала обслуживания в прогнозируемый момент времени;

Pτ - вероятность того, что заявка поступит на обслуживание; - число сочетаний соответственно из ln по i и из kи пo kj (∀i = 0,kj).

- число сочетаний соответственно из ln по i и из kи пo kj (∀i = 0,kj).

Технический результат достигается тем, что устройство для оценки эффективности, содержащее первый и второй блоки вычитания, первый и второй блоки умножения и первый сумматор, дополнительно содержит блок входных регистров, первый и второй счетчики, с первого по третье постоянное запоминающее устройство (ПЗУ), с первого по седьмой коммутаторы, третий блок вычитания, с первого по десятый элементы задержки (ЭЗ), первый и второй регистры, с третьего по шестой блоки умножения, с первого по четвертый блоки возведения в степень, с первого по четвертый элементы ИЛИ, блок сравнения, блок индикации, генератор тактовых импульсов, второй сумматор, элемент И и распределитель импульсов, тактовый вход которого соединен с выходом генератора тактовых импульсов, а с первого по двадцать четвертый выходы подключены соответственно к четырем входам записи блока входных регистров, к первому и второму входам считывания блока входных регистров, к управляющим входам первого и второго коммутаторов, к входу считывания первого ПЗУ, к входам записи первого и второго регистров, к входам считывания первого и второго регистров, к третьему и четвертому входам считывания блока входных регистров, к управляющим входам с третьего по шестой коммутаторов, к входам запуска первого и второго счетчиков, к тактовым входам первого и второго счетчиков, к управляющему входу элемента И, с первого по четвертый информационные входы блока входных регистров являются входом задания исходной информации устройства, с первого по четвертый выходы блока входных регистров соединены с информационными входами с первого по четвертый коммутаторов, первые выходы первого и второго коммутаторов подключены к входам вычитаемого соответственно первого и второго блоков вычитания, а вторые выходы этих коммутаторов соединены с входами основания соответственно третьего и четвертого блоков возведения в степень, первый выход третьего коммутатора подключен к входу уменьшаемого третьего блока вычитания, а также к первым входам блока сравнения и третьего ПЗУ, первый выход четвертого коммутатора соединен с входом уменьшаемого четвертого блока вычитания, а также с первым входом второго ПЗУ, выход первого счетчика подключен к входу вычитаемого третьего блока вычитания, к входу показателя четвертого блока возведения в степень, а также ко вторым входам блока сравнения и третьего ПЗУ, выход второго счетчика соединен с входом вычитаемого четвертого блока вычитания, с входом показателя третьего блока возведения в степень и со вторым входом второго ПЗУ, выход первого ПЗУ подключен к входам уменьшаемого первого и второго блоков вычитания, выходы которых соединены с информационными входами соответственно второго и первого регистров, выходы которых подключены к входам основания соответственно первого и второго блоков возведения в степень, выходы которых соединены с информационными входами соответственно пятого и шестого коммутаторов, а входы показателей - с выходами соответственно первого и второго элементов ИЛИ, первые входы которых подключены к выходам соответственно третьего и четвертого блоков вычитания, а вторые входы - ко вторым выходам соответственно третьего и четвертого коммутаторов, выходы второго и третьего ПЗУ соединены с входами соответственно первого и второго ЭЗ, выходы которых подключены к первым входам соответственно первого и второго блоков умножения, вторые входы которых соединены с выходами соответственно третьего и четвертого блоков возведения в степень, а выходы - с первыми входами соответственно третьего и четвертого блоков умножения, выходы которых подключены соответственно к первому входу первого сумматора и входу третьего ЭЗ, а вторые входы этих блоков умножения - к выходам соответственно четвертого и пятого ЭЗ, входы которых соединены с первыми выходами соответственно шестого и пятого коммутаторов, вторые выходы которых подключены соответственно к первому и второму входам пятого блока умножения, выход которого через шестой ЭЗ соединен с первым входом третьего элемента ИЛИ, второй вход которого через седьмой ЭЗ подключен к первому выходу седьмого коммутатора, а выход - к первому входу второго сумматора, выход которого соединен с информационным входом седьмого коммутатора, а второй вход - с выходом шестого блока умножения, первый вход которого подключен к выходу третьего ЭЗ, а второй вход - к выходу первого сумматора, который этим же выходом соединен через восьмой ЭЗ с первым входом четвертого элемента ИЛИ, выход которого подключен ко второму входу первого сумматора, а второй вход - через девятый элемент задержки к выходу элемента И, информационный вход которого соединен с выходом второго блока возведения в степень, выход блока сравнения через десятый ЭЗ соединен с управляющим входом седьмого коммутатора, второй выход которого подключен к входу блока индикации.

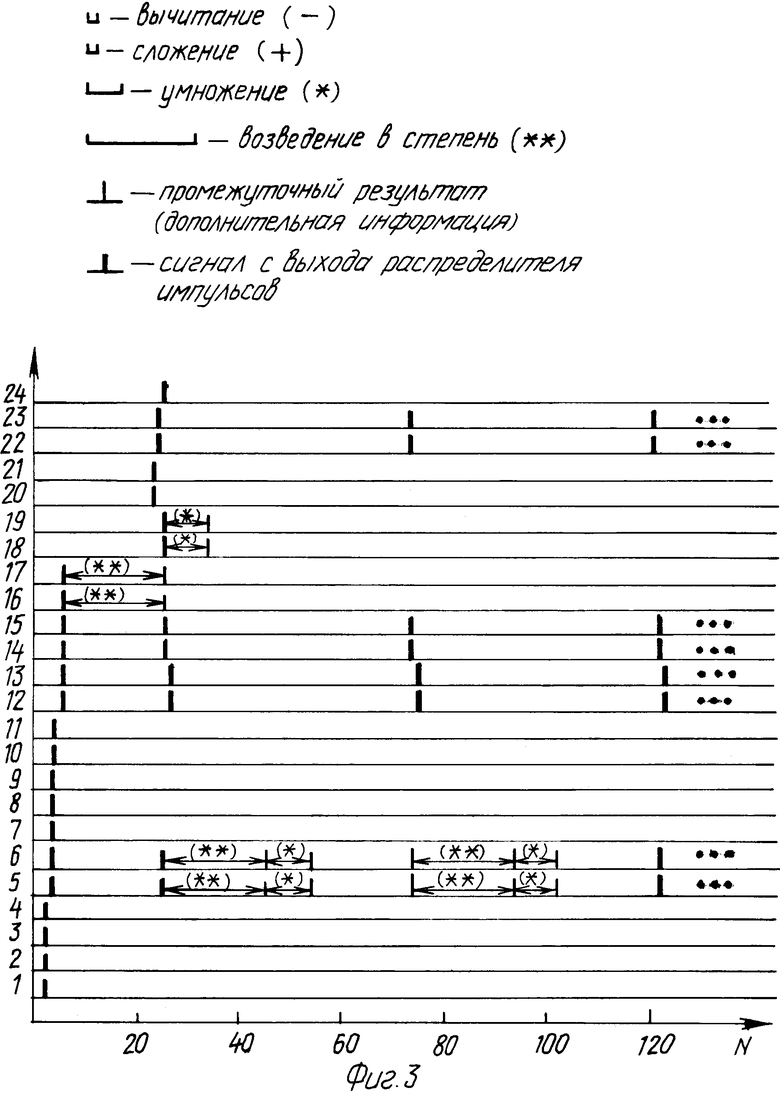

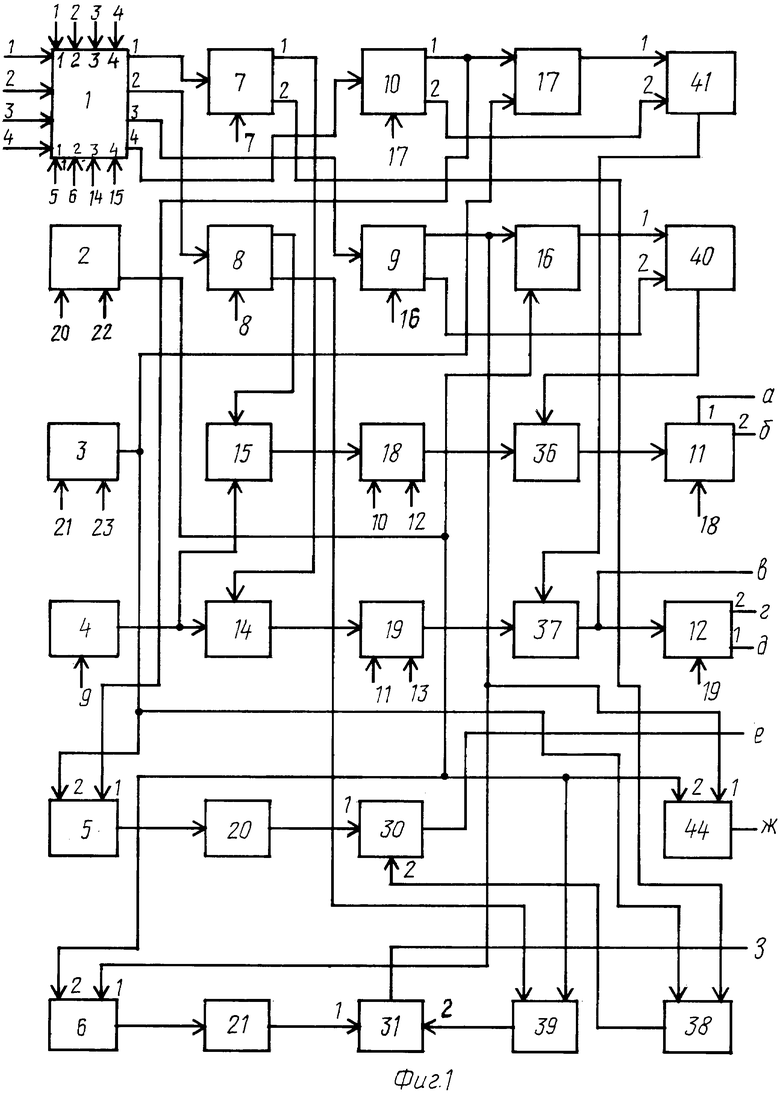

На фиг. 1 и 2 представлена функциональная схема устройства для оценки эффективности (для ликвидации громоздкости связи между распределителем импульсов и управляющими входами соответствующих блоков показаны не полностью, а обозначены путем нумерации входов и выходов); на фиг. 3 изображена циклограмма работы устройства для оценки эффективности (по оси ординат обозначены номера выходов распределителя импульсов, а по оси абсцисс - число текстов, причем длительность различных вычислительных операций в верхней части фиг. 3).

Устройство для оценки эффективности (фиг. 1 и 2) содержит блок 1 входных регистров, первый 2 и второй 3 счетчики, первое 4, второе 5 и третье 6 ПЗУ, первый 7, второй 8, третий 9, четвертый 10, пятый 11, шестой 12 и седьмой 13 коммутаторы, первый 14, второй 15, третий 16 и четвертый 17 блоки вычитания, первый 18 и второй 19 регистры, первый 20, второй 21, третий 22, четвертый 23, пятый 24, шестой 25, седьмой 26, восьмой 27, девятый 28 и десятый 29 ЭЗ, первый 30, второй 31, третий 32, четвертый 33, пятый 34 и шестой 35 блоки умножения, первый 36, второй 37, третий 38 и четвертый 39 блоки возведения в степень, первый 40, второй 41, третий 42 и четвертый 43 элементы ИЛИ, блок 44 сравнения, генератор 45 тактовых импульсов, первый 46 и второй 47 сумматоры, распределитель 48 импульсов, блок 49 индикации и элемент И 50.

Устройство для оценки эффективности работает следующим образом.

С входа задания исходной информации значения Pτ, Рn, kи и l подаются на информационные входы блока 1 входных регистров. При этом сигналы на запись поступают на четыре входа записи блока 1 с первого по четвертый выходов распределителя 48 импульсов, темп работы которого задается генератором 45 тактовых импульсов (фиг. 1 и 2). По сигналам с пятого и шестого выходов распределителя 48 импульсов величины Pτ и Pn с первого и второго выходов блока 1 входных регистров подаются на информационные входы соответственно первого 7 и второго 8 коммутаторов, на управляющие входы которых засылаются сигналы соответственно с седьмого и восьмого выходов распределителя 48 импульсов. Благодаря наличию этих управляющих сигналов величины Pτ и Рn подаются с первых выходов коммутаторов 7 и 8 на входы вычитаемого соответственно первого 14 и второго 15 блоков вычитания. По сигналу с девятого выхода распределителя 48 импульсов с выхода первого ПЗУ 4 поступает "единица" на входы уменьшаемого блоков 14 и 15, с выходов которых сигналы, соответствующие величинам (1-Pτ) и (1-Рn), поступают на информационные входы соответственно второго 19 и первого 18 регистров. При этом управляющие сигналы на блоки 18 и 19 для записи этих величин подаются с десятого и одиннадцатого выходов распределителя 48 импульсов.

По сигналам с двенадцатого и тринадцатого выходов распределителя 48 импульсов на входы считывания первого 18 и второго 19 регистров с их выходов величины (1-Рn) и (1-Pτ) направляются на входы основания соответственно первого 36 и второго 37 блоков возведения в степень. С третьего и четвертого выходов блока 1 входных регистров по сигналам с четырнадцатого и пятнадцатого выходов распределителя 48 импульсов на третий и четвертый входы считывания блока 1 величины kи и lи подаются на информационные входы соответственно третьего 9 и четвертого 10 коммутаторов. Со вторых выходов этих коммутаторов значения kи и lи засылаются на вторые входы соответственно первого 40 и второго 41 элементов или (сигналы на управляющие входы третьего 9 и четвертого 10 коммутаторов подаются соответственно с шестнадцатого и семнадцатого выходов распределителя 48 импульсов), с выходов которых эти величины направляются на входы показателя соответственно первого 35 и второго 37 блоков возведения в степень.

С выходов блоков 36 и 37 значения  и

и  поступают на информационные входы соответственно пятого 11 и шестого 12 коммутаторов, со вторых выходов которых эти значения подаются соответственно на второй и первый входы пятого блока 34 умножения (сигналы на управляющие входы пятого 11 и шестого 12 коммутаторов направляются соответственно с восемнадцатого и девятнадцатого выходов распределителя 48 импульсов). Кроме того, величина

поступают на информационные входы соответственно пятого 11 и шестого 12 коммутаторов, со вторых выходов которых эти значения подаются соответственно на второй и первый входы пятого блока 34 умножения (сигналы на управляющие входы пятого 11 и шестого 12 коммутаторов направляются соответственно с восемнадцатого и девятнадцатого выходов распределителя 48 импульсов). Кроме того, величина  с выхода второго блока 37 возведения в степень засылается через элемент И 50 на вход девятого ЭЗ 28. Сигнал на пропуск этой величины подается на управляющий вход блока 50 с двадцать четвертого выхода распределителя 48 импульсов. С выхода блока 34 величина

с выхода второго блока 37 возведения в степень засылается через элемент И 50 на вход девятого ЭЗ 28. Сигнал на пропуск этой величины подается на управляющий вход блока 50 с двадцать четвертого выхода распределителя 48 импульсов. С выхода блока 34 величина  поступает на вход шестого ЭЗ 25. Это значение соответствует первому слагаемому формулы (3) при kj= i= 0.

поступает на вход шестого ЭЗ 25. Это значение соответствует первому слагаемому формулы (3) при kj= i= 0.

В соответствии с циклограммой работы устройства (фиг. 3) с двадцатого и двадцать первого выходов распределителя 48 импульсов управляющие сигналы подаются на входы запуска первого 2 и второго 3 счетчиков (фиг. 1 и 2). После этого с двадцать второго и двадцать третьего выходов блока 48 направляются сигналы на тактовые входы счетчиков 2 и 3. Таким образом, на выходе первого счетчика 2 формируется величина kj= l, которая поступает на вторые входы третьего ПЗУ 6 и блока 44 сравнения, на вход показателя четвертого блока 39 возведения в степень и на вход вычитаемого третьего блока 16 вычитания. На выходе второго счетчика 3 будет появляться значение i= 1, направляемое на второй вход второго ПЗУ 5, на вход показателя третьего блока 38 возведения в степень и на вход вычитаемого четвертого блока 17 вычитания.

По сигналам с четырнадцатого и пятнадцатого выходов распределителя 48 импульсов на третий и четвертый входы считывания блока 1 входных регистров с третьего и четвертого выходов этого блока значения kи и lи поступают на информационные входы соответственно третьего 9 и четвертого 10 коммутаторов. Причем в данной ситуации управляющие сигналы на эти коммутаторы не подаются, поэтому величины kи и lи будут появляться на их первых выходах. Значения lи направляются на вход уменьшаемого четвертого блока 17 вычитания и на первый вход второго ПЗУ 5. Величина kи засылается на вход уменьшаемого третьего блока 16 вычитания, на первые входы третьего ПЗУ 6 и блока 44 сравнения. Блок 44 настроен следующим образом. При соблюдении неравенства kj<kи на его выходе появится сигнал. А в случае, когда kj= kи, на выходе сигнал будет отсутствовать.

С выходов второго 5 и третьего 6 ПЗУ значения  и

и  подаются на входы соответственно первого 20 и второго 21 ЭЗ. С выходов третьего 16 и четвертого 17 блоков вычитания величины (kи-kj) и (lи-i) поступают на первые входы соответственно первого 40 и второго 41 элементов ИЛИ, с выходов которых эти величины направляются на входы показателя соответственно первого 36 и второго 37 блоков возведения в степень. На входы основания этих блоков с выходов соответственно первого 18 и второго 19 регистров поступают по сигналам на входы считывания этих регистров с двенадцатого и тринадцатого выходов распределителя 48 импульсов значения (1-Рn) и (1-Pτ). С выходов первого 36 и второго 37 блоков возведения в степень величины

подаются на входы соответственно первого 20 и второго 21 ЭЗ. С выходов третьего 16 и четвертого 17 блоков вычитания величины (kи-kj) и (lи-i) поступают на первые входы соответственно первого 40 и второго 41 элементов ИЛИ, с выходов которых эти величины направляются на входы показателя соответственно первого 36 и второго 37 блоков возведения в степень. На входы основания этих блоков с выходов соответственно первого 18 и второго 19 регистров поступают по сигналам на входы считывания этих регистров с двенадцатого и тринадцатого выходов распределителя 48 импульсов значения (1-Рn) и (1-Pτ). С выходов первого 36 и второго 37 блоков возведения в степень величины  и

и  подаются на информационные входы соответственно пятого 11 и шестого 12 коммутаторов, с первых выходов которых эти величины поступают на входы соответственно пятого 24 и четвертого 23 ЭЗ. В данной ситуации управляющие сигналы на эти коммутаторы не подаются.

подаются на информационные входы соответственно пятого 11 и шестого 12 коммутаторов, с первых выходов которых эти величины поступают на входы соответственно пятого 24 и четвертого 23 ЭЗ. В данной ситуации управляющие сигналы на эти коммутаторы не подаются.

С первого и второго выходов блока 1 входных регистров по сигналам на первый и второй входы считывания с пятого и шестого выходов распределителя 48 импульсов значения Pτ и Рn засылаются на информационные входы соответственно первого 7 и второго 8 коммутаторов. В этом случае управляющие сигналы на их управляющие входы не подаются, поэтому величины Pτ и Рn со вторых выходов коммутаторов 7 и 8 подаются на входы основания соответственно третьего 38 и четвертого 39 блоков возведения в степень, с выходов которых значения P направляются на вторые входы соответственно первого 30 и второго 31 блоков умножения. На первые входы этих блоков с выходов соответственно первого 20 и второго 21 ЭЗ поступают величины

направляются на вторые входы соответственно первого 30 и второго 31 блоков умножения. На первые входы этих блоков с выходов соответственно первого 20 и второго 21 ЭЗ поступают величины

.

.

С выходов первого 30 и второго 31 блоков умножения значения  и

и  засылаются на первые входы соответственно третьего 32 и четвертого 33 блоков умножения, на вторые входы которых подаются с выходов соответственно четвертого 23 и пятого 24 ЭЗ величины

засылаются на первые входы соответственно третьего 32 и четвертого 33 блоков умножения, на вторые входы которых подаются с выходов соответственно четвертого 23 и пятого 24 ЭЗ величины  и

и  . С выхода третьего блока 32 умножения значения

. С выхода третьего блока 32 умножения значения  направляется на первый вход первого сумматора 46, а величина

направляется на первый вход первого сумматора 46, а величина  c выхода четвертого блока 33 умножения поступает на вход третьего ЭЗ 22.

c выхода четвертого блока 33 умножения поступает на вход третьего ЭЗ 22.

На второй вход первого сумматора 46 с выхода девятого ЭЗ 28 через четвертый элемент или 43 засылается значение  , соответствующее случаю i= 0. С выхода этого сумматора величина

, соответствующее случаю i= 0. С выхода этого сумматора величина  при i= 1 подается на вход восьмого ЭЗ 27 и на второй вход шестого блока 35 умножения, на второй вход которого направляется с выхода третьего ЭЗ 22 значение

при i= 1 подается на вход восьмого ЭЗ 27 и на второй вход шестого блока 35 умножения, на второй вход которого направляется с выхода третьего ЭЗ 22 значение  . С выхода блока 35 величина

. С выхода блока 35 величина  при i= 0 и 1, kj= l поступает на второй вход второго сумматора 47, на первый вход которого с выхода шестого ЭЗ 25 через третий элемент или 42 засылается значение

при i= 0 и 1, kj= l поступает на второй вход второго сумматора 47, на первый вход которого с выхода шестого ЭЗ 25 через третий элемент или 42 засылается значение  при i= 0, kj= 0.

при i= 0, kj= 0.

С выхода второго сумматора 47 величина W, определяемая по формуле (1) для случая i= 0 и 1, kj= 0 и 1, подается на информационный вход седьмого коммутатора 13. Поскольку в данной ситуации kj < kи (как правило kи > 1), то на выходе блока 44 сравнения будет сигнал, который через десятый ЭЗ 29 направляется на управляющий вход седьмого коммутатора 13. Следовательно, с первого выхода этого коммутатора промежуточное значение W засылается на вход седьмого ЭЗ 26 для последующего суммирования при kj= 2.

В дальнейшем работа устройства происходит по описанному выше порядку. Когда kj= kи, на выходе блока 44 сравнения сигнал будет отсутствовать и уже конечное значение W со второго выхода седьмого коммутатора 13 поступает на блок 49 индикации для наглядного отображения.

Таким образом, описанное устройство позволяет оценить эффективность различных систем за счет определения вероятности выполнения задач этими системами благодаря вычислению вероятности того, что одна случайная величина больше или меньше другой случайной величины.

Промышленная применимость изобретения обосновывается тем, что оно может быть использовано в различных областях (отраслях) в процессе оценки эффективности различных систем, например систем массового обслуживания.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ОЦЕНКИ ЭФФЕКТИВНОСТИ | 2006 |

|

RU2306598C1 |

| УСТРОЙСТВО ДЛЯ ВЫБОРА РАЦИОНАЛЬНОГО ВАРИАНТА | 2001 |

|

RU2202822C1 |

| УСТРОЙСТВО ДЛЯ ОЦЕНКИ ЭФФЕКТИВНОСТИ АЛГОРИТМИЧЕСКОГО ОБЕСПЕЧЕНИЯ | 2002 |

|

RU2207621C1 |

| АДАПТИВНЫЙ ВРЕМЕННОЙ ДИСКРЕТИЗАТОР | 2015 |

|

RU2583707C1 |

| УСТРОЙСТВО ДЛЯ ВЗАИМОДЕЙСТВИЯ С ЭКСПЕРТАМИ ПРИ ОПРЕДЕЛЕНИИ КАРДИНАЛЬНОЙ СОГЛАСОВАННОЙ ОЦЕНКИ | 2004 |

|

RU2256214C1 |

| Устройство формирования оптимальных управляющих воздействий для обеспечения устойчивой работы сложных технических систем | 2017 |

|

RU2674281C1 |

| УСТРОЙСТВО ДЛЯ ОЦЕНКИ ФУНКЦИИ РАСПРЕДЕЛЕНИЯ СЛУЧАЙНЫХ ВЕЛИЧИН И ЕЕ ТОЛЕРАНТНЫХ ГРАНИЦ ПО МАЛЫМ ВЫБОРКАМ | 2014 |

|

RU2553120C1 |

| ЦИФРОВОЙ РАДИОПЕЛЕНГАТОР | 1999 |

|

RU2149419C1 |

| УСТРОЙСТВО ДЛЯ ВЫБОРА ВАРИАНТА ИСПЫТАНИЙ ТЕХНИЧЕСКИХ УСТРОЙСТВ | 2010 |

|

RU2417392C1 |

| Устройство для контроля параметров | 1990 |

|

SU1728869A1 |

Изобретение относится к вычислительной технике, а именно к оборудованию для обработки данных, и может быть использовано для оценки эффективности различных систем, например систем массового обслуживания. Техническим результатом является возможность оценки эффективности различных систем за счет определения вероятности выполнения задач этими системами благодаря вычислению вероятности того, что одна случайная величина больше или равна другой случайной величине. Для этого устройство содержит ПЗУ, коммутаторы, блоки умножения, сумматоры, элементы задержки, регистры, элементы ИЛИ, блок сравнения, блок индикации, генератор тактовых импульсов, элементов И и распределитель импульсов. 3 ил.

Устройство для оценки эффективности, содержащее первый и второй блоки вычитания, первый и второй блоки умножения и первый сумматор, отличающееся тем, что оно дополнительно содержит блок входных регистров, первый и второй счетчики, с первого по третье постоянное запоминающее устройство (ПЗУ), с первого по седьмой коммутаторы, третий блок вычитания, с первого по десятый элементы задержки (ЭЗ), первый и второй регистры, с третьего по шестой блоки умножения, с первого по четвертый блоки возведения в степень, с первого по четвертый элементы ИЛИ, блок сравнения, блок индикации, генератор тактовых импульсов, второй сумматор, элемент И и распределитель импульсов, тактовый вход которого соединен с выходом генератора тактовых импульсов, а с первого по двадцать четвертый выходы подключены соответственно к четырем входам записи блока входных регистров, к первому и второму входам считывания блока входных регистров, к управляющим входам первого и второго коммутаторов, к входу считывания первого ПЗУ, к входам записи первого и второго регистров, к входам считывания первого и второго регистров, к третьему и четвертому входам считывания блока входных регистров, к управляющим входам с третьего по шестой коммутаторов, к входам запуска первого и второго счетчиков, к тактовым входам первого и второго счетчиков, к управляющему входу элемента И, с первого по четвертый информационные входы блока входных регистров являются входом задания исходной информации устройства, с первого по четвертый выходы блока входных регистров соединены с информационными входами с первого по четвертый коммутаторов, первые выходы первого и второго коммутаторов подключены к входам вычитаемого соответственно первого и второго блоков вычитания, а вторые выходы этих коммутаторов соединены с входами основания соответственно третьего и четвертого блоков возведения в степень, первый выход третьего коммутатора подключен к входу уменьшаемого третьего блока вычитания, а также к первым входам блока сравнения и третьего ПЗУ, первый выход четвертого коммутатора соединен с входом уменьшаемого четвертого блока вычитания, а также с первым входом второго ПЗУ, выход первого счетчика подключен к входу вычитаемого третьего блока вычитания, к входу показателя четвертого блока возведения в степень, а также ко вторым входам блока сравнения и третьего ПЗУ, выход второго счетчика соединен с входом вычитаемого четвертого блока вычитания, с входом показателя третьего блока возведения в степень и со вторым входом второго ПЗУ, выход первого ПЗУ подключен к входам уменьшаемого первого и второго блоков вычитания, выходы которых соединены с информационными входами соответственно второго и первого регистров, выходы которых подключены к входам основания соответственно первого и второго блоков возведения в степень, выходы которых соединены с информационными входами соответственно пятого и шестого коммутаторов, а входы показателей - с выходами соответственно первого и второго элементов ИЛИ, первые входы которых подключены к выходам соответственно третьего и четвертого блоков вычитания, а вторые входы - ко вторым выходам соответственно третьего и четвертого коммутаторов, выходы второго и третьего ПЗУ соединены с входами соответственно первого и второго ЭЗ, выходы которых подключены к первым входам соответственно первого и второго блоков умножения, вторые входы которых соединены с выходами соответственно третьего и четвертого блоков возведения в степень, а выходы - с первыми входами соответственно третьего и четвертого блоков умножения, выходы которых подключены соответственно к первому входу первого сумматора и входу третьего ЭЗ, а вторые входы этих блоков умножения - к выходам соответственно четвертого и пятого ЭЗ, входы которых соединены с первыми выходами соответственно шестого и пятого коммутаторов, вторые выходы которых подключены соответственно к первому и второму входам пятого блока умножения, выход которого через шестой ЭЗ соединен с первым входом третьего элемента ИЛИ, второй вход которого через седьмой ЭЗ подключен к первому выходу седьмого коммутатора, а выход - к первому входу второго сумматора, выход которого соединен с информационным входом седьмого коммутатора, а второй вход - с выходом шестого блока умножения, первый вход которого подключен к выходу третьего ЭЗ, а второй вход - к выходу первого сумматора, который этим же выходом соединен через восьмой ЭЗ с первым входом четвертого элемента ИЛИ, выход которого подключен ко второму входу первого сумматора, а второй вход - через девятый элемент задержки к выходу элемента И, информационный вход которого соединен с выходом второго блока возведения в степень, выход блока сравнения через десятый ЭЗ соединен с управляющим входом седьмого коммутатора, второй выход которого подключен к входу блока индикации.

| УСТРОЙСТВО ДЛЯ РЕШЕНИЯ ЗАДАЧИ АНАЛИЗА РАБОТЫ СИСТЕМ МАССОВОГО ОБСЛУЖИВАНИЯ | 1991 |

|

RU2041491C1 |

| УСТРОЙСТВО ДЛЯ РЕШЕНИЯ ЗАДАЧИ АНАЛИЗА РАБОТЫ СИСТЕМ МАССОВОГО ОБСЛУЖИВАНИЯ | 1991 |

|

RU2041492C1 |

| УСТРОЙСТВО ДЛЯ РЕШЕНИЯ ЗАДАЧИ АНАЛИЗА РАБОТЫ СИСТЕМ МАССОВОГО ОБСЛУЖИВАНИЯ | 1990 |

|

RU2043655C1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР | 1991 |

|

RU2015554C1 |

| УСТРОЙСТВО ДЛЯ ПАРАМЕТРИЧЕСКОЙ ОЦЕНКИ ЗАКОНА РАСПРЕДЕЛЕНИЯ ПОТОКОВ СООБЩЕНИЙ | 1994 |

|

RU2094844C1 |

| УСТРОЙСТВО ДЛЯ ПАРАМЕТРИЧЕСКОЙ ОЦЕНКИ ЗАКОНА РАСПРЕДЕЛЕНИЯ ПОТОКОВ СООБЩЕНИЙ | 1999 |

|

RU2165100C2 |

| US 5546564 А, 13.08.1996. | |||

Авторы

Даты

2002-01-10—Публикация

2001-04-16—Подача