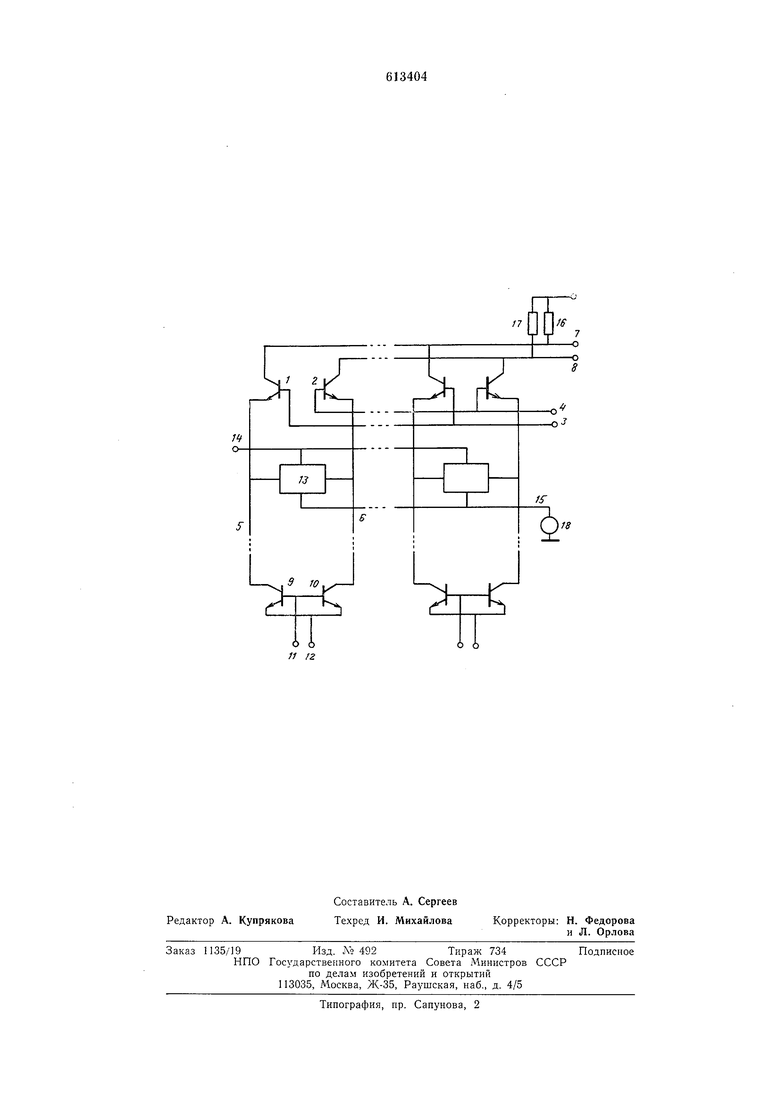

ти, которые соединяются с соответствующими разрядными шинами 5 и 6 и шинами 14, 15 строки. Резисторы 16, 17, одни выводы которых соединены с шинами 7 и 8, а другие подключены к общей щине источника питания, обеспечивают режим работы усилителей считывания. Источник 18 тока, подключенный к щине 15, обеспечивает режим питания строки элементов памяти.

Устройство работает следующим образом.

В режлме хранения информации ток в щину 12, а соответственно и в щины 5 и 6 поступает, и все транзисторы 1, 2 выключены. При этом разрядные усилители не потребляют мощность. При выборке информации потенциал шины 14 повышается, а в шину 12 выбираемого разряда подается импульс тока. Транзисторы 9 и 10 выполняются идентичными по структуре и топологии, поэтому практически равные токи поступают в разрядные шины 5 и 6. Поскольку в шины 12 других разрядов ток не поступает, соответствующие разрядные усилители не потребляют мощность.

При считывании информации уровни напряжения щин 3, 4 на базах транзисторов 1 и 2 равны и должны быть выше потенциала базы включенного транзистора в невыбранном элементе 13 памяти. Уровень высокого напряжения на шипе 14 при выборке таков, что потенциал базы включенного транзистора выбранного элемента 13 выше, а потенциал базы выключенного транзистора ниже потенциала баз транзисторов 1, 2.

Будем считать, что хранению логического «О соответствует такое состояние элемента, при котором транзистор элемента 13, связанный с шиной 5, включен, а транзистор, связанный с шиной 6, выключен. При хранении логической «1 наоборот: первый транзистор выключен, а второй включен. Пусть, например, элемент памяти хранит «О. В этом случае при считывании потенциал базы включенного транзистора элемента 13 памяти становится выше потенциала базы транзистора 1, и разрядный ток, поступающий в шину 5, переключается в транзистор элемента 13 памяти. Поскольку через транзистор 1 ток не идет, «а шине 7 - высокий потенциал. С другой стороны, потенциал базы выключенного транзистора элемента 13 ниже потенциала базы транзистора 2, и разрядный ток шины 6 переключается в транзистор 2. В результате на шине 8 формируется нижний уровень напряжения. Разность потенциалов шин 7 и 8 представляет сигнал считанной информации. Аналогично происходит считывание «1. При этом разность .потенциалов шин 7 и 8 имеет противополол ный знак.

При записи информации выборка элемента памяти производится так же как и при считывании, а запись осуществляется по щинам 3 и 4 путем понижения потенциала базы одного из транзисторов 1, 2 отиосительно его значения в режиме хранения и считывания. 5 Предположим, что элемент памяти хранит «О. В этом случае для записи логической «1 потенциал базы транзистора 2 понижается и становится ниже потенциала базы транзистора элемента 13, связанного с шиной 6. При

0 этом разрядный ток шины 6 переключается в транзистор элемента, связанный с щиной 6, который включается. Перекос напряжений на базах транзисторов 1, 2 приводит к перебросу триггера элемента памяти. После окончания выборки элемент памяти оказывается в состоянии хранения «1. Если в исходном состоянии элемент памяти хранит «1, то его состояние не меняется.

Предлагаемое устройство обладает следующими преимуществами в сравнении с прототипом. Не нужны диоды и резисторные источники постоянных токов разрядных щин и диодов, что упрощает устройство и исключает потребление мощности в режиме хранения.

5 Соединение эмиттеров двух транзисторов, обеспечивающих выборку разрядов соответствующими адресными шинами, уменьшает узловые паразитные емкости, что повышает быстродействие устройства. Транзисторы, обеспечивающие выборку разряда, одновременно служат оконечным каскадом дещифратора, что упрощает схему дешифратора, повышает его быстродействие и уменьшает потребляемую им мощность.

Формула изобретения

Запоминающее устройство, содержашее „ матрицу элементов памяти и разрядные усилители считывания и записи, выполненные на четырех транзисторах, эмиттеры первых двух транзисторов соединены с разрядными шинами, базы - с управляющими шипами, а коллекторы - с шинами считывания, коллекторы вторых двух транзисторов подключены к разрядным шинам, а базы объединены и подключены к одной из адресных щин, отличающееся тем, что, с целью упрощения устройства, уменьшения потребляемой им мощности и повышения быстродействия, в нем эмиттеры вторых двух транзисторов объединены и подключены к другим адресны.м шинам.

Источники информации, принятые во внимание при экспертизе

1.Патент США № 3725878, кл. 340-173, опубл. 1973.

2.Патент Великобритании № 1331815, кл. ПОЗК, опубл. 1973.

/ г

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1976 |

|

SU613405A1 |

| Запоминающее устройство | 1985 |

|

SU1269208A1 |

| Способ записи и считывания информации в запоминающих устройствах с инжекционным питанием и устройство для его осуществления | 1975 |

|

SU646371A1 |

| Матричное запоминающее устройство | 1977 |

|

SU744724A1 |

| Усилитель записи и считывания для запоминающего устройства с произвольной выборкой | 1983 |

|

SU1091223A1 |

| Ячейка памяти | 1973 |

|

SU444244A1 |

| Ячейка памяти | 1973 |

|

SU444245A1 |

| Ячейка памяти | 1974 |

|

SU546935A1 |

| Ячейка памяти | 1974 |

|

SU491998A1 |

| Запоминающее устройство | 1976 |

|

SU597006A1 |

,9 ю

--ч

л-т-Ц

Авторы

Даты

1978-06-30—Публикация

1975-10-22—Подача