Цель изобретения - улучшение гармонического состава выходного напряжения преобразователя.

Поставленная цель достигается тем, что в способе интегрального управления т-фаз- ным вентильным преобразователем, заключающемся в том, что интегрируют разность между напряжением, формируют опорный сигнал, сравнивают результат интегрирования с опорным сигналом, запоминают интервал времени от момента естественной коммутации тиристоров до момента равенства результата интегрирования опорному сигналу и формируют угол отпирания тиристоров, равный заполненному интервалу времени через интервалов повторяемости преобразователя.

Таким образом, за счет асимметричного управления целенаправленно создается такая асимметрия углов отпирания, при которой неканоническая гармоника выходного напряжения не увеличивается по сравнению со случаем симметричного управления, а уменьшается.

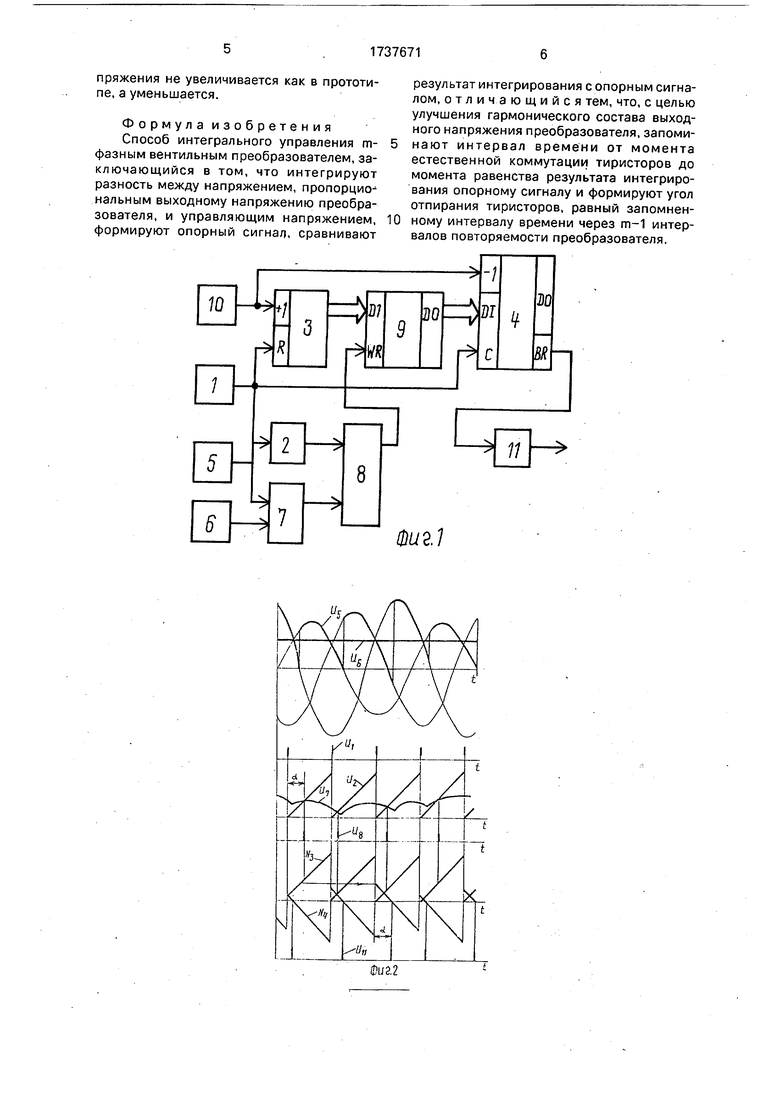

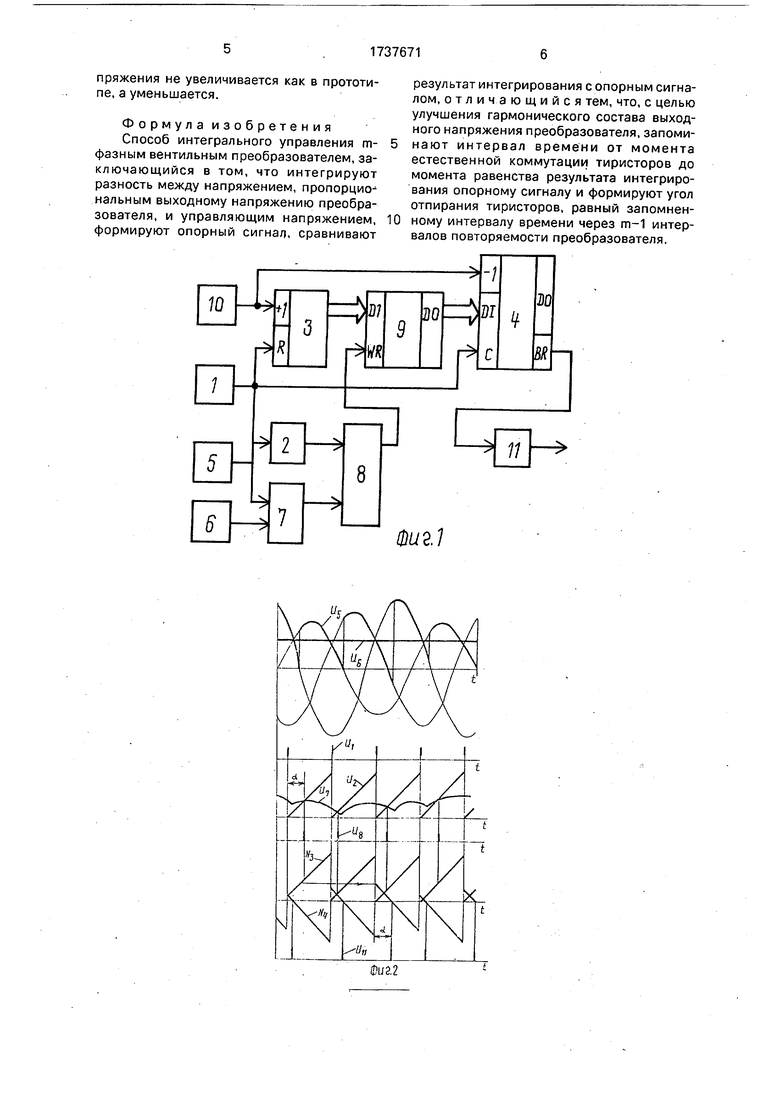

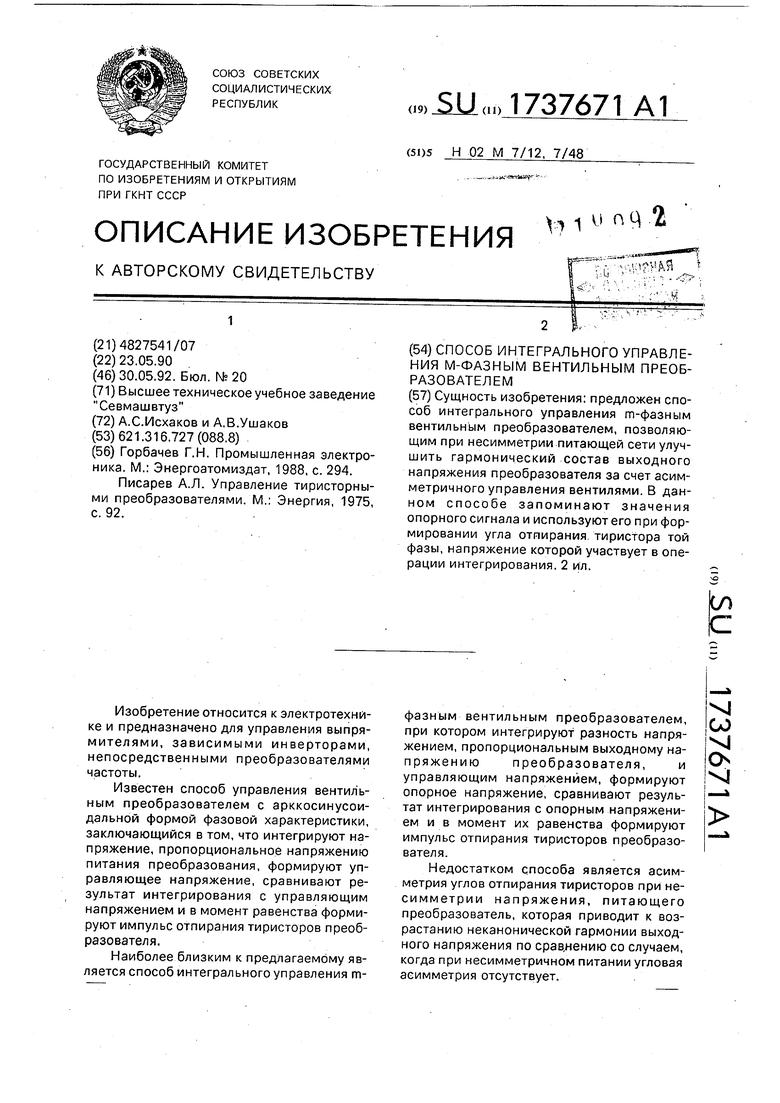

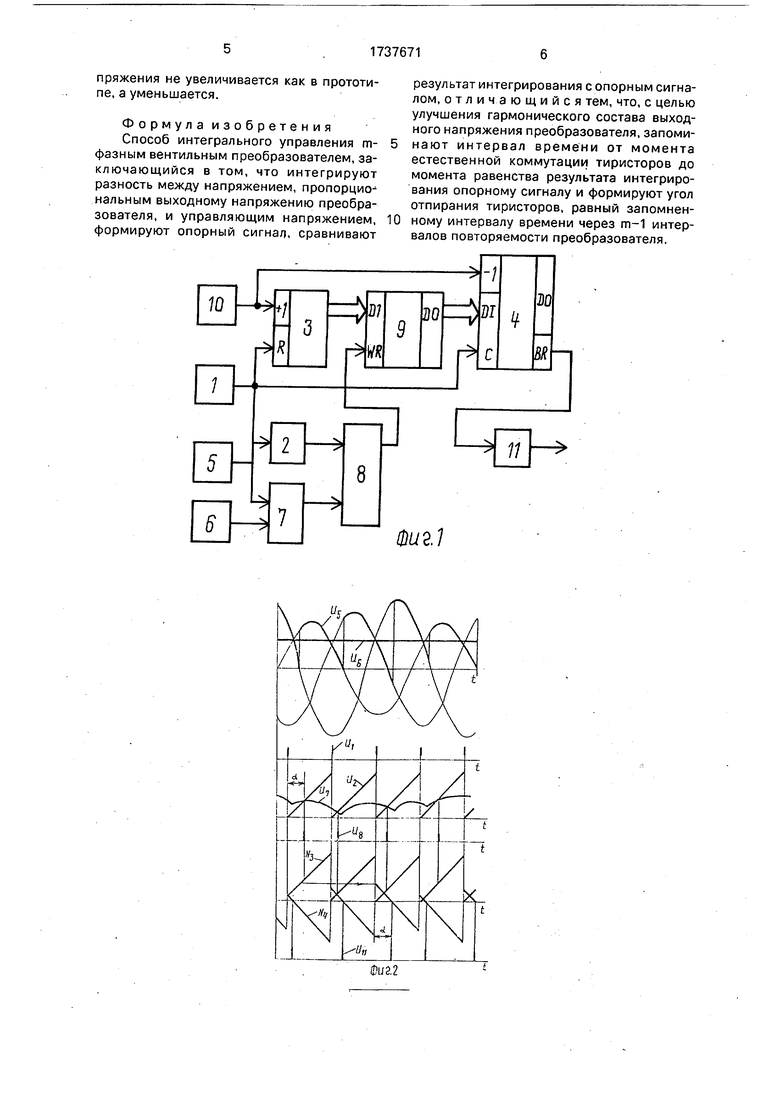

На фиг. 1 изображена структурная схема устройства; на фиг. 2 - временные диаграммы, которые поясняют работу устройства на примере управления выпрямителя с числом фаз m 3.

Устройство состоит из следующих элементов. Схема 1 синхронизации присоединена к генератору 2 опорного напряжения, обнуляющему входу суммирующего счетчика 3, и входу управления предварительной записью информации в вычитающий счетчик 4. Датчик выходного напряжения преобразователя 5 и формирователь 6 управляющего напряжения связаны с входом вычитающего интегратора 7, выход которого подключен к второму входу компаратора-формирователя 8 импульсов, соединенного первым входом со схемой 2, а выходом - с входом управления записью запоминающего устройства 9. Генератор 10 опорной частоты присоединен к тактовым входам счетчиков 3 и 4. Выход счетчика 3 через схему 9 подключен к входу предварительной записи информации счетчика 4, выход займа переноса которого связан с формирователем импульсов отпирания тиристоров преобразователя 11.

На фиг. 2 приведены временные диаграммы напряжения на выходе датчика выходного напряжения преобразователя (диаграмма Us), управляющего напряжения на выходе схемы 6 (диаграмма Ue), опорного напряжения на выходе схемы 2 (диаграмма U2), напряжения на выходе схемы 1 синхронизации (диаграмма 1Н), напряжения на выходе вычитающего интегратора (диаграмма U), напряжения на выходе компаратора- формирователя 8 импульсов (диаграмма Ue), кода на выходе суммирующего счетчика 3

(диаграмма N3), кода на выходе вычитающего счетчика 4 (диаграмма N4) и напряжения на выходе формирователя 11 импульсов (диаграмма Un).

Принцип действия устройства заключается в следующем.

В моменты естественной коммутации тиристоров схема 1 формирует синхронизирующие импульсы Ui, устанавливающие нулевое значение напряжение 1)2 на выходе

генератора 2 опорного напряжения и нулевой код Na на выходе счетчика 3. Разность напряжения, пропорционального выходному напряжению преобразователя, вырабатываемого схемой 5, и управляющего

напряжения, формируемого схемой 6, интегрируется интегратором 7, На выходе счетчика 3 формируется линейно увеличивающийся код со скоростью нарастания, определяемой частотой генератора 10.

В момент равенства напряжения U на

выходе интегратора опорному, на выходе схемы 8 формируется импульс Us, по которому текущее значение кода на выходе счетчика 3, пропорциональное углу отпирания

а тиристоров преобразователя, записывается в запоминающее устройство 9. Используется запоминающее устройство стекового типа, в котором информация хранится в форме очереди двоичных кодов. Поэтому в

момент записи кода в запоминающее устройство, на его выходе появляется код, запомненный ранее. Этот код синхронизирующим импульсом Ui заносится в счетчик 4.

Под действием импульсов генератора 10, поступающих на вычитающий тактовый вход счетчика 4, его содержимое N4 линейно уменьшается со скоростью убывания, равной скорости нарастания кода на выходе

счетчика 3. После обнуления содержимого счетчика 4, на его выходе займа переноса формируется импульс, который усиливается схемой 11 и отпирает тиристоры преобразователя. Выбор информационной емкости запоминающего устройства, равной т-1 кодов, обеспечивает формирование угла отпирания «тиристора той базы, напряжение которой участвует в операции интегрирования.

Таким образом, устройство, реализующее предлагаемый способ, обеспечивает такую асимметрию углов отпирания тиристоров преобразователя, при которой неканоническая гармоника выходного напряжения не увеличивается как в прототипе, а уменьшается.

Формула изобретения Способ интегрального управления т- фазным вентильным преобразователем, заключающийся в том, что интегрируют разность между напряжением, пропорциональным выходному напряжению преобразователя, и управляющим напряжением, формируют опорный сигнал, сравнивают

0

результат интегрирования с опорным сигналом, отличающийся тем, что, с целью улучшения гармонического состава выходного напряжения преобразователя, запоминают интервал времени от момента естественной коммутации тиристоров до момента равенства результата интегрирования опорному сигналу и формируют угол отпирания тиристоров, равный запомненному интервалу времени через т-1 интервалов повторяемости преобразователя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ управления вентильным преобразователем | 1990 |

|

SU1737672A1 |

| Устройство для управления вентильным преобразователем | 1990 |

|

SU1705988A1 |

| Автоматический регулятор компенсирующего устройства | 1990 |

|

SU1704145A1 |

| ФАЗОСДВИГАЮЩЕЕ УСТРОЙСТВО | 2005 |

|

RU2288532C1 |

| Устройство для измерения температуры | 1987 |

|

SU1490504A1 |

| Устройство для измерения мощности | 1990 |

|

SU1751685A1 |

| Способ регулирования тока нагрузки вентильного преобразователя | 1985 |

|

SU1304148A1 |

| Цифровой измеритель составляющих комплексных сопротивлений | 1987 |

|

SU1456907A1 |

| Устройство управления ферритовым фазовращателем | 1986 |

|

SU1448395A1 |

| Цифровой измеритель температуры | 1985 |

|

SU1303849A1 |

Фиг.2

Авторы

Даты

1992-05-30—Публикация

1990-05-23—Подача