7

Ё

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство поиска шумоподобного сигнала | 1988 |

|

SU1540020A1 |

| Цифровой частотомер | 1990 |

|

SU1765779A1 |

| Устройство для регистрации телевизионного изображения | 1989 |

|

SU1720168A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ВЕНТИЛЬНЫМ ПРЕОБРАЗОВАТЕЛЕМ | 1991 |

|

RU2064730C1 |

| Цифровой измеритель задержки | 1981 |

|

SU951228A1 |

| Рекуррентный вычислитель оценки математического ожидания | 1978 |

|

SU746548A1 |

| УСТРОЙСТВО ДЛЯ ЗАДЕРЖКИ СИГНАЛОВ | 1992 |

|

RU2024186C1 |

| Цифровой измеритель параметров комплексного сопротивления | 1989 |

|

SU1732292A1 |

| Устройство для вычисления уровня жидких сред | 1984 |

|

SU1251101A1 |

| Устройство для формирования частотно-манипулированного сигнала в многоканальных системах связи | 1986 |

|

SU1354434A1 |

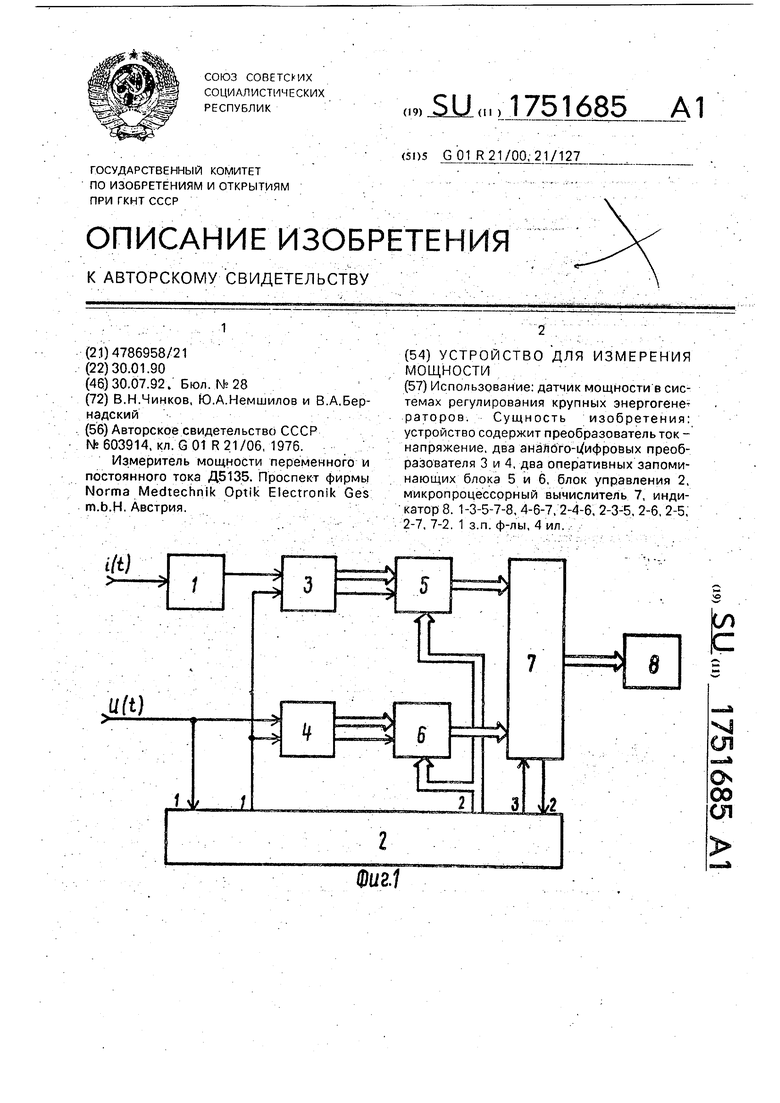

Использование: датчик мощности в системах регулирования крупных энергогенераторов. Сущность изобретения: устройство содержит преобразователь ток - напряжение, два аналого-цифровых преобразователя 3 и 4, два оперативных запоминающих блока 5 и 6, блок управления 2, микропроцессорный вычислитель 7, индикатор 8. 1-3-5-7-8, 4-6-7, 2-4-6, 2-3-5, 2-6, 2-5, 2-7, 7-2. 1 з.п. ф-лы, 4 ил.

Ж

М

w2

ON 00

сл

Фиг.1

Изобретение относится к цифровой измерительной технике и электроприводу и может быть использовано в качестве измерительного прибора и датчика мощности в системах регулирования крупных генераторов.

.Известен цифровой ваттметр, содержащий два входных устройства, два аналого- цифровых преобразователя (или преобразователя аналог - код), блок управления, умножитель частоты, цифровой распределитель точек дискретизации, множительное устройство, два электронных ключа (или импульсно-потенциальных вентиля), триггер и два реверсивных счетчика. Недостатками данного ваттметра являются большое время измерения в низкочастотном диапазоне, ограниченные функциональные возможности, сложность процесса измерения и низкая надежность. Наиболее близким к предлагаемому является измеритель мощности переменного и постоянного тока D5135, содержащий два аналого-цифровых преобразователя, два компаратора, преобразователь ток - напряжение, блок управления, блок индикации, микропроцессорный вычислитель и оперативный запоминающий блок.

Недостатками известного измерителя являются большое время измерения в низкочастотном диапазоне и узкий класс решаемых Задач, так как он не позволяет измерять полную мощность, коэффициент мощности cosy) и величину sin р.

Цель изобретения - повышение быстродействия измерения в низкочастотном диапазоне и расширение функциональных возможностей за счет измерения полной мощности, коэффициента мощности cos p и величины sin p.

Поставленная цель достигается тем, что в устройство для измерения мощности, содержащее первый и второй аналого-цифровые пребразователи, преобразователь ток- напряжение, блок управления, блок индикации, микропроцессорный вычислитель, оперативный запоминающий блок, при этом сигнальный вход первого агналого-цифро- вого преобразователя соединен через преобразователь ток - напряжение С первым входом устройства, дополнительно введен второй оперативный запоминающий блок, причем информационные выходы первого и второго аналого-цифровых преобразователей соединены соответственно с информационными входами первого и второго оперативных запоминающих блоков, а выходы Конец преобразования аналого-цифровых преобразователей подключены к

входам стробирования записи соответствующих оперативных запоминающих блоков, адресные входы которых объединены в общую шину, подключенную к второму выходу

5 блока управления, а выходы первого и второго оперативных запоминающих блоков соединены с первым и вторым информационными входами микропроцессорного вычислителя, который своим управляющим

0 входом подключен к третьему выходу блока управления, управляющим выходом соединен с вторым входом блока управления, а информационным выходом подключен к входу блока индикации, причем сигнальный

5 вход второго аналого-цифрового преобразователя объединен с первым входом блока управления и подключен к второму входу устройства, а входы запуска аналого-цифровых преобразователей соединены с первым

0 выходом блока управления.

Поставленная цель достигается также тем, что блок управления содержит нуль-орган, генератор образцовой частоты, первый и второй делители частоты, первый и второй

5 вычитающие счетчики, регистр, счетчик импульсов, первый, второй, третий, четвертый и пятый триггеры, первый, второй, третий и четвертый элементы И, первый, второй, третий и четвертый элементы ИЛИ, первый.

0 второй и третий элементы задержки, формирователь импульсов, кнопку Пуск и переключатель, имеющий три переключающих контакта, при этом первый вход блока управления подключен к входу нуль-органа,

5 выход которого соединен с первыми входами первого и второго элементов И, подключенных своими вторыми входами к прямым выходам соответственно первого и второго триггеров, вход установки первого триггера

0 соединен через первый элемент задержки и формирователь импульса с кнопкой Пуск, а вход сброса объединен с входом второго элемента задержки и первым входом четвертого элемента ИЛИ и подключен кинвер5 сному выходу третьего триггера, счетный вход которого соединен с выходом первого элемента И, а прямой выход - с первым входом третьего элемента И, второй вход которого подключен к выходу генератора

0 образцовой частоты и первому входу четвертого элемента И, соединенного своим вторым входом с прямым выходом четвертого триггера, выход третьего элемента И соединен через первый делитель частоты со

5 счетным входом счетчика импульсов, а выход второго элемента И - с объединенными счетным входом второго делителя частоты и первым неподвижным контактом переключателя, второй неподвижный контакт которрго подключен к выходу второго делителя

частоты, а первый подвижный контакт соединен с входом установки четвертого триггера, подключенного своим входом сброса к выходу первого элемента ИЛИ, первый вход которого соединен с третьим неподвижным контактом переключателя и первым входом четвертого элемента ИЛИ, выход которого соединен с входом записи регистра и входом третьего элемента задержки, подключенного своим выходом к первому входу третьего элемента ИЛИ, второй вход которого соединен с пятым неподвижным контактом переключателя, информационный вход регистра соединен с кодовым выходом счетчика импульсов, а выход регистра по- разрядно подключен к кодовому входу первого вычитающего счетчика, соединенного своим счетным входом с выходом четвертого элемента И, входом записи - с выходом третьего элемента ИЛИ и выходом займа - с объединенными первым входом блока управления, вторым и третьим подвижными контактами переключателя и первым входом второго элемента ИЛИ, подключенного своим вторым входом к второму входу блока управления, а своим выходом - к счетному входу второго вычитающего счетчика, информационный выход которого соединен с вторым выходом блока управления, а его счетный вход подключен к входу сброса вто- рого триггера, соединенного своим входом установки с выходом второго элемента задержки, и входу установки пятого триггера, прямой выход которого подключен к второму входу первого элемента ИЛИ и третьему выходу блока управления, прямой выход второго триггера соединены с вторым входом второго элемента И.

Предлагаемое устройство для измерения мощности отличается введением второ- го оперативного запоминающего блока и функциональных связей между введенными и известными блоками устройства.

Сущность изобретения состоит в том, что оно основано на корреляционной обра- ботке отсчетов мгновенных значений напряжения и тока, которая проводится в два этапа: сначала накопления отсчетов, а затем их обработка в универсальном микропроцессорном вычислителе для определения измеряемых величин.

Наличие введенного блока с функциональными связями между известными узлами прототипа обеспечивает уменьшение времени измерения в низкочастотном диа- гтазоне и расширение функциональных возможностей за счет измерения полной мощности, коэффициента мощности cosy и величины sin p , а также характеристик напряжения и тока. Блоки управления также широко используются в цифровых измерительных приборах и устройствах, однако построение блока управления в предлагаемом устройстве определяется алгоритмами получения отсчетов тока и напряжения и их обработки, а также принципом построения устройств, т.е. он специфичен для данного устройства.

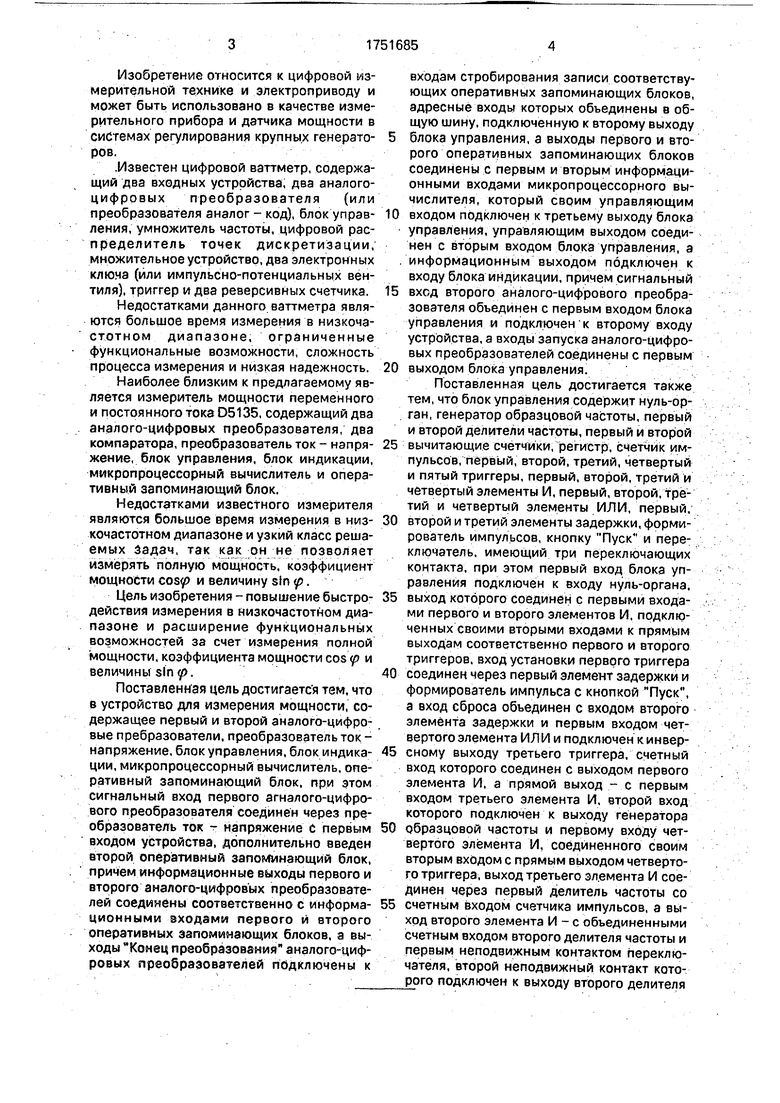

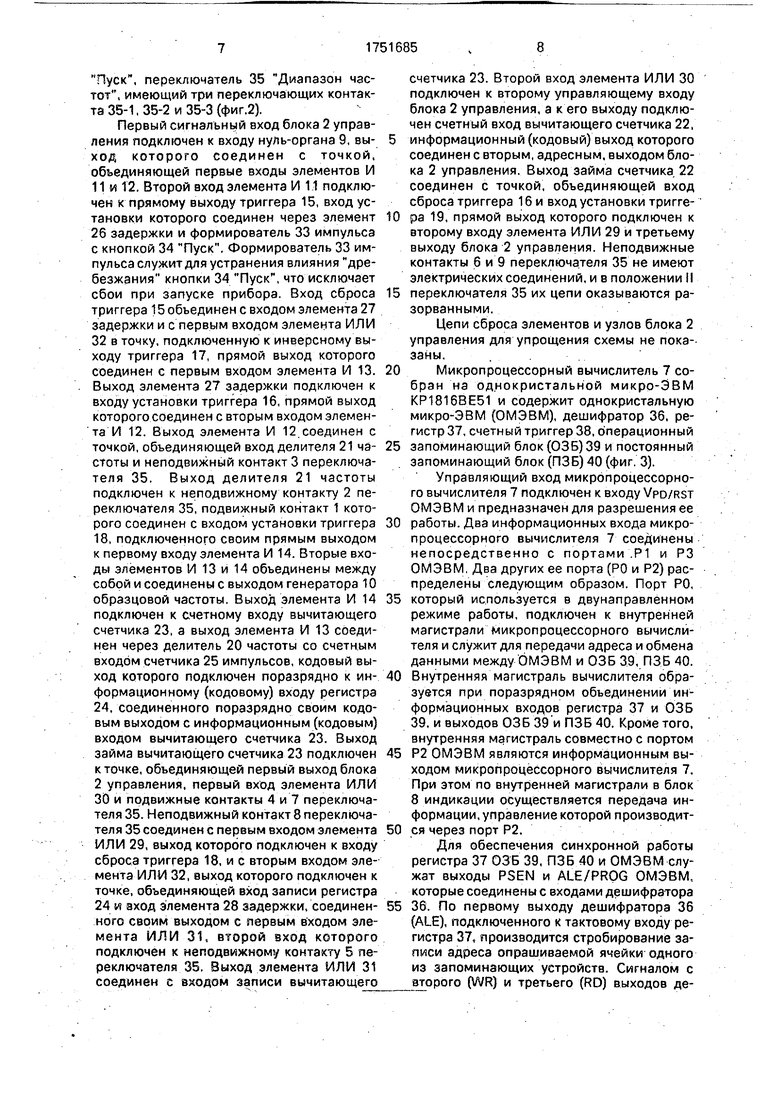

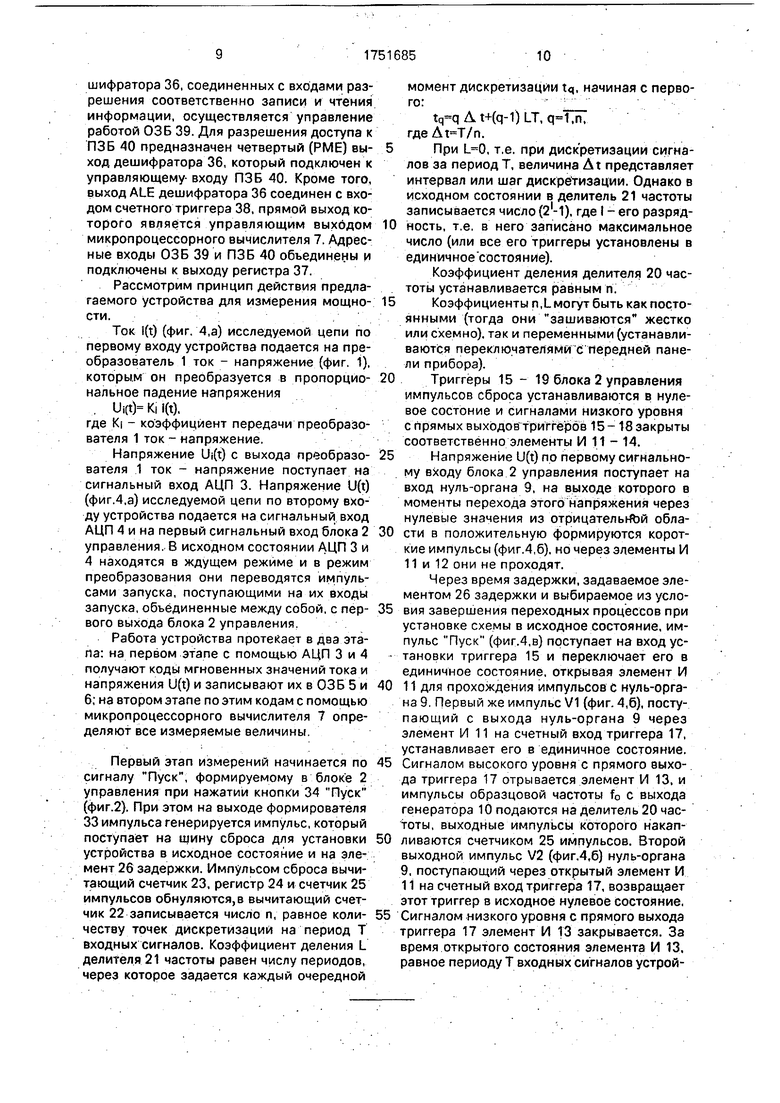

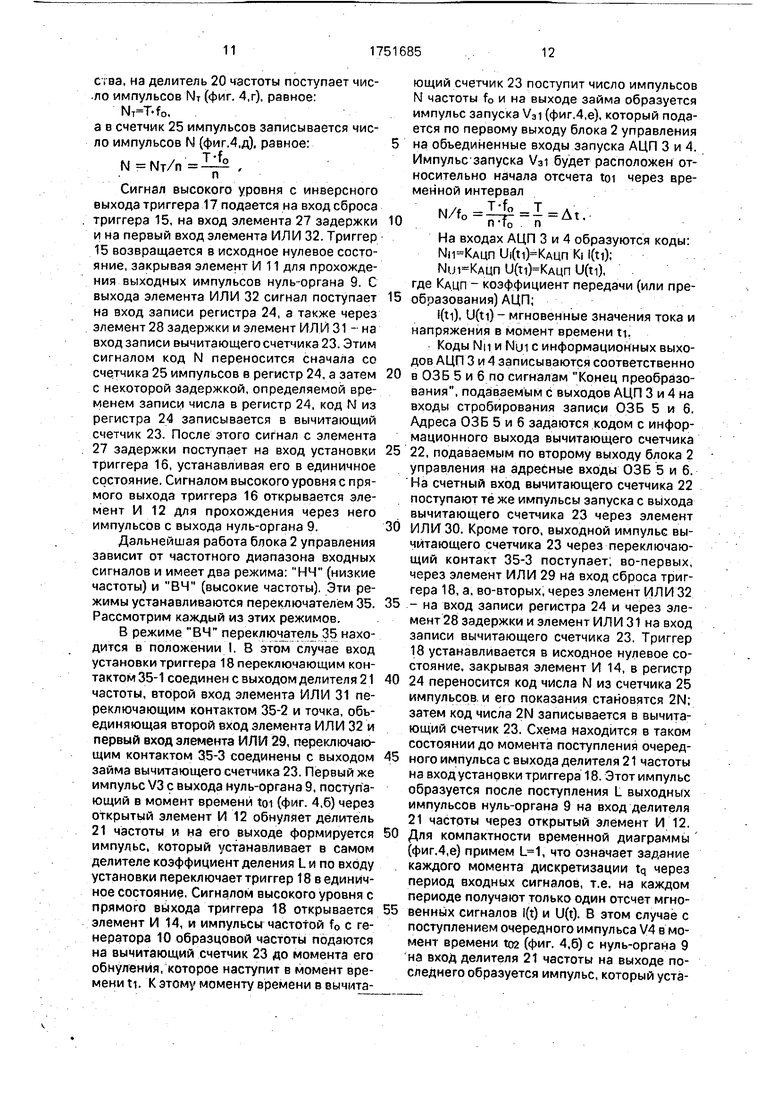

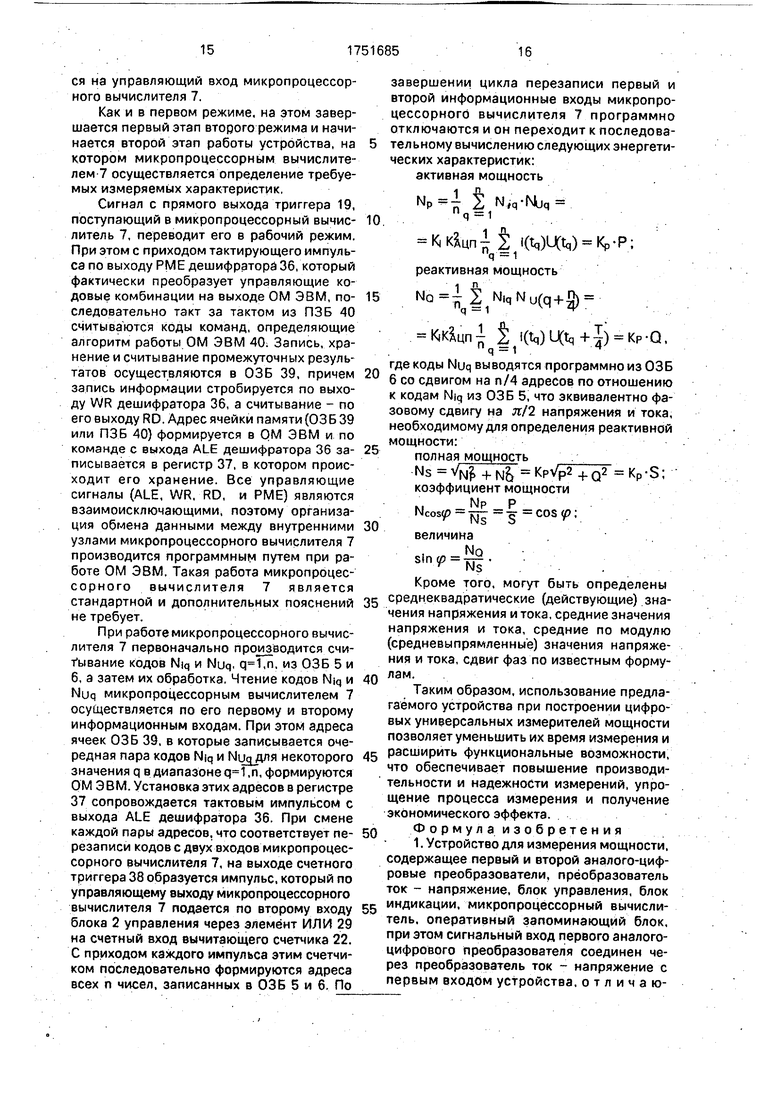

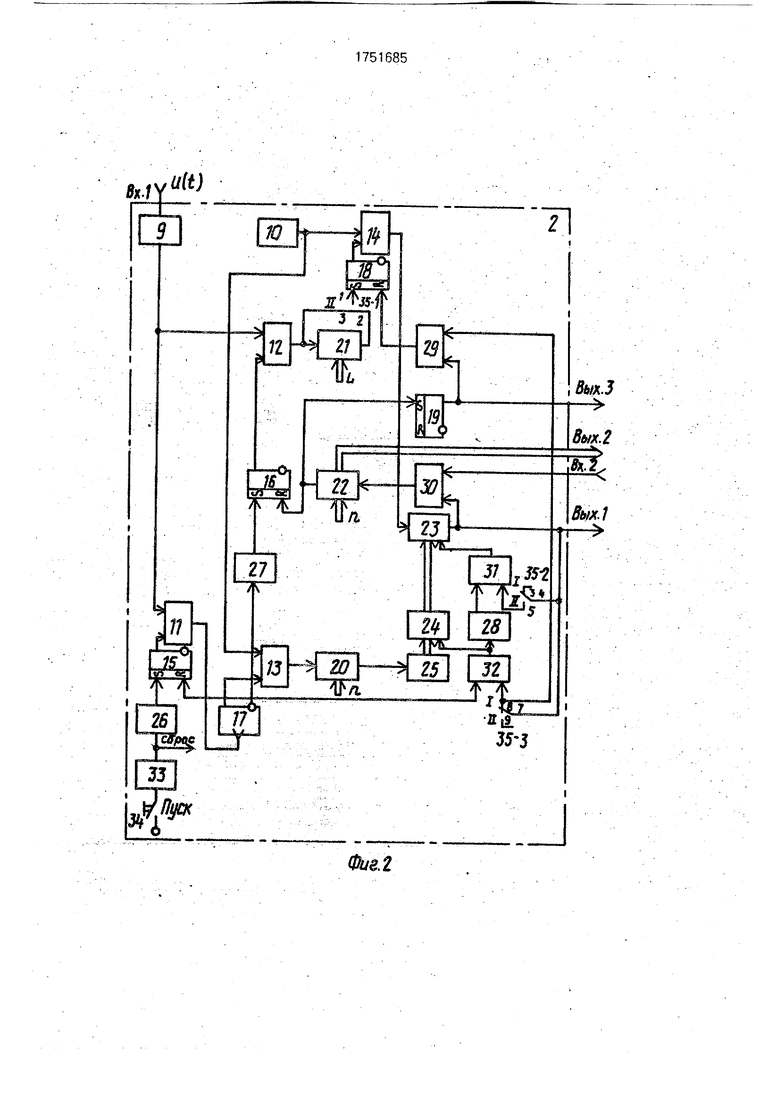

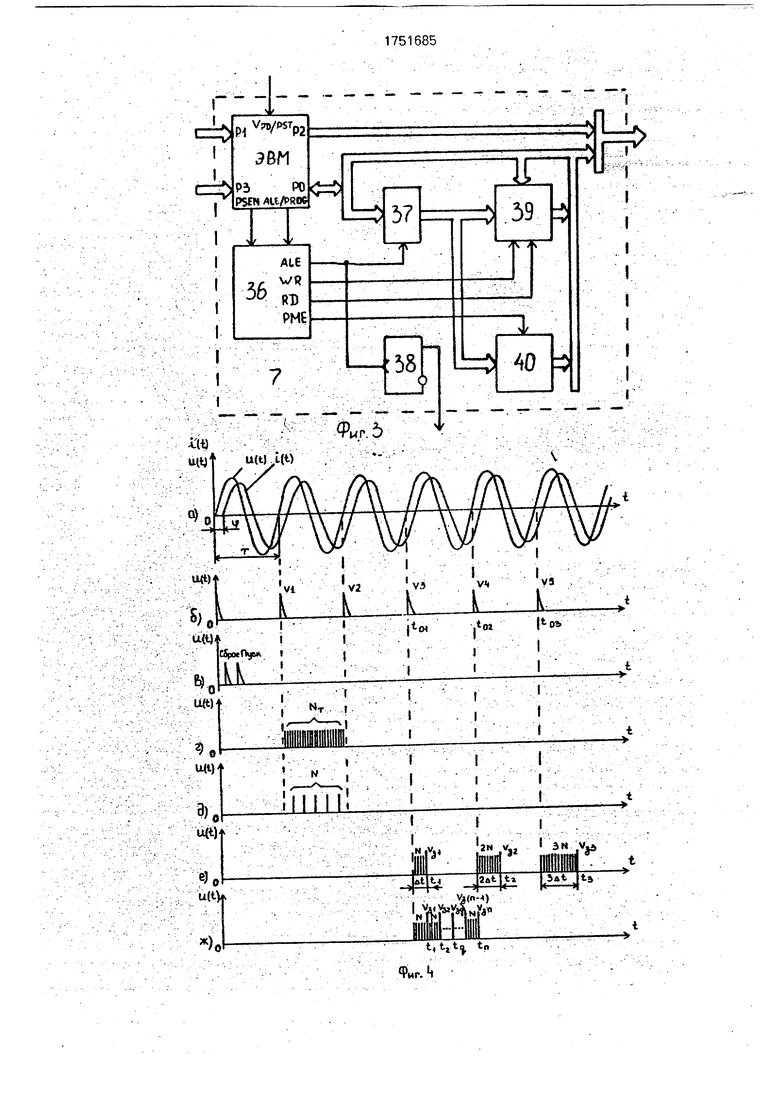

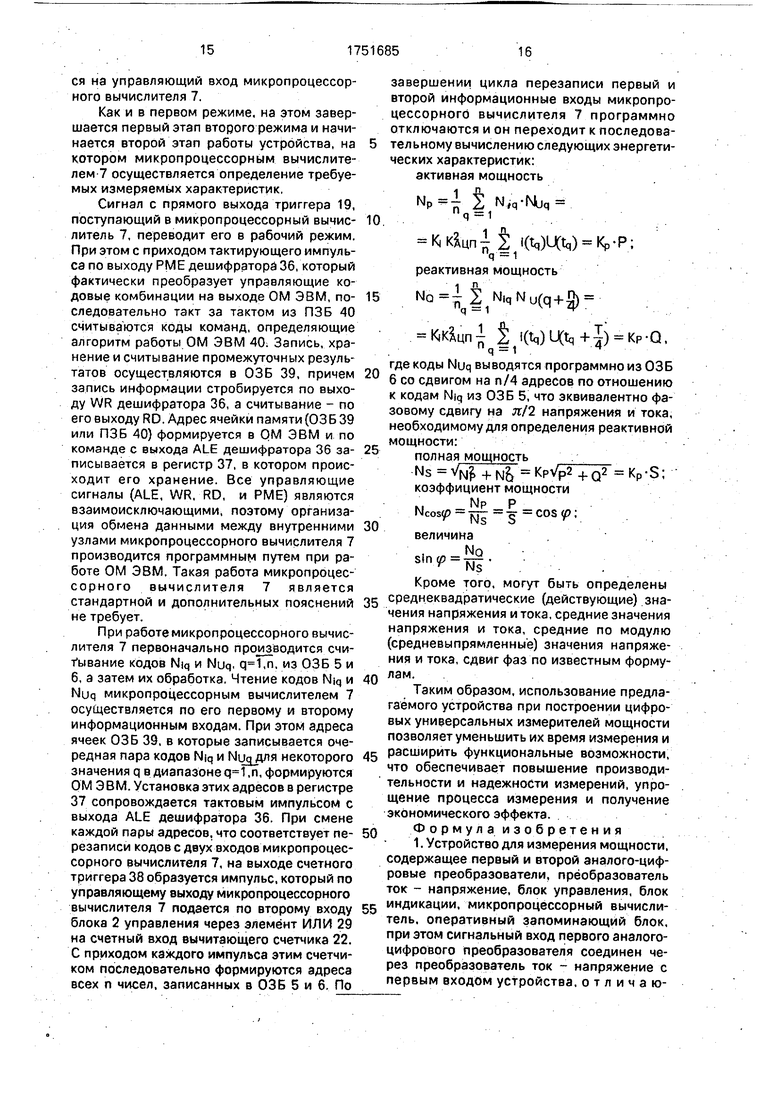

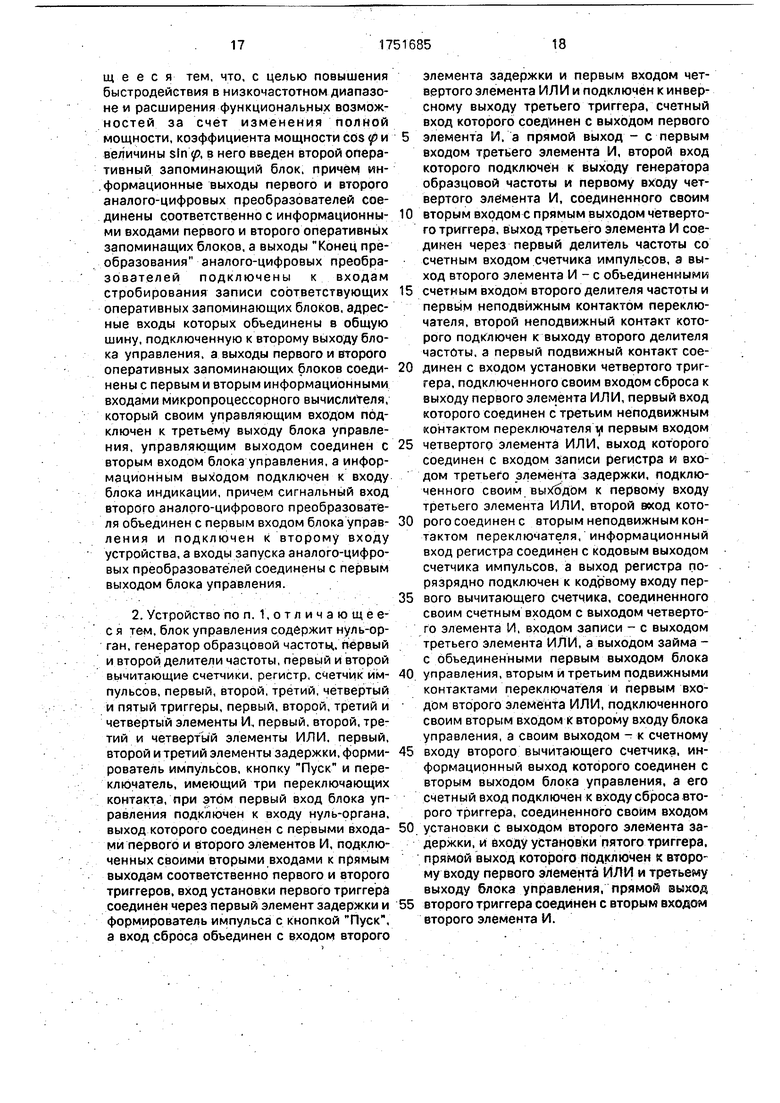

На фиг,1 приведена структурная электрическая схема предлагаемого устройства для измерения мощности; на фиг. 2 - структурная электрическая схема блока управления; на фиг, 3 - структурная электрическая схема микропроцессорного вычислителя; на фиг. 4 - временные диаграммы работы блока управления.

Устройство для измерения мощности содержит преобразователь 1 ток-напряжение, блок 2 управления, первый и второй аналого-цифровые преобразователи (АЦП) 3 и 4, первый и второй оперативные запоминающие блоки (03Б) 5 и 6, микропроцессорный вычислитель 7 и блок 8 индикации (фиг.1)./

Первый, токовый, вход устройства для измерения мощности через преобразователь Т ток - напряжение подключен к сигнальному входу АЦП 3, а второй вяод, вход напряжения, соединен с точкой, объединяющей сигнальный вход АЦП 4 и первый вход блока 2 управления. Входы запуска АЦП 3 и Л объединены между собой и подключены к первому выходу блока 2 управления. Информационные выходы АЦП 3 и 4 соединены с информационными входами (входами данных) ОЗБ 5 и 6 соответственно. Выход Конец преобразования АЦП 3 подключен к входу стробирования записи ОЗБ 5, а выход Конец преобразования АЦП 4 - к входу стробирования записи ОЗБ 6. Адресные входы ОЗБ 5 и б объединены в общую шину, соединенную с вторым адресным ЁЫХОДОМ блока 2 управления, а их выходы подключены соответственно к первому и второму информационным входам (входам данных) микропроцессорного вычислителя 7, управляющий вход которого соединен с третьим выходом блока 2 управления. Управляющий выход микропроцессорного вычислителя 7 подключен к второму входу блока 2 управления, а его информационный выход соединен с входом блока 8 индикации.

Блок 2 управления содержит нуль-орган 9, генератор 10 образцовой частоты, элементы И 11 - 14, триггеры 15-19, делители 20 и 21 частоты, вычитающие счетчики 22 и 23, регистр 24, счетчик 25 импульсов, элементы 26 - 28 задержки,,элементы ИЛИ 29 - 32, формирователь33 импульса, кнопку 34

Пуск, переключатель 35 Диапазон частот, имеющий три переключающих контакта 35-1, 35-2 и 35-3 (фиг.2).

Первый сигнальный вход блока 2 управления подключен к входу нуль-органа 9, выход которого соединен с точкой, объединяющей первые входы элементов И 11 и 12. Второй вход элемента И 11 подключен к прямому выходу триггера 15, вход установки которого соединен через элемент 26 задержки и формирователь 33 импульса с кнопкой 34 Пуск. Формирователь 33 импульса служит для устранения влияния дребезжания кнопки 34 Пуск, что исключает сбои при запуске прибора. Вход сброса триггера 15 объединен с входом элемента 27 задержки и с первым входом элемента ИЛИ 32 в точку, подключенную к инверсному выходу триггера 17, прямой выход которого соединен с первым входом элемента И 13. Выход элемента 27 задержки подключен к входу установки триггера 16, прямой выход которого соединен с вторым входом элемента И 12. Выход элемента И 12 соединен с точкой, объединяющей вход делителя 21 частоты и неподвижный контакт 3 переключателя 35. Выход делителя 21 частоты подключен к неподвижному контакту 2 переключателя 35, подвижный контакт 1 которого соединен с входом установки триггера 18, подключенного своим прямым выходом к первому входу элемента И 14. Вторые входы элементов И 13 и 14 объединены между собой и соединены с выходом генератора 10 образцовой частоты. Выход элемента И 14 подключен к счетному входу вычитающего счетчика 23, а выход элемента И 13 соединен через делитель 20 частоты со счетным входом счетчика 25 импульсов, кодовый выход которого подключен поразрядно к информационному (кодовому) входу регистра 24, соединенного поразрядно своим кодовым выходом с информационным (кодовым) входом вычитающего счетчика 23. Выход займа вычитающего счетчика 23 подключен к точке, объединяющей первый выход блока 2 управления, первый вход элемента ИЛИ 30 и подвижные контакты 4 и 7 переключателя 35. Неподвижный контакт 8 переключателя 35 соединен с первым входом элемента ИЛИ 29, выход которого подключен к входу сброса триггера 18, и с вторым входом элемента ИЛИ 32, выход которого подключен к точке, объединяющей вход записи регистра 24 и аход элемента 28 задержки, соединенного своим выходом с первым входом элемента ИЛИ 31, второй вход которого подключен к неподвижному контакту 5 переключателя 35. Выход элемента ИЛИ 31 соединен с входом записи вычитающего

счетчика 23. Второй вход элемента ИЛИ 30 подключен к второму управляющему входу блока 2 управления, а к его выходу подключен счетный вход вычитающего счетчика 22,

информационный (кодовый) выход которого соединен с вторым, адресным, выходом блока 2 управления. Выход займа счетчика 22 соединен с точкой, объединяющей вход сброса триггера 16 и вход установки тригге0 ра 19, прямой выход которого подключен к второму входу элемента ИЛИ 29 и третьему выходу блока 2 управления. Неподвижные контакты 6 и 9 переключателя 35 не имеют электрических соединений, и в положении II

5 переключателя 35 их цепи оказываются разорванными.

Цепи сброса элементов и узлов блока 2 управления для упрощения схемы не показаны.

0 Микропроцессорный вычислитель 7 собран на однокристальной микро-ЭВМ КР1816ВЕ51 и содержит однокристальную микро-ЭВМ (ОМЭВМ), дешифратор 36, регистр 37, счетный триггер 38, операционный

5 запоминающий блок (ОЗБ) 39 и постоянный запоминающий блок (ПЗБ) 40 (фиг. 3).

Управляющий вход микропроцессорного вычислителя 7 подключен к входу VPD/RST ОМЭВМ и предназначен для разрешения ее

0 работы. Два информационных входа микропроцессорного вычислителя 7 соединены непосредственно с портами Р1 и РЗ ОМЭВМ, Два других ее порта (РО и Р2) распределены следующим образом. Порт РО,

5 который используется в двунаправленном режиме работы, подключен к внутренней магистрали микропроцессорного вычислителя и служит для передачи адреса и обмена данными между ОМЭВМ и ОЗБ 39, ПЗБ 40.

0 Внутренняя магистраль вычислителя образуется при поразрядном объединении информационных входов регистра 37 и ОЗБ 39, и выходов ОЗБ 39 и ПЗБ 40. Кроме того, внутренняя магистраль совместно с портом

5 Р2 ОМЭВМ являются информационным выходом микропроцессорного вычислителя 7. При этом по внутренней магистрали в блок 8 индикации осуществляется передача информации, управление которой производит0 ся через порт Р2.

Для обеспечения синхронной работы регистра 37 ОЗБ 39, ПЗБ 40 и ОМЭВМ служат выходы PSEN и ALE/PROG ОМЭВМ, которые соединены с входами дешифратора

5 36. По первому выходу дешифратора 36 (ALE), подключенного к тактовому входу регистра 37, производится стробирование записи адреса опрашиваемой ячейки одного из запоминающих устройств. Сигналом с второго (WR) и третьего (RD) выходов дешифратора 36, соединенных с входами разрешения соответственно записи и чтения информации, осуществляется управление работой 03Б 39. Для разрешения доступа к ПЗБ 40 предназначен четвертый (РМЕ) выход дешифратора 36, который подключен к управляющему- входу ПЗБ 40. Кроме того, выход ALE дешифратора 36 соединен с входом счетного триггера 38, прямой выход которого является управляющим выходом микропроцессорного вычислителя 7. Адресные входы ОЗБ 39 и ПЗБ 40 объединены и подключены к выходу регистра 37.

Рассмотрим принцип действия предлагаемого устройства для измерения мощности.

Ток l(t) (фиг. 4,а) исследуемой цепи по первому входу устройства подается на преобразователь 1 ток - напряжение (фиг. 1), которым он преобразуется в пропорциональное падение напряжения

Ui(t) Ki i(t).

где KI - коэффициент передачи преобразователя 1 ток - напряжение.

Напряжение Ui(t) с выхода преобразователя 1 ток - напряжение поступает на сигнальный вход АЦП 3. Напряжение U(t) (фиг.4,а) исследуемой цепи по второму входу устройства подается на сигнальный вход АЦП 4 и на первый сигнальный вход блока 2 управления. В исходном состоянии АЦП 3 и 4 находятся в ждущем режиме и в режим преобразования они переводятся импульсами запуска, поступающими на их входы запуска, объединенные между собой, с первого выхода блока 2 управления.

Работа устройства протекает в два этапа: на первом этапе с помощью АЦП 3 и 4 получают коды мгновенных значений тока и напряжения U(t) и записывают их в ОЗБ 5 и 6; на втором этапе по этим кодам с помощью микропроцессорного вычислителя 7 определяют все измеряемые величины.

Первый этап измерений начинается по сигналу Пуск, формируемому в блоке 2 управления при нажатии кнопки 34 Пуск (фиг.2). При этом на выходе формирователя 33 импульса генерируется импульс, который поступает на шину сброса для установки устройства в исходное состояние и на элемент 26 задержки. Импульсом сброса вычитающий счетчик 23, регистр 24 и счетчик 25 импульсов обнуляются, в вычитающий счетчик 22 записывается число п, равное количеству точек дискретизации на период Т входных сигналов. Коэффициент деления L делителя 21 частоты равен числу периодов, через которое задается каждый очередной

момент дискретизации ц, начиная с первого:

At+(q-1)LT,,n, где .

5При , т.е. при дискретизации сигналов за период Т, величина At представляет интервал или шаг дискретизации. Однако в исходном состоянии в делитель 21 частоты записывается число (2-1), где I - его разряд0 ность, т.е, в него записано максимальное число (или все его триггеры установлены в единичное состояние).

Коэффициент деления делителя 20 частоты устанавливается равным п.

5 Коэффициенты n,Lмогут быть как постоянными (тогда они зашиваются жестко или схемно). так и переменными (устанавливаются переключателями с передней панели прибора).

0 Триггеры 15 - 19 блока 2 управления импульсов сброса устанавливаются в нулевое состоние и сигналами низкого уровня с прямых выходов триггеров 15-18 закрыты соответственно элементы И 11 - 14.

5 Напряжение U(t) по первому сигнальному входу блока 2 управления поступает на вход нуль-органа 9, на выходе которого в моменты перехода этого напряжения через нулевые значения из отрицательной обла0 сти в положительную формируются короткие импульсы (фиг.4,6), но через элементы И 11 и 12 они не проходят.

Через время задержки, задаваемое элементом 26 задержки и выбираемое из усло5 вия завершения переходных процессов при установке схемы в исходное состояние, импульс Пуск (фиг.4,в) поступает на вход ус- - тановки триггера 15 и переключает его в единичное состояние, открывая элемент И

0 11 для прохождения импульсов с нуль-органа 9. Первый же импульс V1 (фиг. 4,6), поступающий с выхода нуль-органа 9 через элемент И 11 на счетный вход триггера 17, устанавливает его в единичное состояние.

5 Сигналом высокого уровня с прямого выхода триггера 17 отрывается элемент И 13, и импульсы образцовой частоты f0 с выхода генератора 10 подаются на делитель 20 частоты, выходные импульсы которого накап0 ливаются счетчиком 25 импульсов. Второй выходной импульс V2 (фиг.4,6) нуль-органа 9, поступающий через открытый элемент И 11 на счетный вход триггера 17, возвращает этот триггер в исходное нулевое состояние,

5 Сигналом низкого уровня с прямого выхода триггера 17 элемент И 13 закрывается. За время открытого состояния элемента И 13, равное периоду Т входных сигналов устройсгва, на делитель 20 частоты поступает чис- .ло импульсов NT (фиг. 4,г), равное: Мт-T fo,

а в счетчик 25 импульсов записывается число импульсов N (фиг.4,д). равное:

,

Сигнал высокого уровня с инверсного выхода триггера 17 подается на вход сброса триггера 15, на вход элемента 27 задержки и на первый вход элемента ИЛИ 32. Триггер 15 возвращается в исходное нулевое состояние, закрывая элемент И 11 для прохождения выходных импульсов нуль-органа 9. С выхода элемента ИЛИ 32 сигнал поступает на вход записи регистра 24, а также через элемент 28 задержки и элемент ИЛИ 31 - на вход записи вычитающего счетчика 23. Этим сигналом код N переносится сначала со счетчика 25 импульсов в регистр 24, а затем с некоторой задержкой, определяемой временем записи числа в регистр 24, код N из регистра 24 записывается в вычитающий счетчик 23, После этого сигнал с элемента 27 задержки поступает на вход установки триггера 16, устанавливая его в единичное состояние. Сигналом высокого уровня с прямого выхода триггера 16 открывается элемент И 12 для прохождения через него импульсов с выхода нуль-органа 9.

Дальнейшая работа блока 2 управления зависит от частотного диапазона входных сигналов и имеет два режима: НЧ (низкие частоты) и ВЧ (высокие частоты). Эти режимы устанавливаются переключателем 35. Рассмотрим каждый из этих режимов.

В режиме ВЧ переключатель 35 находится в положении I. 8 этом случае вход установки триггера 18 переключающим контактом 35-1 соединен с выходом делителя 21 частоты, второй вход элемента ИЛИ 31 переключающим контактом 35-2 и точка, объединяющая второй вход элемента ИЛИ 32 и первый вход элемента ИЛИ 29, переключающим контактом 35-3 соединены с выходом займа вычитающего счетчика 23. Первый же импульс V3 с выхода нуль-органа 9, поступающий в момент времени tot (фиг. 4,6) через открытый элемент И 12 обнуляет делитель 21 частоты и на его выходе формируется импульс, который устанавливает в самом делителе коэффициент деления LM по входу установки переключает триггер 18 в единичное состояние, Сигналом высокого уровня с прямого выхода триггера 18 открывается элемент И 14, и импульсы частотой f0 с генератора 10 образцовой частоты подаются на вычитающий счетчик 23 до момента его обнуления, которое наступит в момент времени ti. К этому моменту времени в вычита0

ющий счетчик 23 поступит число импульсов N частоты f0 и на выходе займа образуется импульс запуска V3i (фиг,4,е), который подается по первому выходу блока 2 управления на объединенные входы запуска АЦП 3 и 4. Импульс-запуска V31 будет расположен относительно начала отсчета toi через временной интервал

N/f0 .

П То П

На входах АЦП З и 4 образуются коды: NH-КАЦП Ui(ti)KAun Ki l(ti); NUI-КАЦП U(ti)KAUn U(n), где КАЦП - коэффициент передачи (или преобразования) АЦП;

i(ti), U(ti) - мгновенные значения тока и напряжения в момент времени ti.

Коды Ми и NUI с информационных выходов АЦП 3 и 4 записываются соответственно

в 03Б 5 и 6 по сигналам Конец преобразования, подаваемым с выходов АЦП 3 и 4 на входы стробирования записи ОЗБ 5 и 6. Адреса ОЗБ 5 и 6 задаются кодом с информационного выхода вычитающего счетчика

22, подаваемым по второму выходу блока 2 управления на адресные входы ОЗБ 5 и 6. На счетный вход вычитающего счетчика 22 поступают те же импульсы запуска с выхода вычитающего счетчика 23 через элемент

ИЛИ 30. Кроме того, выходной импульс вычитающего счетчика 23 через переключающий контакт 35-3 поступает, во-первых, через элемент ИЛИ 29 на вход сброса триггера 18, а, во-вторых, через элемент ИЛИ 32

- на вход записи регистра 24 и через элемент 28 задержки и элемент ИЛИ 31 на вход записи вычитающего счетчика 23. Триггер 18 устанавливается в исходное нулевое состояние, закрывая элемент И 14, в регистр

24 переносится код числа N из счетчика 25 импульсов и его показания становятся 2N; затем код числа 2N записывается в вычитающий счетчик 23. Схема находится в таком состоянии до момента поступления очередного импульса с выхода делителя 21 частоты на вход установки триггера 18. Этот импульс образуется после поступления L выходных импульсов нуль-органа 9 на вход делителя 21 частоты через открытый элемент И 12.

Для компактности временной диаграммы (фиг.4,е) примем , что означает задание каждого момента дискретизации tq через период входных сигналов, т.е. на каждом периоде получают только один отсчет мгновенных сигналов l(t) и U(t). В этом случае с поступлением очередного импульса V4 в момент времени to2 (фиг. 4,6) с нуль-органа 9 на вход делителя 21 частоты на выходе последнего образуется импульс, который устанавливает триггер 18 по его входу установки в единичное состояние, открывая элемент И 14. Импульсы частоты f0 с генератора 10 поступают через открытый элемент И 14 на счетный вход вычитающего счетчика 23 до его обнуления, при котором на его выходе займа образуется второй импульс запуска V32 (фиг. 4,е). Он будет расположен относительно опорного момента времени to2 через временной интервал

2N/f0 - 2- 2At.

ПТоП

Импульс запуска V32 выполняет те же операции, что и импульс запуска V31. При этом в регистре 24, а затем в вычитающем счетчике 23 будет записан код числа 3N и очередной импульс запуска V33 на его выходе будет сформирован относительно опорного момента времени юз через временной интервал

3N/f0 2 3At.

ПТо

В дальнейшем работа блока 2 управления повторяется аналогично предыдущему и импульсы запуска будут формироваться в моменты времени tq, отстоящие от начала каждого очередного периода на qAt, что соответствует интервалу дискретизации At, в то время как точки дискретизации распределены через один период входных сигналов.

При другом числе L работа блока 2 управления сохраняется, отличие состоит в том, что импульсы на выходе делителя 21 частоты образуются через L выходных импульсов нуль-органа 9 и тем самым на L периодов смещаются опорные моменты времени toa. toaton.

Так продолжается до момента задания всех п точек дискретизации tq или импульсов запуска на выходе вычитающего счетчика 23, после чего вычитающий счетчик 22 обнуляется. На его выходе займа образуется импульс, поступающий на вход сброса триггера 16 и на вход установки триггера 19. Триггер 16 возвращается в исходное нулевое состояние, закрывая элемент И 12. Триг- гер 10 переключается в единичное состояние и сигнал высокого уровня с его прямого выхода, являющегося третьим выходом блока 2 управления, подается в микропроцессорный вычислитель 7 по его управляющему входу. Сигналом низкого уровня с прямого выхода триггера 18, установленного в нулевое состояние, закрывается элемент И 14. На этом работа блока 2 управления прекращается и завершается первый этап измерений. В 03 Б 5 и 6 будут

записаны коды Niq и Nuq, ,n, мгновенных значений тока l(t) и напряжения U(t).

В режиме НЧ переключатель 35 устанавливается в положение II. В данном режиме моменты дискретизации tq задаются за один период входных сигналов (фиг.4,ж). До момента времени ti (формирования первого импульса запуска V3i) устройство и его блок 2 управления работают аналогично, отличие

0 состоит только в том, что на вход установки триггера 18 импульс нуль-органа V3 поступаете выхода элемента И 12 через переключающий контакт 35-1. Основное отличие в работе устройства обусловлено формирова5 нием остальных импульсов запуска V32.

У3зV3n на выходе вычитающего счетчика

23, которые следуют с шагом дискретизации At. Для обеспечения этого временного интервала в регистре 24 сохраняется записан0 ное в нем число импульсов N, так как цепь записи кода в регистр 24 из счетчика 25 импульсами V32, V33,...,V3n с выхода займа вычитающего счетчика 23 через переключающий контакт 35-3 разорвана. И это число

5 импульсов N теми же импульсами V32, У3зV3n с выхода займа вычитающего счетчика 23 через замкнутый переключающий контакт 35-2 и элемент ИЛИ 31 записываются в вычитающий счетчик 23. Н8 счетный

0 вход вычитающего счетчика 23 импульсы образцовой частоты f0 с выхода генератора 10 подаются через открытый элемент И14 непрерывно в течение всего периода Т входных сигналов, ограниченного импульсами

5 V3 и V4 с выхода нуль-органа 9 (фиг. 4,ж). Элемент И 14 открыт в этом интервале сигналом высокого уровня с прямого выхода триггера 18, так как этот триггер остается в единичном состоянии до момента формиро0 вания импульса Узп на выходе займа вычитающего счетчика 23. Все остальные

импульсы V31, V32V3(n-i) на триггер 18 не

воздействуют,как в предыдущем режиме, поскольку переключающим контактом 35-3

5 разорвана их цепь поступления через элемент ИЛ И 29 на вход сброса этого триггера. В момент времени tn формирования последнего импульса V3n (фиг,4,ж) на выходе займа вычитающего счетчика 23 обнуляется вычи0 тающий счетчик 22, и, как и в предыдущем режиме, импульсом с его выхода займа триггер 16 устанавливается в исходное состояние, закрывая элемент И 12, а триггер 19 переключается в единичное состояние. При

5 этом сигналом высокого уровня с его прямого выхода, поступающим через элемент ИЛИ 19 на вход сброса триггера 18, последний устанавливается в исходное состояние, закрывая элемент И 14. Этот же сигнал по третьему выходу блока управления подается на управляющий вход микропроцессорного вычислителя 7.

Как и в первом режиме, на этом завершается первый этап второго режима и начинается второй этап работы устройства, на котором микропроцессорным вычислителем 7 осуществляется определение требуемых измеряемых характеристик,

Сигнал с прямого выхода триггера 19, поступающий в микропроцессорный вычис- литель 7, переводит его в рабочий режим. При этом с приходом тактирующего импульса по выходу РМЕ дешифратора 36, который фактически преобразует управляющие кодовые комбинации на выходе ОМ ЭВМ, по- следовательно такт за тактом из ПЗБ 40 считываются коды команд, определяющие алгоритм работы ОМ ЭВМ 40. Запись, хранение и считывание промежуточных результатов осуществляются в ОЗБ 39, причем запись информации стробируется по выходу WR дешифратора 36, а считывание - по его выходу RD. Адрес ячейки памяти (03 Б 39 или ПЗБ 40) формируется в ОМ ЭВМ и по команде с выхода ALE дешифратора 36 за- писывается в регистр 37, в котором происходит его хранение. Все управляющие сигналы (ALE, WR, RD, и РМЕ) являются взаимоисключающими, поэтому организация обмена данными между внутренними узлами микропроцессорного вычислителя 7 производится программным путем при работе ОМ ЭВМ. Такая работа микропроцессорного вычислителя 7 является стандартной и дополнительных пояснений не требует.

При работе микропроцессорного вычислителя 7 первоначально производится счи- Уывание кодов Niq и Nuq, ,n, из ОЗБ 5 и 6, а затем их обработка. Чтение кодов и Nuq микропроцессорным вычислителем 7 осуществляется по его первому и второму информационным входам. При этом адреса ячеек ОЗБ 39, в которые записывается очередная пара кодов Niq и Мцддля некоторого значения q в диапазоне ,n, формируются ОМ ЭВМ. Установка этих адресов в регистре 37 сопровождается тактовым импульсом с выхода ALE дешифратора 36. При смене каждой пары адресов, что соответствует пе- резаписи кодов с двух входов микропроцессорного вычислителя 7, на выходе счетного триггера 38 образуется импульс, который по управляющему выходу микропроцессорного вычислителя 7 подается по второму входу блока 2 управления через элемент ИЛИ 29 на счетный вход вычитающего счетчика 22. С приходом каждого импульса этим счетчиком последовательно формируются адреса всех п чисел, записанных в ОЗБ 5 и 6. По

завершении цикла перезаписи первый и второй информационные входы микропроцессорного вычислителя 7 программно отключаются и он переходит к последовательному вычислению следующих энергетических характеристик: активная мощность

Mr

4 t

К|йцпЈЈ i(tq)UCtq) Kp-P;

q 1 реактивная мощность

|iN,qNu(q+n)

КйцпЈ ДЮч) Ufo+}) Kp-Q,

где коды Nuq выводятся программно из ОЗБ 6 со сдвигом на п/4 адресов по отношению к кодам Niq из ОЗБ 5, что эквивалентно фазовому сдвигу на л:/2 напряжения и тока, необходимому для определения реактивной мощности:

полная мощность

Ns VNЈ+Nk KPVp2+Q2 KP-S;

коэффициент мощности Np P

Ncosp Щ jr COS р ;

величина slnp.

Кроме того, могут быть определены среднеквадратические (действующие) значения напряжения и тока, средние значения напряжения и тока, средние по модулю (средневыпрямленные) значения напряжения и тока, сдвиг фаз по известным формулам.

Таким образом, использование предлагаемого устройства при построении цифровых универсальных измерителей мощности позволяет уменьшить их время измерения и расширить функциональные возможности, что обеспечивает повышение производительности и надежности измерений, упрощение процесса измерения и получение экономического эффекта.

Формула изобретения

элемента задержки и первым входом четвертого элемента ИЛ И и подключен к инверсному выходу третьего триггера, счетный вход которого соединен с выходом первого 5 элемента И. а прямой выход - с первым входом третьего элемента И, второй вход которого подключен к выходу генератора образцовой частоты и первому входу четвертого элемента И, соединенного своим

0 вторым входом с прямым выходом четвертого триггера, выход третьего элемента И соединен через первый делитель частоты со счетным входом счетчика импульсов, а выход второго элемента И - с объединенными

5 счетным входом второго делителя частоты и первым неподвижным контактом переключателя, второй неподвижный контакт которого подключен к выходу второго делителя частоты, а первый подвижный контакт сое0 динен с входом установки четвертого триггера, подключенного своим входом сброса к выходу первого элемента ИЛИ, первый вход которого соединен с третьим неподвижным контактом переключателя у первым входом

5 четвертого элемента ИЛИ, выход которого соединен с входом записи регистра и ахо- дом третьего элемента задержки, подключенного своим выходом к первому входу третьего элемента ИЛИ, второй вход кото0 рого соединен с вторым неподвижным контактом переключателя, информационный вход регистра соединен с кодовым выходом счетчика импульсов, а выход регистра по- рязрядно подключен к кодрвому входу пер5 вого вычитающего счетчика, соединенного своим счетным входом с выходом четвертого элемента И, входом записи - с выходом третьего элемента ИЛИ, а выходом займа - с объединенными первым выходом блока

0 управления, вторым и третьим подвижными контактами переключателя и первым входом второго элемента ИЛИ, подключенного своим вторым входом к второму входу блока управления, а своим выходом - к счетному

5 входу второго вычитающего счетчика, информационный выход которого соединен с вторым выходом блока управления, а его счетный вход подключен к входу сброса второго триггера, соединенного своим входом

0 установки с выходом второго элемента задержки, и входу установки пятого триггера, прямой выход которого подключен к второму входу первого элемента ИЛИ и третьему выходу блока управления, прямой выход

5 второго триггера соединен с вторым входом второго элемента И.

И

I

Фиг,2

i

c±a

I I

Уй

TT

| Цифровой ваттметр | 1972 |

|

SU603914A1 |

| Тележка для перевозки поплавкового гидросамолета с суши на воду и обратно | 1926 |

|

SU5135A1 |

| Проспект фирмы Norma Medtechnik Optik Electronik Ges m.b.H, Австрия. | |||

Авторы

Даты

1992-07-30—Публикация

1990-01-30—Подача