кэ

4

Изобретение относится к вычислительной технике и может быть использовано в системах отображения графической информации.

Цель изобретения - повышение быстро- действия устройства.

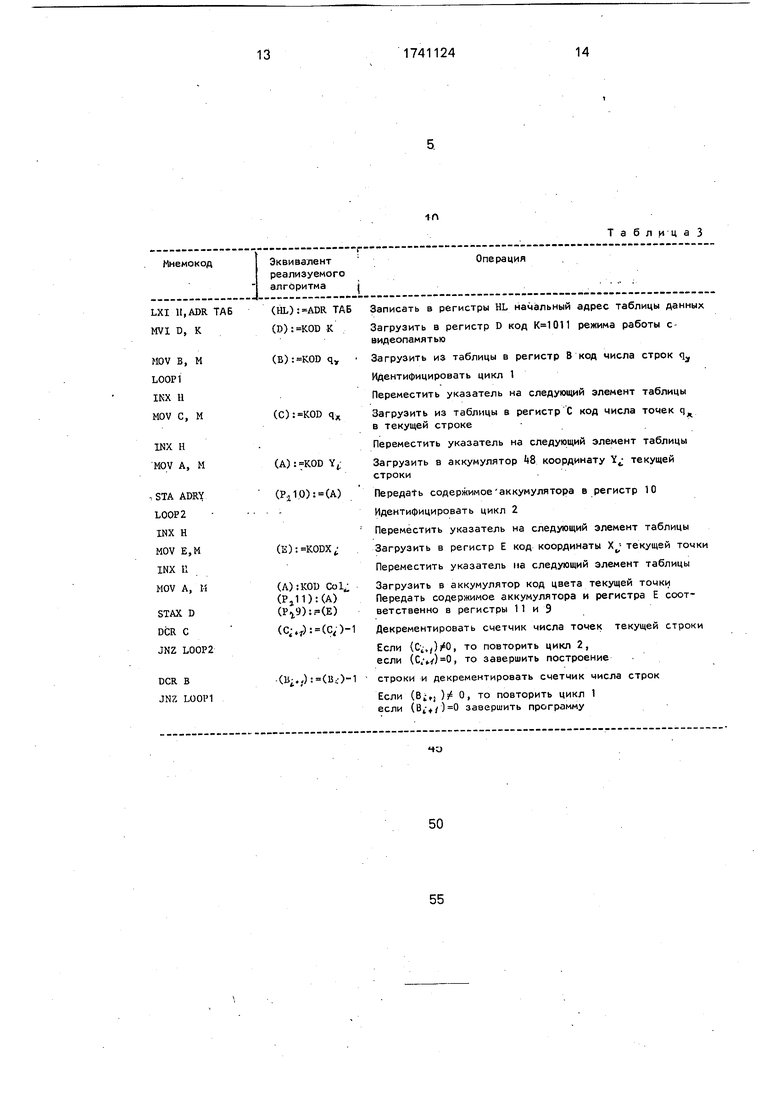

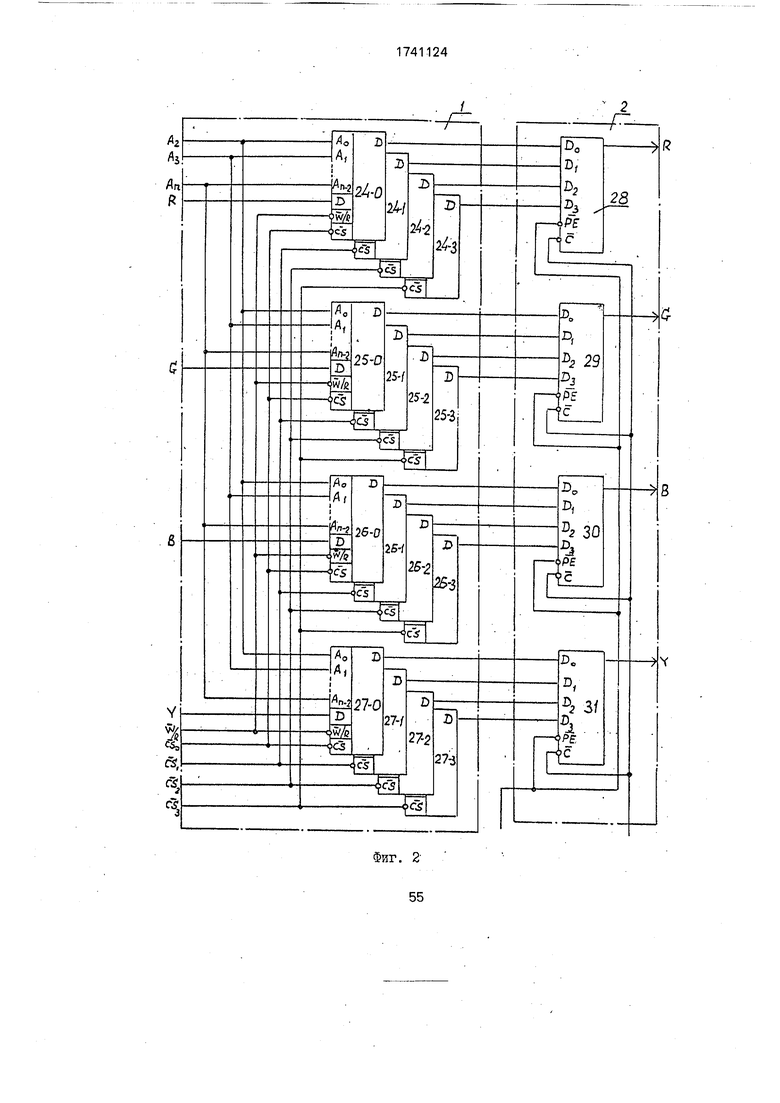

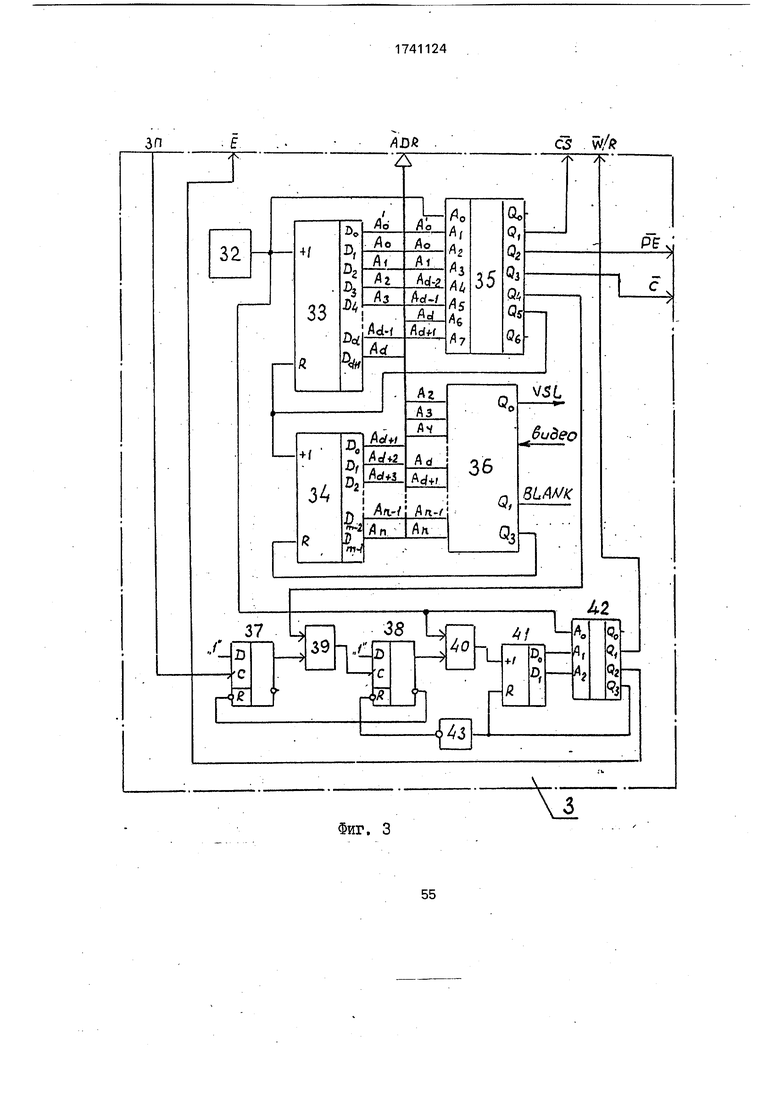

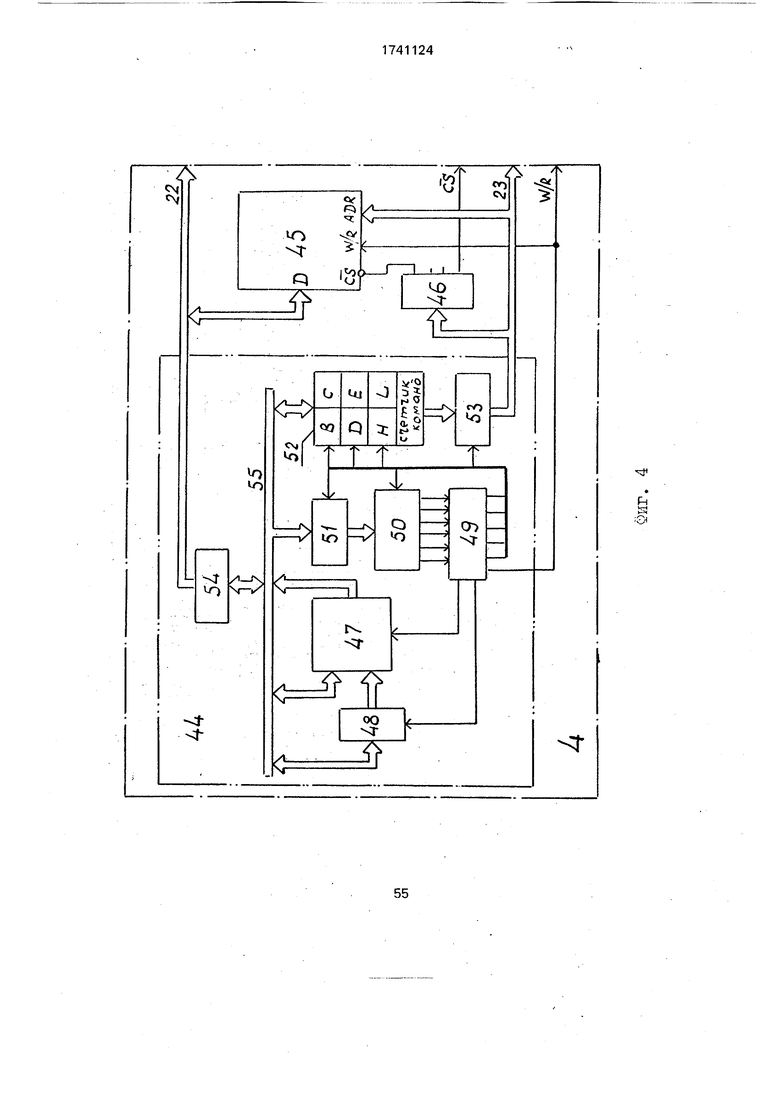

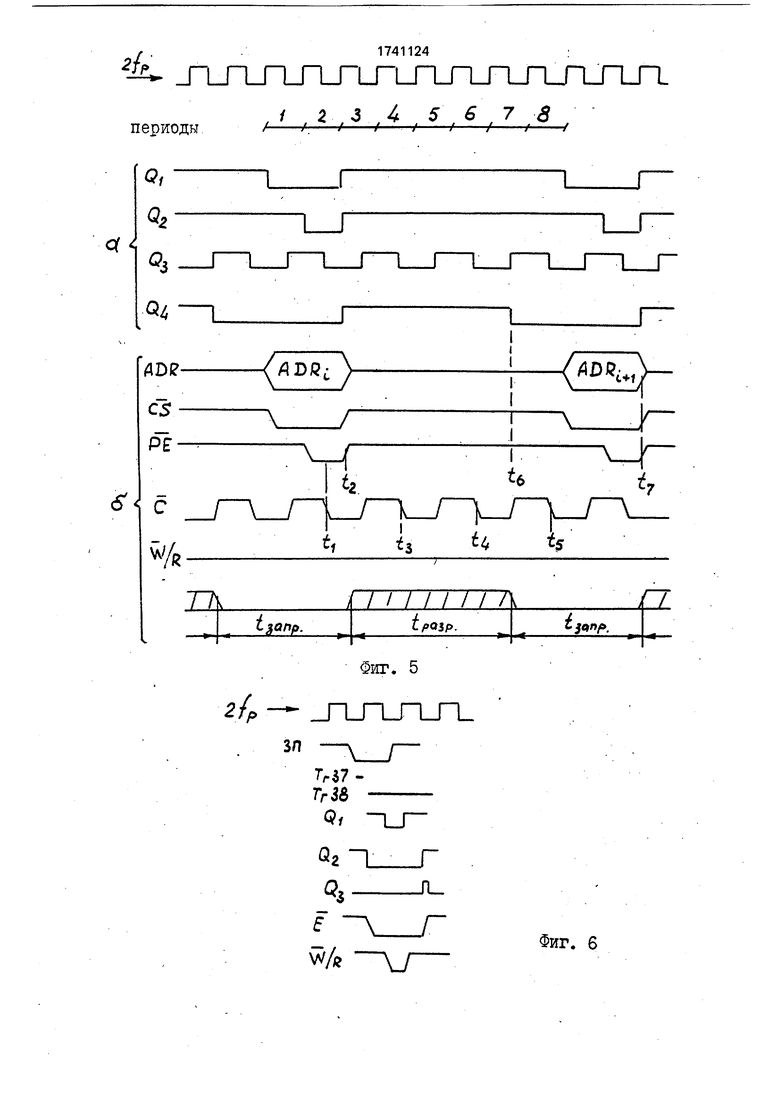

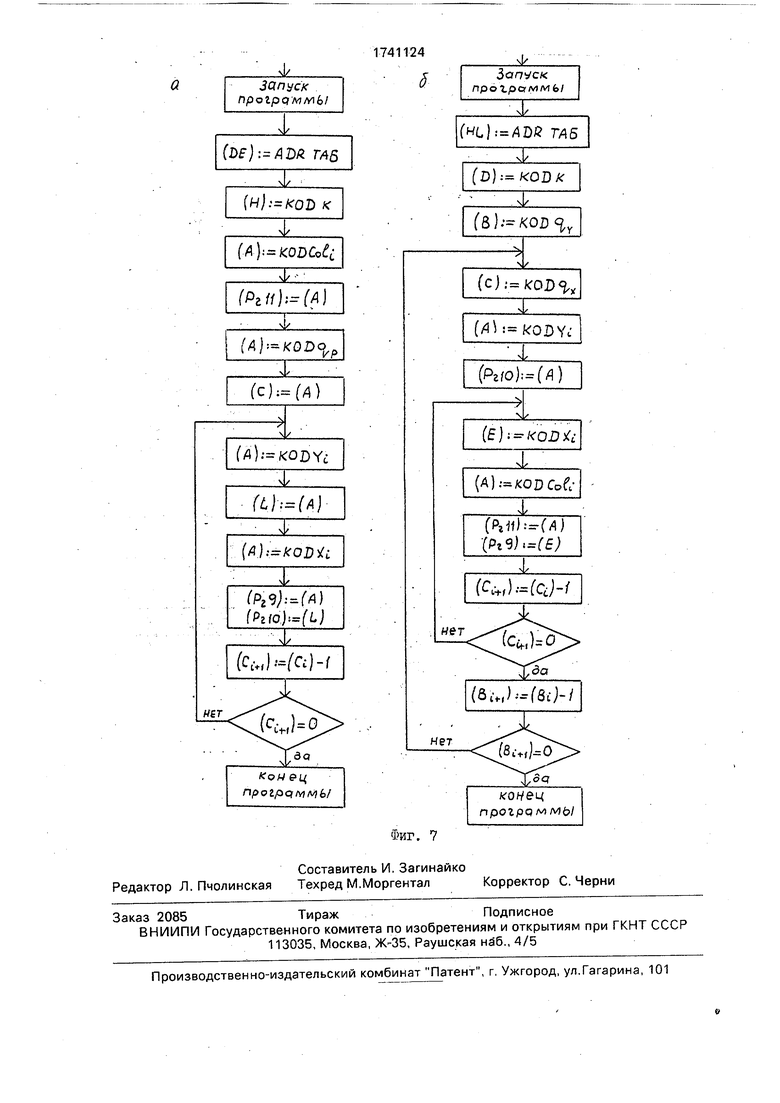

На фиг.1 приведена функциональная схема устройства; на фиг.2 - схема блоков видеопамяти и сдвиговых регистров; на фиг.З и 4 - схемы блока регенерации изо- бражений и ЭВМ; на фиг.5 и 6 - диаграммы формирования команд блоком регенерации изображений; на фиг.7 - схемы алгоритмов формирования и передачи в блок видеопамяти новой информации.

Устройство содержит блок 1 видеопамяти, блок 2 сдвиговых регистров, блок 3 регенерации изображений, коммутаторы 5-8, регистры 9- 11, дешифратор 12, преобразователь 13 кодов и элементы И 14 - 21, По- зицией 4 обозначено ЭВМ, позициями 22 и 23 - соответственно шина данных (информационный вход) и шина адресов (первый адресный вход) устройства.

Блок 1 видеопамяти содержит видеопа- мяти 24 - 27, например, статического типа, каждая из которых выполнена на четырех матричных накопителях емкостью d (m-2) бит, где d и m - число разрядов координатной сетки (X и У) экранной области дисплея. В видеопамяти 24 - 26 хранится информация о составе RGB-сигнала, а в видеопамяти 27-о его интенсивности.

Одноименные адресные входы А0, Ai,...An-2 и входы чтения - записи W/R всех матричных накопителей объединены и подключены к соответствующим входам блока.

Блок 2 сдвиговых регистров состоит из четырех сдвиговых регистров 28 - 31 по числу битов информационного кода.

Блок 3 регенерации изображений содержит генератор 32 тактовых импульсов, счетчик 33 пикселей по строке, счетчики 34 строк, блок 35 программируемой памяти, формирователь 36 видеосигнала, D-тригге- ры 37 и 38, элементы И 39 и 40, счетчик 41 микрокоманд, постоянную память (ПЗУ) 42 и элемент НЕ 43,

В состав ЭВМ 4 входят микропроцессор 44, оперативная память (ОЗУ) 45 и дешифратор 46 адреса, причем микропроцессор в упрощенном виде содержит арифметиче- ско-логическое устройство 47, аккумулятор 48, устройство управления 49, дешифратор 50 кода операций, регистры 51 команд, регистры 52 общего назначения (В, С, D, Ё, Н, L) регистр 53 адреса, буфер 54 данных и внутреннюю шину 55 данных.

Дешифратор 46 предназначен для формирования команд CS обращения ЭВМ к устройствам внешней памяти, к которым в данном случае относится ОЗУ 45 и видеопамять блока 1 с регистрами 9 - 11. На его входы подключены старшие разряды шины 23 адреса, например AIS, Аи и Ai3. При необходимости количество устройств типа памяти может быть увеличено за счет подключения к другим выходам дешифратора 46 дополнительных ОЗУ .

Преобразователь 13 кодов выполнен, например, на базе ПЗУ, которое программирует согласно табл.1. Сигнал STB, соответствующий 1, означает запись информации, пересылаемой по шинам 22 и 23, как в регистры 9-11, так и в соответствующие ячейки видеопамяти блока 1 (по нулевому сигналу STB пересылаемая информация фиксируется только в регистрах 9-11).

Устройство работает следующим образом.

В исходном состоянии сигналы на управляющих входах коммутаторов 6-8 отсутствуют и они установлены в положение, при котором входы регистров 9-11 оказываются подключенными к шине 22 данных. Эти регистры содержат произвольную информацию. На управляющий вход коммутатора 5 поступает сигнал высокого уровня, и к адресным входам АОАп-аблока 1 подключены выходы А2,...АП регистров 9 и 10. На выходах дешифратора 12 и на выходе управления чтением блока 3 установлены сигналы высокого уровня, которые через элементы И 17 - 20 транслируются на входы С5р...С5з выбора кристаллов блока 1. Сигналы высокого уровня установлены также на управляющем входе дешифратора 12, на входе W/R чтения-записи и разрешения параллельной записи РЕ сдвиговых регистров блока 2.

В ОЗУ 45 загружена программа вывода на экран дисплея новой графической информации и совокупность констант, определяющих цвет отображаемых пикселей, их количество, коды координат X, Y, и т.п.

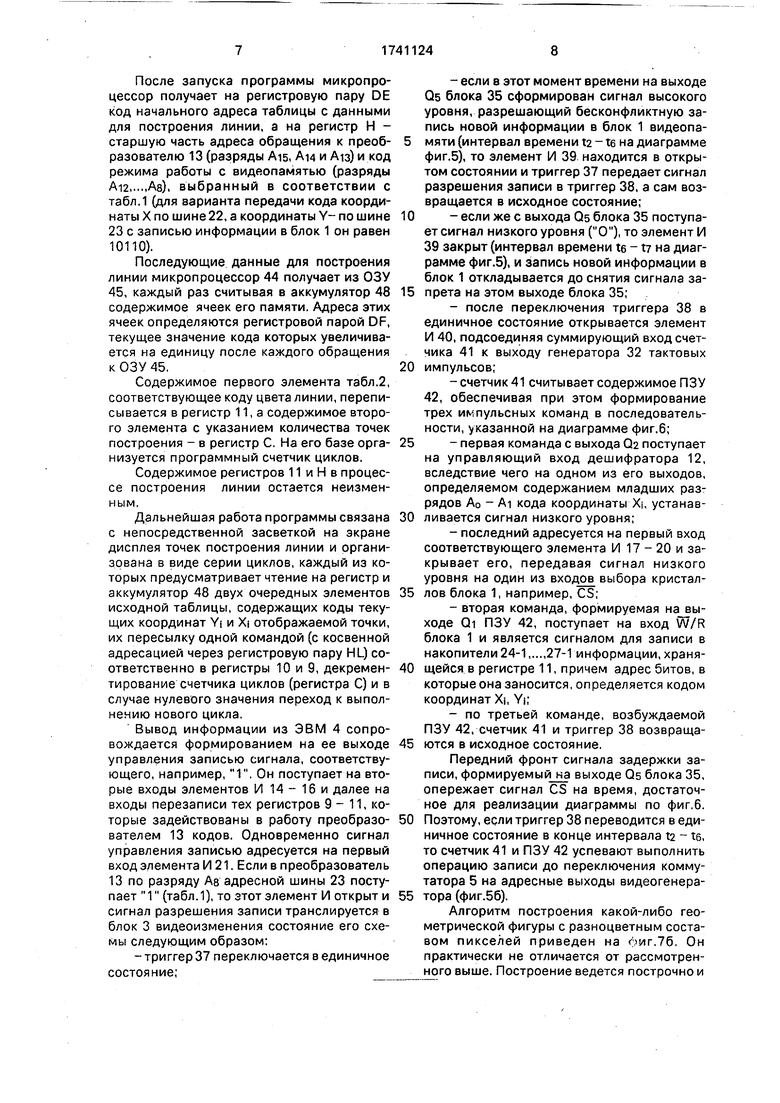

В элементы памяти блока 1 записана какая-либо графическая и алфавитно-цифровая информация.i . Вывод ее на экран дисплея осуществляется через сдвиговые регистры 28-31, содержимое которых обновляется каждые восемь периодов тактовой частоты 2fp, вырабатываемой генератором 32 (fp - частота переключения пикселей). Блок 35 запрограммировано таким образом, что на его выходах Они Qz сигналы низкого уровня (О) всг буждаются соответственно в начале первого и второго периодов, на выходе 0 - во второй половине 7-го периода, а на выходе Оз в середине всех четных периодов (фиг.ба). Длительность сигнала, формируемого на первом выходе блока 35, составляет 1 /fp. Он поступает на управляющий вход коммутатора 5 и на вторые входы элементов И 17-20, По этом команде коммутатор 5 подсоединяет выходы А2,...АП счетчиков 33 и 34 к адресным входам А0,...,Ап-2 блока .1, элементы И 17 - 20 закрываются, устанавливая сигналы низкого уровня на входах CS всех матричных накопителей 24 - 27. Вследствие этого на их выходы считывается информация о цвете и яркости соседних пикселей, объединенных общим кодом текущего адреса FDR. Импульсный сигнал, возбуждаемый на втором выходе блока 35, поступает на входы РЕ разрешения параллельной записи всех сдвиговых регистров 28-31 и подготавливает их к приему информации, выделенной блоком 1. Считывание ее в регистры 28-31 производится по заднему фронту первого импульса, поступившего с выхода Оз блока 35 (момент времени ti на диаграмме фиг.5). Одновременно часть этой информации, которая считана из накопителей 24-0, 25-0, 26-0 и 27-0, выводится на выходы R, G, В, Y устройства. По окончании второго периода (момент времени t2) сигналы на выходах СИ и Q2 блока 35 снимаются, коммутатор 5 возвращается в исходное состояние, а на входах CS и РЕ блоков 1 и 2 вновь устанавливаются сигналы высокого уровня. В моменты времени t3, t4 и ts на выходы устройства считываются данные о составе RGB-сигнала и его яркости для трех следующих пикселей, которые переписаны в регистры 28-31 соответственно из накопителей 24-1 ,...27-1, 24-2,...27-2 и 24-3....27-3. Далее цикл информации из блока видеопамяти повторяется, но уже для пикселей, имеющих общий адрес FDRi+i. Формирование кода адреса счетчиками 33 и 34 организовано применительно к прогрессивной развертке луча электронно-лучевой трубки (ЭЛТ) дисплея. В начале первой (верхней) строки оба счетчика находится в исходном состоянии и на их информационных выходах установлен нулевой код. В сдвиговые регистры 28-31 считываются данные, относящиеся к первым четырем пикселям этой строки. В дальнейшем код адреса увеличивается на единицу через каждые восемь импульсов тактовой частоты 2fp и соответственно этому производится обновление информации в сдвиговых регистрах блока 2.

Активная часть строки завершается формированием на выходах устройства информации, относящийся к пикселю с порядковым номером (2d-1), после чего возбуждение управляющих сигналов на выходах QiQA блока 35 прекращается, а форформирователь 36 организует для ЭЛТ сточный синхроимпульс и соответственно гасящий

импульс напряжения на время обратного хода луча. Последний снимается по окончании полного периода срока практически одновременно с формированием 1 на выходе Об блока 35. По этой команде счетчикЗЗ пикселей возвращается исходное состояние, обеспечивая безусловный переход на нулевой адрес микропрограммы блока 35, а в счетчик 34 числа строк записывается первая 1. Затем начинается цикл вывода

из блока 1 графической информации для пикселей 2-й строки, который заканчивается повторным включением в работу формирователя 36 и увеличением на единицу содержимого счетчика 34. Вывод информации для пикселей третьей и последующих строк осуществляется аналогичным образом.

По завершению вывода на экран всего информационного кадра, равного, например, 2 строк, формирователь 36 организует кадровый синхроимпульс и гасящий импульс напряжения на время обратного вертикального хода луча. Этот режим работы блока 3 заканчивается формированием на

выходе Оз блока 36 сигнала, соответствующего 1, по которому производится обнуление счетчика 34 и полный переход на нулевой адрес микрограммы блока 36. После этого блок 3 начинает формирование

следующего информационного кадра.

Вывод на экран дисплея новой графической информации осуществляется посредством модификации содержимого соответствующих ячеек видеопамяти блока

1. Этот режим работы устройства поясняется на примерах построения одноцветной линии произвольного характера и какой-либо замкнутой геометрической фигуры с разноцветным составом пикселей. Все остальные

возможные варианты заполнения экрана новыми графическими данными могут рассматриваться как их частные случаи и реализуются аналогичным образом.

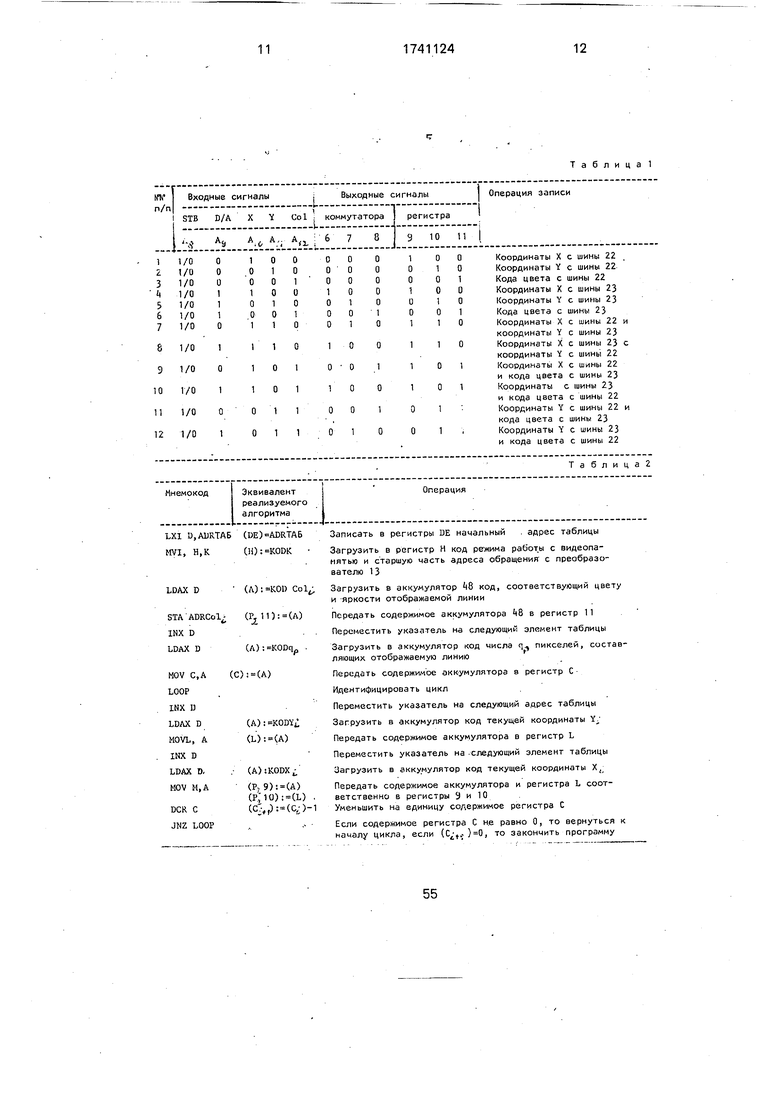

Схема алгоритма работы ЭВМ 4 при построении произвольной линии одного цвета приведена на фиг.7а. Согласно данному алгоритму предусматривает передачу по шине 22 данных кодов координаты X, а младшим

разрядам шины 23 адреса - кодов координаты Y с предварительным считыванием их из ОЗУ 45 в регистр общего назначения L. Последовательность операций, выполняемых микропроцессором 44 для реализации алгоритма фиг.7а, указана в табл.2.

После запуска программы микропроцессор получает на регистровую пару DE код начального адреса таблицы с данными для построения линии, а на регистр Н - старшую часть адреса обращения к преоб- разователю 13 (разряды Ais, Ai4 и Aia) и код режима работы с видеопамятью (разряды Ai2,...,A8), выбранный в соответствии с табл.1 (для варианта передачи кода координаты X по шине 22, а координаты Y- по шине 23 с записью информации в блок 1 он равен 10110).

Последующие данные для построения линии микропроцессор 44 получает из ОЗУ 45, каждый раз считывая в аккумулятор 48 содержимое ячеек его памяти. Адреса этих ячеек определяются регистровой парой DF, текущее значение кода которых увеличивается на единицу после каждого обращения к ОЗУ 45.

Содержимое первого элемента табл.2, соответствующее коду цвета линии, переписывается в регистр 11, а содержимое второго элемента с указанием количества точек построения - в регистр С. На его базе орга- низуется программный счетчик циклов.

Содержимое регистров 11 и Н в процессе построения линии остается неизменным.

Дальнейшая работа программы связана с непосредственной засветкой на экране дисплея точек построения линии и организована в виде серии циклов, каждый из которых предусматривает чтение на регистр и аккумулятор 48 двух очередных элементов исходной таблицы, содержащих коды текущих координат Yj и Xj отображаемой точки, их пересылку одной командой (с косвенной адресацией через регистровую пару HL) соответственно в регистры 10 и 9, декремен- тирование счетчика циклов (регистра С) и в случае нулевого значения переход к выполнению нового цикла.

Вывод информации из ЭВМ 4 сопровождается формированием на ее выходе управления записью сигнала, соответствующего, например, 1. Он поступает на вторые входы элементов И 14 - 16 и далее на входы перезаписи тех регистров 9 - 11, которые задействованы в работу преобразо- вателем 13 кодов. Одновременно сигнал управления записью адресуется на первый вход элемента И 21. Если в преобразователь 13 по разряду As адресной шины 23 поступает 1 (табл.1), то этот элемент И открыт и сигнал разрешения записи транслируется в блок 3 видеоизменения состояние его схемы следующим образом:

- триггер 37 переключается в единичное состояние;

-если в этот момент времени на выходе 0.5 блока 35 сформирован сигнал высокого уровня, разрешающий бесконфликтную запись новой информации в блок 1 видеопамяти (интервал времени t2 - te на диаграмме фиг.5), то элемент И 39 находится в открытом состоянии и триггер 37 передает сигнал разрешения записи в триггер 38, а сам возвращается в исходное состояние;

-если же с выхода Об блока 35 поступает сигнал низкого уровня (О), то элемент И 39 закрыт (интервал времени te -1 на диаграмме фиг.5), и запись новой информации в блок 1 откладывается до снятия сигнала запрета на этом выходе блока 35;

-после переключения триггера 38 в единичное состояние открывается элемент И 40, подсоединяя суммирующий вход счетчика 41 к выходу генератора 32 тактовых импульсов;

-счетчик 41 считывает содержимое ПЗУ 42, обеспечивая при этом формирование трех импульсных команд в последовательности, указанной на диаграмме фиг.6;

-первая команда с выхода Q.2 поступает на управляющий вход дешифратора 12, вследствие чего на одном из его выходов, определяемом содержанием младших разрядов АО - AI кода координаты Х|, устанавливается сигнал низкого уровня;

-последний адресуется на первый вход соответствующего элемента И 17 - 20 и закрывает его, передавая сигнал низкого уровня на один из входов выбора кристаллов блока 1, например, CS;

-вторая команда, формируемая на выходе СИ ПЗУ 42, поступает на вход W/R блока 1 и является сигналом для записи в накопители 24-1 ,...,27-1 информации, хранящейся в регистре 11, причем адрес битов, в которые она заносится, определяется кодом координат Xj, YI;

-по третьей команде, возбуждаемой ПЗУ 42, счетчик 41 и триггер 38 возвращаются в исходное состояние.

Передний фронт сигнала задержки записи, формируемый на выходе Qs блока 35, опережает сигнал CS на время, достаточное для реализации диаграммы по фиг.6. Поэтому, если триггер 38 переводится в единичное состояние в конце интервала ta -16, то счетчик 41 и ПЗУ 42 успевают выполнить операцию записи до переключения коммутатора 5 на адресные выходы видеогенератора (фиг.5б).

Алгоритм построения какой-либо геометрической фигуры с разноцветным составом пикселей приведен на иг.7б. Он практически не отличается от рассмотренного выше. Построение ведется построчно и

в пределах каждой строки координата YI остается постоянной. Коды координаты Xi и цвета, относящиеся к отображаемой точке, считываются из ОЗУ 45 соответственно в регистр Е и аккумулятор 48, а затем одной командой переписываются в регистры 9 и 11 и далее в матричные накопители 24 - 27 блока 1. По завершении построения текущей строки в регистр 10 загружается новое значение координаты Y и цикл операций повторяется. Их полный перечень приведен в табл.3.

Таким образом, в предлагаемом устройстве эквивалентная информация выдается одной командой с полной загрузкой шин адреса и данных. За счет этого время ввода в видеопамять новой графической информации существенно сокращается при некотором упрощении программного обеспечения. Кроме того, за счет раздельной адресации по строкам и столбцам уменьшено адресное пространство процессора, по которому последний обращается к видеопамяти.

При использовании предлагаемого устройства улучшаются технические характеристики средств вычислительной техники создаются возможности более совершенных систем отображения информации без существенного усложнения их структуры.

Формула изобретения

Устройство для формирования видеосигнала, содержащее первый коммутатор, блок сдвиговых регистров, выходы которого являются выходами устройства, информационный вход соединен с выходом блока видеопамяти, блок регенерации изображений, первый выход которого соединен с входом управления чтением блока сдвиговых регистров, а второй выход - с информационными входами первой группы первого коммутатора, выходы которого подключены к адресным входам блока видеопамяти, о т личающееся тем что, с целью повышения быстродействия устройства, оно содержит с второго по четвертый коммутаторы, три регистра, дешифратор, преобразователь кодов и с первого по восьмой элементы И, первые информационные входы с второго по четвертый коммутаторов являются информационными входами устройства, первым адресным входом которого являются вторые информационные входы коммутаторов, вторым адресным входом - информационный вход преобразователя кодов, управляющим входом - управляющий вход преобразователя кодов, входом управления записью - первые входы с первого по

третий и восьмого элементов И, первый, второй и третий выходы преобразователя кодов соединены с управляющими входами соответственно с второго по четвертый коммутаторов, четвертый, пятый и шестой выходы преобразователя кодов соединены с вторыми входами соответственно первого, второго и третьего элементов И, а седьмой выход- с вторым входом восьмого элемента И, выход которого подключен к входу управления записью блока регенерации изображений, третий выход которого соединен с управляющим входом дешифратора, информационные входы которого соединены с первым и вторым выходами первого регистра, выходы группы которого и выходы второго регистра подключены к соответствующим информационным входам второй группы первого коммутатора, информационные входы первого, второго и третьего

регистров соединены с выходами соответственно второго, третьего и четвертого коммутаторов, а управляющие входы - с выходами соответственно первого, второго и третьего элементов И, выходы третьего регистра соединены с информационными входами блока видеопамяти, управляющий вход первого коммутатора и первые входы с четвертого по седьмой элементов И соединены с четвертым выходом блока регенерации изображений, вторые входы с четвертого по седьмой элементов И соединены с соответствующими выходами дешифратора, а выходы их - с соответствующими управляющими входами блока видеопамяти, входупрввления чтением которого подключен к пятому выходу блока регенерации изображений, шестой выход которого соединен с входом управления сдвигом блока сдвиговых регистров,

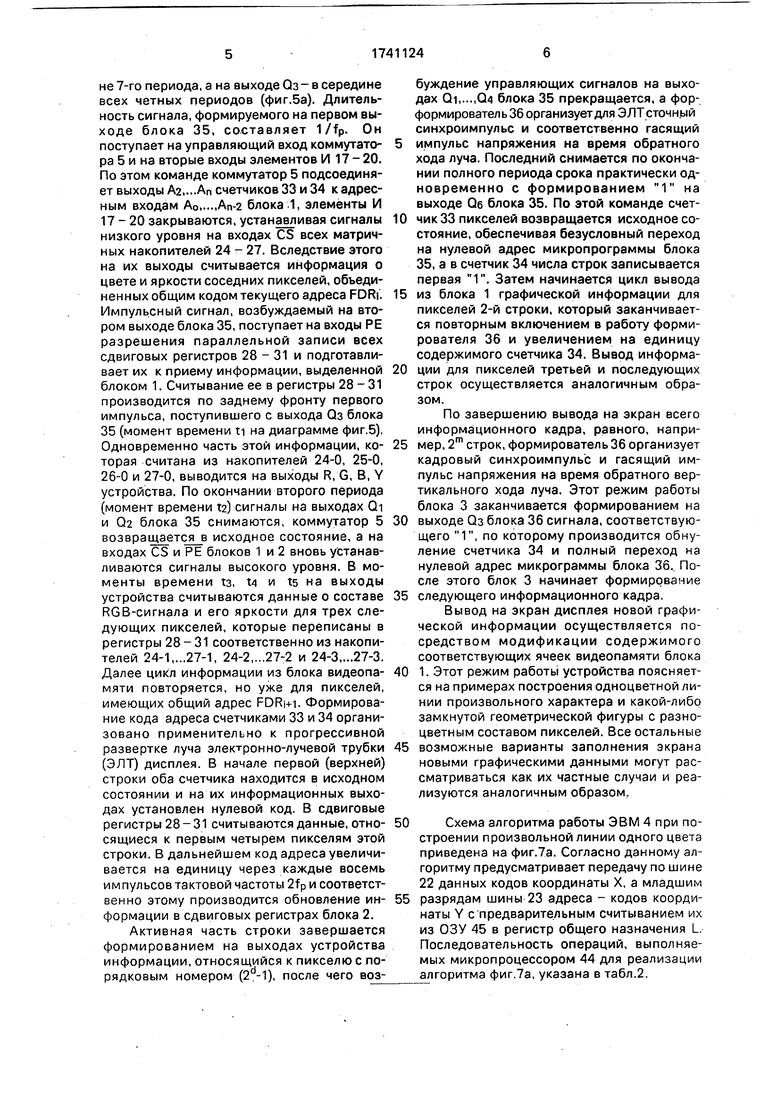

Таблица 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления считыванием и вводом информации | 1990 |

|

SU1751786A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1991 |

|

SU1807516A1 |

| Устройство для вывода графической информации | 1990 |

|

SU1833858A1 |

| Устройство для вывода графической информации | 1989 |

|

SU1698885A1 |

| Устройство для обработки и отображения видеоинформации | 1988 |

|

SU1748284A1 |

| Устройство для отображения информации на экране цветного телевизионного индикатора | 1985 |

|

SU1354243A1 |

| ТЕЛЕВИЗИОННАЯ СИСТЕМА ВЫСОКОГО РАЗРЕШЕНИЯ | 1996 |

|

RU2127961C1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1981 |

|

SU1275521A1 |

| Устройство для контроля печатных плат | 1986 |

|

SU1472929A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ АВТОНОМНЫМ РОБОТОМ | 2008 |

|

RU2424105C2 |

Изобретение относится к вычислительной технике и м.б. использовано в системах отображения графической информации. Устройство содержит блок 2 видеопамяти, блок сдвиговых регистров, блок регенерации изображений, коммутаторы 5 - 8, регистры 9-11, дешифратор 12, преобразователь 13 кодов, элементы И 14-21. 7 ил, 3 табл.

KTAB (DE)ADRTAB K(Н)

Col

P

(A) Col,

№jJ1): (A)

(A): KODqfl

(C)i(A)

(A): . L):(A)

(A)JKODX Ј

(P, 9): (A) (p;iO): (L) . (C%,): (C, )-1

Записать в регистры UE начальный адрес таблицы

Загрузить в регистр И код режима работы с видеопамятью и старшую часть адреса обращения с преобразователю 1 3

Загрузить в аккумулятор № код, соответствующий цвету и яркости отображаемой линии

Передать содержимое аккумулятора Й8 в регистр 11 Переместить указатель на следующий элемент таблицы

Загрузить в аккумулятор код числа q пикселей, составляющих отображаемую линию f

Передать содержимое аккумулятора в регистр С Идентифицировать цикл

Переместить указатель на следующий адрес таблицы Загрузить в аккумулятор код текущей координаты Y Передать содержимое аккумулятора в регистр L Переместить указатель на следующий элемент таблицы Загрузить в аккумулятор код текущей координаты X,

Передать содержимое аккумулятора и регистра L соответственно в регистры 9 и 10 Уменьшить на единицу содержимое регистра С

Сели содержимое регистра С не равно 0, то вернуться к началу цикла, если (.. , то закончить программу

ТаблицаЗ

если (Btt/)0 завершить программу

ЗП

Фиг. 3

ADK

CS W/J

FH

Си

периоды

, .г .з .4 .5.6 ,7 .8

qf 4

Qi Qz

% Q4

Z2

t

jaftp.

г/р

ЗП

l III//

t

ЛОЗР.

CL

i

WP.

Фиг. 5

Фиг. 6

А

а

Запуск программы

( TAB

{HJ. к

А

(A}: KODCoЈ(.

А

(Pi1t)(A)

А

(A) -KODQ

VP

А.

(С))

(,:

М:(А)

А.

(ft): KOUti

А.

(Ы): (А) (РгЮ)-. (Ь)

(ct-tJ.-)-f

KOW Лрог/эрммб/

ч1/

Запуск программы

А

А

(D)

А

(

(C)

А

(b KODYc

J,

(РгЮ).(Л)

(E)i

А

(A): ODCoftА

())

(Рг9).ГЈ;

А

()-fcJ-/

(6lv,).-(8t-j-/

нет

конец программы

| Многотерминальная система отображения информации | |||

| - Микропроцессорные средства и системы, 1986, № 3, рис,6 | |||

| с,49. |

Авторы

Даты

1992-06-15—Публикация

1990-03-06—Подача