Изобретение относится к автоматике и вычислительной технике и может быть ис- польовано в устройствах отображения, когда требуется перемещать изображение на экране,преобразовывать видеоданные в заданном от процессора режиме и обмениваться информацией с процессором.

Цель изобретения - повышение быстродействия и расширение области его применения за счет возможности представления изображения в окнах экрана путем перемещения изображения в любом направлении - программно-изменяемой скоростью.

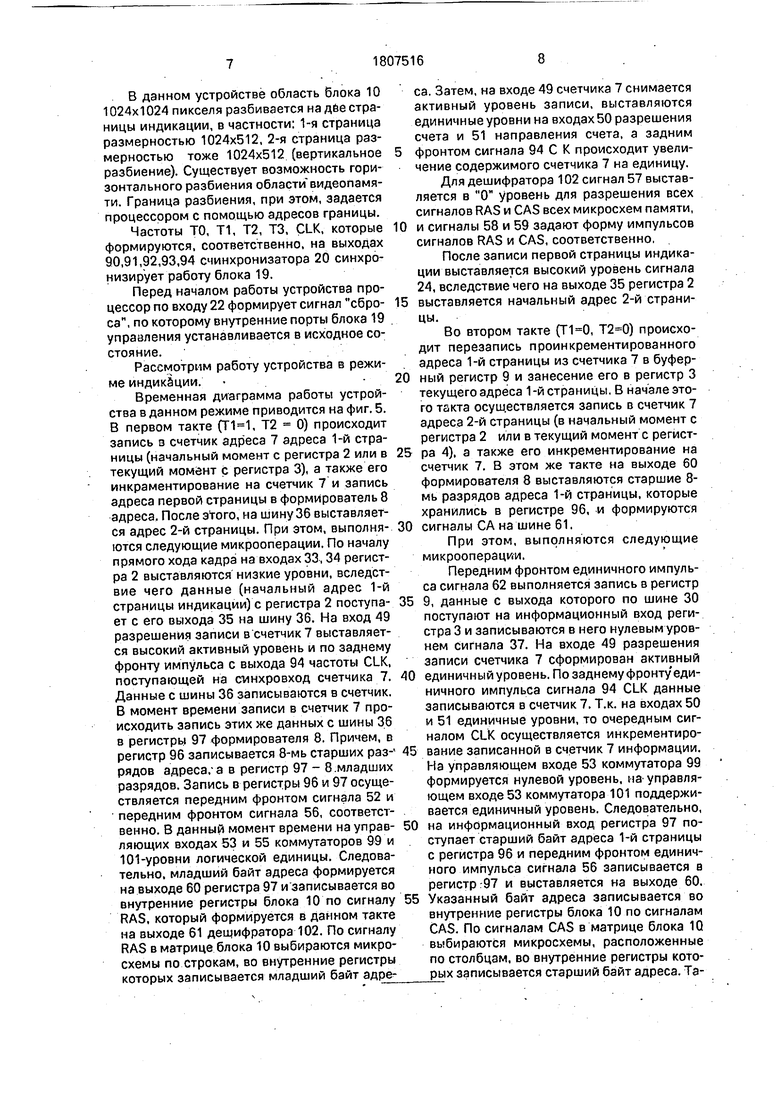

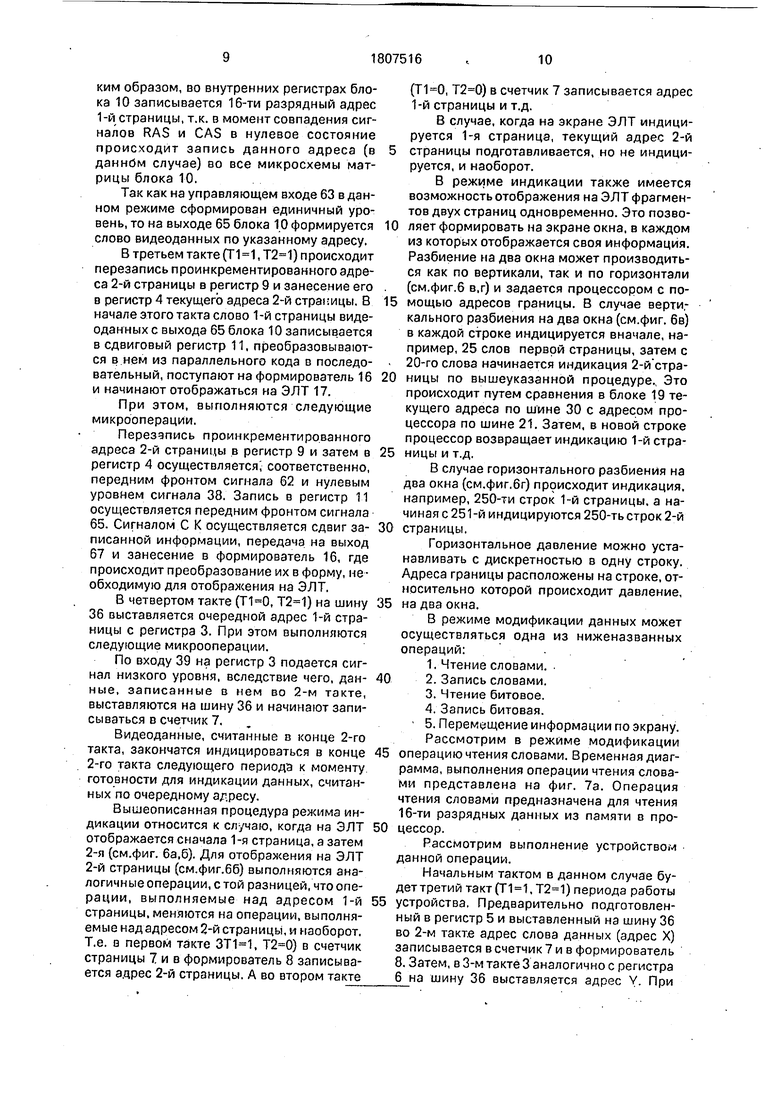

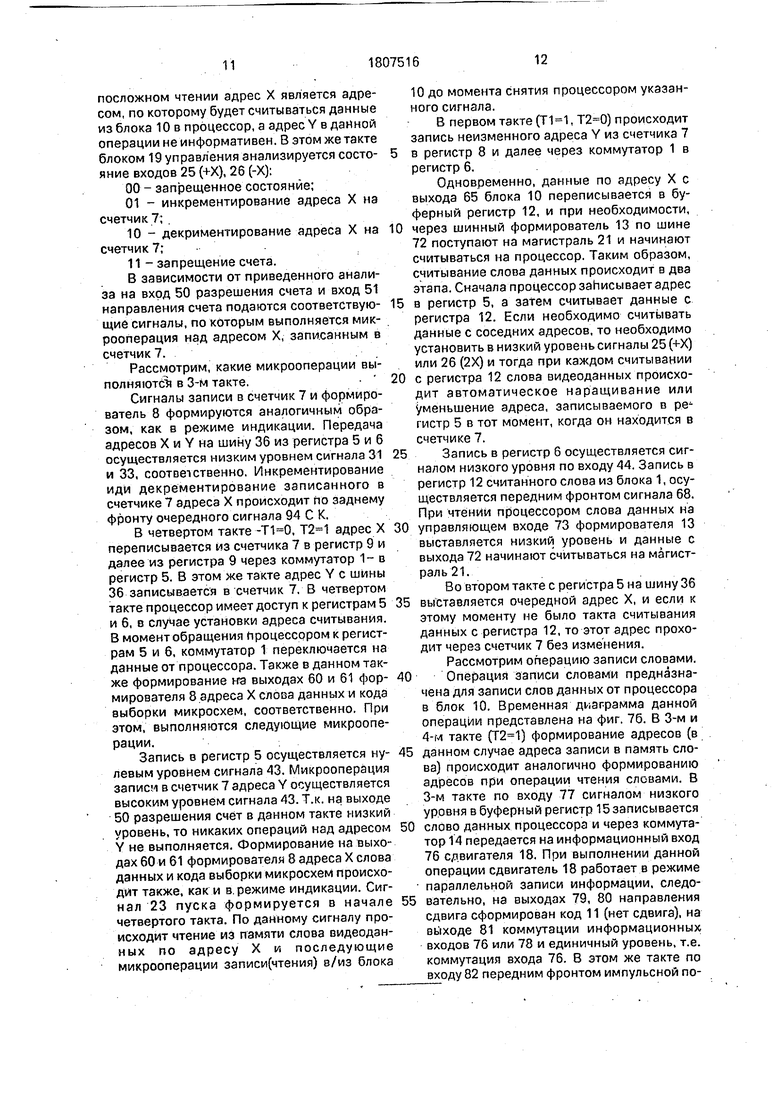

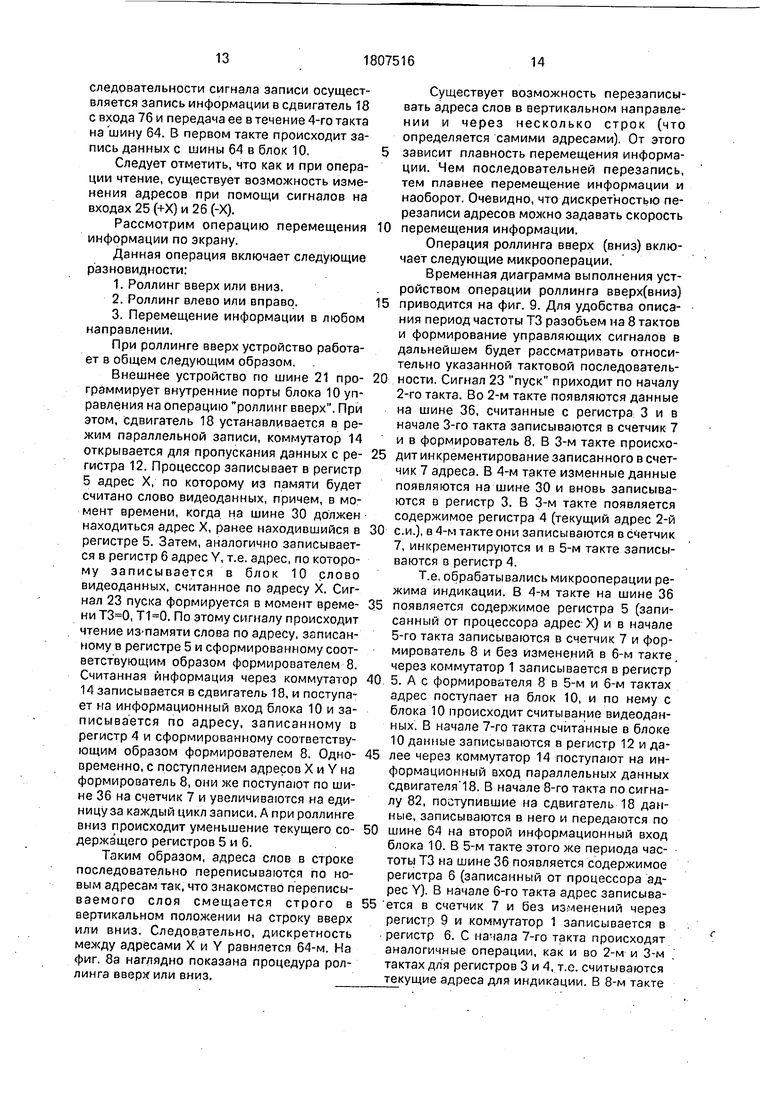

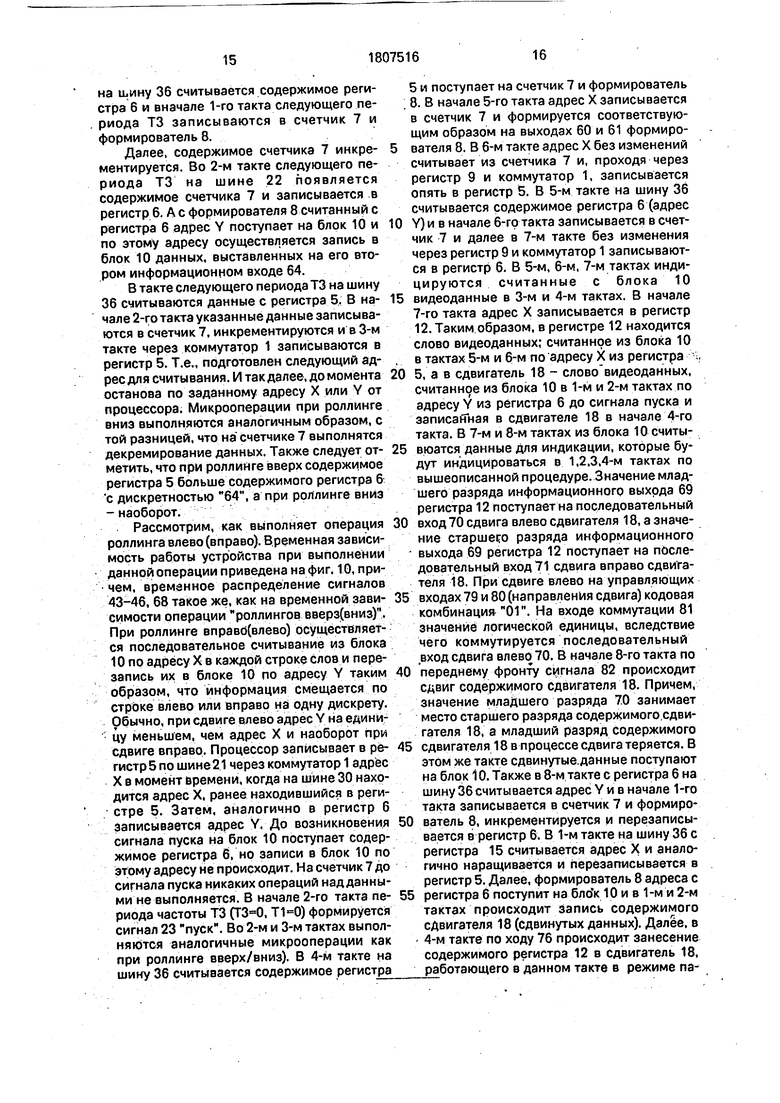

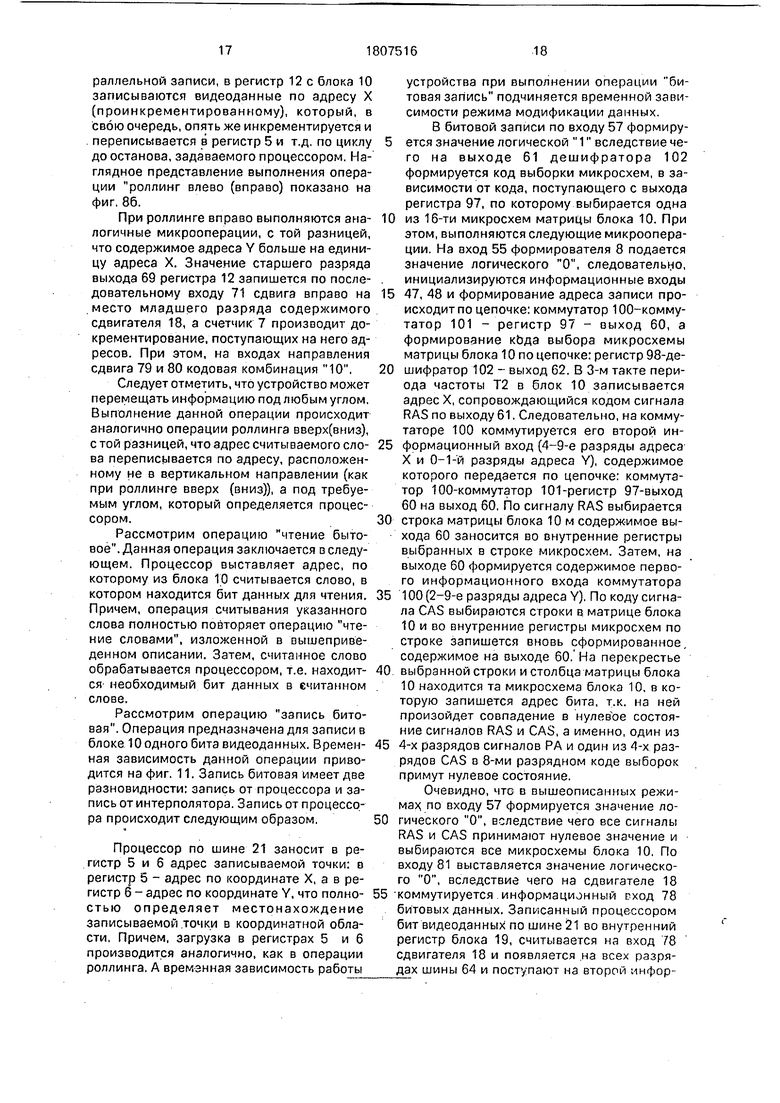

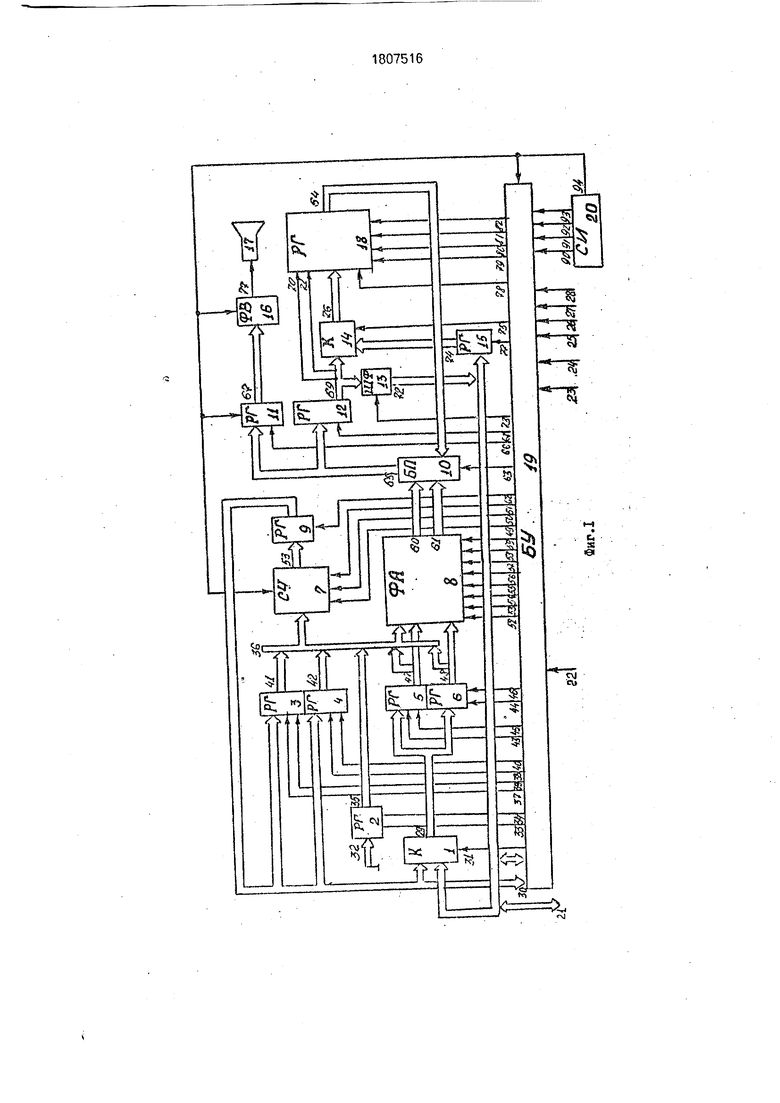

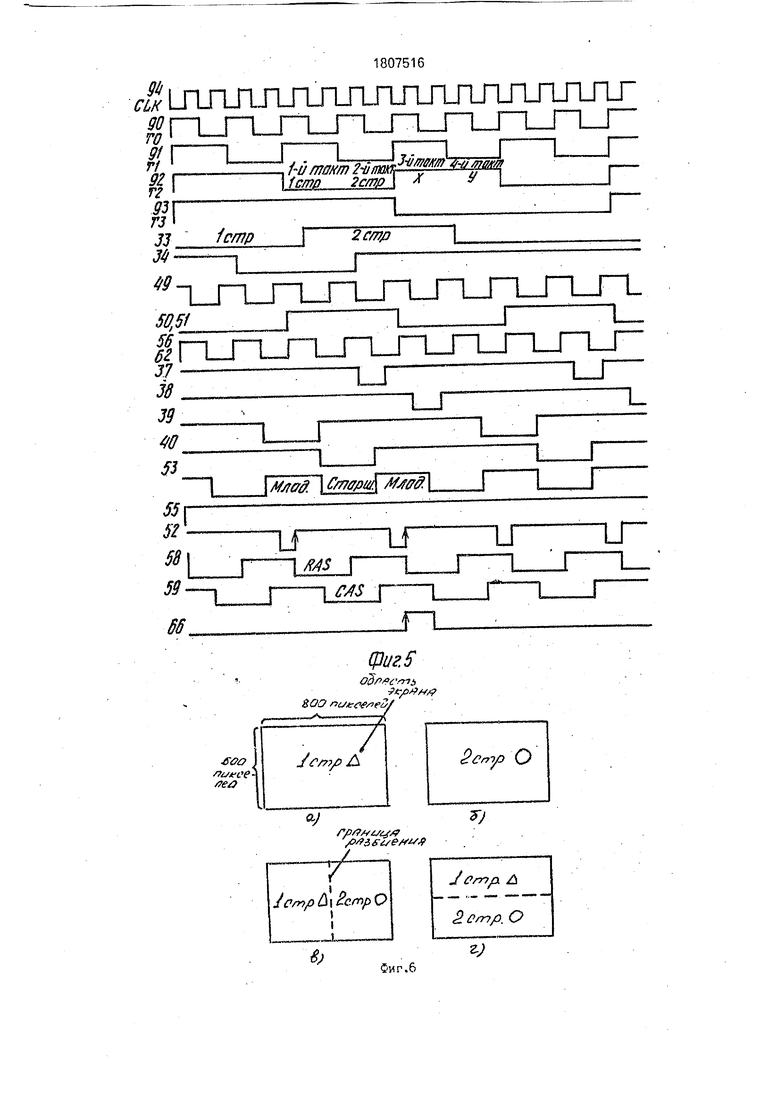

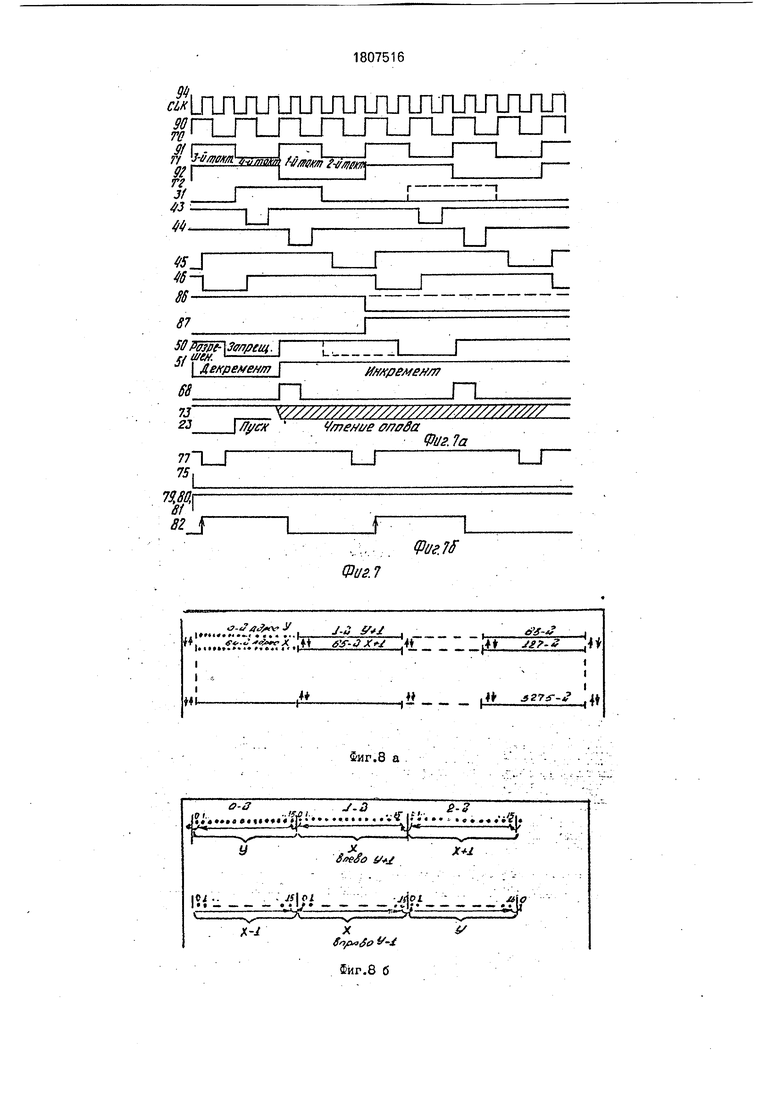

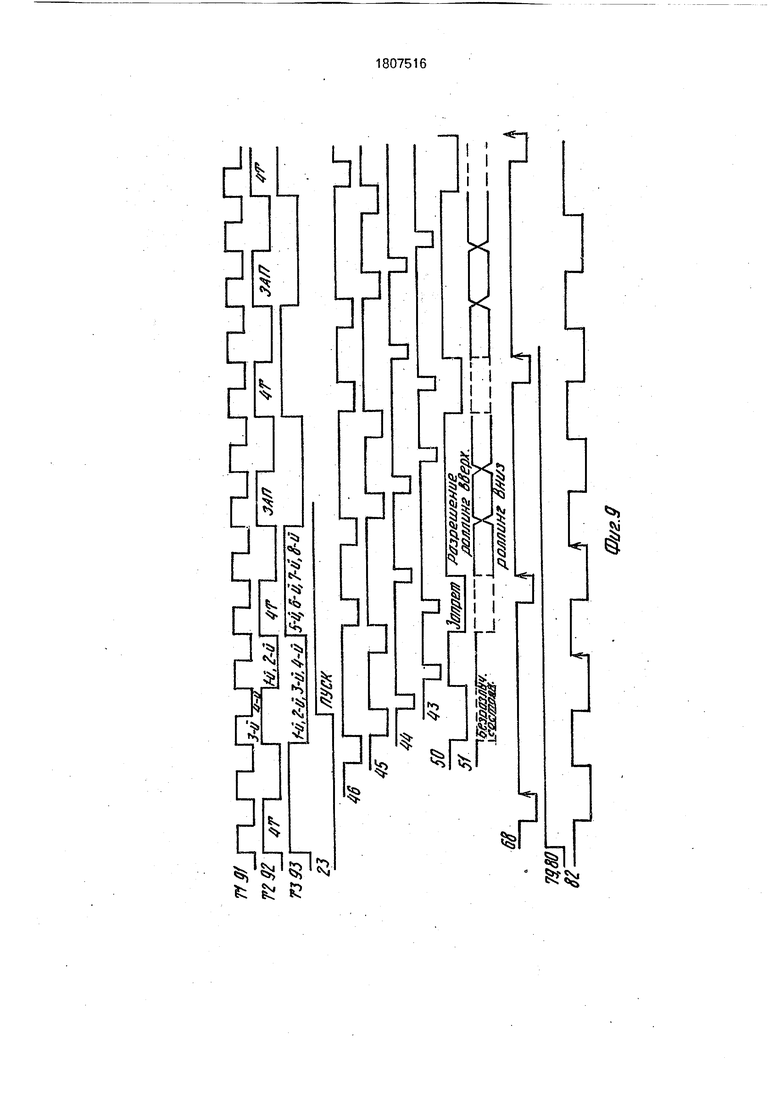

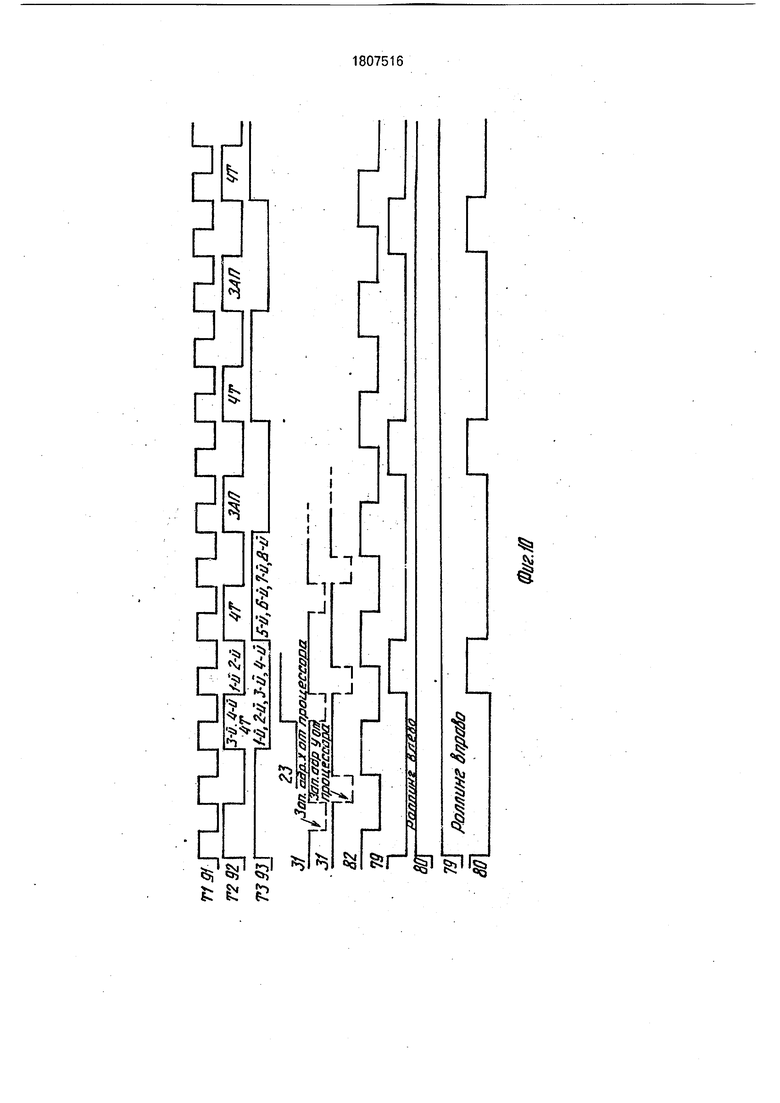

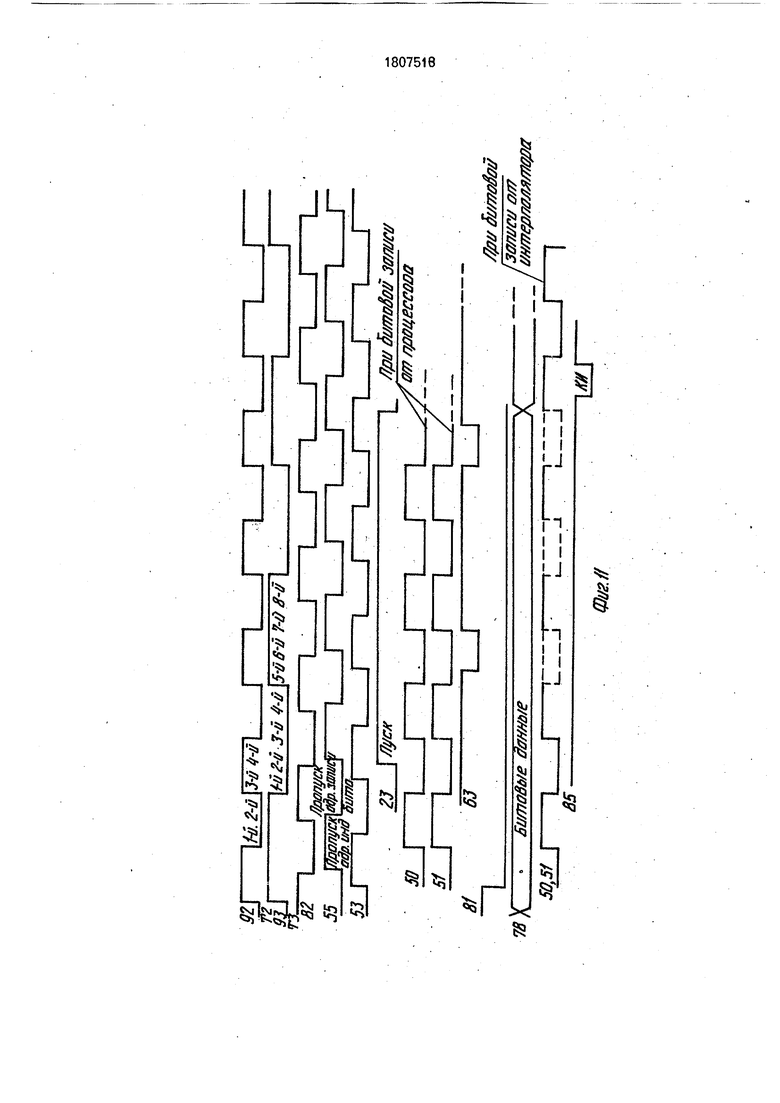

На фиг. 1 приведена структурная схема устройства; на фиг. 2 - функциональная схема формирователя адреса; на фиг. 3 - временная диаграмма работы устройства, на которой показаны основные операции над видеоданными, выполняемые устройством в каждом такте; на фиг. 4 - область координатного пространства видеопамяти: на фиг. 5 - временная диаграмма работы устройства режима индикации; на фиг. 6 - возможные варианты постраничного отображения на экране видеоинформации; на фиг. 7а - временная диаграмма работы устройства при выполнении операции чтение словами ; на фиг. 76 - записи словами ; на фиг. j 8а - выполнение операции роллинг вверх | з (вниз); на фиг, 86 - роллинг влево (вправо) j в области экрана; на фиг. 9 - временная С/) диаграмма работы устройства при выполне- f нии операции роллинг вверх (вниз); на фиг.. 10-временная диаграмма работыустройст- 3 ва при выполнении операции роллинг вле- во(вправо); на фиг. 11 - временная ; диаграмма работы устройства при выпол- нении операции битовая запись ; на фиг. 00 12 - функциональная схема дешифратора формирователя адреса; на фиг. 13 -функци- xj опальная схема регистра сдвига; на фиг. (г 14 - сдвигателя.; л Устройство содержит-первый коммута- л. тор 1, регистр 2 начального адреса, первый 3 и второй 4 регистры текущего адреса (пер- вой и второй страниц индикации), первый 5 и второй 6 регистры адреса модификации - (соответственно, координат X и Y), счетчик 7 : адреса, формирователь 8 адреса, первый буферный регистр 9, блок 10 памяти, регистр 11 сдвига, второй буферный регистр 12, шинный формирователь 13, второй коммутатор 14, третий буферный регистр 15, формирователь 16 видеосигнала, электронно-лучевую трубку (ЭЛТ) 17, сдвигатель 18, блок 19 управления и синхронизатор 20.

Следующими позициями обозначены: 21 - вход/выход, 22 - вход импульса сброса, 23-вход импульса пуска, 24-вход сигнала конца интерполяции, 25-28 - входами импульсов интерполяции +Х,-Х, +Y.-Y устройства, 29-31 - связи соответствующих блоков, 32 - информационный вход устройства, 33-35 - связи соответствующих бло- ков; 36 - первая информационная шина, 37-94 - связи соответствующих блоков, 95 .- вторая информационная шина устройства.

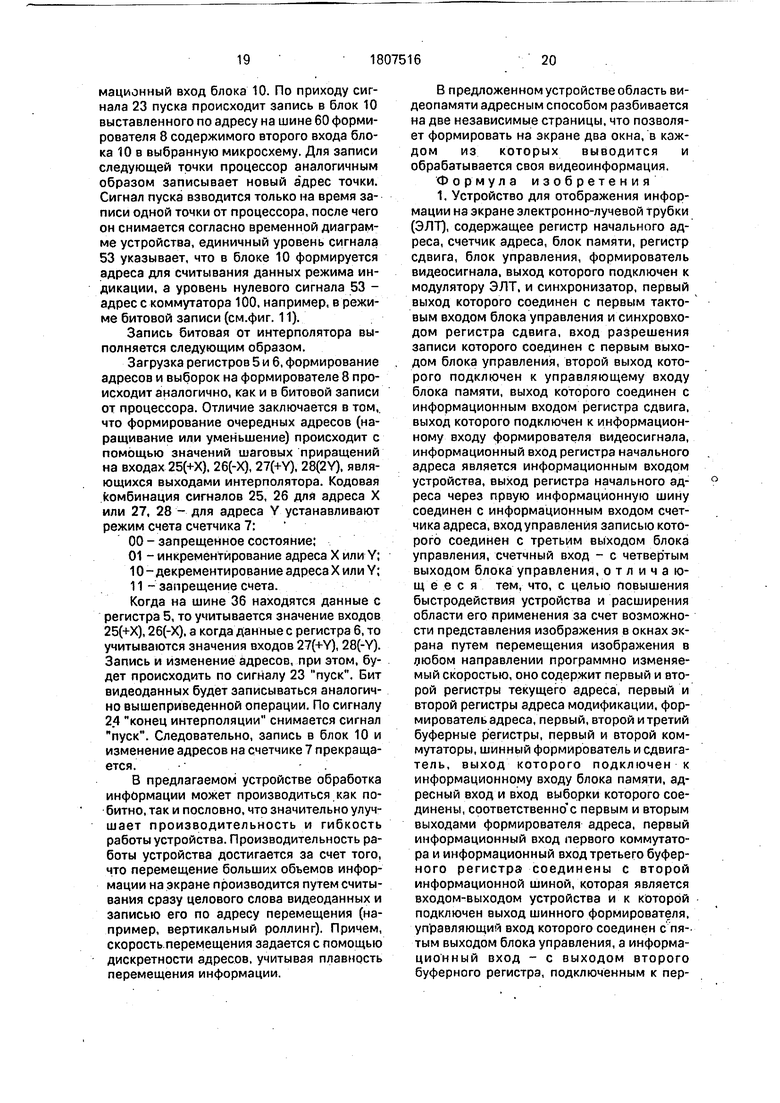

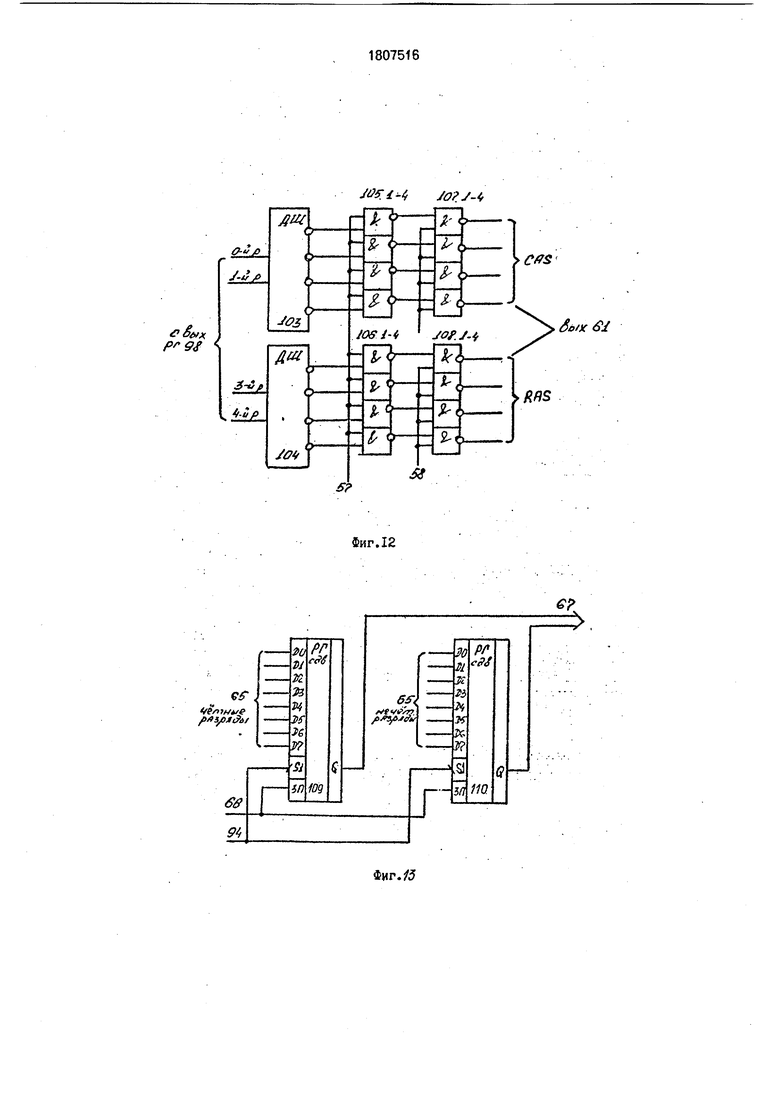

Формирователь 8 адреса содержит с первого по третий регистры 96, 97 и 98 с первого по третий коммутаторы 99,100,101 и дешифратор 102 (адреса).

Регистры 96-98 служат для временного хранения кодов формируемых адресов.

Инфбрмационный вход 36 соединен следующим образом: с 8-15-й - разряды соединены с информационным входом регистра 96, с 0-7-й - разряды - с информационным входом коммутатора 99.

Информационные входы 47 и 48 соеди- йены следующим образом: с 2-9-й разряды входа 47 - в общую шину и к второму информационному входу коммутатора 100, а с 6- 3-й разряды - с информационным входом регистра 98,

Дешифратор 102 состоит из дешифраторов 103 и 104 (два в четыре) и групп элементов 105-108 2И-НЕ, 0-й и 1-й, 3-й и 4-й разряды адресной шины (выход 61) определяет выборку сигналов RA и СА соответст- венно, в режиме битовой записи.

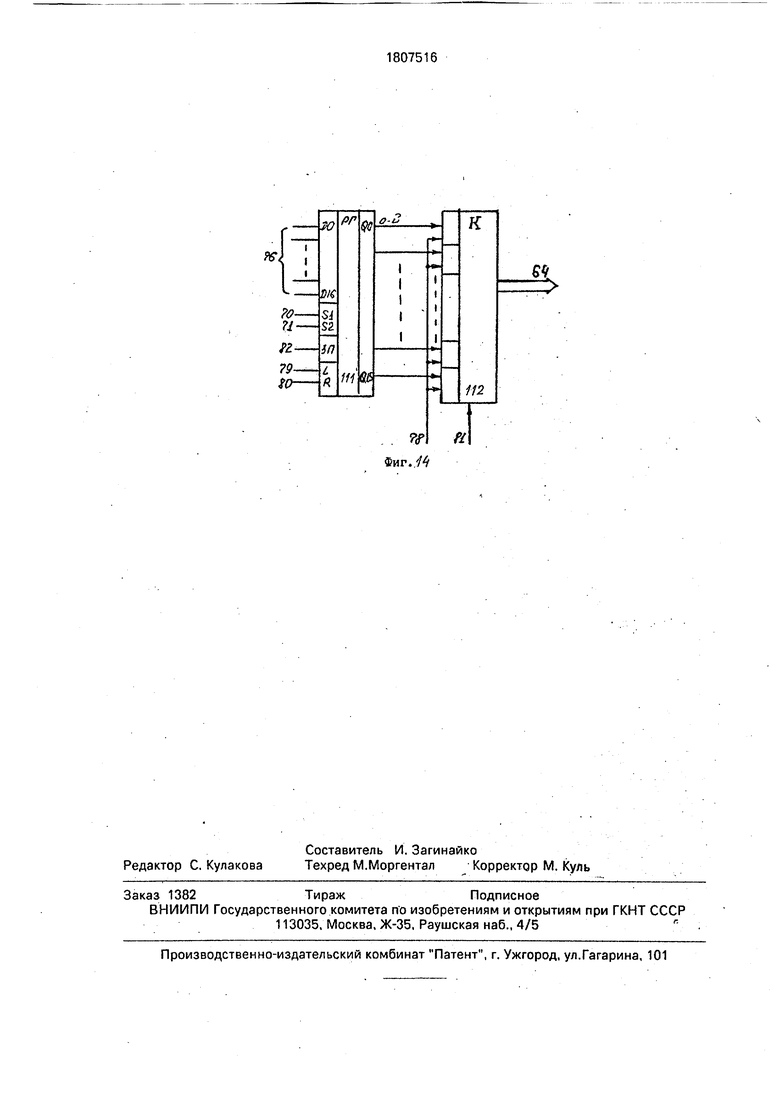

Регистр 11 сдвига состоит из регистров сдвига 109 и 110, что позволяет за период работы устройства последовательно сдвинуть 16-ть разрядов1 слова видеоданных, за- писанных в виде параллельного кода в регистре 110.

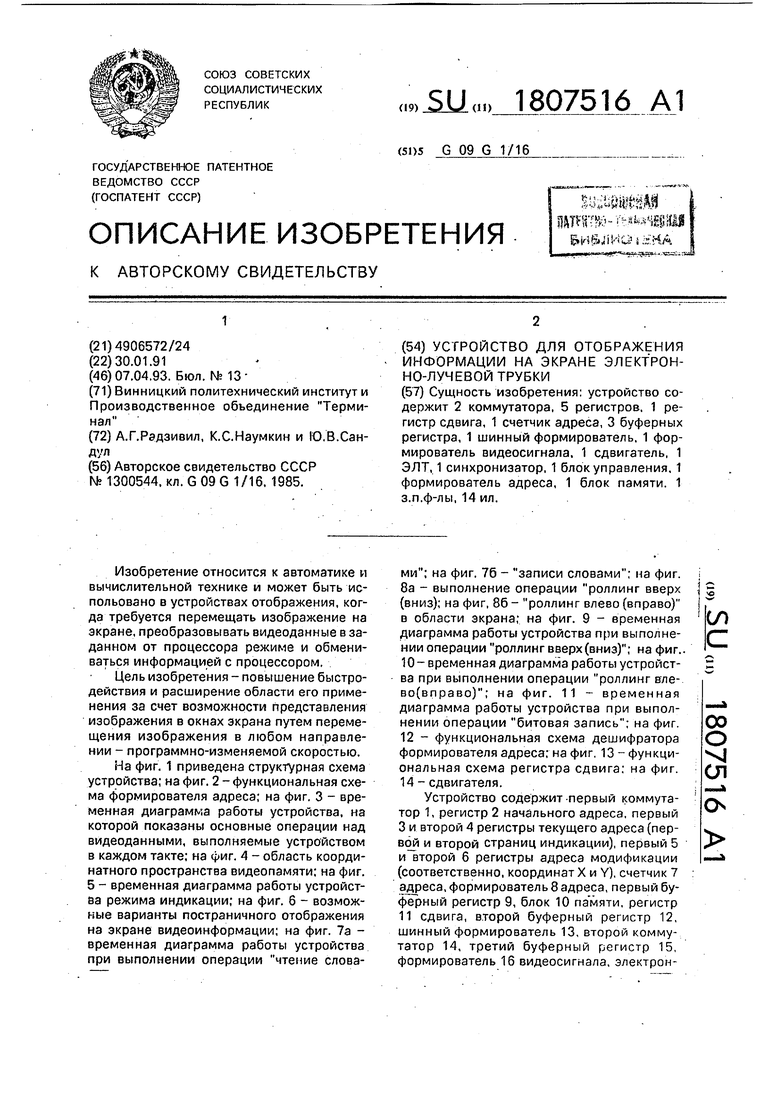

Сдвигатель 18 состоит из сдвигового регистра 111 и коммутатора 112.

Блок 19 управления может быть синте- зирован различным образом и представлен в виде временных диаграмм, полностью отражающих все управляющие сигналы, выра- ботанные блоком.

Для определенности описания работы устройства будет производиться для случая 16-ти разрядных адресных операндов и 16- ти разрядных слоев видеоданных, что определяет разрядности функциональных блоков и информационных шин устройства в нижеприведенном описании,

Коммутатор 1 обеспечивает передачу информации на выход 29 с одного из его информационных входов, один из которых соединен с входом/выходом 30, а другой с входом/выходом 21 устройства, который служит для приема данных от процессора (на чертеже не показан).

Регистр 2 наяльного адреса служит для задания исходного адреса 1-й или 2-й страницы индикации. Младшие 15-ть разрядов информационного входа 32 соединены с выходом логического нуля, а вес старшего 16- го разряда задает адрес 1-й или 2-й страницы.

Выход 35 подключен к информационной шине 36.

Регистры 3 и 4 являются регистрами текущего адреса 1-й и 2-й страницы индикации, соответственно, и служат для хранения текущих адресов 1-й и 2-й страницы индикации, соответственно (адресов 1-й и 2-й страницы видеопамяти).

Выходы 41 и 42 регистров соединены с информационной шиной 36.

Регистры 5 адреса (X) и регистр 6 адреса (Y) модификации служат для хранения 16-ти разрядных адресов, записанных в данные регистры от процессора или с входа 30.

Выход 47 регистра 5 соединен следующим образом: 16-ти разрядов с шиной 36, а 10-ть младших разрядов - с информационным входом формирователя 8. Выход 48 регистра 6 соединен: 16-ть разрядов - с шиной 36, а 10-ть младших - с информационным входом формирователя 8.

Регистры 2,3,4,5 являются регистрами с третьим состоянием, т.к. информационные выходы указанных регистров соединены с одной и той же 16-ти разрядной информаци-. онной шиной 36, которая также подключена к информационному входу счетчика 7. и 16- ти разрядному входу формирователя.

Счетчик 7 адреса предназначен:

1) для наращивания текущих адресов 1-й или 2-й страниц индикации, хранящихся, соответственно, в регистрах 3 и 4, а также в регистре 2;

2) для изменения адреса модификации, хранящихся в регистрах 5 и 6, путем декремента или инкремента, в зависимости от режима работы устройства.

Формирователь 8 адреса служит для формирования адресных операндов блока 10 памяти и соответствующих сигналов выборок матрицы памяти.

Буферный регистр 9 служит для временного хранения данных.

Блок 10 памяти служит для оперативного хранения видеоданных, с последующим отображением их на ЭЛТ по соответствующим адресам.

Блок 10 является ОЗУ динамического типа и представляет собой матрицу 4x4 микросхемы, охватывающая область памяти 1024x1024 бита.

8-ми разрядный вход выборки микросхем служит для приема кодов выборки с выхода 61 формирователя 8, и содержит 4-е разряда сигнала RA (сигналы выбора строк) и 4-е разряда сигнала СА (сигналы выбора столбцов). С помощью указанных сигналов происходит выбор микросхемы матрицы памяти для адресации, записи или чтения видеоданных.

Регистр 1.1 сдвига служит для преобразования параллельного кода видеоданных в последовательный.

Буферный регистр 12 служит для вре- менного хранения видеоданных, считанных из блока 10.

Шинный формирователь 13 служит для выдачи данных из регистра 12 на информа- ционную магистраль 21, а также для перево- да выхода 72 в в.ысокоимпедансное состояние, когда происходит запись данных от процессора в регистр 15.

Буферный регистр 15 служит для временного хранения кода видеоданных, запи- санных от процессора.

Формирователь 16 видеосигнала служит для преобразования последовательного цифрового кода видеоданных в аналоговые сигналы с последующим ото- бражением на ЭЛТ.

Сдвигатель 18 служит для:

1) хранения и передачи информации, считываемой с коммутатора 14 и с информационного входа 78,битовых данных;

2) для сдвига слов данных на один разряд в режиме горизонтального роллинга.

Блок 19 управления служит для выборки управляющих сигналов, в зависимости от режима работы устройства.

Информационный вход/выход блока соединен с информационной магистралью 21 и служит для приема управляющих кодов от процессора, по которым происходит программирование внутренних портов блока на соответствующий режим, а также для выдачи управляющих кодов процессору для контроля работы блока управления.

Синхронизатор 20 импульсов предназначен для выборки тактовых частот ТО-Т4, соответственно, по .п рвому-пятому выходам 90-94, необходимых для временной синхронизации блока

Устройство работает следующим обра- 55

зом.

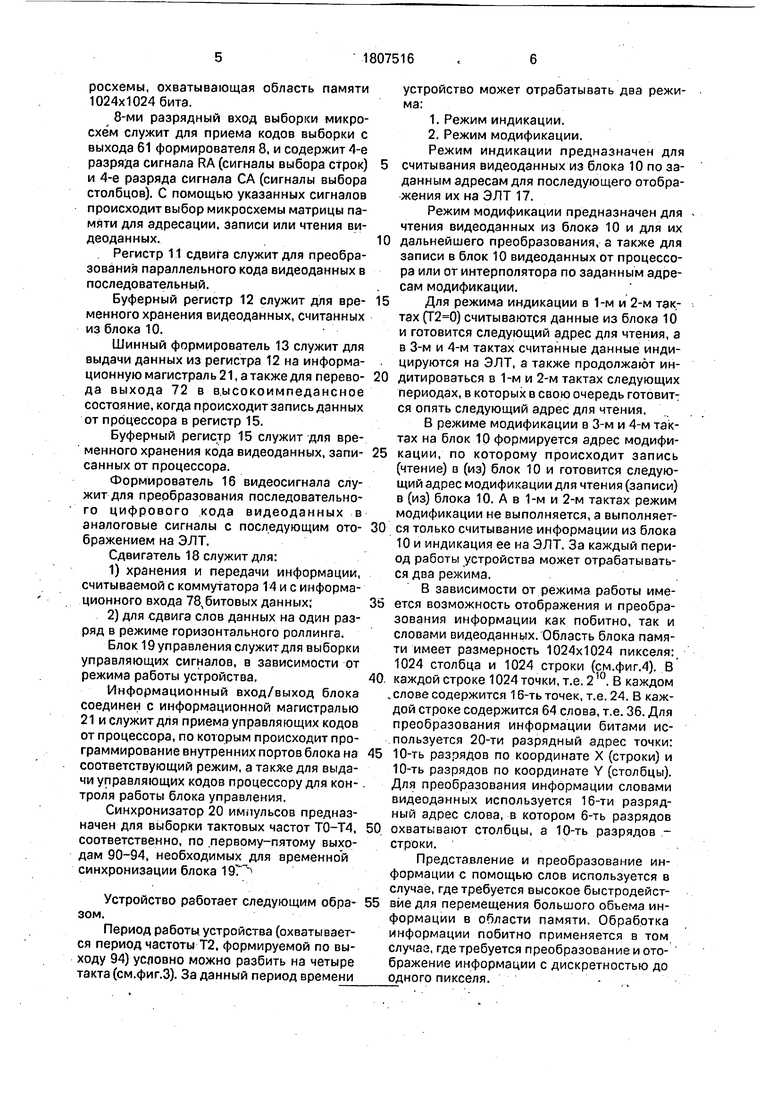

Период работы, устройства (охватывается период частоты Т2, формируемой по выходу 94) условно можно разбить на четыре такта (см.фиг.З). За данный период времени

устройство может отрабатывать два режима:

1. Режим индикации.

2. Режим модификации.

Режим индикации предназначен для считывания видеоданных из блока 10 по заданным адресам для последующего отображения их на ЭЛТ 17.

Режим модификации предназначен для чтения видеоданных из блока 10 и для их дальнейшего преобразования, а также для записи в блок 10 видеоданных от процессора или от интерполятора по заданным адресам модификации.

Для режима индикации в 1-м и 2-м тактах ) считываются данные из блока 10 и готовится следующий адрес для чтения, а в 3-м и 4-м тактах считанные данные индицируются на ЭЛТ, а также продолжают ин- дитироваться в 1-м и 2-м тактах следующих периодах, в которых в свою очередь готовит: ся опять следующий адрес для чтения.

В режиме модификации в 3-м и 4-м тактах на блок 10 формируется адрес модификации, по которому происходит запись (чтение) в (из) блок 10 и готовится следующий адрес модификации для чтения (записи) в (из) блока 10. А в 1-м и 2-м тактах режим модификации не выполняется, а выполняется только считывание информации из блока 10 и индикация ее на ЭЛТ. За каждый период работы устройства может отрабатываться два режима..

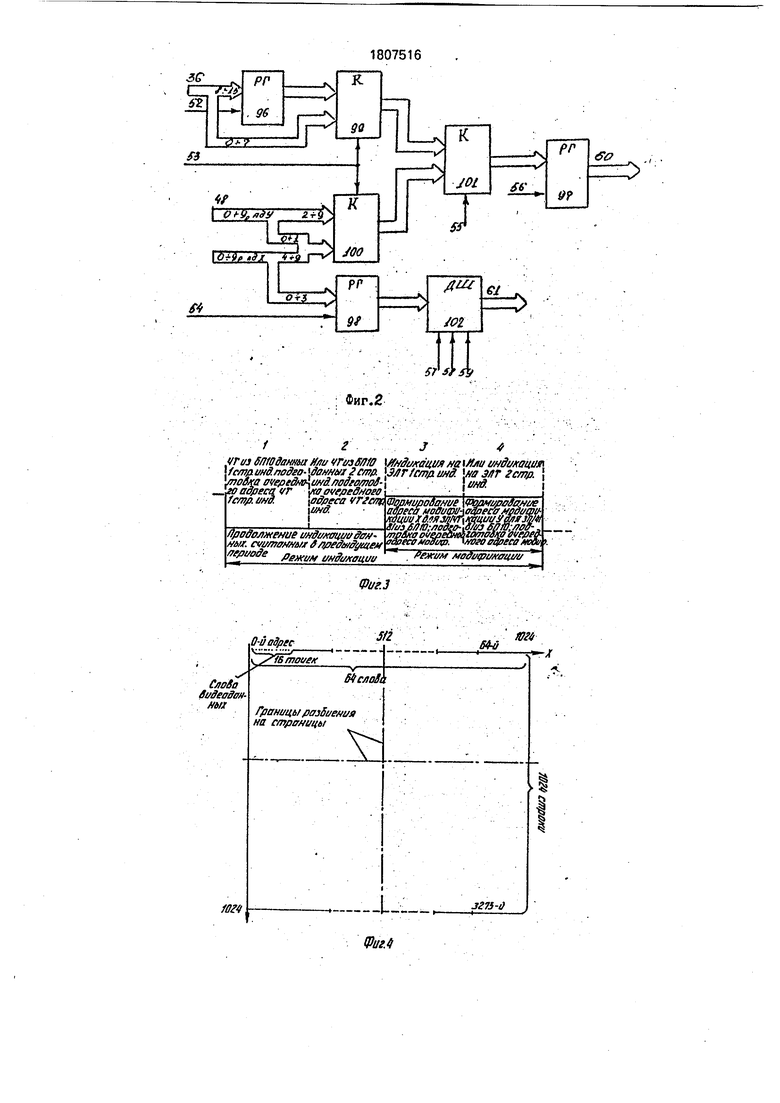

В зависимости от режима работы имеется возможность отображения и преобразования информации как побитно, так и словами видеоданных. Область блока памяти имеет размерность 1024x1024 пикселя: 1024 столбца и 1024 строки (см.фиг.4). В каждой строке 1024 точки, т.е. 210. В каждом .словесодержится 16-тьточек, т.е. 24. В каждой строке содержится 64 слова, т.е. 36. Для преобразования информации битами ис- .пользуется 20-ти разрядный адрес точки: 10-ть разрядов по координате X (строки) и 10-ть разрядов по координате Y (столбцы). Для преобразования информации словами видеоданных используется 16-ти разрядный адрес слова, в котором 6-ть разрядов охватывают столбцы, а 10-ть разрядов - строки.

Представление и преобразование информации с помощью слов используется в случае, где требуется высокое быстродействие для перемещения большого объема информации в области памяти. Обработка информации побитно применяется в том случае, где требуется преобразование и ото- бражение информации с дискретностью до одного пикселя..

В данном устройстве область блока 10 1024x1024 пикселя разбивается на две страницы индикации, в частности: 1-я страница размерностью 1024x512, 2-я страница размерностью тоже 1024x512 (вертикальное разбиение). Существует возможность горизонтального разбиения области видеопамяти. Граница разбиения, при этом, задается процессором с помощью адресов границы.

Частоты ТО, Т1, Т2, ТЗ, CLK, которые формируются, соответственно, на выходах 90,91,92,93,94 счинхронизатора 20 синхронизирует работу блока 19.

Перед началом работы устройства процессор по входу 22 формирует сигнал сброса, по которому внутренние порты блока 19 управления устанавливается в исходное состояние.

Рассмотрим работу устройства в режиме индикации.

Временная диаграмма работы устройства в данном режиме приводится на фиг. 5. В первом такте (, Т2 0) происходит запись з счетчик адреса 7 адреса 1-й страницы (начальный момент с регистра 2 или в текущий момент с регистра 3), а также его инкраментирование на счетчик 7 и запись адреса первой страницы в формирователь 8 адреса, После этого, на шину 36 выставляется адрес 2-й страницы. При этом, выполняются следующие микрооперации. По началу прямого хода кадра на входах 33,34 регистра 2 выставляются низкие уровни, вследствие чего данные (начальный адрес 1-й страницы индикации) с регистра 2 поступает с его выхода 35 на шину 36. На вход 49 разрешения записи в счетчик 7 выставляется высокий активный уровень и по заднему фронту импульса с выхода 94 частоты CLK, поступающей на синхровход счетчика 7. Данные с шины 36 записываются в счетчик. В момент времени записи в счетчик 7 происходить запись этих же данных с шины 36 в регистры 97 формирователя 8. Причем, в регистр 96 записывается 8-мь старших раз- рядов адреса,-а в регистр 97 - 8.младших разрядов. Запись в регистры 96 и 97 осуществляется передним фронтом сигнала 52 и передним фронтом сигнала 56, соответственно. В данный момент времени на управляющих входах 53 и 55 коммутаторов 99 и 101-уровни логической единицы. Следовательно, младший байт адреса формируется на выходе 60 регистра 97 и записывается во внутренние регистры блока 10 по сигналу RAS, который формируется в данном такте на выходе 61 дешифратора 102. По сигналу RAS в матрице блока 10 выбираются микросхемы по строкам, во внутренние регистры которых записывается младший байт адреса. Затем, на входе 49 счетчика 7 снимается активный уровень записи, выставляются единичные уровни на входах 50 разрешения счета и 51 направления счета, а задним

фронтом сигнала 94 С К происходит увеличение содержимого счетчика 7 на единицу. Для дешифратора 102 сигнал 57 выставляется в О уровень для разрешения всех сигналов RAS и CAS всех микросхем памяти,

0 и сигналы 58 и 59 задают форму импульсов сигналов RAS и CAS, соответственно,

После записи первой страницы индикации выставляется высокий уровень сигнала 24, вследствие чего на выходе 35 регистра 2

5 выставляется начальный адрес 2-й страницы.

Во втором такте (, ) происходит перезапись проинкрементированного адреса 1-й страницы из счетчика 7 в буфер0 ный регистр 9 и занесение его в регистр 3 текущего адреса 1-й страницы. В начале этого такта осуществляется запись в счетчик 7 адреса 2-й страницы (в начальный момент с регистра 2 или в текущий момент с регист5 ра 4), а также его инкрементирование на счетчик 7. В этом же такте на выходе 60 формирователя 8 выставляются старшие 8- мь разрядов адреса 1-й страницы, которые хранились в регистре 96, и формируются

0 сигналы СА на шине 61.

При этом, выполняются следующие микрооперации.

Передним фронтом единичного импульса сигнала 62 выполняется запись в регистр

5 9, данные с выхода которого по шине 30 поступают на информационный вход регистра 3 и записываются в него нулевым уровнем сигнала 37. На входе 49 разрешения записи счетчика 7 сформирован активный

0 единичный уровень. По заднему фронту единичного импульса сигнала 94 CLK данные записываются в счетчик 7. Т.к. на входах 50 и 51 единичные уровни, то очередным сигналом CLK осуществляется инкрементиро5 вание записанной в счетчик 7 информации. На управляющем входе 53 коммутатора 99 формируется нулевой уровень, на управляющем входе 53 коммутатора 101 поддерживается единичный уровень. Следовательно,

0 на информационный вход регистра 97 поступает старший байт адреса 1-й страницы с регистра 96 и передним фронтом единичного импульса сигнала 56 записывается в регистр:97 и выставляется на выходе 60.

5 Указанный байт адреса записывается во внутренние регистры блока 10 по сигналам CAS. По сигналам CAS в матрице блока 10 выбираются микросхемы, расположенные по столбцам, во внутренние регистры кото- рых записывается старший байт адреса. Таким образом, во внутренних регистрах блока 10 записывается 16-ти разрядный адрес 1-й страницы, т.к. в момент совпадения сигналов RAS и CAS в нулевое состояние происходит запись данного адреса (в данном случае) во все микросхемы матрицы блока 10.

Так как на управляющем входе 63 в данном режиме сформирован единичный уровень, то на выходе 65 блока 10 формируется слово видеоданных по указанному адресу.

В третьем такте (, ) происходит перезапись проинкрементированного адреса 2-й страницы в регистр 9 и занесение его в регистр 4 текущего адреса 2-й страницы. В начале этого такта слово 1-й страницы видеоданных с выхода 65 блока 10 записывается в сдвиговый регистр 11, преобразовываются в нем из параллельного кода в последовательный, поступают на формирователь 16 и начинают отображаться на ЭЛТ 17.

При этом, выполняются следующие микрооперации.

Перезапись проинкрементированного адреса 2-й страницы в регистр 9 и затем в регистр 4 осуществляется; соответственно, передним фронтом сигнала 62 и нулевым уровнем сигнала 38. Запись в регистр 11 осуществляется передним фронтом сигнала 65. Сигналом С К осуществляется сдвиг записанной информации, передача на выход 67 и занесение в формирователь 16, где происходит преобразование их в форму, необходимую для отображения на ЭЛТ.

В четвертом такте (, ) на шину 36 выставляется очередной адрес 1-й страницы с регистра 3. При этом выполняются следующие микрооперации.

По входу 39 на регистр 3 подается сигнал низкого уровня, вследствие чего, данные, записанные в нем во 2-м такте, выставляются на шину 36 и начинают записываться в счетчик 7.

Видеоданные, считанные в конце 2-го такта, закончатся индицироваться в конце 2-го такта следующего периода к моменту, готовности для индикации данных, считанных по очередному адресу.

Вышеописанная процедура режима индикации относится к случаю, когда на ЭЛТ отображается сначала 1-я страница, а затем 2-я (см.фиг. ба.б). Для отображения на ЭЛТ 2-й страницы (см.фиг.бб) выполняются аналогичные операции, с той разницей, что операции, выполняемые над адресом 1-й страницы, меняются на операции, выполняемые над адресом 2-й страницы, и наоборот. Т.е. в первом такте , ) в счетчик страницы 7 и в формирователь 8 записывается адрес 2-й страницы. А во втором такте

(, ) в счетчик 7 записывается адрес 1-й страницы и т.д.

В случае, когда на экране ЭЛТ индицируется 1-я страница, текущий адрес 2-й 5 страницы подготавливается, но не индицируется, и наоборот.

В режиме индикации также имеется возможность отображения на ЭЛТ фрагментов двух страниц одновременно. Это позво0 ляет формировать на экране окна, в каждом из которых отображается своя информация. Разбиение на два окна может производиться как по вертикали, так и по горизонтали (см.фиг.6 в.г) и задается процессором с по5 мощью адресов границы. В случае вертикального разбиения на два окна (см.фиг. 6в) в каждой строке индицируется вначале, например, 25 слов первой страницы, затем с . 20-го слова начинается индикация 2-й стра0 ницы по вышеуказанной процедуре., Это происходит путем сравнения в блоке 19 текущего адреса по шине 30 с адресом процессора по шине 21. Затем, в новой строке процессор возвращает индикацию 1-й стра5 ницы и т.д.

В случае горизонтального разбиения на два окна (см.фиг.бг) происходит индикация, например, 250-ти строк 1-й страницы, а начиная с 251 -и индицируются 250-ть строк 2-й

0 страницы.

Горизонтальное давление можно устанавливать с дискретностью в одну строку. Адреса границы расположены на строке, относительно которой происходит давление,

5 на два окна.

В режиме модификации данных может осуществляться одна из ниженазванных операций: 1. Чтение словами. .

0 2. Запись словами.

3. Чтение битовое.

4. Запись битовая.

5. Перемощение информации по экрану. Рассмотрим в режиме модификации 5 операцию чтения словами. Временная диаграмма, выполнения операции чтения словами представлена на фиг. 7а. Операция чтения словами предназначена для чтения 16-ти разрядных данных из памяти в про- 0 цессор.

Рассмотрим выполнение устройством данной операции.

Начальным тактом в данном случае будет третий такт(,) периода работы 5 устройства. Предварительно подготовленный в регистр 5 и выставленный на шину 36 во 2-м такте адрес слова данных (адрес X) записывается в счетчик 7 и в формирователь 8. Затем, в 3-м такте 3 аналогично с регистра 6 на шину 36 выставляется адрес Y- При

посложном чтении адрес X является адресом, по которому будет считываться данные из блока 10 в процессор, а адрес Y в данной операции не информативен. В этом же такте блоком 19 управления анализируется состояние входов 25 (+Х), 26 (-Х):

00 - запрещенное состояние;

01 - инкрементировзние адреса X на счетчик 7;

10 - декриментирование адреса X на счетчик 7;

11 - запрещение счета.

В зависимости от приведенного анализа на вход 50 разрешения счета и вход 51 направления счета подаются соответствующие сигналы, по которым выполняется микрооперация над адресом X, записанным в счетчик.

Рассмотрим, какие микрооперации выполняются в 3-м такте.

Сигналы записи в счетчик 7 и формирователь 8 формируются аналогичным образом, как в режиме индикации. Передача адресов X и Y на шину 36 из регистра 5 и 6 осуществляется низким уровнем сигнала 31 и 33, соответственно. Инкрементирование иди декрементирование записанного в счетчике 7 адреса X происходит по заднему фронту очередного сигнала 94 С К.

В четвертом такте , адрес X переписывается из счетчика 7 в регистр 9 и далее из регистра 9 через коммутатор 1- в регистр 5. В этом же такте адрес Y с шины 36 записывается в счетчик 7, В четвертом такте процессор имеет доступ к регистрам 5 и 6, в случае установки адреса считывания. В момент обращения процессором к регистрам 5 и 6, коммутатор 1 переключается на данные от процессора. Также в данном также формирование нз выходах 60 и 61 формирователя 8 адреса X слова данных и кода выборки микросхем, соответственно. При этом, выполняются следующие микрооперации.

Запись в регистр 5 осуществляется нулевым уровнем сигнала 43. Микрооперация записи в счетчик 7 адреса Y осуществляется высоким уровнем сигнала 43. Т.к. на выходе 50 разрешения счет в данном такте низкий уровень, то никаких операций над адресом Y не выполняется. Формирование на выходах 60 и 61 формирователя 8 адреса X слова данных и кода выборки микросхем происходит также, как и в. режиме индикации. Сигнал 23 пуска формируется в начале четвертого такта. По данному сигналу происходит чтение из памяти слова видеодан- ных по адресу X и последующие микрооперации записи(чтения) в/из блока

10 до момента снятия процессором указанного сигнала.

В первом такте (, ) происходит запись неизменного адреса Y из счетчика 7

в регистр 8 и далее через коммутатор 1 в регистр 6.

Одновременно, данные по адресу X с выхода 65 блока 10 переписывается в буферный регистр 12, и при необходимости,

0 через шинный формирователь 13 по шине 72 поступают на магистраль 21 и начинают считываться на процессор. Таким образом, считывание слова данных происходит в два этапа. Сначала процессор записывает адрес

5 в регистр 5, а затем считывает данные с регистра 12. Если необходимо считывать данные с соседних адресов, то необходимо установить в низкий уровень сигналы 25 (+Х) или 26 (2Х) и тогда при каждом считывании

0 с регистра 12 слова видеоданных происходит автоматическое наращивание или уменьшение адреса, записываемого в регистр 5 в тот момент, когда он находится в счетчике 7.

5 Запись в регистр 6 осуществляется сигналом низкого уровня по входу 44. Запись в регистр 12 считанного слова из блока 1, осуществляется передним фронтом сигнала 68. При чтении процессором слова данных на

0 управляющем входе 73 формирователя 13 выставляется низкий уровень и данные с выхода 72 начинают считываться на магистраль 21.

Во втором такте с регистра 5 на шину 36

5 выставляется очередной адрес X, и если к этому моменту не было такта считывания данных с регистра 12, то этот адрес проходит через счетчик 7 без изменения.

Рассмотрим операцию записи словами.

0 Операция записи словами предназначена для записи слов данных от процессора в блок 10. Временная диаграмма данной операции представлена на фиг. 76. В 3-м и 4-м такте () формирование адресов (в

5 данном случае адреса записи в память слова) происходит аналогично формированию адресов при операции чтения словами. В 3-м такте по входу 77 сигналом низкого уровня в буферный регистр 15 записывается

0 слово данных процессора и через коммутатор 14 передается на информационный вход 76 сдвигателя 18. При выполнении данной операции сдвигатель 18 работает в режиме параллельной записи информации, следо5 вательно, на выходах 79, 80 направления сдвига сформирован код 11 (нет сдвига), на выходе 81 коммутации информационных входов 76 или 78 и единичный уровень, т.е. коммутация входа 76. В этом же такте по входу 82 передним фронтом импульсной последовательности сигнала записи осуществляется запись информации в сдвигатель 18 с входа 76 и передача ее в течение 4-го такта на шину 64. В первом такте происходит запись данных с шины 64 в блок 10.

Следует отметить, что как и при операции чтение, существует возможность изменения адресов при помощи сигналов на входах 25 (+Х) и 26 (-Х).

Рассмотрим операцию перемещения информации по экрану.

Данная операция включает следующие разновидности:

1. Роллинг вверх или вниз.

2. Роллинг влево или вправо.

3. Перемещение информации в любом направлении.

При роллинге вверх устройство работает в общем следующим образом.

Внешнее устройство по шине 21 программирует внутренние порты блока 10 управления на операцию роллинг вверх. При этом, сдвигатель 18 устанавливается в режим параллельной записи, коммутатор 14 открывается для пропускания данных с регистра 12. Процессор записывает в регистр 5 адрес X, по которому из памяти будет считано слово видеоданных, причем, в момент времени, когда, на шине 30 должен находиться адрес X, ранее находившийся в регистре 5. Затем, аналогично записывается в регистр 6 адрес Y, т.е. адрес, по которому записывается в блок 10 слово видеоданных, считанное по адресу X. Сигнал 23 пуска формируется в момент времени , . По этому сигналу происходит чтение из-памяти слова по адресу, записанному в регистре 5 и сформированному соответствующим образом формирователем 8. Считанная информация через коммутатор 14 записывается в сдвигатель 18, и поступает на информационный вход блока 10 и записывается по адресу, записанному в регистр 4 и сформированному соответствующим образом формирователем 8. Одновременно, с поступлением адресов X и Y на формирователь 8, они же поступают по шине 36 на счетчик 7 и увеличиваются на единицу за каждый цикл записи. А при роллинге вниз происходит уменьшение текущего содержащего регистров 5 и 6.

Таким образом, адреса слов в строке последовательно переписываются по новым адресам так, что знакомство переписы- ваемого слоя смещается строго в вертикальном положении на строку вверх или вниз. Следовательно, дискретность между адресами X и Y равняется 64-м. На фиг. 8а наглядно показана процедура рол- линга вверя или вниз.

Существует возможность перезаписывать адреса слов в вертикальном направлении и через несколько строк (что определяется самими адресами). От этого 5 зависит плавность перемещения информации. Чем последовательней перезапись, тем плавнее перемещение информации и наоборот. Очевидно, что дискретностью перезаписи адресов можно задавать скорость 0 перемещения информации.

Операция роллинга вверх (вниз) включает следующие микрооперации.

Временная диаграмма выполнения устройством операции роллинга вверх(вниз)

5 приводится на фиг. 9. Для удобства описания период частоты ТЗ разобьем на 8 тактов и формирование управляющих сигналов в дальнейшем будет рассматривать относительно указанной тактовой последователь0 ности. Сигнал 23 пуск приходит по началу 2-го такта. Во 2-м такте появляются данные на шине 36, считанные с регистра 3 и в начале 3-го такта записываются в счетчик 7 и в формирователь 8. В 3-м такте происхо5 дит инкрементирование записанного в счетчик 7 адреса. В 4-м такте изменные данные появляются на шине 30 и вновь записываются в регистр 3. В 3-м такте появляется содержимое регистра 4 (текущий адрес 2-й

0 с.и.), в 4-м такте они записываются в счетчик 7, инкрементируются и в 5-м такте записываются в регистр 4.

Т.е. обрабатывались микрооперации режима индикации. В 4-м такте на шине 36

5 появляется содержимое регистра 5 (записанный от процессора адрес X) и в начале 5-го такта записываются в счетчик 7 и формирователь 8 и без изменений в б-м такте, через коммутатор 1 записывается в регистр

0. 5. А с формирователя 8 в 5-м и 6-м тактах адрес поступает на блок 10, и по нему с блока 10 происходит считывание видеоданных. В начале 7-го такта считанные в блоке 10 данные записываются в регистр 12 и да5 лее через коммутатор 14 поступают на информационный вход параллельных данных сдвигателя 18. В начале 8-го такта по сигналу 82, поступившие на сдвигатель 18 данные, записываются в него и передаются по

0 шине 64 на второй информационный вход блока 10. В 5-м такте этого же периода частоты ТЗ на шине 36 появляется содержимое регистра 6 (записанный от процессора адрес Y). В начале 6-го такта адрес записыва5 ется в счетчик 7 и без изменений через регистр 9 и коммутатор 1 записывается в регистр 6. С начала 7-го такта происходят аналогичные операции, как и во 2-м и 3-м тактах для регистров 3 и 4, т.е. считываются текущие адреса для индикации. В 8-м такте

на 1ьину 36 считывается содержимое реги-5 и поступает на счетчик 7 и формирователь

стра 6 и вначале 1-го такта следующего пе-; 8. В начале 5-го такта адрес X записывается

риода ТЗ записываются в счетчик 7 ив счетчик 7 и формируется соответствуюформирователь 8.щим образом на выходах 60 и 61 формироДалее, содержимое счетчика 7 инкре-5 вателя 8. В 6-м такте адрес X без изменений

ментируется. Во 2-м такте следующего пе-считывает из счетчика 7 и, проходя через

риода ТЗ на шине 22 появляетсярегистр 9 и коммутатор 1, записывается

содержимое счетчика 7 и записывается вопять в регистр 5. В 5-м такте на шину 36

регистр 6. А с формирователя 8 считанный ссчитывается содержимое регистра 6 (адрес

регистра 6 адрес Y поступает на блок 10 и10 У)и в начале 6-го такта записывается в счетпо этому адресу осуществляется запись вчик 7 и далее в 7-м такте без изменения

блок 10 данных, выставленных на его вто-через регистр 9 и коммутатор 1 записываютром информационном входе 64.ся в регистр 6. В 5-м, 6-м, 7-м тактах индиВ такте следующего периода ТЗ на шинуцируются считанные с блока 10

36 считываются данные с регистра 5, В на-15 видеоданные в 3-м и 4-м тактах. В начале

чале 2-го такта указанные данные записыва-7-го такта адрес X записывается в регистр

ются в счетчик 7, инкрементируются ив 3-м12. Таким образом, в регистре 12 находится

такте через коммутатор 1 записываются вслово видеоданных; считанное из блока 10

регистр 5. Т.е., подготовлен следующий ад-, в тактах 5-м и 6-м по адресу X из регистра

рее для считывания. И так далее, до момента20 5, а в сдвигатель 18 - слово видеоданных,

останова по заданному адресу X или Y отсчитанное из блока 10 в 1-м и 2-м тактах по

процессора. Микрооперации при роллингеадресу Y из регистра 6 до сигнала пуска и

вниз выполняются аналогичным образом, сзаписайная в сдвигателе 18 в начале 4-го

той разницей, что на счетчике 7 выполнятсятакта. В 7-м и 8-м тактах из блока 10 считыдекремирование данных. Также следует от-25 вюатся данные Для индикации, которые буметить, что при роллинге вверх содержимоедут индицироваться в 1,2,3,4-м тактах по

регистра 5 больше содержимого регистра 6вышеописанной процедуре. Значение млад с дискретностью 64, а при роллинге внизшего разряда информационного выхода 69

-наоборот.регистра 12 поступает на последовательный

Рассмотрим, как выполняет операция30 вход 70 сдвига влево сдвигателя 18, а значероллинга влево (вправо). Временная зависи-ние старшего разряда информационного

мость работы устройства при выполнении- выхода 69 регистра 12 поступает на последанной операции приведена на фиг. 10, при-довательный вход 71 сдвига вправо сдвигачем, временное распределение сигналовтеля 18. При сдвиге влево на управляющих

43-46,68 такое же, как на временной зави-35 входах 79 и 80 (направления сдвига) кодовая

симости операции роплингов вверз(вниз).комбинация 01. На входе коммутации 81

При роллинге вправо(влево) осуществляет-значение логической единицы, вследствие

ся последовательное считывание из блокачего коммутируется последовательный

ЮпоадрёсуХ в каждой строке слов и пере-вход сдвига влево 70. В начале 8-го такта по

запись их в блоке 10 по адресу Y таким40 переднему фронту сигнала 82 происходит

образом, что информация смещается посдвиг содержимого сдвигателя 18. Причем,

строке влево или вправо на одну дискрету.значение младшего разряда 70 занимает

Обычно, при сдвиге влево адрес Y на едини-место старшего разряда содержимого.сдвицу меньшем, чем адрес X и наоборот пригателя 18, а младший разряд содержимого

сдвиге вправо. Процессор записывает в ре-45 сдвигателя 18 в процессе сдвига теряется. В

гистр 5 по шине 21 через коммутатор адресэтом же такте сдвинутые.данные поступают

X в момент времени, когда на шине 30 нахо-на блок 10. Также в 8-м такте с регистра 6 на

дится адрес X, ранее находившийся в реги-шину 36 считывается адрес Y и в начале 1-го

стре 5. Затем, аналогично в регистр 6такта записывается в счетчик 7 и формирозапиеывается адрес У. До возникновения50 ватель 8, инкрементируется и перезаписысигнала пуска на блок 10 поступает содер-вается в регистр 6. В 1-м такте на шину 36 с

жимое регистра 6, но записи в блок 10 порегистра 15 считывается адрес X и аналоэтому адресу не происходит. На счетчик 7 догично наращивается и перезаписывается в

сигнала пуска никаких операций над данны-регистр 5. Далее, формирователь 8 адреса с

ми не выполняется. В начале 2-го такта пе-55 регистра 6 поступит на бло к 10 и в 1-м и 2-м

риода частоты ТЗ (, ) формируетсятактах происходит запись содержимого

сигнал 23 пуск. Во 2-м и 3-м тактах выпол-сдвигателя 18 (сдвинутых данных). Далее, в

няются аналогичные микрооперации как4-м такте по ходу 76 происходит занесение

при роллинге вверх/вниз). В 4-м такте насодержимого регистра 12 в сдвигатель 18,

шину 36 считывается содержимое регистраработающего в данном такте в режиме параллельной записи, в регистр 12 с блока 10 записываются видеоданные по адресу X (проинкрементированному), который, в свою очередь, опять же инкрементируется и . переписывается в регистр 5 и т.д. по циклу до останова, задаваемого процессором. Наглядное представление выполнения операции роллинг влево (вправо) показано на фиг. 86.

При роллинге вправо выполняются аналогичные микрооперации, с той разницей, что содержимое адреса Y больше на единицу адреса X. Значение старшего разряда выхода 69 регистра 12 запишется по последовательному входу 71 сдвига вправо на место младшего разряда содержимого сдвигателя 18, а счетчик 7 производит до- крементирование, поступающих на него адресов. При этом, на входах направления сдвига 79 и 80 кодовая комбинация 10.

Следует отметить, что устройство может перемещать информацию под любым углом. Выполнение данной операции происходит аналогично операции роллинга вверх(вниз), с той разницей, что адрес считываемого слова переписывается по адресу, расположенному не в вертикальном направлении (как при роллинге вверх (вниз)), а под требуемым углом, который определяется процессором.

Рассмотрим операцию чтение бытовое. Данная операция заключается в следующем. Процессор выставляет адрес, по которому из блока ТО считывается слово, в котором находится бит данных для чтения. Причем, операция считывания указанного слова полностью повторяет операцию чтение словами, изложенной в вышеприведенном описании. Затем, считанное слово обрабатывается процессором, т.е. находится необходимый бит данных в считанном слове.

Рассмотрим операцию запись битовая. Операция предназначена для записи в блоке 10 одного бита видеоданных. Временная зависимость данной операции приводится на фиг. 11. Запись битовая имеет две разновидности: запись от процессора и запись от интерполятора. Запись от процессора происходит следующим образом.

Процессор по шине 21 заносит в регистр 5 и 6 адрес записываемой точки: в регистр 5 - адрес по координате X, а в регистр 6 - адрес по координате Y, что полностью определяет местонахождение записываемой .точки в координатной области. Причем, загрузка в регистрах 5 и 6 производится аналогично, как в операции роллинга. А временная зависимость работы

устройства при выполнении операции битовая запись подчиняется временной зависимости режима модификации данных.

В битовой записи по входу 57 формиру- 5 ется значение логической 1 вследствие чего на выходе 61 дешифратора 102 формируется код выборки микросхем, в зависимости от кода, поступающего с выхода регистра 97, по которому выбирается одна 0 из 16-ти микросхем матрицы блока 10. При этом, выполняются следующие микрооперации. На вход 55 формирователя 8 подается значение логического О, следовательно, инициализируются информационные входы 5 47, 48 и формирование адреса записи происходит по цепочке: коммутатор 100-комму- татор 101 - регистр 97 - выход 60, а формирование кода выбора микросхемы матрицы блока 10 по цепочке: регистр 98-де0 шифратор 102 - выход 62. В 3-м такте периода частоты Т2 в блок 10 записывается адрес X, сопровождающийся кодом сигнала RAS по выходу 61. Следовательно, на коммутаторе 100 коммутируется его второй ин5 формационный вход (4-9-е разряды адреса X и 0-1-и разряды адреса Y), содержимое которого передается по цепочке: коммутатор 100-коммутатор 101-регистр 97-выход 60 на выход 60. По сигналу RAS выбирается

0 строка матрицы блока 10 м содержимое выхода 60 заносится во внутренние регистры выбранных в строке микросхем. Затем, на выходе 60 формируется содержимое первого информационного входа коммутатора

5 100 (2-9-е разряды адреса Y). По коду сигнала CAS выбираются строки в матрице блока 10 и во внутренние регистры микросхем по строке запишется вновь сформированное, содержимое на выходе 60. На перекрестье

0. выбранной строки и столбца матрицы блока 10 находится та микросхема блока 10, в которую запишется адрес бита, т.к. на ней произойдет совпадение в нулевое состояние сигналов RAS и CAS, а именно, один из

5 4-х разрядов сигналов РА и один из 4-х разрядов CAS в 8-ми разрядном коде выборок примут нулевое состояние.

Очевидно, что в вышеописанных режимах, по входу 57 формируется значение ло0 гического О, вследствие чего все сигналы RAS и CAS принимают нулевое значение и выбираются все микросхемы блока 10. По входу 81 выставляется значение логического О, вследствие чего на сдвигателе 18

5 коммутируется информационный еход 78 битовых данных. Записанный процессором бит видеоданных по шине 21 во внутренний регистр блока 19, считывается на вход 78 сдвигателя 18 и появляется на всех разрядах шины 64 и поступают на второй информационный вход блока 10. По приходу сигнала 23 пуска происходит запись в блок 10 выставленного по адресу на шине 60 формирователя 8 содержимого второго входа блока 10 в выбранную микросхему. Для записи следующей точки процессор аналогичным образом записывает новый а дрес точки. Сигнал пуска взводится только на время записи одной точки от процессора, после чего он снимается согласно временной диаграмме устройства, единичный уровень сигнала 53 указывает, что в блоке 10 формируется адреса для считывания данных режима индикации, а уровень нулевого сигнала 53 - адрес с коммутатора 100, например, в режиме битовой записи (см.фиг. 11).

Запись битовая от интерполятора выполняется следующим образом.

Загрузка регистров 5 и 6, формирование адресов и выборок на формирователе 8 происходит аналогично, как и в битовой записи от процессора. Отличие заключается в том,, что формирование очередных адресов (наращивание или уменьшение) происходит с помощью значений шаговых приращений на входах 25(+Х). 2б(-Х), 27(+Y), 28(2Y), являющихся выходами интерполятора. Кодовая комбинация сигналов 25, 26 для адреса X или 27, 28 - для адреса Y устанавливают режим счета счетчика 7:

00 - запрещенное состояние;

01 - инкрементйрование адреса X или Y;

10 - декрементирование адреса X или Y;

11 - запрещение счета.

Когда на шине 36 находятся данные с регистра 5, то учитывается значение входов 25(+Х), 26(-Х), а когда данные с регистра 6, то учитываются значения входов 27(+Y), 28(-Y). Запись и изменение адресов, при этом, будет происходить по сигналу 23 пуск. Бит видеоданных будет записываться аналогично вышеприведенной операции. По сигналу 24 конец интерполяции снимается сигнал пуск. Следовательно, запись в блок 10 и изменение адресов на счетчике 7 прекращается. - .

В предлагаемом устройстве обработка информации может производиться как по- битно, так и пословно, что значительно улуч- шает производительность и гибкость работы устройства. Производительность работы устройства достигается за счет того, что перемещение больших объемов информации на экране производится путем считывания сразу целевого слова видеоданных и записью его по адресу перемещения (например, вертикальный роллинг). Причем, скорость перемещения задается с помощью дискретности адресов, учитывая плавность перемещения информации.

В предложенном устройстве область видеопамяти адресным способом разбивается на две независимые страницы, что позволяет формировать на экране два окна, в каждом из которых выводится и обрабатывается своя видеоинформация. Формула изобретения 1. Устройство для отображения информации на экране электронно-лучевой трубки (ЭЛТ), содержащее регистр начального адреса, счетчик адреса, блок памяти, регистр сдвига, блок управления, формирователь видеосигнала, выход которого подключен к модулятору ЭЛТ, и синхронизатор, первый выход которого соединен с первым такто- вым входом блока управления и синхровхо- дом регистра сдвига, вход разрешения записи которого соединен с первым выходом блока управления, второй выход которого подключен к управляющему входу блока памяти, выход которого соединен с информационным входом регистра сдвига, выход которого подключен к информационному входу формирователя видеосигнала, информационный вход регистра начального адреса является информационным входом устройства, выход регистра начального ад- реса через првую информационную шину соединен с информационным входом счетчика адреса, вход управления записью которого соединен с третьим выходом блока управления, счетчный вход - с четвертым выходом блока управления, отличающееся тем, что, с целью повышения быстродействия устройства и расширения области его применения за счет возможности представления изображения в окнах экрана путем перемещения изображения в любом направлении программно изменяемый скоростью, оно содержит первый и второй регистры текущего адреса, первый и второй регистры адреса модификации, формирователь адреса, первый, второй и третий буферные регистры, первый и второй коммутаторы, шинный формирователь и сдвига- тель, выход которого подключен к информационному входу блока памяти, адресный вход и вход выборки которого соединены, соответствен но с первым и вторым выходами формирователя адреса, первый информационный вход первого коммутатора и информационный вход третьего буферного регистра соединены с второй информационной шиной, которая является входом-выходом устройства и к которой подключен выход шинного формирователя, управляющий вход которого соединен с пятым выходом блока управления, а информа- ционный вход - с выходом второго буферного регистра, подключенным к первому информационному входу второго коммутатора, второй информационный вход которого соединен с выходом третьего буферного регистра, управляющий вход которого соединен с шестым выходом блока управления, седьмой выход которого подключен к управляющему входу второго буферного регистра, информационный вход которого соединен с выходом блока памяти, восьмой выход блока управления подключен к управляющему входу второго коммутатора, выход которого соединен с первым информационным входом сдвигателя, входы управления сдвигом влево и вправо ко- торого соединены соответственно с выходами младшего и старшего разрядов второго буферного регистра, второй информационный вход сдвигателя соединен с девятым выходом блока управления, десятый и одиннадцатый выходы которого соединены соответственно с первым и вторым входами направления сдвига сдвигателя, а двенадцатый и тринадцатый выходы - с входами коммутации и управления записью сдвигателя соответственно, четырнадцатый выход блока управления соединен с управляющим входом первого коммутатора, второй .информационный вход которого соединен с выходом первого буферного регистра и информационными входами первого и второго регистров текущего адреса и блока управления, управляющие входы формирователя адреса соединены с пятнадцатого по двадцать второй выходами блока управления, выходы первого и второго регистров адреса модификации подключена соответственно к первому и второму информационным входам формирователя адреса и через первую информационную шину

- к информационному входу счетчика адреса, выход которого соединен с информационным входом первого буферного регистра, выходы первого и второго регистров текущего адреса соединены через первую информационную шину с третьим информационным входом формирователя адреса, выходы первого и второго регистров текущего адреса через первую информационную шину подключены к информационному вчходу счетчика адрсзса, выход первого коммутатора подключен к информационным входам соответственно первого и второго

регистров адреса модификации, входы управления записью и входы разрешения выдачи данных которых и регистра начального адреса и регистров текущего адреса подключены соответственно к двадцать третьему по тридцать второй выходам блока управления, вход-выход которого соединен с второй информационной шиной, с второго по пятый тактовые входы блока управления соединены соответственно с второго по пятый выходами синхронизатора, с первого по седьмой управляющие входы блока управления являются соответственно входом импульса сброса, входом импульса пуска, входом сигнала конца интерполяции +Х,- X,+Y,-Y устройства, первый выход синхронизатора подключен к управляющему входу формирователя видеосигнала и синхровхо- ду счетчика адреса, тридцать третий и тридцать четвертый выходы блока управления подключены соответственно к входу направления сета счетчка адреса и входу управления записью первого буферного регистра.

2. Устройстов поп.1,отличающее- с я тем, что формирователь адреса содержит первый, второй и третий регистры, первый, второй и третий коммутаторы и дешифратор, управляющие входы которых являются управляющими входами формирователя, первым и вторым выходами которого являются, соответственно выход второго регистра и выход дешифратора, информационный вход которого соединен с выходом третьего регистра, первый и второй информационные входы третьего коммутатора соединены с выходами первого и второго коммутаторов, а выход - с информацией-. ным входом второго регистра, первый ин- формационный вход первого коммутатора подключен к выходу первого регистра, второй информационный вход первого коммутатора и информационный вход первого регистра являются третьим информационным входом формирователя, первый и второй информационные входы второго коммутатора являются соответственно вторым и первым информационными входами формирователя, первый информационный вход формирователя соединен с информационным входом третьего регистра, управяющие входы первого и второго коммутаторов соединены между собой.

ft Qi

m

| название | год | авторы | номер документа |

|---|---|---|---|

| Параллельный процессор | 1985 |

|

SU1315989A1 |

| Многопроцессорная система | 1987 |

|

SU1464168A1 |

| Ассоциативный параллельный процессор | 1981 |

|

SU1166128A1 |

| Центральный процессор | 1991 |

|

SU1804645A3 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Устройство центрального управления процессора | 1983 |

|

SU1136177A1 |

| Устройство для обработки и отображения видеоинформации | 1988 |

|

SU1748284A1 |

| Устройство для отображения информации | 1984 |

|

SU1231496A1 |

| Вычислительная система | 1989 |

|

SU1777148A1 |

| Микропрограммный процессор | 1981 |

|

SU1037262A1 |

Сущность изобретения: устройство содержит 2 коммутатора, 5 регистров. 1 регистр сдвига, 1 счетчик адреса, 3 буферных регистра, 1 шинный формирователь, 1 формирователь видеосигнала, 1 сдвигатель, 1 ЭЛТ, 1 синхронизатор, 1 блок управления, 1 формирователь адреса, 1 блок памяти. 1 з.п.ф-лы, 14 ил.

. Cri

bs

г

J

Si

5

91SA081

f

2

у г из SMOdamta Или vraafffffO #мдцхация //а Мли t/ндикацщ /с/принд.подго- даннш2с/пр. 3jrfс/лр. анд. на ЭЙТ гс/пр. wooxa ovepe&a(/ffdffooeo/n0a- инд. jo адреса vr vcoovepeSttmo .

itt, f

fc/пр. ova

affpeca УГгслк гмй

- шройаное адресамооифо. fyuoXAMMrfi.

v3efftO;/IOOfO-f

Vtra

&ГСЛОЙ1

Границы разбиения на страницы

ММ

J

4

S/2

Ш

-X

.J&S-u ФигЛ

f2 LПJU J J j JlплJlллJlЛJlл

#,

LriJinjiJiimji и

90Г- TO l

fff I---i--;-l

П wwMffiefa МшлТмйт

тг I-----3

J/ j:

50 Рамс- 3сглрск4.

ffU/M.

{Декремент

68

ГТ

///////7/ /////////////////////// Лусх У/леше

Фиг.7а

Фиг.8 а

Фиг.8 б

tf/мремем/я

ГТ

Фиг.7&

9

fc fc И

«

fc fc fc

,

Фиг.12

Фиг. 13

| Устройство для отображения информации на экране электронно-лучевой трубки | 1985 |

|

SU1300544A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Приспособление для установки двигателя в топках с получающими возвратно-поступательное перемещение колосниками | 1917 |

|

SU1985A1 |

Авторы

Даты

1993-04-07—Публикация

1991-01-30—Подача