Изобретение относится к вычислительной технике и может быть использовано при построении однородных вичислительных структур и сред повышенной надежности,

Цель изобретения - снижение временных затрат на контроль и повышение достоверности результатов выполняемых задач за счет введения устройства управления и устройства сравнения результатов.

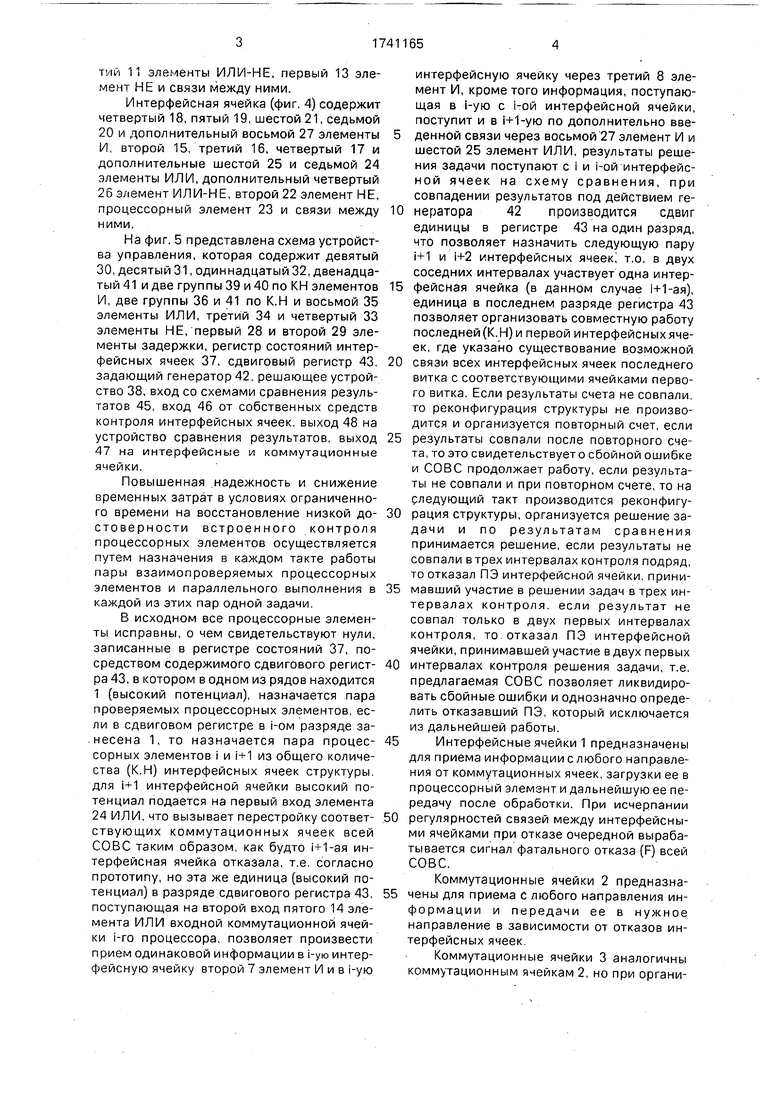

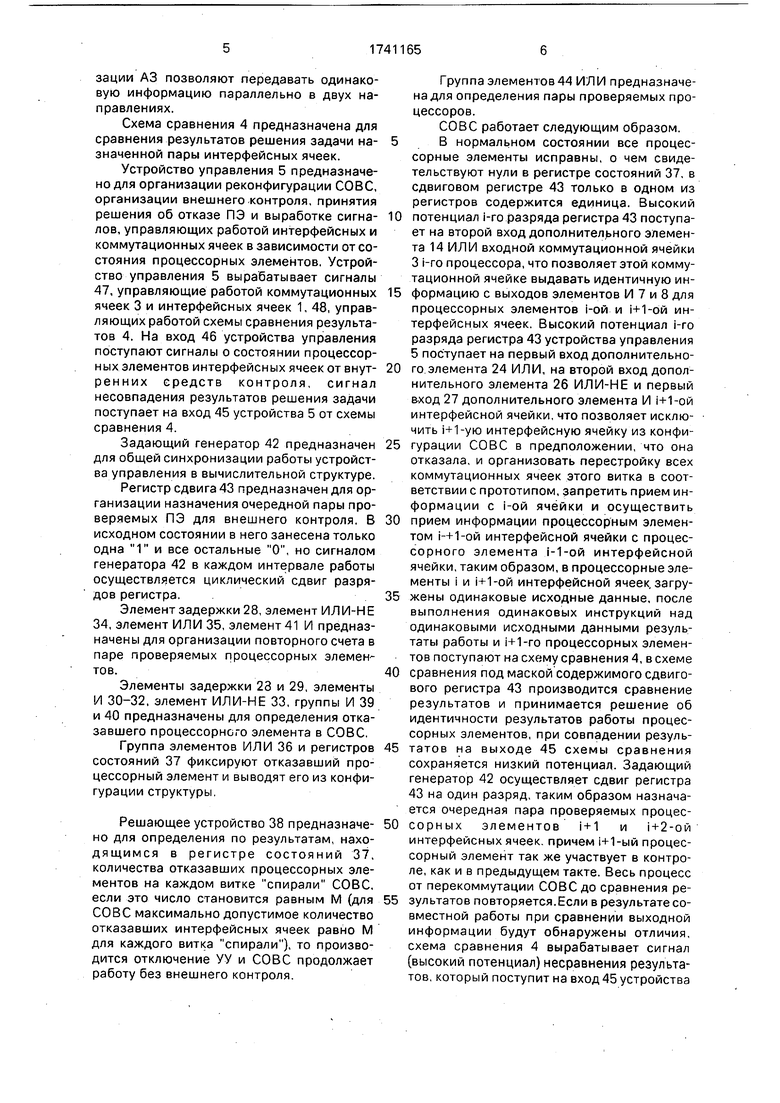

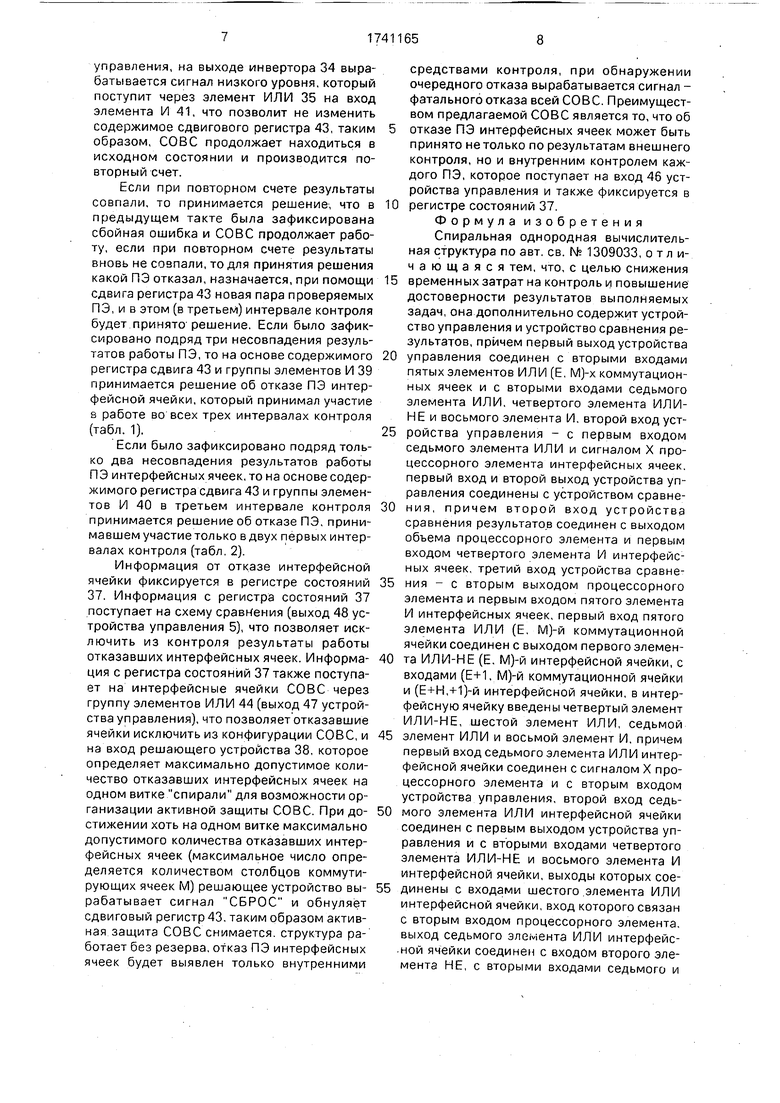

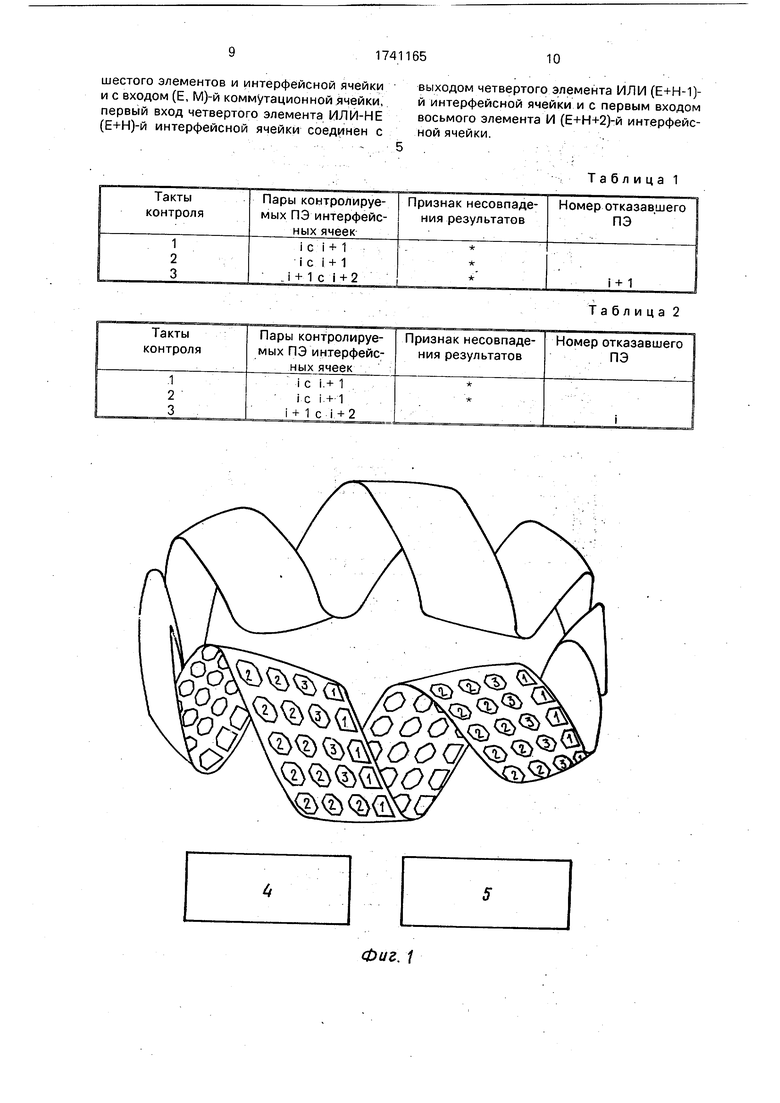

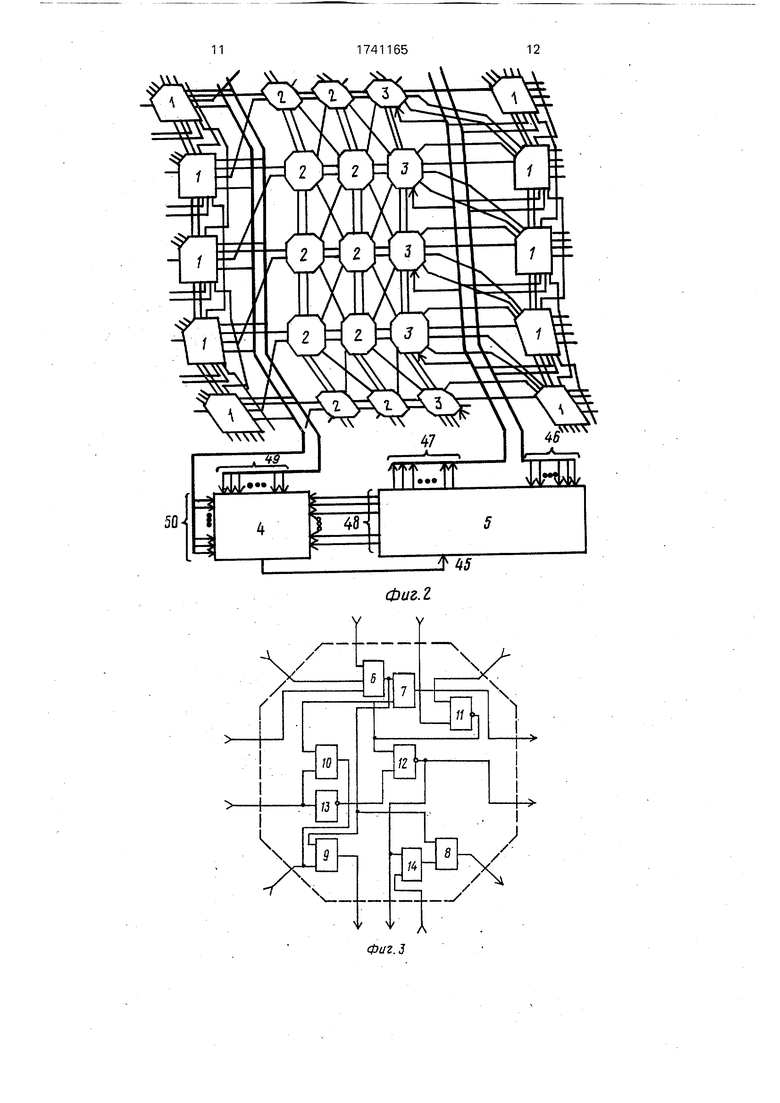

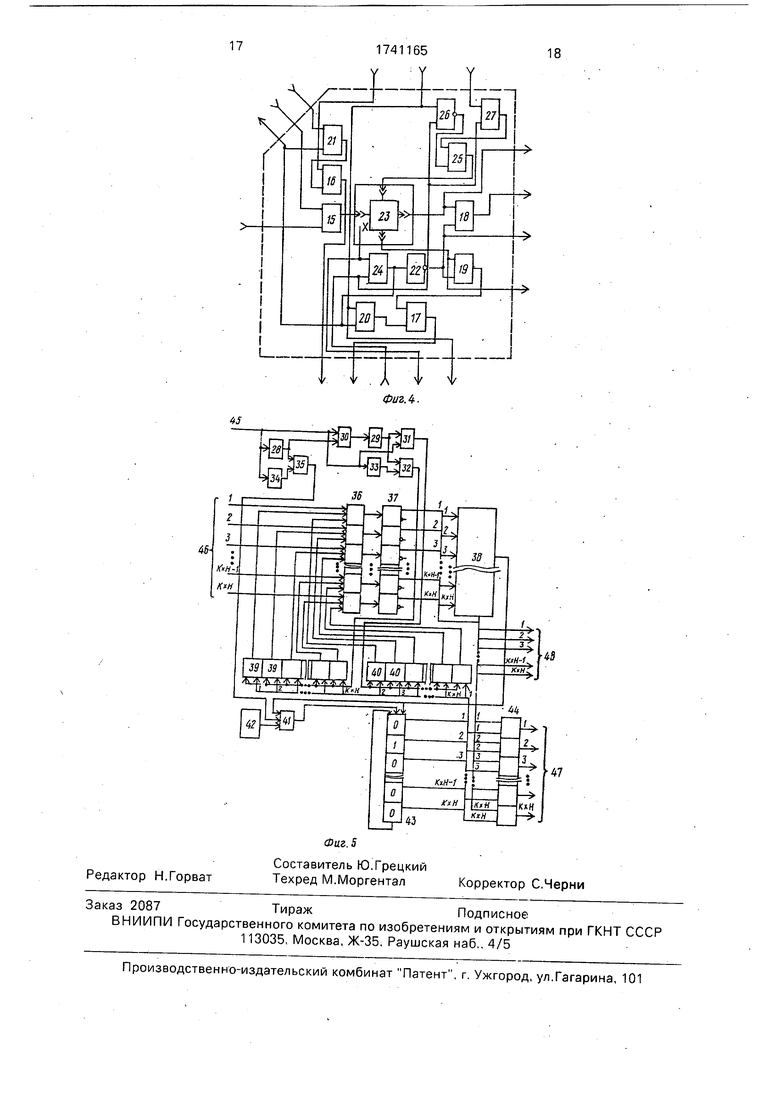

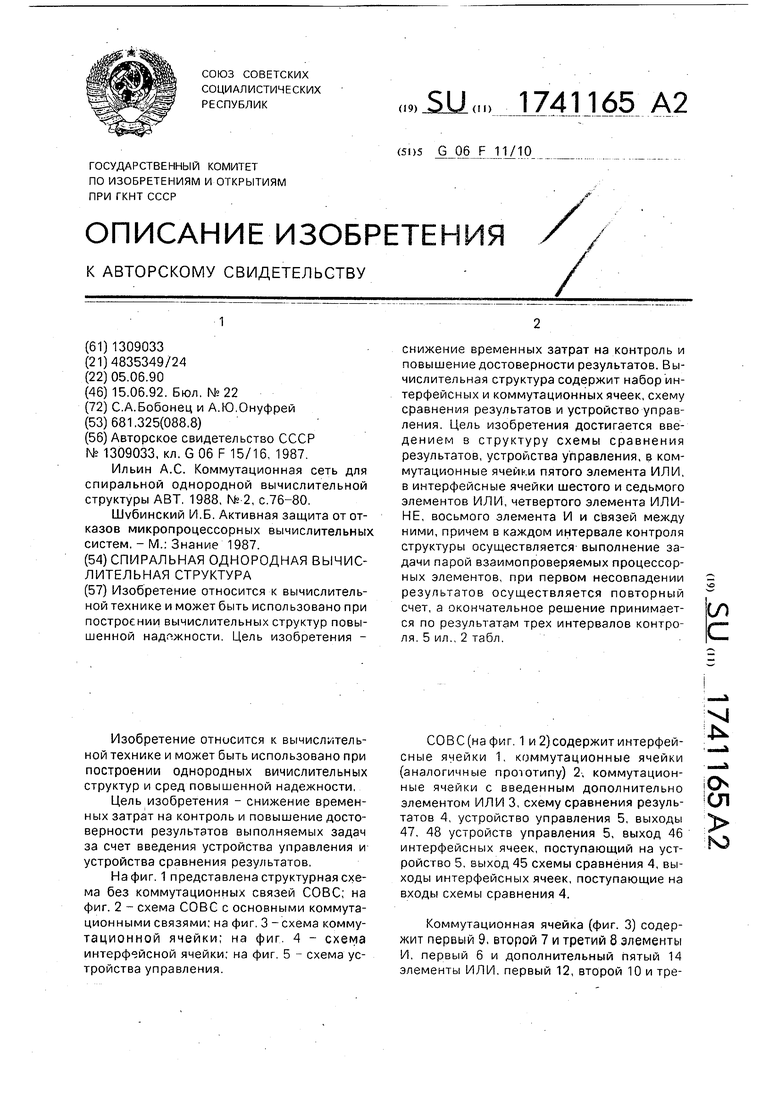

На фиг. 1 представлена структурная схема без коммутационных связей СОВС; на фиг. 2 - схема СОВС с основными коммутационными связями; на фиг. 3 - схема коммутационной ячейки; на фиг. 4 - схема интерфейсной ячейки; на фиг. 5 - схема устройства управления.

СО В С (на фиг. 1 и 2) содержит интерфейсные ячейки 1, коммутационные ячейки (аналогичные прототипу) 2, коммутационные ячейки с введенным дополнительно элементом ИЛИ 3, схему сравнения результатов 4, устройство управления 5, выходы 47, 48 устройств управления 5, выход 46 интерфейсных ячеек, поступающий на устройство 5, выход 45 схемы сравнения 4, выходы интерфейсных ячеек, поступающие на входы схемы сравнения 4.

Коммутационная ячейка (фиг. 3) содержит первый 9, второй 7 и третий 8 элементы И, первый 6 и дополнительный пятый 14 элементы ИЛИ. первый 12, второй 10 и треvi

,о ел

го

тий 11 элементы ИЛИ-НЕ, первый 13 элемент НЕ и связи между ними.

Интерфейсная ячейка (фиг. 4) содержит четвертый 18, пятый 19, шестой 21, седьмой 20 и дополнительный восьмой 27 элементы И, второй 15, третий 16, четвертый 17 и дополнительные шестой 25 и седьмой 24 элементы ИЛИ, дополнительный четвертый 26 элемент ИЛИ-НЕ, второй 22 элемент НЕ, процессорный элемент 23 и связи между ними.

На фиг. 5 представлена схема устройства управления, которая содержит девятый 30, десятый 31, одиннадцатый 32, двенадцатый 41 и две группы 39 и 40 по КН элементов И, две группы 36 и 41 по К.Н и восьмой 35 элементы ИЛИ, третий 34 и четвертый 33 элементы НЕ, первый 28 и второй 29 элементы задержки, регистр состояний интерфейсных ячеек 37, сдвиговый регистр 43, задающий генератор 42, решающее устройство 38, вход со схемами сравнения результатов 45, вход 46 от собственных средств контроля интерфейсных ячеек, выход 48 на устройство сравнения результатов, выход 47 на интерфейсные и коммутационные ячейки.

Повышенная надежность и снижение временных затрат в условиях ограниченного времени на восстановление низкой до- стоверности встроенного контроля процессорных элементов осуществляется путем назначения в каждом такте работы пары взаимопроверяемых процессорных элементов и параллельного выполнения в каждой из этих пар одной задачи.

В исходном все процессорные элементы исправны, о чем свидетельствуют нули, записанные в регистре состояний 37, посредством содержимого сдвигового регист- ра 43, в котором в одном из рядов находится 1 (высокий потенциал), назначается пара проверяемых процессорных элементов, если в сдвиговом регистре в i-ом разряде занесена 1, то назначается пара процес- сорных элементов i и i+1 из общего количества (К.Н) интерфейсных ячеек структуры, для i+1 интерфейсной ячейки высокий потенциал подается на первый вход элемента 24 ИЛИ, что вызывает перестройку соответ- ствующих коммутационных ячеек всей СОВС таким образом, как будто i+1-ая интерфейсная ячейка отказала, т.е. согласно прототипу, но эта же единица (высокий потенциал) в разряде сдвигового регистра 43, поступающая на второй вход пятого 14 элемента ИЛИ входной коммутационной ячейки i-ro процессора, позволяет произвести прием одинаковой информации в i-ую интерфейсную ячейку второй 7 элемент И и в i-ую

интерфейсную ячейку через третий 8 элемент И, кроме того информация, поступающая в i-ую с i-ой интерфейсной ячейки, поступит и в i+1-ую по дополнительно введенной связи через восьмой 27 элемент И и шестой 25 элемент ИЛИ, результаты решения задачи поступают с i и i-ой интерфейсной ячеек на схему сравнения, при совпадении результатов под действием генератора 42 производится сдвиг единицы в регистре 43 на один разряд, что позволяет назначить следующую пару i+1 и i+2 интерфейсных ячеек, т.о. в двух соседних интервалах участвует одна интерфейсная ячейка (в данном случае i+1-ая), единица в последнем разряде регистра 43 позволяет организовать совместную работу последней (К.Н) и первой интерфейсныхяче- ек, где указано существование возможной связи всех интерфейсных ячеек последнего витка с соответствующими ячейками первого витка. Если результаты счета не совпали, то реконфигурация структуры не производится и организуется повторный счет, если результаты совпали после повторного счета, то это свидетельствует о сбойной ошибке и СОВС продолжает работу, если результаты не совпали и при повторном счете, то на Следующий такт производится реконфигурация структуры, организуется решение задачи и по результатам сравнения принимается решение, если результаты не совпали втрех интервалах контроля подряд, то отказал ПЭ интерфейсной ячейки, принимавший участие в решении задач в трех интервалах контроля, если результат не совпал только в двух первых интервалах контроля, то отказал ПЭ интерфейсной ячейки, принимавшей участие в двух первых интервалах контроля решения задачи, т.е. предлагаемая СОВС позволяет ликвидировать сбойные ошибки и однозначно определить отказавший ПЭ, который исключается из дальнейшей работы.

Интерфейсные ячейки 1 предназначены для приема информации с любого направления от коммутационных ячеек, загрузки ее в процессорный элемэнт и дальнейшую ее передачу после обработки. При исчерпании регулярностей связей между интерфейсными ячейками при отказе очередной вырабатывается сигнал фатального отказа (F) всей СОВС.

Коммутационные ячейки 2 предназначены для приема с любого направления информации и передачи ее в нужное направление в зависимости от отказов интерфейсных ячеек

Коммутационные ячейки 3 аналогичны коммутационным ячейкам 2, но при организации A3 позволяют передавать одинаковую информацию параллельно в двух направлениях.

Схема сравнения 4 предназначена для сравнения результатов решения задачи назначенной пары интерфейсных ячеек.

Устройство управления 5 предназначено для организации реконфигурации СОВС, организации внешнего контроля, принятия решения об отказе ПЭ и выработке сигналов, управляющих работой интерфейсных и коммутационных ячеек в зависимости от состояния процессорных элементов. Устройство управления 5 вырабатывает сигналы 47, управляющие работой коммутационных ячеек 3 и интерфейсных ячеек 1, 48, управляющих работой схемы сравнения результатов 4. На вход 46 устройства управления поступают сигналы о состоянии процессорных элементов интерфейсных ячеек от внут- ренних средств контроля, сигнал несовпадения результатов решения задачи поступает на вход 45 устройства 5 от схемы сравнения 4.

Задающий генератор 42 предназначен для общей синхронизации работы устройства управления в вычислительной структуре.

Регистр сдвига 43 предназначен для организации назначения очередной пары проверяемых ПЭ для внешнего контроля. В исходном состоянии в него занесена только одна 1 и все остальные О, но сигналом генератора 42 в каждом интервале работы осуществляется циклический сдвиг разрядов регистра.

Элемент задержки 28, элемент ИЛИ-НЕ 34, элемент ИЛИ 35, элемент 41 И предназначены для организации повторного счета в паре проверяемых процессорных элементов.

Элементы задержки 23 и 29, элементы И 30-32, элемент ИЛИ-НЕ 33, группы И 39 и 40 предназначены для определения отказавшего процессорного элемента в СОВС.

Группа элементов ИЛИ 36 и регистров состояний 37 фиксируют отказавший процессорный элемент и выводят его из конфигурации структуры

Решающее устройство 38 предназначено для определения по результатам, находящимся в регистре состояний 37, количества отказавших процессорных элементов на каждом витке спирали СОВС, если это число становится равным М (для СОВС максимально допустимое количество отказавших интерфейсных ячеек равно М для каждого витка спирали), то производится отключение УУ и СОВС продолжает работу без внешнего контроля.

Группа элеметов44 ИЛИ предназначена для определения пары проверяемых процессоров.

СОВС работает следующим образом.

В нормальном состоянии все процессорные элементы исправны, о чем свидетельствуют нули в регистре состояний 37, в сдвиговом регистре 43 только в одном из регистров содержится единица. Высокий

0 потенциал i-ro разряда регистра 43 поступает на второй вход дополнительного элемента 14 ИЛИ входной коммутационной ячейки 3 i-ro процессора, что позволяет этой коммутационной ячейке выдавать идентичную ин5 формацию с выходов элементов И 7 и 8 для процессорных элементов i-ой и i+1-ой интерфейсных ячеек. Высокий потенциал i-ro разряда регистра 43 устройства управления 5 поступает на первый вход дополнительно0 го элемента 24 ИЛИ, на второй вход дополнительного элемента 26 ИЛИ-НЕ и первый вход 27 дополнительного элемента И i+1-ой интерфейсной ячейки, что позволяет исключить i+1-ую интерфейсную ячейку из конфи5 гурации СОВС в предположении, что она отказала, и организовать перестройку всех коммутационных ячеек этого витка в соответствии с прототипом, запретить прием информации с i-ой ячейки и осуществить

0 прием информации процессорным элементом -+1-ой интерфейсной ячейки с процессорного элемента i-1-ой интерфейсной ячейки, таким образом, в процессорные элементы i и i+1-ой интерфейсной ячеек, загру5 жены одинаковые исходные данные, после выполнения одинаковых инструкций над одинаковыми исходными данными результаты работы и i+1-го процессорных элементов поступают на схему сравнения 4, в схеме

0 сравнения под маской содержимого сдвигового регистра 43 производится сравнение результатов и принимается решение об идентичности результатов работы процессорных элементов, при совпадении резуль5 татов на выходе 45 схемы сравнения сохраняется низкий потенциал. Задающий генератор 42 осуществляет сдвиг регистра 43 на один разряд, таким образом назначается очередная пара проверяемых процес0 сорных элементов i + 1 и i + 2-ой интерфейсных ячеек причем i+1-ый процессорный элемент так же участвует в контроле, как и в предыдущем такте. Весь процесс от перекоммутации СОВС до сравнения ре5 зультатов повторяется.Если в результате совместной работы при сравнении выходной информации будут обнаружены отличия, схема сравнения 4 вырабатывает сигнал (высокий потенциал) несравнения результатов, который поступит на вход 45 устройства

управления, на выходе инвертора 34 вырабатывается сигнал низкого уровня, который поступит через элемент ИЛИ 35 на вход элемента И 41, что позволит не изменить содержимое сдвигового регистра 43, таким образом, СОВС продолжает находиться в исходном состоянии и производится повторный счет.

Если при повторном счете результаты совпали, то принимается решение, что в предыдущем такте была зафиксирована сбойная ошибка и СОВС продолжает работу, если при повторном счете результаты вновь не совпали, то для принятия решения какой ПЭ отказал, назначается, при помощи сдвига регистра 43 новая пара проверяемых ПЭ, и в этом (в третьем) интервале контроля будет примято решение. Если было зафиксировано подряд три несовпадения результатов работы ПЭ, то на основе содержимого регистра сдвига 43 и группы элементов И 39 принимается решение об отказе ПЭ интерфейсной ячейки, который принимал участие в работе во всех трех интервалах контроля (табл. 1).

Если было зафиксировано подряд только два несовпадения результатов работы ПЭ интерфейсных ячеек, то на основе содержимого регистра сдвига 43 и группы элементов И 40 в третьем интервале контроля принимается решение об отказе ПЭ, принимавшем участиетолько в двух первых интервалах контроля (табл. 2).

Информация от отказе интерфейсной ячейки фиксируется в регистре состояний 37. Информация с регистра состояний 37 поступает на схему сравнения (выход 48 устройства управления 5), что позволяет исключить из контроля результаты работы отказавших интерфейсных ячеек. Информация с регистра состояний 37 также поступает на интерфейсные ячейки СОВС через группу элементов ИЛИ 44 (выход 47 устройства управления), что позволяет отказавшие ячейки исключить из конфигурации СОВС, и на вход решающего устройства 38, которое определяет максимально допустимое количество отказавших интерфейсных ячеек на одном витке спирали для возможности организации активной защиты СОВС. При достижении хоть на одном витке максимально допустимого количества отказавших интерфейсных ячеек (максимальное число определяется количеством столбцов коммутирующих ячеек М) решающее устройство вырабатывает сигнал СБРОС и обнуляет сдвиговый регистр 43, таким образом активная защита СОВС снимается, структура работает без резерва, отказ ПЭ интерфейсных ячеек будет выявлен только внутренними

средствами контроля, при обнаружении очередного отказа вырабатывается сигнал - фатального отказа всей СОВС. Преимуществом предлагаемой СОВС является то, что об

отказе ПЭ интерфейсных ячеек может быть принято не только по результатам внешнего контроля, но и внутренним контролем каждого ПЭ, которое поступает на вход 46 устройства управления и также фиксируется в

0 регистре состояний 37.

Формула изобретения Спиральная однородная вычислительная структура по авт. св. № 1309033, отличающаяся тем, что, с целью снижения

5 временных затрат на контроль и повышение достоверности результатов выполняемых задач, она дополнительно содержит устройство управления и устройство сравнения результатов, причем первый выход устройства

0 управления соединен с вторыми входами пятых элементов ИЛИ (Е. М)-х коммутационных ячеек и с вторыми входами седьмого элемента ИЛИ, четвертого элемента ИЛИ- НЕ и восьмого элемента И. второй вход уст5 ройства управления - с первым входом седьмого элемента ИЛИ и сигналом X процессорного элемента интерфейсных ячеек, первый вход и второй выход устройства управления соединены с устройством сравне0 ния, причем второй вход устройства сравнения результатов соединен с выходом объема процессорного элемента и первым входом четвертого элемента И интерфейсных ячеек, третий вход устройства сравне5 ния - с вторым выходом процессорного элемента и первым входом пятого элемента И интерфейсных ячеек, первый вход пятого элемента ИЛИ (Е, М)-й коммутационной ячейки соединен с выходом первого элемен0 та ИЛИ-НЕ (Е, М)-й интерфейсной ячейки, с входами (Е+1, М)-й коммутационной ячейки и (Е+Н,+1)-й интерфейсной ячейки, в интерфейсную ячейку введены четвертый элемент ИЛИ-НЕ, шестой элемент ИЛИ, седьмой

5 элемент ИЛИ и восьмой элемент И, причем первый вход седьмого элемента ИЛИ интерфейсной ячейки соединен с сигналом X процессорного элемента и с вторым входом устройства управления, второй вход седь0 мого элемента ИЛИ интерфейсной ячейки соединен с первым выходом устройства управления и с вторыми входами четвертого элемента ИЛИ-НЕ и восьмого элемента И интерфейсной ячейки, выходы которых сое5 динены с входами шестого элемента ИЛИ интерфейсной ячейки, вход которого связан с вторым входом процессорного элемента, выход седьмого элемента ИЛИ интерфейсной ячейки соединен с входом второго элемента НЕ, с вторыми входами седьмого и

шестого элементов и интерфейсной ячейки и с входом (Е, М)-й коммутационной ячейки, первый вход четвертого элемента ИЛИ-НЕ (Е+Н)-й интерфейсной ячейки соединен с

выходом четвертого элемента ИЛИ (Е+Н-1)- й интерфейсной ячейки и с первым входом восьмого элемента И (Е+Н+2)-й интерфейсной ячейки.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЯЧЕЙКА МАРШРУТИЗАЦИИ ОДНОРОДНОЙ СРЕДЫ ПРОЦЕССОРНЫХ ЭЛЕМЕНТОВ | 2004 |

|

RU2273876C1 |

| ЯЧЕЙКА ОДНОРОДНОЙ СРЕДЫ ПРОЦЕССОРНЫХ ЭЛЕМЕНТОВ | 2004 |

|

RU2267153C2 |

| ЯЧЕЙКА ОДНОРОДНОЙ СРЕДЫ ПРОЦЕССОРНЫХ ЭЛЕМЕНТОВ | 2000 |

|

RU2177169C1 |

| ЯЧЕЙКА ОДНОРОДНОЙ СРЕДЫ | 2001 |

|

RU2197745C2 |

| Ячейка однородной среды | 1989 |

|

SU1756898A1 |

| ЯЧЕЙКА ОДНОРОДНОЙ СРЕДЫ | 1995 |

|

RU2103724C1 |

| ЯЧЕЙКА ОДНОРОДНОЙ ОТКАЗОУСТОЙЧИВОЙ СРЕДЫ ПРОЦЕССОРНЫХ ЭЛЕМЕНТОВ | 2003 |

|

RU2256212C2 |

| Измерительная система с автоматическим контролем аналого-цифрового преобразования и блок задания нечувствительности | 1991 |

|

SU1837261A1 |

| Мажоритарно-резервированный интерфейс памяти | 1990 |

|

SU1751766A1 |

| Постоянное запоминающее устройство с резервированием | 1986 |

|

SU1372363A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении вычислительных структур повышенной надежности. Цель изобретения снижение временных затрат на контроль и повышение достоверности результатов. Вычислительная структура содержит набор интерфейсных и коммутационных ячеек, схему сравнения результатов и устройство управления. Цель изобретения достигается введением в структуру схемы сравнения результатов, устройства управления, в коммутационные ячейки пятого элемента ИЛИ, в интерфейсные ячейки шестого и седьмого элементов ИЛИ, четвертого элемента ИЛИ- НЕ, восьмого элемента И и связей между ними, причем в каждом интервале контроля структуры осуществляется выполнение задачи парой взаимопроверяемых процессорных элементов, при первом несовпадении результатов осуществляется повторный счет, а окончательное решение принимается по результатам трех интервалов контроля. 5 ил., 2 табл. (Л С

Таблица 1

Таблица 2

Фиг. 1

Фиг. 2

| Однородная коммутирующая сеть | 1985 |

|

SU1309033A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Ильин А.С | |||

| Коммутационная сеть для спиральной однородной вычислительной структуры АВТ | |||

| Механическая топочная решетка с наклонными частью подвижными, частью неподвижными колосниковыми элементами | 1917 |

|

SU1988A1 |

| Шубинский И.Б | |||

| Активная защита от отказов микропроцессорных вычислительных систем | |||

| Кузнечная нефтяная печь с форсункой | 1917 |

|

SU1987A1 |

Авторы

Даты

1992-06-15—Публикация

1990-06-05—Подача