Изобретение относится к вычислительной технике и может быть использовано при построении высоконадежных высокопроизводительных резервированных вычислительных систем

Известен мажоритарно-резервированный интерфейс памяти, содержащий в каждом канале соответствующим образом соединенные между собой коммутаторы входной и выходной информации, первый и второй коммутатора внутренней информации, регистр контроля, шесть буферных регистров, регистры состояния памяти и устройства ввода-вывода, первый и второй регистры состояния процессора, счетчики временных интервалов и состояний, счетчики адресов команд и данных, коммутатор состояний блока памяти, коммутаторы первого, второго и третьего разрядов состояний процессора, три коммутатора кодов состояний, коммутатор адреса, коммутатор перестройки процессора, коммутаторы сигналов переполнения счетчика состояний, счегчика временных интервалов, блок пуска счетчиков, блок сравнения, коммутационный блок управления, преобразователь кодов, дешифратор отказов, дешифраторы состояний блока памяти и процессора, первый и второй триггеры сброса, первый и второй триггеры управления перестройкой процессора, мажоритарные блоки адреса и управления, первый и второй мажоритарные блоки информации, первый и второй мажоритарные элементы начальной установки, мажоритарный элемент перестройки процессора, с первого по четвертый элементы И-ИЛИVJ

СП

4 О О

НЕ, с первого почетвертый элементы И-НЕ, первый и второй элементы ИЛИ-НЕ, с первого по восьмой элементы И и с первого по пятый элементы ИЛИ, при этом каналы соединены между собой по мажоритарному Принципу.

Недостатками данного устройства являются большие аппаратные затраты на реализацию интерфейса и низкая надежность устройства, поскольку отказ оборудования, организующего надежную передачу данных через интерфейс, равноценен отказу всего канала интерфейса.

Наиболее близким по технической сущности и достигаемому положительному эффекту к предлагаемому устройству является мажоритарно-резервированный интерфейс памяти, содержащий в каждом канале соответствующим образом соединенные коммутаторы входной, выходной и внутренней информации, регистр контроля, два буферных регистра, блок вентилей, блок мажоритарных элементов, включающий три мажоритарных элемента, регистры состояний блоков памяти и устройства ввода-вывода, два регистра состояний процессора, счетчики временных интервалов и состояний, счетчики адресов команд и данных, коммутатор состояний блока памяти, коммутаторы первого, второго и третьего разрядов состояния процессора, три коммутатора кодов состояний, коммутатор адреса, коммутатор реконфигурации процессора, коммутаторы сигналов переполнения счетчика временных интервалов и счетчика состояний, блок пуска счетчиков, блок сравнения, коммутационный блок управления, преобразователь кодов, дешифратор отказов, дешифраторы состояний процессора и блока памяти, два триггера сброса, два триггера управления реконфигурацией процессора, мажоритарные блоки управления, адреса и информации, два мажоритарных элемента начальной установки, мажоритарный элемент управления реконфигурацией процессора, четыре элемента И-ИЛИ-НЕ, элемент И-ИЛИ (управления реконфигурацией процессора), четыре элемента И-НЕ, два элемента ИЛИ- НЕ, восемь элементов И и пять элементов ИЛИ, при этом каналы соединены между собой по мажоритарному принципу,

Недостатком данного устройства является низкая надежность, обусловленная тем, что обнаружение отказов (сбоев) происходит только в моменты передачи информации через интерфейс. Поскольку процессоры, как правило, включают сверхоперативную память (регистры общего назначения), то в течение определенного

времени они преобразуют информацию, расположенную в сверхоперативной памяти, без передачи ее через интерфейс. Обнаружение отказа (сбоя), возникающего во

время преобразования ее процессором в данном интерфейсе, происходит с запаздыванием на время г, зависящее от алгоритмов преобразования. Если принять среднее время возникновения сбоя (отказа) равным

t, то соотношения величин t и т приводит к следующим последствиям.

При t т происходит снижение производительности устройства из-за потерь времени работы, равных Т (Т t), если имеется

зафиксированный в интерфейсе отказавший процессор. В данной ситуации недостатком устройства следует назвать его низкую производительность.

При t г, если имеется зафиксированный в интерфейсе отказавший процессор, или при t 2 т даже при трех исправных процессорах сбои могут привести к невосстановлению интерфейсом информации. В данном случае процедура восстановления

информации и, соответственно, вычислительного процесса может снизить производительность устройства настолько, что приведет к приостанову вычислительного процесса, т.е.- этот недостаток следует классифицировать как низкую надежность работы устройства.

Другим фактором, снижающим надежность устройства, является то, что при подключении к нему блоков памяти в виде ОЗУ,

имеющих отказы в одноименных разрядах одноименных адресов в трех каналах, или в виде ПЗУ, имеющих ошибки программ, не обнаруженные при отладках этих программ, или программ, требующих коррекции (замены ПЗУ) из-за изменившихся условий эксплуатации, такие ситуации в рассмотренном устройстве классифицируются как отказ устройства в целом и определяют его низкую надежность в определенных условиях эксплуатации устройства,

Цель изобретения - повышение надежности интерфейса путем повышения оперативности контроля возникающих отказов, адаптации интерфейса к отказам и

обеспечения динамической коррекции программ.

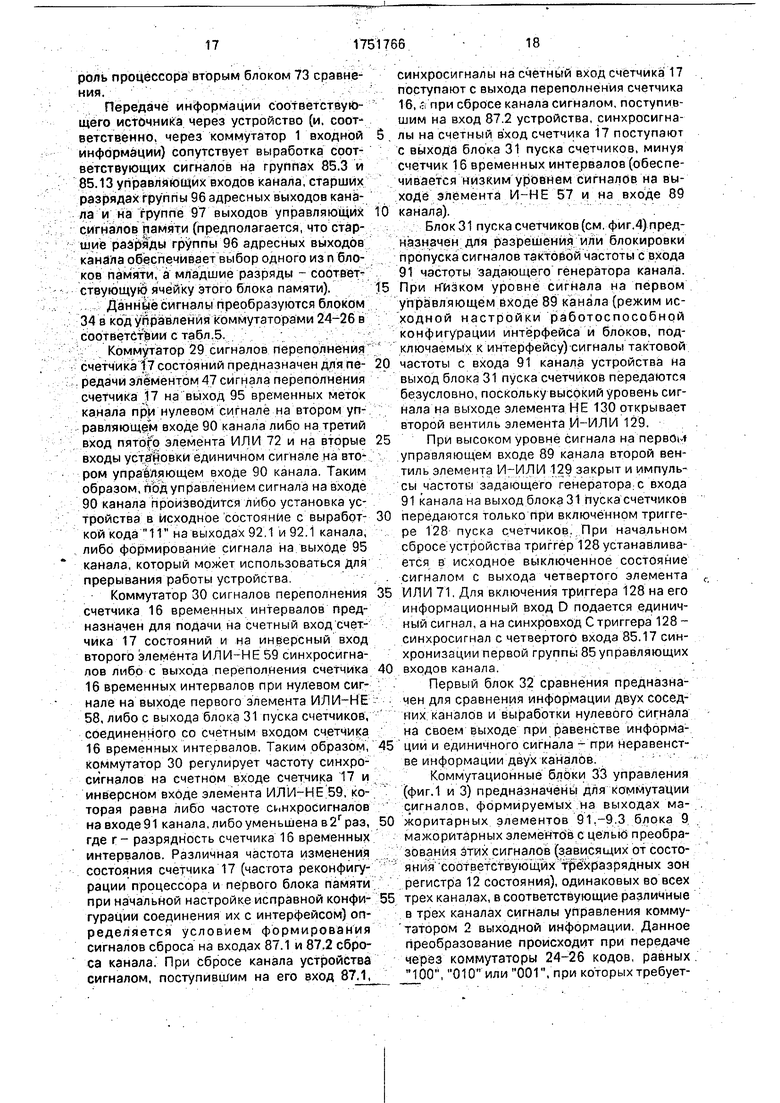

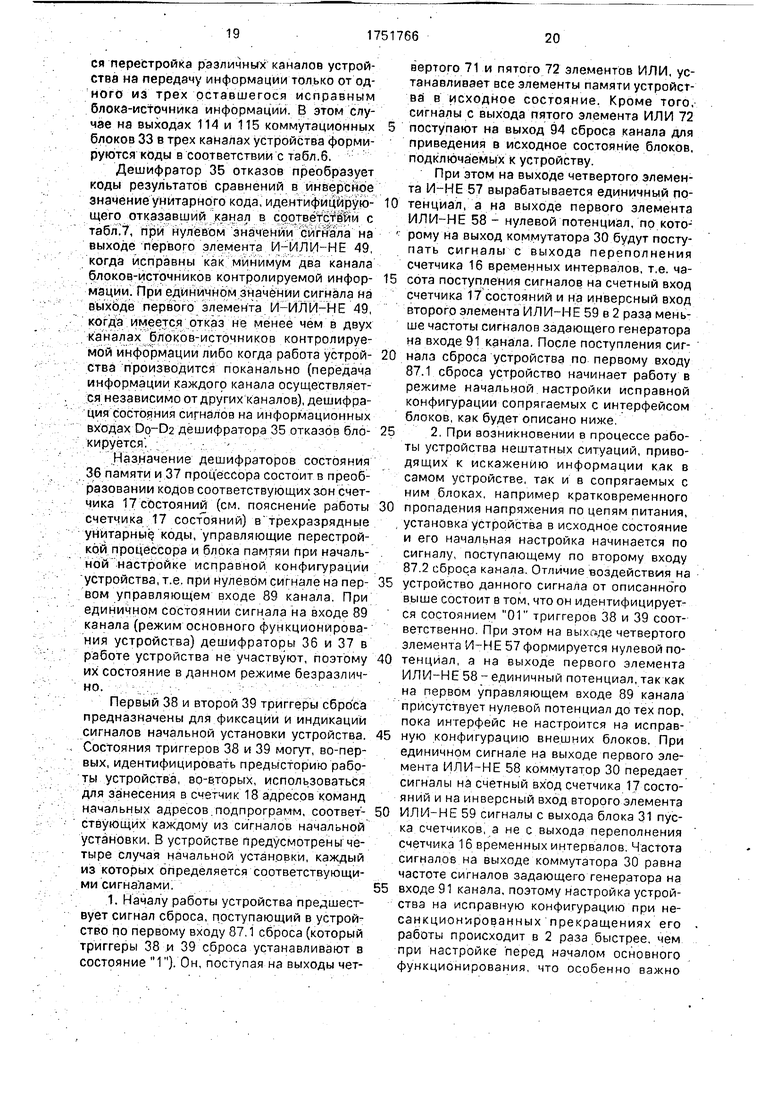

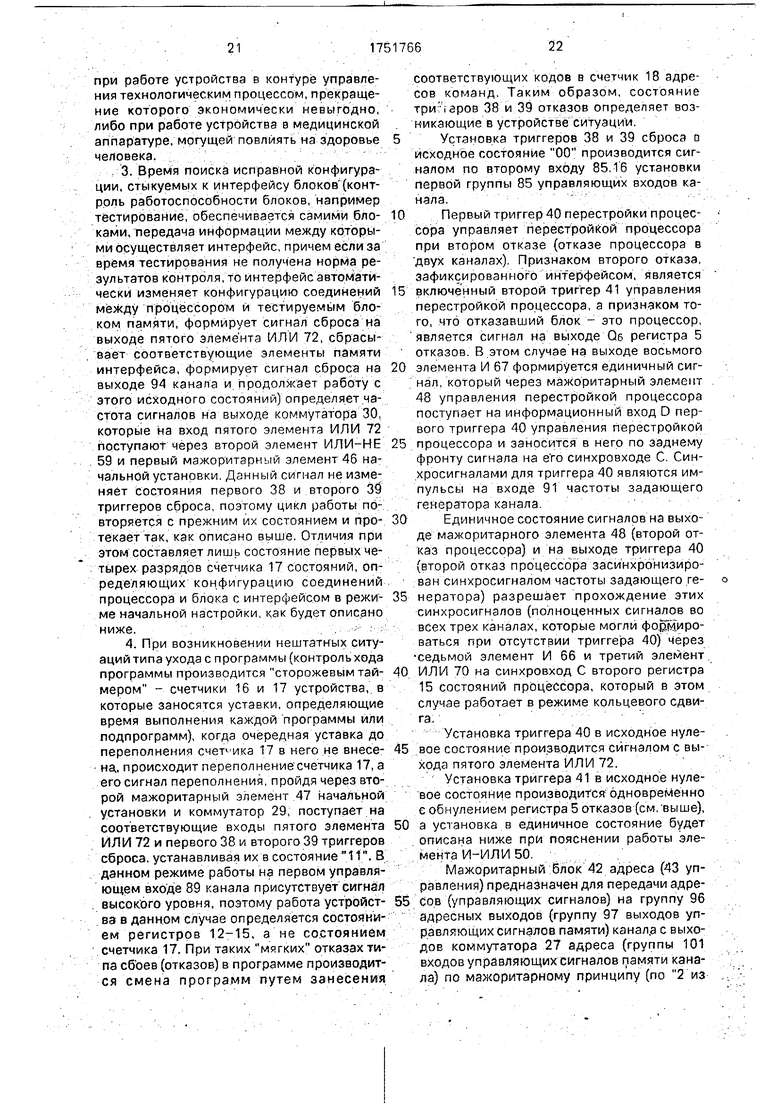

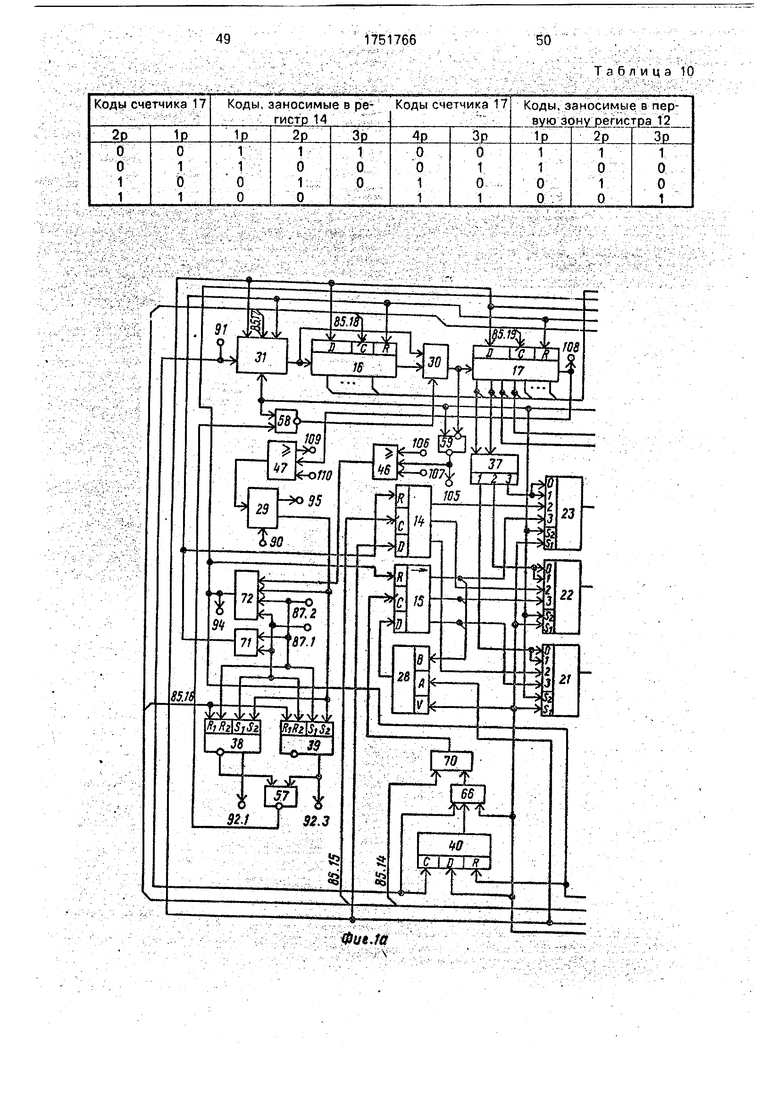

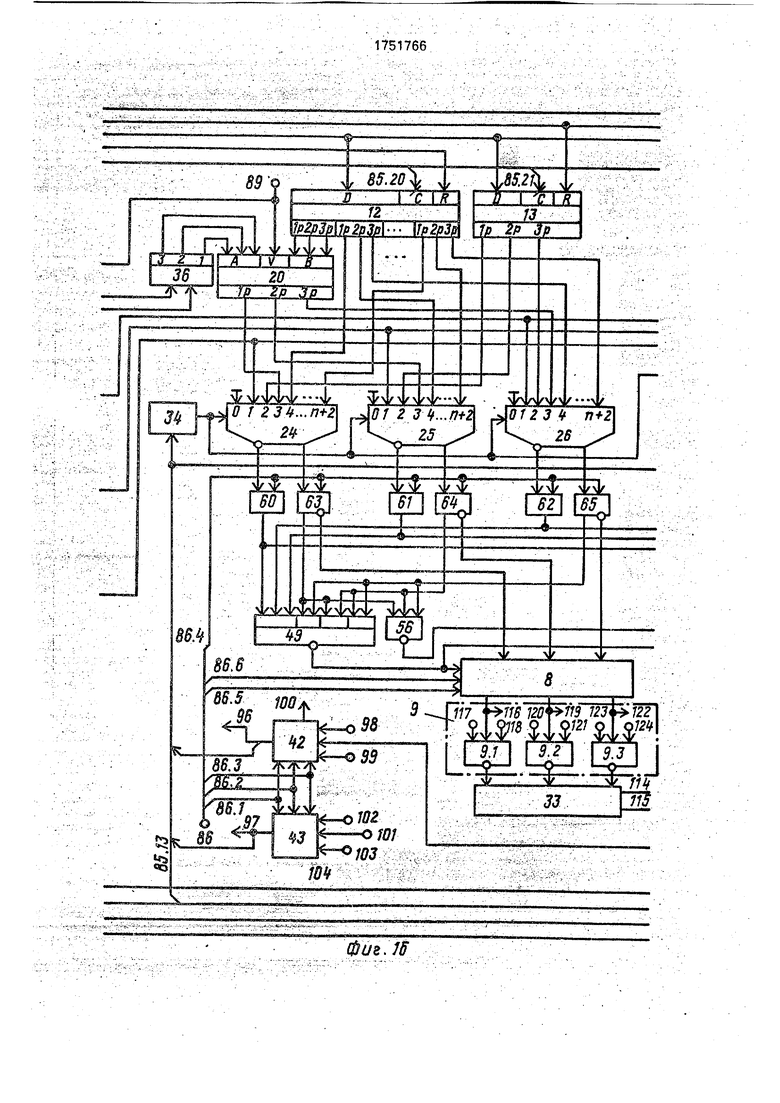

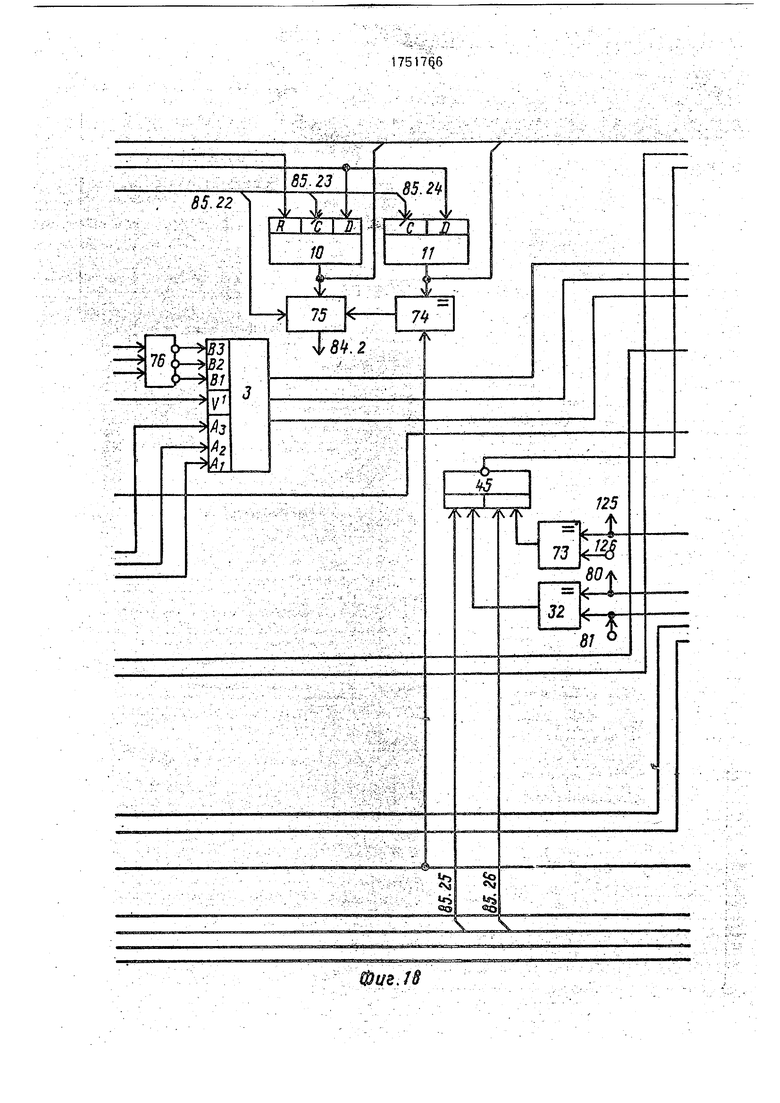

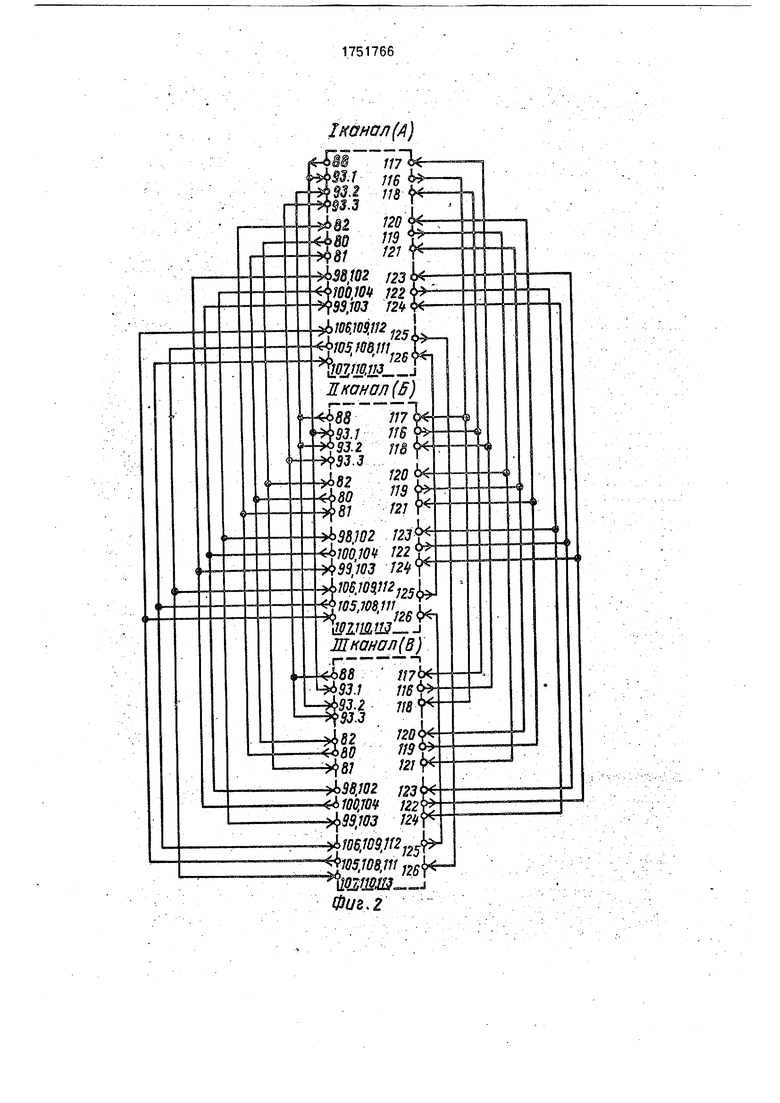

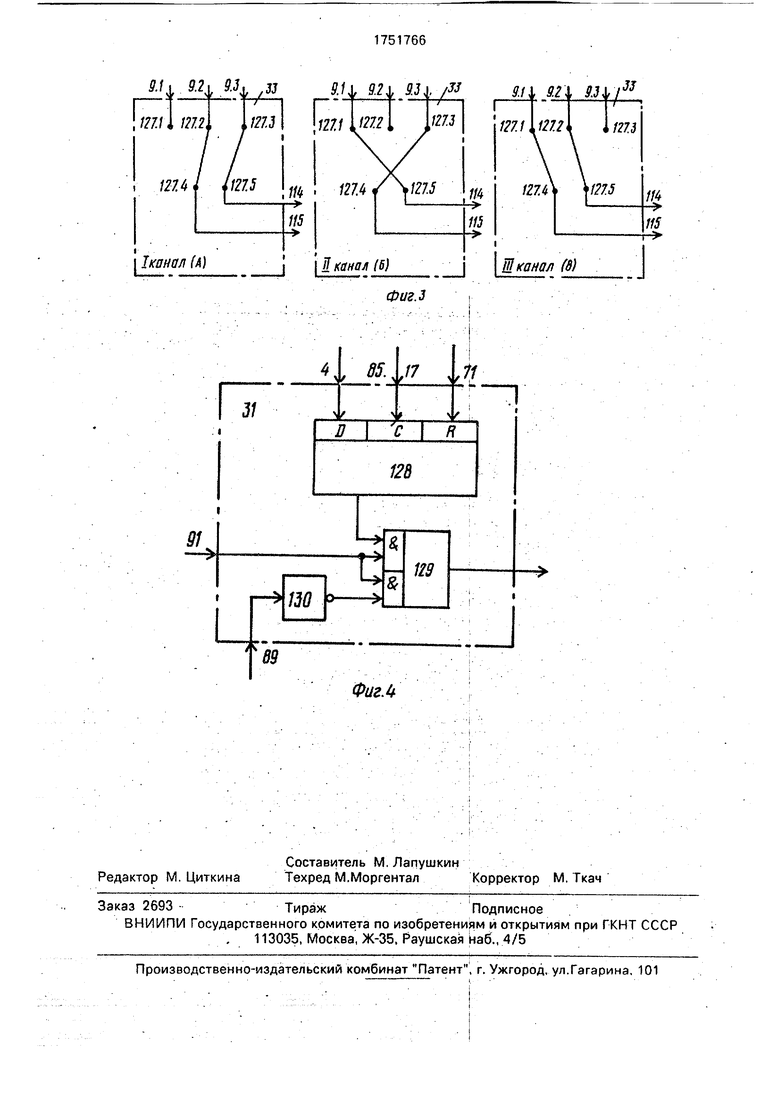

На фиг.1а-1г представлена структурная схема одного канала мажоритарно-резервированного интерфейса памяти; на фиг.2 соединение трех каналов устройства; на фиг.З - выполнение коммутационного блока управления каждого канала устройства; на фиг.4 - пример выполнения блока пуска счетчиков.

Мажоритарно-резервированный интерфейс памяти (фиг,1а-1г)содержит в каждом канале коммутатор 1 входной информации, коммутатор 2 выходной информации, коммутатор 3 блокировки контроля, коммутатор 4 служебной информации, регистр 5 контроля, первый 6 и второй 7 буферные регистры, блок 8 вентилей, блок 9 мажоритарных элементов, включающий первый 9.1, второй 9.2 и третий 9,3 мажоритарные элементы, регистр 10 управления признаком прерывания, регистр 11 адреса признака прерывания, регистр 12 состояния блоков памяти, регистр 13 состояния устройства ввода-вывода, первый 14 и второй 15 регистры состояния процессора, счетчик 16 временных интервалов, счетчик 17 состояний, счетчик 18 адресов команд, счетчик 19 адресов данных, коммутатор 20 состояния блока памяти, коммутаторы 21 первого, 22 второго и 23 третьего разрядов состояния процессора, первый 24, второй 25 и третий 26 коммутаторы кодов процессора, коммутатор 27 адреса, коммутатор 28 реконфигурации процессора, коммутатор 29 сигналов переполнения счетчика состояний, коммутатор 30 сигналов переполнения счетчика временных интервалов, блок 31 пуска счетчиков, первый блок 32 сравнения, блок 33 управления коммутации, преобразователь 34 кодов, дешифратор 35 отказов, дешифратор 36 состояний блока памяти, дешифратор 37 состояний процессора, первый 38 и второй 39 триггеры сброса, первый 40 и второй 41 триггеры управления реконфигурацией процессора, мажоритарные блоки 42 адреса, 43 управления и 44 информации, элемент И-ИЛИ-НЕ 45 управления контролем, первый 46 и второй 47 мажоритарные элементы начальной установки, мажоритарной элемент 48 управления реконфигурацией процессора, первый элемент 49 И-ИЛИ-НЕ 49, элемент И-ИЛИ 50 управления реконфигурацией процессора, второй 51, третий 52 и четвертый 53 элементы И- ИЛИ-НЕ, первый 54. второй 55, третий 56 и четвертый 57 элементы И-НЕ, первый 58 и второй 59 элементы ИЛИ-НЕ, первый 60, второй 61, третий 62, четвертый 63, пятый 64, шестой 65, седьмой 66 и восьмой 67 элементы И, первый 68, второй 69, третий 70, четвертый 71 и пятый 72 элементы ИЛИ, второй блок 73 сравнения, блок 74 сравнения адресов, дешифратор 75 признаков прерывания, блок 76 элементов НЕ.

Кроме того, на фиг.1а-1г обозначены: группа 77 информационных входов от процессора, группа 78 информационных входов от устройства ввода-вывода (УВВ), группы 79 информационных входов от блоков памяти, первая группа 80 межканальных выходов канала, первая 81 и вторая 82 группы г.зжканальных входов канала, группа 83 информационных выходов канала, первый

84.1и второй 84.2 выходы требований пре- рывания канала, первая группа 85 управляющих входов канал а, включающая первый вход 85.1 синхронизации, первый вход 85 2 установки, группу входов 85.3 управления коммутаторы входной информа0 ции, входы 85.4 и 85 5 управления буферны- ми регистрами, вход 85.6 управления коммутатором внутренней информации, входы, 857 сигналов записи, 85.8 увеличения и 85.9 уменьшения содержимого счетчи5 ка адресов команд, входы 85.10 сигналов записи и 85.11 увеличения содержимого счетчика адресов данных, вход 85.12 управления коммутатором адреса, группу входов 85.13 признаков работы внешних блоков,

0 второй 85.14 и третий 85.15 входы синхронизации, второй вход 85.16 установки, четвертый 85.17, пятый 85.18, шестой 85.19, седьмой 85 20 и восьмой 85 21 входы синхронизации, вход 85 22 управления дешиф5 ратором признака прерывания, девятый 85.23 и десятый 85 24 входы синхронизации, первый 85.25 и второй 85.26 входы управления контролем, вторая группа 86 управляющих входов канала, включающая

0 входы первой группы 86.1 имитации нулей и

86.2имитации единиц, первый 86 3 и второй 86 4 входы выбора работы канала, входы второй группы 86 5 имитации единиц 86.6 ° имитации нулей, первый 87.1 и второй 87.2

5 входы сброса канала, выход 88 результатов сравнения канала, первый 89 и второй 90 управляющие входы канала, вход 91 частоты задающего генератора, первый 92.1 и второй 92,2 выходы кода начальной уста0 новки канала, первый 93.1, второй 93.2 и третий 93.3 входы кода сравнения канала, выход 94 сброса канала, выход 95 временных меток канала, группа 96 адресных выходов канала, группа 97 выходов

5 управляющих сигналов памяти, третья 98 и четвертая 99 группы межканальных входов канала, вторая группа 100 межканальных выходов канала, группа 101 входов управляющих сигналов памяти, пятая 102 и ше0 стая 103 группы межканальных входов канала, третья группа 104 межканальных выходов канала, второй межканальный выход 105 канала, третий 106 и четвертый 107 межканальные входы канала, третий меж5 канальный выход 108 канала, пятый 109 и шестой 110 межканальные входы канала, первый межканальный выход 111 канала, первый 112 и второй 113 межканальные входы канала, первый 114 и второй 115 выходы

блока управления коммутацией, четвертый межканальный выход 116 канала, седьмой 117 и восьмой 118 межканальные входы канала, пятый межканальный выход 119 канала, девятый 120 и десятый 121 межканальные входы канала, шестой межканальный выход 122 канала, одиннадцатый 123 и двенадцатый 124 межканальные входы канала, четвертая группа 125 межканальных выходов канала и седьмая группа 126 межканальных входов канала.

Блок 33 управления коммутацией каждого канала (фиг.З) содержит первый 127.1, второй 127.2 и третий 127.3 входные контакты, подключенные соответственно к первому, второму и третьему входам блока 33, и первый 127.4 и второй 127.5 выходные контакты, подключенные соответственно к второму 115 и первому 114 выходам блока 33.

При этом в первом канале (фиг 3) соединены попарно между собой второй входной контакт 127.2 с первым выходным контактом 127.4, а третий входной контакт 127,3 - с вторым выходным контактом 127.5. Во втором канале соединены попарно между собой первый входной контакт 127,1 с вторым выходным контактом 127.5, а третий входной контакт 127.3 - с первым выходным контактом 127.4. В третьем канале соединены попарно между собой первый входной контакт 127.1 с первым выходным контактом, а второй входной контакт 127,2 - с вторым выходным контактом 127,5,

Блок 31 пуска счетчиков (фиг.4) содержит триггер 128 пуска, элемент И-ИЛИ 129 и элемент НЕ 130. Информационный вход D, синхровход С и вход Р сброса триггера 128 пуска соединены с одноименными входами 4,85.17 и 71 соответственно блока 31 пуска счетчиков, импульсный вход 91 которого соединен с первыми входами первого и второго вентилей элемента Й-ИЛИ 129, своим выходом образующего выход блока 31. Выход триггера 128 пуска соединен с вторым входом первого вентиля элемента И-ИЛИ 129. Блокирующий вход блока 31 пуска счетчиков через элемент НЕ 130 соединен с вторым входом второго вентиля элемента И-ИЛИ 129.

Коммутатор 3 блокировки контроля предназначен для разрешения срабатывания контроля, т.е. для разрешения передачи результатов контроля на информационные входы D1-D3 регистра 5 контроля, по-пер- вйх, в зависимости от состояния исправности блоков передающих информацию через интерфейс. Это осуществляется тем, что сигналы с выходов элементов И с первого 60 по третий 62, ранее (в прототипе) передававшиеся непосредственно на входы первых вентилей элементов И-ИЛИ-НЕ с второго 51 по четвертый 53, передаются на них через первую группу входов коммутатора 3

блокировки контроля всегда, когда коммутаторы 24-26 кодов состояний настроены на передачу кодов со своих входов с первого по

(п+2)-й.

Во-вторых, коммутатор 3 блокировки

контроля обеспечивает передачу инверсного состояния сигналов с выходов коммутаторов 21-23 первого-третьего разрядов состояния процессора на входы первых вентилей соответственно второго-четвертого

51-53 элементов И-ИЛИ-НЕ всякий раз, когда коммутаторы 24-26 кодов состояний настроены на передачу сигналов с шины нулевого потенциала.

Поскольку процессор может работать

не только в те моменты времени, когда через интерфейс передается информация процессора, но и в те моменты времени, когда, например, через интерфейс информация не передается (коммутаторы 24-26 настроены

на передачу информации с шины нулевого потенциала). Это позволяет заранее обнаружить отказ (сбой) и соответствующим образом на него отреагировать, т.е. увеличить оперативность контроля устройства,

Блок 76 элементов НЕ предназначен для согласования уровней сигналов управления элементами И-ИЛИ-НЕ 51-53 и сигналов с выходов коммутаторов 21-23, так как при передаче этих сигналов через первую группу информационных входов коммутатора 3 блокировки контроля также инвертирование сигналов происходит на коммутаторах 24-26 кодов состояния.

Второй блок 73 сравнения предназначен для сравнения информации процессора, являющейся признаками результатов его работы, как во время передачи соответствующей информации процессора через интерфейс, так и тогда, когда передача информации процессора не передается через интерфейс, но процессор производит переработку информации. При равенстве сравниваемой информации на выходе блока 73 сравнения нулевой, а при неравенстве единичный сигнал.

Элемент И-ИЛИ-НЕ 45 управления контролем предназначен для передачи с инвертированием результатов контроля сравнением передаваемой через интерфейс

информации (сигналы с выхода первого блока 32 сравнения) и результатов контроля сравнением информации процессора независимо от передачи ее через интерфейс (сигналы с выхода второго блока 73 сравнения). Управление передачей результатов

сравнения сйбтветствующей информации производится соответствующими сигналами на первом 85.25 и втором 85.26 входах управления контроля первой группы 85 управляющих входов канала. Таким образом, при сравнении информации блоками 32 и 73 сравнения на выходе элемента И-ИЛИ-НЕ 45 единичный, а при неравенстве - нулевой уровни сигнала.

Регистр 11 адреса признака прерывания предназначен для приема, хранения и выдачи адреса ячейки памяти, при обращении к которой необходимо вызвать прерывание работы устройства,

Идентификация адреса ячейки памяти, при обращении к которой должно быть вызвано прерывание, производится блоком 74 сравнения адресов путем сравнения содержимого регистра 11 адреса признака прерывания с адресом ячейки памяти, к которой производится обращение.

Поскольку обращение в памяти производится в режимах считывания команд и операндов, а также в режиме записи результатов соответствующих операций, то для разделения этих режимов для формирования сигнала соответствующего прерывания в устройство введены регистр 10 управления признаком прерывания и дешифратор 75 признаков прерывания, Регистр 10 управления признаком прерывания предназначен для приема, хранения и выдачи кода признака режима работы с памятью, при котором необходимо вызывать прерывание, а дешифратор 75 идентифицирует этот код по управляющим сигналам на входе 85.22 первой группы 85 управляющих сигналов канала.

В принципе для динамической коррекции программ достаточно идентифицировать только один из режимов (выборка командного слова из памяти), однако идентификация дополнительно режимов считывания и записи данных расширяет функциональные возможности устройства, та.к как оно может вызывать прерывания для обхода отдельных ячеек, например неисправных, и упрощает программирование вообще, т.е. улучшает удобство эксплуатации устройства.

Устройство работает следующим образом.

Коммутатор 1 входной информации осуществляет передачу информации от внут- ренних узлов интерфейса и внешних устройств на соответствующие входы первого блока 32 сравнения, коммутатора 2 выходной информации, мажоритарного блока 44 информации и на первую группу межканальных выходов канала под управлением

соответствующих кодов на группе 85.3 вхо- - дов первой (руппы 85 управляющих входов канала.

Коммутатор 2 выходной информации

осуществляет передачу информации с выхода мажоритарного блока 44 информации (мажоритарный режим передачи информации) или с выходов коммутаторов 1 входной информации своего и соседних каналов (режимы поканальной передачи информации или передачи информации одного из каналов в трех каналах) под управлением сигналов на выходах 114 и 115 коммутационного блока 33 управления на информационные

входы первого 6 и второго 7 буферных регистров,

Коммутатор 4 осуществляет передачу информации (под управлением сигналов на входе 85.6 первой группы 85 управляющих

входов канала) с выходов первого 6 или второго 7 буферных регистров на информационные входы коммутатора 28, блока 31 пуска счетчиков, регистров 10-14 и счётчиков 16 и 17.

Регистр 5 контроля осуществляет запоминание результатов контроля, поступающих на его информационные входы Di-D/j, и диагностической информации о локализации отказов (информация на входах De-Dm

регистра 5) и состоянии контролируемого оборудования до обнаружения очередного отказа (сигнал на входе Об регистра 5 контроля). Синхронизацию запоминания результатов контроля осуществляют о

синхросигналы на входе 85.1 группы 85 управляющих входов канала вплоть до фиксации отказа хотя бы на одном из выходов Qi-Qs регистра 5 контроля, что обеспечивается работой элемента И-НЕ 55 и элемента

ИЛИ 68,

Установка регистра 5 контроля в исходное нулевое состояние производится с помощью элемента ИЛИ 69 либо сигналом с выхода 85.2 группы 85 управляющих входов

канала, либо сигналом с выхода элемента ИЛИ 72.

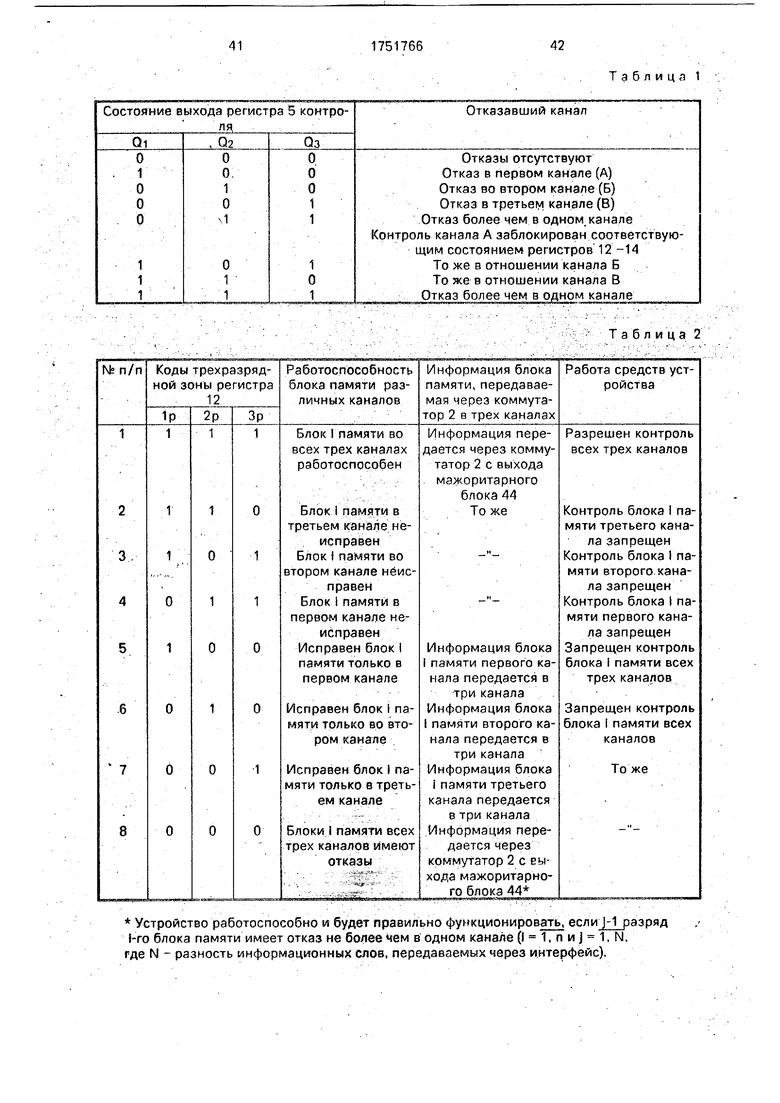

Единичная информация на выходах QI- Qs регистра 5 контроля соответствует отказу в каналах А, Б или В или отказу средств

контроля в соответствии с табл.1 и наличию отказа уже зафиксированного в регистрах 12-14. Код на выгодах Qe-Qm регистра 5 контроля идентифицирует оборудование, в котором возник обнаруженный отказ.

При отказе более чем в одном канале отказавший канал определяется тестированием, например, путем переключения устройства в поканальный режим работы.

Буферные регистры 6 и 7 осуществляют (под воздействием сигналов на входах 85.4

и 85.5 группы 85 управляющих входов канала) либо временное хранение информации (наличие упомянутых сигналов), либо пропуск ее без запоминания

Использование двух буферных регистров повышает производительность устройства путем распараллеливания передачи информации, при этом информация с выхода первого буферного регистра 6 подается на информационный выход 83 канала и на информационные входы счетчиков адресов 18 команд и 19 данных Кроме того, информация с выходов буферных регистров 6 и 7 подается на информационные входы коммутатора 4.

Блок 8 вентилей формирует сигналы управления коммутатором 2 выходной информации в зависимости от сигналов на выходах коммутаторов 24-26 кодов состояний, определяющих состояние сигналов на выходах элементов И 60-65 и элемента И- ИЛИ-НЕ49.

Для передачи информации каналов через коммутатор 2 выходной информации по мажоритарному принципу на выходе элемента И-ЙЛИ-НЕ 49 вырабатывается низкий уровень сигнала, обеспечивающий нулевые сигналы на выходах блока 8 вентилей (на вторые входы 86.5 имитации единиц и 86.8 имитации нулей группы 86 управляющих сигналов, за исключением случаев, описанных ниже, постоянно лоступают единичные сигналы). При передаче информации через коммутатор 2 из одного какого-либо к анала на выходе элемента И-ИЛИ-НЕ 45 присутствует единичный сигнал, поэтому состояние сигналов на выходах блока 8 вентилей однозначно соответствует состоянию сигналов на выходах элементов И 63-65.

Сигнаяы с выходов блока 8 вентилей передаются через мажоритарные элементы $.1-9.3 блока 9 по мажоритарному принципу с инвертированием сигнала. Для проверки работоспособности мажоритарных элементов 9,1-9 3 блока 9, а также для формирования истинной информации на выходах блока 9 мажоритарных элементов при отказе средств реконфигурации устройства не более чем в двух каналах интерфейса используются сигналы на вторых входах 86.5 имитации единиц и 86.6 имитации нулей группы 86 управляющих входов канала. При формировании нулевых сигналов на втором входе 86.5 имитации единиц в одном канале и втором входе 86.6 имитации нулей в другом канале на выходах блоков 9 мажоритарных элементов во всех трех каналах формируется истинная информация средств реконфигурации третьего (исправного) «знала, что обеспечивается установкой единичной информации на выходе блока 8 вентилей одного канала, нулевой информации - второго канала и истинной

информации - третьего (исправного) канала.

Регистр 12 состояния памяти предназначен для приема, хранения и выдачи информации о состоянии блоков памяти,

0 информация которых передается через интерфейс. Состояние регистра 12 использу- - ется в устройстве для управления передачей информации через интерфейс, а также для управления контролем информации, пере5 даваемой через интерфейс и блоков-источников этой информации Каждая трехразрядная зона регистра 12 указывает состояние исправности соответствующего блока памяти и управляет контролем и ре0 конфигурацией тракта передачи информации при обращении к соответствующему блоку памяти

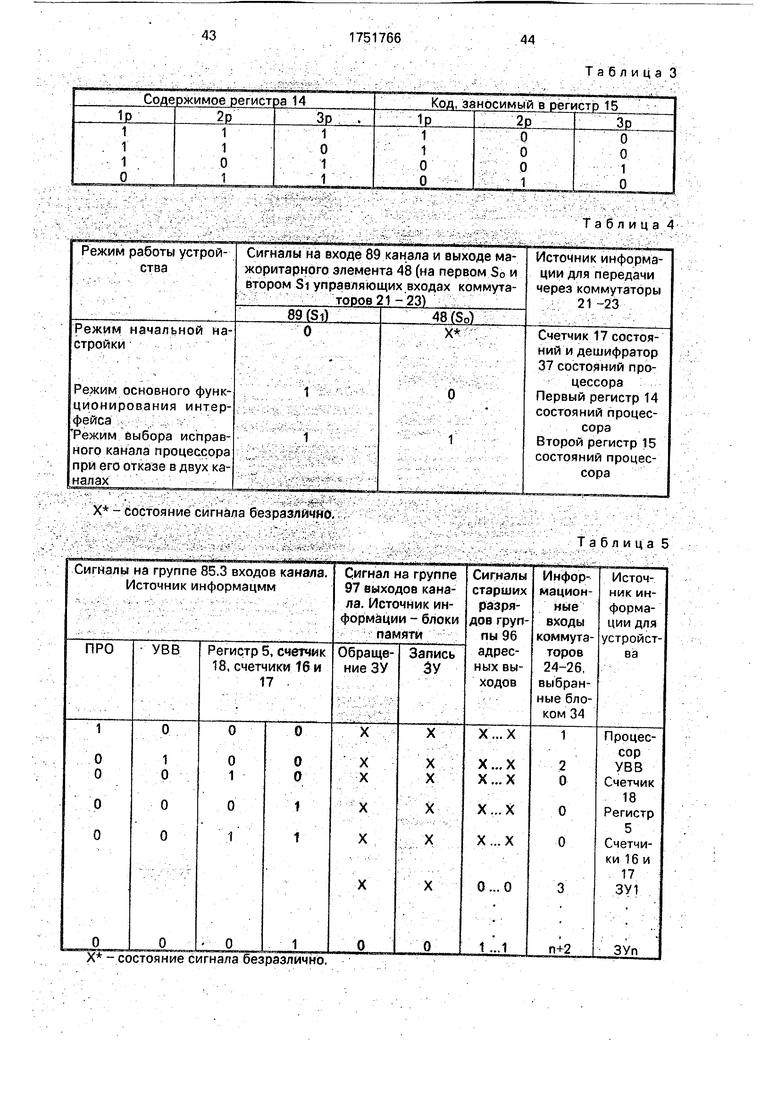

Табл.2 поясняет назначение кодовтрех- разрядных зон регистра 12

5 Перед началом работы регистр 12 сбрасывается сигналом с выхода элемента ИЛИ 71. Результаты начальной настройки устройства (будет описано ниже) и результаты тестирования всех блоков памяти записыва0 ются в регистр 12 состояния памяти, поступая на его информационный вход с группы 77 входов канала через коммутатор 1. мажоритарный блок 44, коммутатор 2, регистр 6 и коммутатор 4

5 Регистр 13 состояния УВВ работает идентично трехразрядной зоне описанного регистра 12 Отличие составляет начальная установка регистра 13, которая происходит по сигналу с выхода элемента ИЛИ 72

0 Первый регистр 14 состояния процессора идентифицирует состояние процессора, его назначение и работа идентичны работе одной трехразрядной зоне регистра 12, описанной выше Поскольку процессор являет5 ся основным управляющим звеном то отказы трех каналов процессора (код 000 в регистре 14), как правило, приводит к отказу системы в целом, за исключением случаев, когда отказывают отдельные разряды

0 выходных шин процессора С целью возврата устройства к работоспособной конфигурации при отказе в двух каналах процессора используется второй регистр 15 состояний, процессора, работа которого производится

5 совместно с коммутатором 28 перестройки процессора в двух режимах - в режиме записи информации, когда коммутатор 28 пе- редазт информацию с первой группы информационных входов, или в режиме кольцевого сдвига, когда коммутатор 28 передает информацию с выхода на информационный вход регистра 15 со сдвигом (кольцевым) на один разряд

Записываемая в регистр 15 информация зависит от информации, заносимой в регистр 14. и производится в соответствии с таблицей 3.

Режим записи или сдвига в регистр 15 определяется состоянием выхода мажоритарного элемента 48 и, соответственно, триггеров 40 и 41 управления реконфигурацией процессора. Поскольку при кодах 000, 001я. 010 и 100 в регистре 14 блокируется контроль процессора и, соответственно, возможность включения триггеров 41 и 40, то в этом случае исключается переключение работы регистра 15 в режим кольцевого сдвига и управление работой интерфейса от регистра 15 Поэтому указанные коды для табл.3 безразличны.

Первый (второй) регистр 14 (15) состояний процессора устанавливается в исходное состояние сигналом с выхода элемента 71 (72) ИЛИ.

Счетчик 16 временных интервалов формирует временные метки, определяющие время тестирования устройства при каждой его конфигурации, те является делителем частоты для Сигналов частоты задающего генератора, поступающих на счетный вход счетчика со входа 91 канала через блок 31 пуска счетчиков

Установка счетчика 16 в исходное нулевое состояние производится сигналом с выхода элемента ИЛИ 71 Поскольку счетчик 16 используется кроме этого и в качестве части сторожевого таймера (будет описано ниже), то в него предусмотрена запись информации (кода пересчета счетчика), подаваемой на его информационный вход с одного из источников коммутатора 1 и синхронизируемой сигналом на входе 85 18 канала.

Сигналы с выхода переполнения счетчика 16 передаются через коммутатор 30 на сметный вход счетчика 17 состояний через элемент ИЛИ-НЕ 59 и мажоритарный Зле- мент46 на вход элемента ИЛИ 72 для формирования сигналов сброса, если отсутствует сигнал на входе 89 канала

Счетчик 17 состояний формирует коды реконфигурации процессора и блока памяти, идентифицируемого первой трехразрядной зоной регистра 12, при выборе исправной конфигурации блоков при включении интерфейса в работу При начальной настройке исправной конфигурации блоков млад шие два разряда счетчика 17 состояний определяют выбор исправной конфигурации процессора, а следующие два разряда - исправной конфигурации блока памяти

Состояния этих пар разрядов дешифрируются дешифратором 37 состояния процессора и дешифратором 36 состояния блока памяти. При этом процессор и блок памяти подключается к интерфейсу по мажоритарному принципу при равенстве указанных пар разрядов коду 00, при коде

0 01 происходит работа от первого канала процессора (блока памяти), при коде 10 - от второго канала, а при коде 11 - от третьего канала процессора (блока памяти)

Кроме того, все разряды счетчика 17 со5 стояний совместно со счетчиком 16 временных интервалов в устройство выполняют роль сторожевого таймера, переполнение которого используется для формирования временных меток, передаваемых на выход

0 95 канала (при отсутствии сигнала на входе 90 устройства), либо для приведения устройства в исходное состояние путем его сброса и установки кода 11 на выходах 92,1 и 92,2 кода начальной установки канала (при еди5 ничном сигнале на входе 90 канала).

Использование сторожевого таймера для начальной установки устройства происходит в тех случаях, когда для выполнения отдельных подпрограмм выделяется задан0 ное время Невыполнение этих подпрограмм классифицируется как сбой программы, и переполнение сторожевого таймера приводит устройство в исходное состояние, а состояние 11 триггеров 38 и 0

5 39 указывает причину установки в исходное состояние

Для задания соответствующих интервалов работы сторожевого таймера в счетчики 16 и 17 производится запись соот0 ветствующих кодов, задаваемых на одном из входов коммутатора 1, Поскольку счетчики 16 и 17 могут сами обеспечивать сигналы сброса на выходе элемента ИЛИ 72, то сброс этих счетчиков производится сигнала5 ми с выхода элемента ИЛИ 71

Счетчик 18 адресов команд (счетчик 19 адресов данных) предназначен для формирования адресов команд (данных) при обращении за ними к памяти либо для адресации

0 элементов массивов данных при перемещении их в памяти.

Занесение начальных адресов в счетчик 18 (19) производится следующим образом. Код начального адреса с групп 77 или 79

5 информационных входов устройства через коммутаторы I, мажоритарный блок 44 информации, коммутатор 2 и буферный регистр 6 подается на информационные входы D счетчика 18 (19), на синхровход С которого подается синхросигнал по входу 85 7 (85.10)

сигнала записи первой группы 85 управляющих входов канала, по которому начальный адрес записывается в счетчик 18 (19). При подаче синхросигнала на вход 86.8 (85.11) увеличения содержимого счетчика первой группы 85 управляющих входов канала содержимое счетчика 18 (19) увеличивается на единицу. Уменьшение на единицу содержимого счетчика 18 производится подачей сигнала на вход 85 9 группы 85 входов устройства.

Установка в исходное нулевое состояние счетчиков 18 и 19 производится сигналом с выхода пятого элемента,ИЛИ 72.

Для запоминания в памяти адреса очередной команды он с выхода счетчика 18 адресов команд передается на группу 83 информационных выходов устройства через коммутатор 1, мажоритарный блок 44 информации, коммутатор 2 и буферный регистр 6.

Передача адресов команд или данных с выходов счетчиков 18 и 19 на группу 96 адресных выходов канала производится через коммутатор 27 адреса и мажоритарный блок 42 адреса. При нулевом сигнале на входе 85.12 первой группы 85 управляющих входов канала через коммутатор 27 адреса передается содержимое счетчика 18 адреса команд, а при единичном сигнале - содержимое счетчика 19 адреса данных.

Коммутатор 20 состояний блока памяти предназначен для передачи на соответствующие информационные входы коммутаторов 24-26 кодов состояния кодов, идентифицирующих состояние первого блока памяти, либо с выходов дешифратора 36 состояний блока памяти в режиме работы начальной настройки исправной конфигурации блоков при низком уровне сигнала на первом управляющем входе 89 канала, либо с выходов первой трехразрядной зоны регистра 12 состояний памяти в процессе основной работы устройства при единичном сигнале на первом управляющем входе 89 канала. Из сказанного следует, что признаком задания режима работы устройства по начальной настройке исправной конфигурации подключаемых блоков либо основной его работы по передаче информации между блоками через интерфейс является отсутствие или наличие сигнала на первом управляющем входе 89 канала.

Коммутаторы первого 21, второго 22 и третьего 23 разрядов состояния процессора предназначены для передачи на соответствующие информационные входы коммутаторов 24-26 кодов состояния кодов, идентифицирующих состояние процессора, либо с выходов дешифратора 37 состояний

проц эссора в режиме начальной настройки исправнойчконфигурации процессора при нулевом сигнале на первом управляющем входе 89 канала (состояние сигнала на выходе мажоритарного элемента 48 управления перестройкой процессора в данном режиме на работу коммутаторов 21-23 не оказывает влияния, поскольку выходы дешифратора 37 состояний процессора подключены к пер0 вым О и вторым 1 информационным входам коммутаторов 21-23), либо с выходов первого регистра 14 состояний процессора в режиме основного функционирования интерфейса при единичном сигнале на первом

5 управляющем входе 89 канала и нулевом сигнале на выходе мажоритарного элемента 48 управления перестройкой процессора, либо с выходов второго регистра 15 состояний процессора в режиме настройки исп0 равной конфигурации процессора при его отказах в двух каналах, что определяется единичным состоянием сигналов на первом управляющем входе 89 канала и на выходе мажоритарного элемента 48

5 В табл 4 приведены источники информации, передаваемой через коммутаторы 21-23, и условия передачи этой информации

Первый 24, второй 25 и третий 26 ком0 мутаторы кодов состояний предназначены для передачи содержимого регистра 12 состояний памяти или кода с выхода дешифратора 36 состояний памяти, содержимого регистра 13 состояний УВВ и содержимого

5 первого регистра 14 состояний процессора, или информации с выходов дешифратора 37 состояний процессора, или кода с выходов второго регистра 15 состояний процессора, либо нулевого кода (состояния

0 шины нулевого потенциала) на первые входы соответственно четвертого 63, пятого 64 и шестого 65 элементов И, а инверсных значений этих кодов - на первые входы соответственно первого 60, второго 61 и третьего 62

5 элементов И. Выбор информационного входа коммутаторов 24-26 кодов состояния для передачи информации соответствующего источника осуществляется кодом на выходе преобразователя 34 кодов. При

0 передаче содержимого регистра 5 контроля, счетчика 18 адресов команд или счетчика 16 временных интервалов и счетчика 17 состояний источников кода для передачи кода через коммутаторы 24-26 является

5 шина нулевого потенциала Поэтому информация данных узлов интерфейса передается на его группу 83 информационных выходов по мажоритарному принципу, а средства контроля в момент передачи их информации могут разрешать только контроль процессора вторым блоком 73 сравнения.

Передаче информации соответствующего источника через устройство (и, соответственно, через коммутатор 1 входной информации) сопутствует выработка соответствующих сигналов на группах 85.3 и 85.13 управляющих входов канала, старших разрядах группы 96 адресных выходов канала и на группе 97 выходов управляющих сигналов памяти (предполагается, что старшие разряды группы 96 адресных выходов канала обеспечивает выбор одного из п блоков памяти, а младшие разряды - соответствующую ячейку этого блока памяти).

Данные сигналы преобразуются блоком 34 в код управления коммутаторами 24-26 в соответствии с табл.5

Коммутатор 29 сигналов переполнения счетчика 17 состояний предназначен для передачи элементом 47 сигнала переполнения счетчика 17 на выход 95 временных меток канала при нулевом сигнале на втором управляющем входе 90 канала либо на третий вход пятого элемента ИЛИ 72 и на вторые входы установки единичном сигнале на втором управляющем входе 90 канала Таким образом, под управлением сигнала на входе 90 канала производится либо установка устройства в исходное состояние с выработкой кода 11 на выходах 92 1 и 92 1 канала, либо формирование сигнала на выходе 95 канала, который может использоваться для прерывания работы устройства

Коммутатор 30 сигналов переполнения счетчика 16 временных интервалов предназначен для подачи на счетный вход счетчика 17 состояний и на инверсный вход второго элемента ИЛИ-НЕ 59 синхросигналов либо с выхода переполнения счетчика 16 временных интервалов при нулевом сигнале на выходе первого элемента ИЛИ-НЕ 58, либо с выхода блока 31 пуска счетчиков, соединенного со счетным входом счетчика 16 временных интервалов Таким образом, коммутатор 30 регулирует частоту синхросигналов на счетном входе счетчика 17 и инверсном входе элемента ИЛИ-НЕ 59, которая равна либо частоте синхросигналов на входе91 канала, либо уменьшена в2г раз, где г- разрядность счетчика 16 временных интервалов. Различная частота изменения состояния счетчика 17 (частота реконфигурации процессора и первого блока памяти при начальной настройке исправной конфигурации соединения их с интерфейсом) определяется условием формирования сигналов сброса на входах 87.1 и 87.2 сброса канала. При сбросе канала устройства сигналом, поступившим на его вход 87.1,

синхросигналы на счетный вход счетчика 17 поступают с выхода переполнения счетчика 16,. при сбросе канала сигналом, поступившим на вход 87 2 устройства, синхросигналы на счетный вход счетчика 17 поступают с выхода блока 31 пуска счетчиков, минуя счетчик 16 временных интервалов (обеспечивается низким уровнем сигналов на выходе элемента И-НЕ 57 и на входе 89

0 канала)

Блок 31 пуска счетчиков (см фиг.4) предназначен для разрешения или блокировки пропуска сигналов тактовой частоты с входа 91 частоты задающего генератора канала

5 При н изком уровне сигнала на первом управляющем входе 89 канала (режим исходной настройки работоспособной конфигурации интерфейса и блоков, подключаемых к интерфейсу) сигналы тактовой

0 частоты с входа 91 канала устройства на выход блока 31 пуска счетчиков передаются безусловно, поскольку высокий уровень сигнала на выходе элемента НЕ 130 открывает второй вентиль элемента И-ИЛИ 129.

5 При высоком уровне сигнала на первое управляющем входе 89 канала второй вентиль элемента И-ИЛИ 129 закрыт и импульсы частоты задающего генератора с входа 91 канала на выход блока 31 пуска счетчиков

0 передаются только при включенном триггере 128 пуска счетчиков При начальном сбросе устройства триггер 128 устанавливается в исходное выключенное состояние сигналом с выхода четвертого элемента 5 ИЛИ 71 Для включения триггера 128 на его информационный вход D подается единичный сигнал, а на синхровход С триггера 128 - синхросигнал с четвертого входа 85.17 синхронизации первой группы 85 управляющих

0 входов канала

Первый блок 32 сравнения предназначен для сравнения информации двух соседних каналов и выработки нулевого сигнала на своем выходе при равенстве информа5 ции и единичного сигнала - при неравенстве информации двух каналов

Коммутационные блоки 33 управления (фиг.1 и 3) предназначены для коммутации сигналов, формируемых на выходах ма0 жоритарных элементов 91.-93 блока 9 мажоритарных элементов с целью преобразования этих сигналов (зависящих от состояния соответствующих трёхразрядных зон регистра 12 состояния), одинаковых во всех

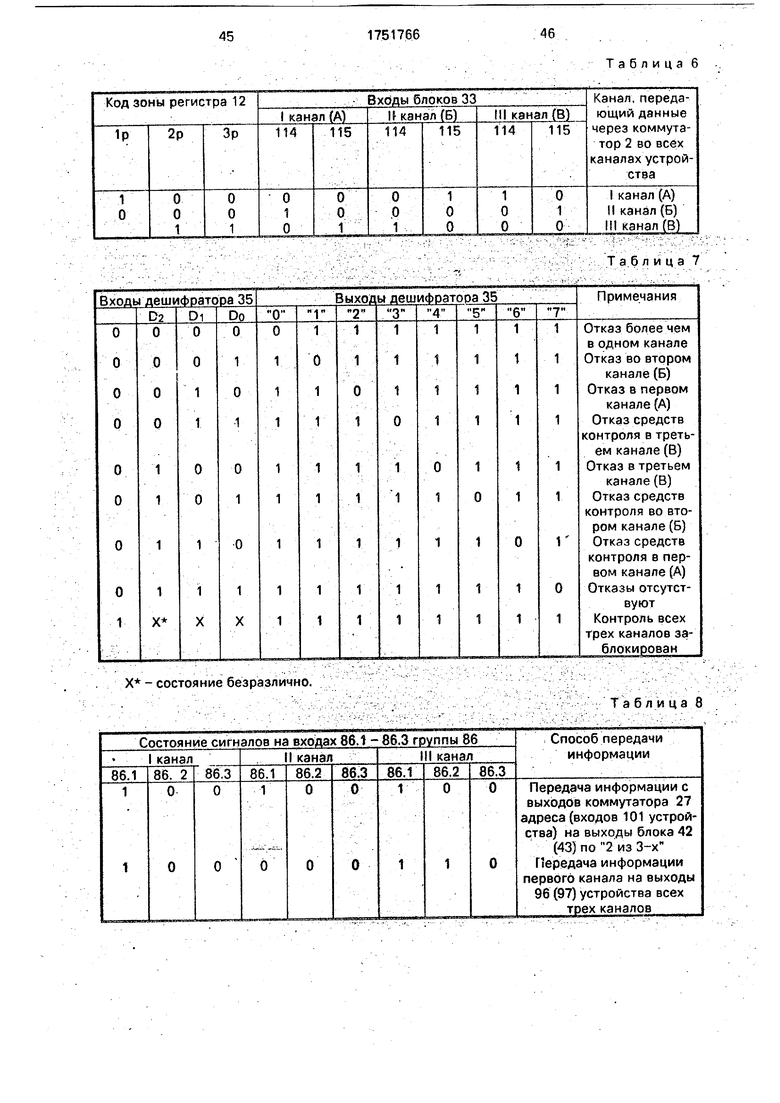

5 трех каналах, в соответствующие различные в трех каналах сигналы управления коммутатором 2 выходной информации Данное преобразование происходит при передаче через коммутаторы 24-26 кодов, равных 100, 010 или 001, при которых требуется перестройка различных каналов устройства на передачу информации только от одного из трех оставшегося исправным блока-источника информации. В этом случае на выходах 114 и 115 коммутационных блоков 33 в трех каналах устройства формируются коды в соответствии с табл.6.

Дешифратор 35 отказов преобразует коды результатов сравнений в инверсное значение унитарного кода, идентифицирующего отказавший канал в соответстбии с табл.7, при нулевом значении сигнала на выходе первого элемента И-ИЛИ-НЕ 49, когда исправны как минимум два канала блоков-источников контролируемой информации. При единичном значении сигнала на выходе первого элемента И-ИЛИ-НЕ 49, когда имеется отказ не менее чем в двух каналах блоков-источников контролируемой информации либо когда работа устройства производится поканально (передача информации каждого канала осуществляется независимо от других каналов), дешифрация состояния сигналов на информационных входах DcrD2 дешифратора 35 отказов блокируется.

Назначение дешифраторов состояния 36 памяти и 37 процессора состоит в преобразовании кодов соответствующих зон счетчика 17 состояний (см. пояснение работы счетчика 17 состояний) в трехразрядные унитарны коды, управляющие перестройкой процессора и блока памтяи при начальной настройке исправной конфигурации устройства, т.е при нулевом сигнале на первом управляющем входе 89 канала При единичном состоянии сигнала на входе 89 канала (режим основного функционирования устройства) дешифраторы 36 и 37 в работе устройства не участвуют, поэтому их состояние в данном режиме безразлично.

Первый 38 и второй 39 триггеры сброса предназначены для фиксации и индикации сигналов начальной установки устройства. Состояния триггеров 38 и 39 могут, во-первых, идентифицировать предысторию работы устройства, во-вторых, использоваться для занесения в счетчик 18 адресов команд начальных адресов подпрограмм, соответствующих каждому из сигналов началоной установки. В устройстве предусмотрены четыре случая начальной установки, каждый из которых определяется соответствующими сигналами.

1. Началу работы устройства предшествует сигнал сброса, поступающий в устройство по первому входу 87 1 сброса (который триггеры 38 и 39 сброса устанавливают в состояние 1). Он, поступая на выходы четвертого 71 и пятого 72 элементов ИЛИ, устанавливает все элементы памяти устройства в исходное состояние. Кроме того, сигналы с выхода пятого элемента ИЛИ 72

поступают на выход 94 сброса канала для приведения в исходное состояние блоков, подключаемых к устройству.

При этом на выходе четвертого элемента И-ИЕ 57 вырабатывается единичный по0 тенциал, а на выходе первого элемента ИЛИ-НЕ 58 - нулевой потенциал, по кото- рому на выход коммутатора 30 будут поступать сигналы с выхода переполнения счетчика 16 временных интервалов, т.е. ча5 сота поступления сигналов на счетный вход счетчика 17 состояний и на инверсный вход второго элемента ИЛИ-НЕ 59 в 2 раза меньше частоты сигналов задающего генератора на входе 91 канала, После поступления сиг0 нала сброса устройства по первому входу 87.1 сброса устройство начинает работу в режиме начальной настройки исправной конфигурации сопрягаемых с интерфейсом блоков, как будет описано ниже

52 При возникновении в процессе работы устройства нештатных ситуаций, приводящих к искажению информации как в самом устройстве, так и в сопрягаемых с ним блоках, например кратковременного

0 пропадения напряжения по цепям питания, установка устройства в исходное состояние и его начальная настройка начинается по сигналу, поступающему по второму входу 87 2 сброса канала Отличие воздействия на

5 устройство данного сигнала от описанного выше состоит в том, что он идентифицируется состоянием 01 триггеров 38 и 39 соответственно При этом на выходе четвертого элемента И-НЕ 57 формируется нулевой по0 тенциал, а на выходе первого элемента ИЛИ-НЕ 58 - единичный потенциал, так как на первом управляющем входе 89 канала присутствует нулевой потенциал до тех пор, пока интерфейс не настроится на исправ5 ную конфигурацию внешних блоков. При единичном сигнале на выходе первого элемента ИЛИ-НЕ 58 коммутатор 30 передает сигналы на счетный вход счетчика 17 состояний и на инверсный вход второго элемента

0 ИЛИ-НЕ 59 сигналы с выхода блока 31 пуска счетчиков, а не с выхода переполнения счетчика 16 временных интервалов Частота сигналов на выходе коммутатора 30 равна частоте сигналов задающего генератора на

5 входе 91 канала, поэтому настройка устройства на исправную конфигурацию при несанкционированных прекращениях его работы происходит в 2 раза быстрее, чем при настройке перед началом основного функционирования что особенно важно

при работе устройства в контуре управления технологическим процессом, прекращение которого экономически невыгодно, либо при работе устройства в медицинской аппаратуре, могущей повлиять на здоровье человека.

3.Время поиска исправной конфигурации, стыкуемых к интерфейсу блоков (контроль работоспособности блоков, например тестирование, обеспечивается самими блоками, передача информации между которыми осуществляет интерфейс, причем если за время тестирования не получена норма результатов контроля, то интерфейс автоматически изменяет конфигурацию соединений между процессором и тестируемым блоком памяти, формирует сигнал сброса на выходе пятого элемента ИЛИ 72, сбрасывает соответствующие элементы памяти интерфейса, формирует сигнал сброса на выходе 94 канала и продолжает работу с этого исходного состояний) определяет частота сигналов на выходе коммутатора 30, которые на вход пятого элемента ИЛИ 72 поступают через второй элемент ИЛИ-НЕ 59 и первый мажоритарный элемент 46 начальной установки. Данный сигнал не изменяет состояния первого 38 и второго 3$ триггеров сброса, поэтому цикл работы повторяется с прежним их состоянием и про- текает так, как описано выше. Отличия при этом составляет лишь состояние первых четырех разрядов счетчика 17 состояний, определяющих конфигурацию соединений процессора и блока с интерфейсом в режиме начальной настройки, как будет описано ниже.

4.При возникновении нештатных ситуаций типа ухода с программы (контроль хода программы производится сторожевым таймером - счетчики 16 и 17 устройства, в которые заносятся уставки, определяющие время выполнения каждой программы или подпрограмм), когда очередная уставка до переполнения счетчика 17 в него не внесена,, происходит переполнение счетчика 17, а его сигнал переполнения, пройдя через второй мажоритарный элемент 47 начальной установки и коммутатор 29, поступает на соответствующие входы пятого элемента ИЛИ 72 и первого 38 и второго 39 триггеров сброса, устанавливая их в состояние 11. В данном режиме работы на первом управляющем входе 89 канала присутствует сигнал высокого уровня, поэтому работа устройства в данном случае определяется состоянием регистров 12-15, а не состоянием счетчика 17. При таких мягких отказах типа сбоев (отказов) в программе производится смена программ путем занесения

соответствующих кодов в счетчик 18 адресов команд. Таким образом, состояние три 11 аров 38 и 39 отказов определяет возникающие в устройстве ситуации.

Установка триггеров 38 и 39 сброса о

исходное состояние 00 производится сигналом по второму входу 85.16 установки первой группы 85 управляющих входов канала.

0 Первый триггер 40 перестройки процес- сора управляет перестройкой процессора при втором отказе (отказе процессора в двух каналах). Признаком второго отказа, зафиксированного инт ерфейсом, является

5 включенный второй триггер 41 управления перестройкой процессора, а признаком того, что отказавший блок - это процессор, является сигнал на выходе Qe регистра 5 отказов. В этом случае на выходе восьмого

0 элемента И 67 формируется единичный сигнал, который через мажоритарный элемент 48 управления перестройкой процессора поступает на информационный вход D первого триггера 40 управления перестройкой

5 процессора и заносится в него по заднему фронту сигнала на его синхровходе С. Синхросигналами для триггера 40 являются импульсы на входе 91 частоты задающего генератора канала

0 Единичное состояние сигналов на выходе мажоритарного элемента 48 (второй отказ процессора) и на выходе триггера 40 (второй отказ процессора засинхронизиро- ван синхросигналом частоты задающего ге- о

5 нератора) разрешает прохождение этих синхросигналов (полноценных сигналов во всех трех каналах, которые могли формироваться при отсутствии триггера 40) через седьмой элемент И 66 и третий элемент

0 ИЛИ 70 на синхровход С второго регистра 15 состояний процессора, который в этом случае работает в режиме кольцевого сдвига.

Установка триггера 40 в исходное нуле5 вое состояние производится сигналом с выхода пятого элемента ИЛИ 72.

Установка триггера 41 в исходное нулевое состояние производится одновременно с обнулением регистра 5 отказов (см, выше),

0 а установка в единичное состояние будет описана ниже при пояснении работы элемента И-ИЛИ 50.

Мажоритарный блок 42 адреса (43 управления) предназначен для передачи адре5 сов (управляющих сигналов) на группу 96 адресных выходов (группу 97 выходов управляющих сигналов памяти) канала с выходов коммутатора 27 адреса (группы 101 входов управляющих сигналов памяти канала) по мажоритарному принципу (по 2 из

3-х) или с перестройкой блока 42 (43) на передачу информации из одного любого канала в три канала или поканально. Перестройка мажоритарных блоков 42 и 43 производится сигналами с входов 86.1-86.3 второй группы 86 управляющих входов канала.

При передаче сигналов через мажоритарный блок 42 (43) по 2 из 3-х на вход 86.1 имитации О группы 86 входов канала подается потенциал единичного сигнала, я на вход 86.2 имитации 1 и первый вход 86.3 выбора работы канала - потенциалы нулевого уровня. В этом случае на выходах мажоритарных блоков 42 и 43 формируются сигналы, значение которых равно значению одноименных сигналов дву#из трех каналов на входах блоков 42 и 43, что соответствует их работе по мажоритарному принципу.

Для передачи сигналов с выходов коммутатора 27 адреса (входов 101 канала) одного канала устройства на выходе блоков 42 (43) всех трех каналов устройства необходимо в данном канале работу блока 42 (43) организовать в мажоритарном режиме, как сказано выше, в другом канале сигналы на входах 86,, 82.2 и 86,3 группы 86 должны иметь значение 000, а в третьем канале - значение 110.

Состояние сигналов на входах 86,1-8.63 группы 86 во всех трех каналах устройства при передаче информации с первого, второго или третьего канала в три канала поясняется табл.8.

Для передачи адресов управляющих сигналов (на выходы мажоритарного блока 42 (43) поканально сигналы на входах 86.1- 86.3 группы 86 должны во всех трех каналах иметь значение 101.

Для выдачи на выходы мажоритарных блоков 42 и 43 соответствующего канала устройства потенциальных сигналов логического нуля или логической единицы на входах 86.1, 86.2 и 86.3 группы 86 входов в соответствующем канале устройства должны устанавливаться соответственно коды 001 и/или 111,

Таким образом, мажоритарные элементы блоков 42 и 43 обеспечивают преобразование входных сигналов по мажоритарной логике, передачу сигналов одного любого канала во все три канала устройства, а также поканальную передачу сигналов. Это обеспечивает как передачу функциональных сигналов с выходов коммутатора 27 и входов 101 устройства, так и передачу потенциальных сигналов логического нуля или логической единицы, что дает возможность организовать полную проверку мажоритарных элементов при наличии таковых в блоках памяти.

Мажоритарный блок 44 информации предназначен для передачи по мажоритарному принципу информации с выходов коммутатора 1 входной информации и межканальных входов 81 и 82 канала на соответствующий вход коммутатора 2.

Мажоритарные элементы 46-48 пред0 назначены для передачи соответствующих сигналов по мажоритарному принципу.

Первый элемент l/1-ИЛИ-НЕ 49 предназначен для управления работой коммутатора 2 (через блоки 8 вентилей и 9 мажори5 тарных элементов, а также через коммутационный блок 33 управления - по входам S0 и Si коммутатора 2) и для блокировки работы дешифратора 35 отказов при наличии отказов более чем в одном канале соответ0 ствующего блока, Работу первого элемента И-ЙЛИ-НЕ 49 рассмотрим при описании назначения элементов И 60-65.

Элемент И-ИЛИ 50 предназначен для включения второго триггера 41 управления

5 перестройкой процессора при отказе процессора в двух каналах. Признаком отказа более чем в одном канале устройства является единичное состояние первого QI, второго Q2 и третьего Оз выходов регистра 5

0 отказов либо наличие сигнала хотя бы на одном из выходов Qi-Оз регистра 5 отказов, приводящих к формированию сигнала на выходе первого элемента ИЛИ 68, и наличие единичного сигнала на выходе QS регистра

5 отказов, запись которого в регистр 5 производится с выхода третьего элемента И-НЕ 56.

Второй 51 - четвертый 53 элементы И- ИЛИ-НЕ предназначены для передачи ин0 версного состояния сигналов контроля с соответствующих выходов дешифратора 35 контроля на информационные входы Di-Da регистра 5 контроля при отсутствии сигналов на выходах соответственно первого 60,

5 второго 61 и третьего 62 элементов И, если через коммутаторы 24-26 передается информация не с шины нулевого потенциала, или при единичном состоянии выходов коммутаторов 21-23 (сигналы отсутствуют на

0 выходах блока 76 элементов Н Е), если через коммутаторы 24-26 передается информация с шины нулевого потенциала (в первом случае через коммутатор 3 передаются сигналы с выходов элементов И 60-62, а во

5 втором - с выходов коммутаторов 21-23 через блок 76 элементов НЕ). При наличии сигнала на выходе первого (второго или третьего) элемента И 60 (61 или 62) или на выходах блока 76 элементов НЕ на выходе элемента И -ИЛИ-НЕ 51 (52 и 53) устанавливается сигнал низкого уровня, т.е. блокируется запись результатов контроля соответствующего канала в регистр 5 Это производится тогда, когда в регистрах 12-14 уже зафиксирован отказ данного канала блока-источника информации

При отказе блоков 32 или 73 сравнения в каком-либо канале на выходе 3, 5 или 6 дешифратора 35 отказов вырабатывается сигнал низкого уровня, который инвертируется первым элементом И-НЕ 54 и запоминается в регистре 5 контроля. После запоминания в регистре 5 контроля информации об отказе средств контроля на выходе элемента И-НЕ 54 постоянно устанавливается единичное состояние, что исключает потерю информации об отказе средств контроля.

Второй элемент И-НЕ 55 предназначен для передачи с инвертированием синхросигнала с первого входа 85 1 группы 85 на синхровход регистра 5 контроля, если в нем не зафиксирован отказ какого-либо блока, т.е. на его выходах Qi-Оз и соответственно на выходе первого элемента ИЛИ 68 сигналы отсутствуют.

Третий элемента И-ДНЕ 56 предназначен для выработки сигнала, если хотя бы в одном канале блока-источника информации зафиксирован отказ соответствующим кодом регистра 12, 13 или 14. Сигнал с выхода элемента И-НЕ 56 запоминается в пятом разряде регистра 5 контроля и при наличии единицы хотя бы на одном из выходов СИСЬ регистра 5 (и, соответственно, на выходе первого элемента ИЛИ 68) обеспечивает срабатывание элемента И-ИЛИ 50 и включение триггера 41.

Четвертый элемент И-НЕ 57 формирует нулевой сигнал на втором входе первого элемента ИЛ И-НЕ 58 только при состоянии 01 триггеров 38 и 39 сброса. Первый элемент ИЛИ-НЕ 58 формирует единичный сигнал на управляющем входе коммутатора 30 только при низких уровнях сигналов на выходе четвертого элемента И-НЕ 57 (работе устройства предшествовал сигнал сброса на втором входе 87.2 сброса канала) и на первом управляющем входе 89 канала (устройство работает в режиме настройки исправной конфигурации стыкуемых с интерфейсом блоков)

Второй элемент ИЛИ-НЕ 59 предназначен для формирования сигналов сброса устройства в режиме начальной настройки (низкий уровень сигнала на первом управляющем входе 89 канала) при появлении синхросигналов на выходе коммутатора 30 сигналов переполнения счетчика 16 временных интервалов (за время тестирования блоков не получена норма результатов контроля).

Первый 60, второй 61 и третий 62 элементы И предназначены для передачи инверсного, а четвертый 63, пятый 64 и шестой 65 элементы И предназначены для передачи прямого значения соответственно первого, второго и третьего разрядов соответствующих зон, регистра 12, либо регстров 13-15,

0 либо выходов дешифраторов 36 и 37 и передаваемых через коммутаторы 24, 25 и 26 кодов состояний соответственно при работе устройства в мажоритарно-резервированном режиме, т.е. при высоком уровне

5 сигнала на втором входе 86.4 поканальной работы второй группы 86 управляющих входов канала. При низком уровне сигнала на входе 86.4 группы 86 входов канала на прямых выходах всех элементов И 60-65 фор0 мируются нулевые сигналы, на инверсных выходах элементов И 63-65 - единичные сигналы, на выходе элемента И-ИЛИ-НЕ 49 формируется единичный сигнал, а на выходах 114 и 115 коммутационных блоков 33 во

5 всех каналах - нулевые сигналы, что настраивает коммутаторы 2 во всех трех каналах интерфейса на передачу информации с выходов коммутаторов 1 входной информации (поканальный режим работы).

0 При работе устройства в мажоритарно- резервированном режиме на прямых выходах четвертого 63 - шестого 65 элементов И формируется коды в соответствии с табл.2, а на выходах первого 60 - третьего 62 эле5 ментов И - инверсные значения этих кодов. При наличии отказа в каком-либо канале{ 0 в табл.2) на выходе соответствующего элемента И 60-62 вырабатывается единичный сигнал, передаваемый через коммутатор 3 и

0 обеспечивающий подачу нулевого сигнала на выход соответствующего элемента И-ИЛИ-НЕ 51-53 независимо от состояния на соответствующем выходе дешифратора 35 контроля, т.е. обеспечивающий блокировку

5 контроля данного канала. Отсюда следует первое назначение элементов И 60-62. Второе назначение элементов И 60-62 - обеспечить передачу информации через интерфейс по 2 из 3-х при наличии отказов

0 в трех каналах блоков-источников дачных для устройства (см. последнюю строку табл.2). В этом случае единичные сигналы на выходах всех трех элементов И 60-62, подключенных к входам первого вентиля эле5 мента И-ИЛИ-НЕ 49, обеспечивают выработку на его выходе нулевого сигнала, по которому информация через устройство передается по 2 из 3-х.

При исправных блоках-источниках информации не менее чем в двух каналах (см.

первые четыре строки в табл.2) сигналы на прямых выходах элементов И 63-65 по мажоритарному принципу обеспечивают выработку нулевого сигнала на выходе элемента И-ИЛИ-НЕ 49, что также обеспечивает передачу данных через интерфейс по 2 из 3-х.

При исправных блоках-источниках информации только в одном из каналов (см, пятую, шестую и седьмую строки в табл.2) хотя бы на одном из входов каждого вентиля элемента И-ИЛИ-НЕ 49 присутствует нулевой сигнал. Поэтому на выходе элемента И-ИЛИ-НЕ 49 формируется единичный сигнал, который, во-первых, блокирует работу дешифратора 35 отказов и соответственно средств контроля (при единичном сигнале на входе V дешифратора 35 на всех его выходах формируются единичные сигналы, соответствующие отсутствию отказов), во-вторых, обеспечивает работу устройства, как описано выше,

Первый элемент ИЛИ 68 предназначен для формирования сигнала на первом выходе 84.1 требования прерывания канала при наличии отказа хотя бы в одном канале, т.е. при наличии единичного сигнала хотя бы на одном из выходов СН-Оз регистра 5 контроля. Кроме того, единичный сигнал на выходе первого элемента ИЛИ 68 разрешает включение триггера 41 (при единичном сигнале на выходе 05 регистра 5 контроля) и блокирует передачу через элемент И-НЕ 55 синхросигналов на синхровход регистра 5 контроля.

Второй элемент ИЛИ 69 предназначен для сброса регистра 5 контроля и второго триггера 41 управления перестройкой процессора сигналами с выхода пятого элемента ИЛИ 72 или с первого входа 85,2 сброса группы 85 входов канала.

Третий элемента ИЛИ 70 обеспечивает передачу на синхровход второго регистра 15 состояний процессора синхросигналов с выхода седьмого элемента И 66 и с второго входа 85.14 синхросигналов группы 85 управляющих входов канала.

Четвертый 71 и пятый 72 элементы ИЛИ предназначены для формирования сигналов сброса соответствующих элементов памяти устройства. При этом четвертый элемент ИЛИ 71 обеспечивает сброс регистра 12 состояний памяти, первого регистра 14 состояний процессора, счетчиков 16 и 17 и блока 31 пуска счетчиков только при по- ступлеииисигналов сброса по входамВ7.1 и 87.2 канала. Пятый элемент ИЛИ 72 осуществляет сброс остальных элементов памяти устройства в дополнение к вышеописанным сигналам и сигналам с выходов мажоритарного элемента 46 и коммутатора 29. По- скольку в формировании этих дополнительных сигналов сброса устройства участвуют счетчики 16 и 17 и блок 31 пуска счетчиков,

поэтому эти сигналы не используются для сброса этих же счетчиков 16 и 17 и блока 31 пуска счетчиков.

Хотя регистры 12 и 14 состояний памяти и процессора не участвуют в выработке до0 полнительных сигналов сброса устройства, они не сбрасываются этими сигналами, т.к. в них производится запись информации о состоянии блоков при начальной настройке исправной конфигурации блоков, стыкуе5 мых с интерфейсом.

Опишем работу устройства в целом, В процессе эксплуатации устройства оно может включаться в работу и выключаться по окончании работы. На протяже0 нии всего времени эксплуатации могут отказывать его узлы и блоки, стыкуемые с интерфейсом, как во время работы, так и в перерывах между работой. Поэтому работа устройства протекает следующим обра5 зом.

Включение в работу устройства начинается установкой в исходное состояние его узлов и стыкуемых с ним блоков сигналом, поступающим на первый вход 87.1 сброса

0 канала (триггеры 38 и 39 сброса устанавливаются в состояние 10) После этого устройство и стыкуемые с ним блоки начинают работу, причем работа начинается с тестирования состояния этих блоков (сигнал

5 низкого уровня на первом управляющем входе 89 канала), а счетчик 16 временных интервалов задает время тестирования, в течение которого должен быть получен результат нормы контроля с подачей единич0 ного сигнала на вход 89 канала Задание этого времени производится пересчетом импульсов частоты задающего генератора, поступающих на вход 91 канала. При отсутствии нормы контроля за контроль5 ное время (единичный сигнал на входе 89 канала отсутствует) сигнал переполнения счетчика 16 временных интервалов с выхода коммутатора 30 производит сброс элементов памяти устройства (кроме счетчиков 16

0 и 17, регистров 12 и 14, блока 31 пуска счетчиков и триггеров 38 и 39), изменение на единицу младшего разряда состояния счетчика 17. Далее работа устройства и стыкуемых с ним блоков повторяется сначала и

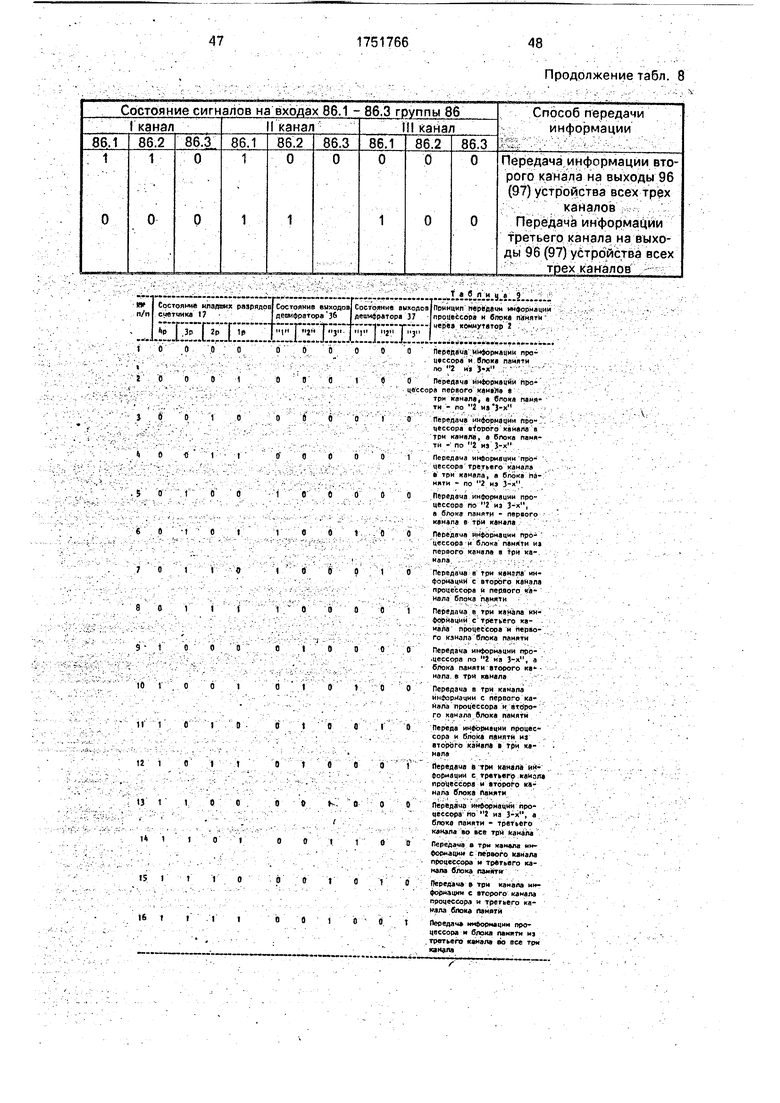

5 повторяется циклически до тех пор, пока не будет автоматически выбрана исправная конфигурация стыкуемых с интерфейсом блоков. При этом конфигурацию блоков определяют содержимое четырех младших разрядов счетчика 17 состояний, дешифрируемое дешифраторами 36 и 37, коды с выходов которых передаются через коммутаторы 20-26, элементы И 60-65, элемент И-ИЛИ-НЕ 49, блок 8 вентилей, мажоритарные элементы 9.1 -9,3 и коммутационный блок 33 на управляющие входы коммутатора 2, определяющие режим передачи данных чрезе интерфейс, В табл.9 показано соответствие работы коммутатора 2 кодам четырех младших разрядов счетчика 17 состояний (примем самый младший разряд счетчика 17 за первый разряд).

Исходным состоянием младших четырех разрядов счетчика 17 является код 0000, конечным их состоянием - код 1111, после чего происходит переход этих разрядов счетчика 17 опять к состоянию 0000. Переполнение счетчика 17 состояний формирует сигнал на выходе 95 устройства (сигнал переполнения проходит через мажоритарный элемент 47 и коммутатор 29 при нулевом сигнале на входе 90 канала) и означает, что не существует ни одной работоспособной конфигурации устройства и стыкуемых с ним блоков

Из кодов табл 9 видно, что работа средств контроля в режиме настройки исправной конфигурации заблокирована,

При получении нормы результатов контроля на первый управляющий вход 89 канала подается единичный сигнал, содержимое счетчика 17 состояний считывается на выход 83 канала через коммутатор 1, мажоритарный блок 44 коммутатор 2 и регистр 6, а в первую зону регистра 12 состояний памяти и в первый регистр 14 состояний процессора заносятся коды, как указано в табл.10 согласно состояниям младших разрядов счетчика 17 (в зоны регистра 12 состояний памяти с второй по последнюю и в регистр 13 состояний УВВ заносятся коды 1t1).

Контроль работы остальных блоков памяти и УВВ производится с использованием средств контроля интерфейса аналогично работе его в основном функционировании,

Работа устройства проходит по программе, определяемой содержимым счетчика 18 адресов команд, при этом на входы 86.1-86.6 группы 86 входов подается код 100111, обеспечивающий работу мажоритарных блоков 42 и 43 в мажоритарном режиме .

Результаты сравнения блоками 32 и 73 сравнения, передаваемые через интерфейс, преобразовываются дешифратором 35 отказов и элементами И-1/1ЛЙ-НЕ 51-53 и И- НЕ 54 в соответствующие коды отказов каналов, запоминаемые в регистре 5 контроля. При этом первый-третий разряды регистра 5 контроля идентифицируют отказавший канал, четвертый разряд фиксирует отказ средств контроля, а пятый - m-й разряды идентифицируют отказавшие блоки в канале.

Наличие отказа в каком-либо канале приводит к формированию сигнала требования на первом выходе 84,1 требования прерывания канала, а коды регистра 5 контроля

0 используются дли занесения соответствующих кодов (см. табл.2) в трехразрядные зоны соответствующих регистров 12-15

Поскольку в устройстве блокируется контроль отказавшего блока и при двух ос5 тавшихся исправными блоках работа их происходит по 2 из 3-х, то замена отказавшего блока может происходит в процессе основного функционирования устройства с занесением соответствующего кода в реги0 стры 12-15 состояний блоков

При отказах одноименного оборудования в двух каналах устройства оно функционирует в режиме передачи информации из исправлного канала в три канала устройства

5 при работе устройства с упомянутым оборудованием в соответствии с вышебписан- ным, причем запрещен контроль всех трех каналов данного оборудования.

Независимая работа трех каналов уст0 ройства задается подачей кода 101011 на входы 86 1-86 6 группы 86 входов во всех трех каналах устройства, при этом в устройстве блокируется работа средств контроля

5 Если в течение работы устройства происходит несанкционированная ситуация типа пропадания питания, причем если критичным является время настройки устройства на исправную конфигурацию для

0 продолжения функционирования, то устройство начинает работу с подачи сигнала на второй вход 87.2 сброса канала. В этом случае период смены состояний счетчика 17 определяется частотой импульсов задаю5 щего генератора на входе 91 канала, а не частотой переполнения счетчика 16 временных интервалов. В остальном работа устройства происходит аналогично описанному выше,

0 Для контроля хода программы в устройстве применен сторожевой таймер, в качестве которого используются счетчики 16 и 17 и блок 31 их пуска. При этом заносимые в них коды определяют время прохождения

5 программы (подпрограммы), в конце которой производится занесение новых кодов в счетчики 16 и 17, определяющие время ра- Х6оты очередной программы (подпрограммы). Если в программе имеется ошибка или происходит сбой, то в течение контрольного

,

времени не произойдет смена кодов в счетчиках 16 и 17 и переполнение сторожевого таймера приведет к сбросу устройства и переходу его к работе, определяемой кодом 11й на выходах триггеров 38 и 39 сброса в 5 соответствии с описанным выше

При необходимости выключения сторожевого таймера производится выключение триггера 128 пуска в блоке 31 пуска счетчиков.10

При необходимости прерывания хода работы устройства при достижении заданной команды в режиме считывания комая- дых слов (граница подпрограммы, за пределами которой может быть брак в про- 15 грамме, или за которой требуется смена подпрограммы по какой-либо другой причине) или при обращении к памяти по определенному адресу в режиме чтения или режиме записи данных в регистр 10 управ- 20 ления признаком прерывания заносится код соответствующего режима, а в регистр 11 адреса признака прерывания - код адре- .са, при обращении к которому требуется сформировать сигнал требования преры- 25 вания. Моменты возникновения того или иного из упомянутых выше режимов в устройстве определяются сигналами на входе 85,22 управления дешифратором признаков прерывания первой группы 85 управляю- 30 щих входов канала. Эти сигналы поступают на первый управляющий вход дешифратора 75 признаков прерывания, который расшифровывает код соответствующего режима в регистре 10 При обращении к 35 соответствующему адресу памяти на выходе блока 74 сравнения адресов, сравнивающего содержимое регистра 11 с кодом адреса на-выходе коммутатора 27 адреса, вырабатывается сигнал, поступающий на АО второй управляющий вход дешифратора 75. При совпадении всех заданных условий на выходе дешифратора 75 формируется сигнал, поступащий на второй выход 84.2 требований прерываний и обеспечивающий 45 прерывание работы устройства.

Работа устройства протекает под управлением сигналов, подаваемых в устройство по группам 85 и 86 управляющих входов и по входам 87-91 каналов, причем в интер- 50 фейсе производится совмещение во времени передачи информации на группу 83 информационных выходов (в соответствии с законом функционирования внешних блоков) с передачей информации на внутренние 55 элементы памяти интерфейса (регистры, счетчики), а контроль работоспособности процессора производится не только в моменты передачи его информации через интерфейс, но и в те моменты време ни, когда

преобразование информации в процессоре происходит без передачи информации через интерфейс/

Таким образом, обеспечивается увеличение оперативности контроля, и соответственно, увеличение скорости настройки интерфейса на работоспособную конфигурацию. Кроме того, обеспечивается возможность динамического исправления ошибок программирования, что, помимо повышения надежности работы устройства, позволяет снизить стоимость вычислительных средств, составной частью которых является предлагаемое устройство.

Дополнительный положительный эффект - это увеличение производительности устройства, так как исключаются потери времени от моментов обнаружения отказа процессора до моментов передачи его информации через интерфейс

Формула изобретения Мажоритарно-резервированный интерфейс памяти, содержащий в каждом канале коммутаторы входной, выходной и служебной информации, регистр контроля, первый и второй буферные регистры, блок вентилей, блок мажоритарных элементов, включающий первый, второй и третий мажоритарные элементы, регистр состояния блоков памяти, регистр состояния устройства ввода-вывода, первый и второй регистры состояния процессора счетчик временных интервалов, счетйик состояний, счетчик адресов команд, счетчик адресов Данных, коммутатор состояния блока памяти, коммутаторы первого, второго и третьего разрядов состояния процессора, первый, второй и третий коммутаторы кодов состояний, коммутатор адреса, коммутатор реконфигурации процесора, коммутатор сигналов переполнения счетчика временных интервалов, блок пуска счетчиков, первый блок сравнения, блок управления коммутацией, преобразователь кодов, дешифратор отказов, дешифратор состояний блока памяти, дешифратор состояний процессора, первый и второй триггеры сброса, первый и второй триггеры управления реконфигурацией процессора, мажоритарные блоки адреса, управления и информации, первый и, второй мажоритарные элементы начальной установки, мажоритарный элемент управления реконфигурацией процессора, с первого по четвертый элементы И-ИЛЙ-НЕ, с первого по четвертый элементы И-НЕ, первый и второй элементы ИЛИ-НЕ, с первого по вось- мой элементы И, с первого по пятый элементы ИЛ И, элемент И-ИЛ И управления реконфигурацией процессора, информационные входы первой-третьей групп коммутатора входной информации являются соответственно информационными входами от процессора, от устройства ввода-вывода и от блока памяти канала, выходы коммутато- ра входной информации соединены с входами первой группы первого блока сравнения, с информационными входами первой группы коммутатора выходной информации, с входами первой группы мажоритарного блока информации и являются межканальными выходами первой группы канала, информационные входы второй группы коммутатора выходной информации соединены с входами второй группы мажоритар- ного блока информации и являются межканальными входами второй группы канала, входы третьей группы мажоритарного блока информации соединены с информационными входами третьей группы комму- татора выходной информации, с входами второй группы первого блока сравнения и являются межканальными входами первой группы канала, выходы мажоритарного блока информации - с информационными вхо- дами четвертой группы коммутатора выходной информации, выходы которого соединены с информационными входами первого и второго буферных регистров, входы синхронизации которых являются соответ- ствующими входами канала, выходы второго буферного регистра соединены с входами первой группы коммутатора служебной информации, входы второй группы которого соединены с информационными входами счетчиков адресов команд и адресов данных, с выходами первого буферного регистра и являются информационными выходами канала, входы управления коммутаторов входной и служебной информации являются соответствующими управляющими входами канала, выходы коммутатора служебной информации Соединены с входами первой группы коммутатора реконфигурации процессора, с информационными входами пер- вого регистра состояния процессора, счетчика временных интервалов, счетчика состояний, регистра состояния блоков памяти, регистра состояния устройства ввода- вывода и блока пуска счетчиков, вход синхронизации которого является соответствующим входом канала, тактовый вход блока пуска счетчиков соединен с входом синхронизации первого триггера управления реконфигурацией процессора, с первым входом седьмого элемента И и является входом частоты задающего генератора канала, входы установки блока пуска счетчиков, счетчика временных интервалов, счетчика состояний, регистра состояния блоков памяти и первого регистра состояния процессора объединены и соединены с выходом четвертого элемента ИЛИ, первый и второй входы которого соединены с первым и вторым входами пятого элемента ИЛИ и с первым входом установки и вторым входом сброса соответствующих триггеров сброса соответственно и являются первым и вторым входами сброса канала, первые входы сброса первого и второго триггеров сброгэ объединены и являются вторым входом установки канала, вторые входы установки первого и второго триггеров сброса обьеди- нены и соединены с третьим входом пятого элемента ИЛИ и с первым выходом коммутатора сигналов переполнения счетчика состояний, второй выход которого является выходом временных меток канала, выходы счетчика адресов команд соединены с информационными входами четвертой группы коммутатора входной информации и с входами первой группы коммутатора адреса, входы второй группы которого соединены с выходами счетчика адресов данных, вход установки которого соединен с входами установки счетчика адресов команд, первого триггера управления реконфигурацией процессора, второго регистра состояния процессора, регистра состояния устройства ввода-вывода, с первым входом второго элемента ИЛИ и с выходом пятого элемента ИЛИ и является выходом сброса канала, второй вход второго элемента ИЛИ - первым входом установки канала, входы синхронизации, уменьшения и увеличения содержимого счетчиков адресов команд и адресов данных являются соответствующими входами канала, выход блока пуска счетчиков соединен со счетным входом счетчика временных интервалов и с первым входом коммутатора сигналов переполнения счетчика временных интервалов, второй вход которого соединен с выходом переполнения счетчика временных интервалов, информационные выходы которого соединены с информационными выходами счетчика состояний и с информационными входами пятой группы коммутатора входной информации, управляющий вход коммутатора сигналов переполнения счетчика временных интервалов - с выходом первого элемента ИЛИ-НЕ, первый вход которого соединен с входом управления блока пуска счетчиков, с первым входом второго элемента ИЛИ- НЕ, с вторыми управляющими входами коммутаторов первого-третьего разрядов состояния процессора, с управляющим входом коммутатора состояний блока памяти и является первым управляющим входом канала, второй вход первого элемента

ИЛИ-НЕ соединен с выходом четвертого элемента И-НЕ, первый и второй входы которого соединены соответственно с инверсным выходом первого и с прямым выходом второго триггеров сброса, прямые выходы которых являются первым и вторым выходами кода начальной установки канала соответственно, выход коммутатора сигналов переполнения счетчика временных интервалов соединен со счетным входом счетчика состояний и с инверсным входом второго элемента ИЛИ-НЕ, выход которого соединен с первым входом первого мажоритарного элемента начальной установки и является вторым межканальным выходом канала, выход переполнения счетчика состояний соединен с первым входом второго мажоритарного элемента начальной установки и является третьим межканальным выходом канала, вход синхронизации счетчика состояний является соответствующим входом канала, второй и третий входы первого и второго мажоритарных элементов началь- .ной установки являются соответственно третьим и четвертым, пятым и шестым межканальными входами канала, выход первого мажоритарного элемента начальной установки соединен с четвертым входом пятого элемента ИЛИ, выход второго мажоритарного элемента начальной установки - с входом коммутатора сигналов переполнения счетчика состояний, управляющий вход которого является вторым управляющим входом канала, вход синхронизации первого регистра состояния процессора является соответствующим входом канала, первый- третий выходы первого регистра состояния процессора соединены соответственно с входами третьего разряда коммутаторов первого-третьего разрядов состояния процессора, объединенные входы первого и второго разрядов которых соединены с соответствующими выходами дешифратора состояний процессора, входы которого соединены с соответствующими информацион- ными выходами счетчика состояний, пер вый-третий выходы второго регистра состояний процессора соединены соответственно с входами четвертого разряда коммутаторов первого-третьего разрядов состояния процессора и с входами второй группы коммутатора реконфигурации процессора, выходы которого соединены с информационными входами второго регистра состояния процессора, вход синхронизации которого соединен с выходом третьего элемента ИЛИ, первый вход которого является входом синхронизации второго регистра состояния процессора канала, второй вход третьего элемента ИЛИ соединен с выходом

седьмого элемента И, второй вход которого соединен с выходом первого триггера управления реконфигурацией процессора, информационный вход которого соединен с

третьим входом седьмого элемента И, с управляющим входом коммутатора реконфигурации процессора, с первыми управляющими входами коммутаторов первого- третьего разрядов состояния процессора и

0 с выходом мажоритарного элемента управления реконфигурацией процессора, первый вход которого соединен с выходом восьмого элемента И и является первым межканальным выходом канала, второй и

5 третий входы - соответственно первым и вторым межканальными входами канала, выходы коммутаторов первого-третьего разрядов состояния процессора соединены соответственно с входами первого раз0 ряда первого-третьего коммутаторов кодов состояний, дополнительные информационные входы которых подключены к шине нулевого потенциала, входы синхронизации регистров состояния блоков памяти и ус5 тройства ввода-вывода являются соответствующими входами канала, выходы первого-третьего разрядов регистра состояния устройства ввода-вывода соединены соответственно с входами второго разряда

0 первого-третьего коммутаторов кодов состояний, входы дешифратора состояний блока памяти - с соответствующими информационными выходами сччетчика состояний, выходы дешифратора состояний блока па5 мяти - с входами первой группы коммутатора состояния блока памяти, входы второй группы которого соединены с выходами первой зоны регистра состояния блоков памяти, выходы первого - третьего разрядов